格雷码、二进制转换电路,vhdl南京理工大学紫金学院实验报告,eda

南京理工大学EDA设计(一)实验报告

南京理⼯⼤学EDA设计(⼀)实验报告(此⽂档为word格式,下载后您可任意编辑修改!)⽬录实验⼀单级放⼤电路的设计与仿真 (2)⼀、实验⽬的 (2)⼆、实验要求 (2)三、实验原理图 (3)四、实验过程及结果 (3)1、电路的饱和失真和截⽌失真分析 (3)2、三极管特性测试 (7)3.电路基本参数测定 (10)五、数据分析 (14)六、实验感想 (14)实验⼆差动放⼤电路的设计与仿真 (15)⼀、实验⽬的 (15)⼆、实验要求 (15)三、实验原理图 (15)四、实验过程及结果 (17)1、电路的静态分析 (17)2.电路电压增益的测量 (23)五、数据分析 (26)六、实验感想 (27)实验三反馈放⼤电路的设计与仿真 (27)⼀、实验⽬的 (27)⼆、实验要求 (27)三、实验原理图 (27)四、实验过程及结果 (28)1.负反馈接⼊前后放⼤倍数、输⼊电阻、输出电阻的测定 (28)2.负反馈对电路⾮线性失真的影响 (32)五、实验结论 (37)六、实验感想 (37)实验四阶梯波发⽣器电路的设计 (38)⼀、实验⽬的 (38)⼆、实验要求 (38)三、电路原理框图 (38)四、实验过程与仿真结果 (39)1.⽅波发⽣器 (39)2.微分电路 (40)3.限幅电路 (42)4.积分电路 (43)5.⽐较器及电⼦开关电路 (45)五、实验思考题 (46)六、实验感想 (47)写在后⾯的话对此次EDA设计的感想 (47)问题与解决 (47)收获与感受 (48)期望与要求 (48)实验⼀单级放⼤电路的设计与仿真⼀、实验⽬的1.掌握放⼤电路静态⼯作点的调整和测试⽅法2.掌握放⼤电路的动态参数的测试⽅法3.观察静态⼯作点的选择对输出波形及电压放⼤倍数的影响⼆、实验要求1.设计⼀个分压偏置的胆管电压放⼤电路,要求信号源频率10kHz(峰值1—10mV),负载电阻,电压增益⼤于80.2.调节电路静态⼯作点(调节偏置电阻),观察电路出现饱和失真和截⽌失真的输出信号波形,并测试对应的静态⼯作点值。

格雷码和二进制的相互转换-vhdl程序剖析

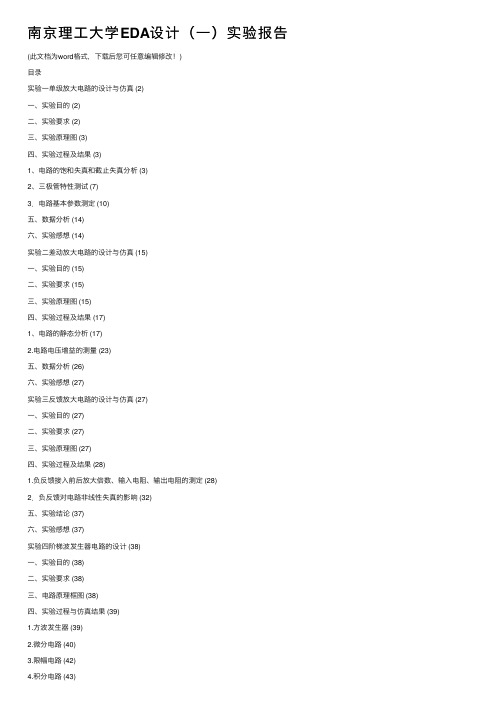

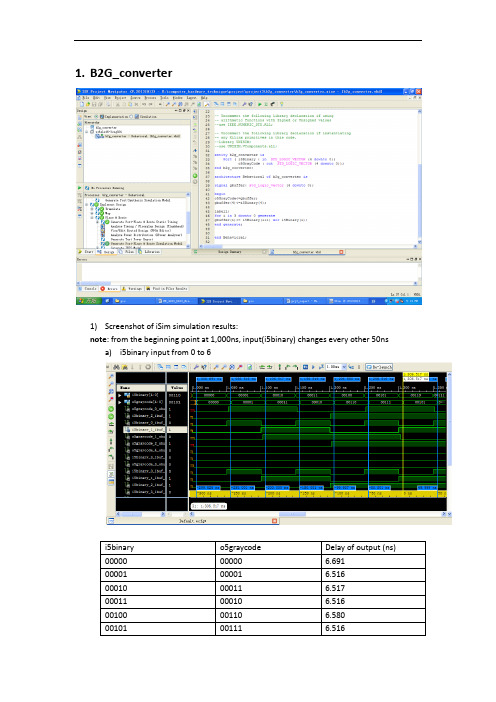

1.B2G_converter1)Screenshot of iSim simulation results:note: from the beginning point at 1,000ns, input(i5binary) changes every other 50nsa)i5binary input from 0 to 6b)i5binary input from 7 to 13c)i5binary input from 14 to 20d)i5binary input from 21 to 27e)i5binary input from 28 to 312)VHDL for Binary-to-Gray-Code converter:------------------------------------------------------------------------------------ Company:-- Engineer:---- Create Date: 13:02:37 09/15/2015-- Design Name:-- Module Name: b2g_converter - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating-- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity b2g_converter isPort ( i5Binary : in STD_LOGIC_VECTOR (4 downto 0);o5GrayCode : out STD_LOGIC_VECTOR (4 downto 0));end b2g_converter;architecture Behavioral of b2g_converter issignal gbuffer: std_logic_vector (4 downto 0);begino5GrayCode<=gbuffer;gbuffer(4)<=i5Binary(4);label1:for i in 3 downto 0 generategbuffer(i)<= i5Binary(i+1) xor i5Binary(i);end generate;end Behavioral;2.G2B_converter1)Gray-code-to-Binary conversionFrom the combinational logic described for gray-code-to-binary conversion, we obtain:Thus, for a n-bit graycode number g, g=g(n-1)g(n-2)…g(2)g(1)g(0), the corresponding n-bit binary number b, b=b(n-1)b(n-2)…b(2)b(1)b(0) is computed using the following description:b(n-1)=g(n-1) for the MSB, andb(i)= g(i) b(i+1) for bits in position 0 to n-22)Screenshot of iSim simulation results:note: from the beginning point at 1,000ns, input(i5graycode) changes every other 50nsa)i5graycode input from 0 to 6b)i5graycode input from 7 to 13c)i5graycode input from 14 to 20d)i5graycode input from 21 to 27e)i5graycode input from 28 to 313)VHDL for Gray-Code-to-Binary converter:------------------------------------------------------------------------------------ Company:-- Engineer:---- Create Date: 15:20:03 09/15/2015-- Design Name:-- Module Name: g2b_converter - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------ library IEEE;use IEEE.STD_LOGIC_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating-- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity g2b_converter isPort ( i5GrayCode : in STD_LOGIC_VECTOR (4 downto 0);o5Binary : out STD_LOGIC_VECTOR (4 downto 0)); end g2b_converter;architecture Behavioral of g2b_converter issignal bbuffer: std_logic_vector (4 downto 0);begino5Binary <= bbuffer;bbuffer(4)<= i5GrayCode(4);label1:for i in 3 downto 0 generatebbuffer(i)<= bbuffer(i+1) xor i5GrayCode(i); end generate;end Behavioral;。

(最新版)南京理工大学EDA设计实验报告

摘要通过实验学习和训练,掌握基于计算机和信息技术的电路系统设计和仿真方法。

要求:1. 熟悉Multisim软件的使用,包括电路图编辑、虚拟仪器仪表的使用和掌握常见电路分析方法。

2. 能够运用Multisim软件对模拟电路进行设计和性能分析,掌握EDA设计的基本方法和步骤。

Multisim常用分析方法:直流工作点分析、直流扫描分析、交流分析。

掌握设计电路参数的方法。

复习巩固单级放大电路的工作原理,掌握静态工作点的选择对电路的影响。

了解负反馈对两级放大电路的影响,掌握阶梯波的产生原理及产生过程。

关键字:电路仿真 Multisim 负反馈阶梯波目次实验一 (1)实验二.............................................................................................11实验三 (17)实验一单级放大电路的设计与仿真一、实验目的1.设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz(峰值10mV) ,负载电阻5.1kΩ,电压增益大于50。

2.调节电路静态工作点(调节电位计),观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3.调节电路静态工作点(调节电位计),使电路输出信号不失真,并且幅度尽可能大。

在此状态下测试:①电路静态工作点值;②三极管的输入、输出特性曲线和β、r be 、r ce值;③电路的输入电阻、输出电阻和电压增益;④电路的频率响应曲线和f L、f H值。

二、实验要求1.给出单级放大电路原理图。

2.给出电路饱和失真、截止失真和不失真且信号幅度尽可能大时的输出信号波形图,并给出三种状态下电路静态工作点值。

3.给出测试三极管输入、输出特性曲线和β、r be 、r ce值的实验图,并给出测试结果。

4.给出正常放大时测量输入电阻、输出电阻和电压增益的实验图,给出测试结果并和理论计算值进行比较。

南京理工大学EDA设计实验报告

目录设计一单级放大电路设计 (3)一、设计要求 (3)二、实验原理图 (3)三、实验过程及测试数据 (3)1. 调节电路静态工作点,测试电路饱和失真、截止失真和不失真的输出信号波形图,以及三种状态下电路静态工作点值。

(3)2. 在正常放大状态下,测试三极管输入、输出特性曲线以及、的值。

(7)3. 在正常放大状态下,测试电路的输入电阻、输出电阻和电压增益。

.94. 在正常放大状态下,测试电路的频率响应曲线和、值。

(10)四、实验数据整理 (11)五、实验数据分析 (11)设计二差动放大电路设计 (13)一、设计要求 (13)二、实验原理图 (13)三、实验过程及测试数据 (13)1.双端输出时,测试电路每个三极管的静态工作点值和、、值。

(13)2. 测试电路双端输入直流小信号时,电路的、、、值。

173. 测试射级恒流源的动态输出电阻。

(21)四、实验数据整理 (21)五、实验数据分析 (22)设计三负反馈放大电路设计 (24)一、设计要求 (24)二、实验原理图 (24)三、实验过程及测试数据 (24)1. 测试负反馈接入前,电路的放大倍数、输入电阻、输出电阻。

(24)2. 测试负反馈接入后,电路的放大倍数、输入电阻、输出电阻并验证。

(25)3. 测试负反馈接入前,电路的频率特性和、值,以及输出开始出现失真时的输入信号幅度。

(27)4. 测试负反馈接入后,电路的频率特性和、值,以及输出开始出现失真时的输入信号幅度。

(28)四、实验数据整理 (30)五、实验数据分析 (31)设计四阶梯波发生器设计 (31)一、设计要求 (31)二、实验原理图 (32)三、实验过程及与仿真结果 (32)1.方波发生器 (33)2.方波电路+微分电路 (34)3.方波电路+微分电路+限幅电路 (35)4.方波电路+微分电路+限幅电路+积分电路 (36)5.阶梯波发生总电路 (36)四、实验结果分析 (38)五、技术改进 (38)设计一单级放大电路设计一、设计要求1.设计一个分压偏置的单管电压放大电路,要求信号源频率20kHz,峰值5mV,负载电阻1.8kΩ,电压增益大于50。

格雷码、二进制转换及译码电路

EDA技术与应用实验报告实验名称:格雷码、二进制转换及译码电路姓名:陈丹学号:2班级:电信(2)班时间:南京理工大学紫金学院电光系一、实验目的1)学习用VHDL代码描述组合逻辑电路的方法。

2) 掌握when….else….,generate和case并行语句的使用。

二、实验原理1)学习VHDL的when….else….,generate和case并行语句。

2)利用when….else….并行语句描述4位二进制码/格雷码转换电路。

3)利用generate并行语句描述n位格雷码/二进制码转换电路。

4)利用case并行语句实现译码电路。

5)利用实验箱验证所设计的电路的正确性,要求将输入输出的数据用数码管显示。

三、实验内容1、二进制转换为格雷码4位二进制格雷码转换的真值表如图所示:建立工程,输入代码先建立工程,工程命名为“btog”,顶层文件名为“btog”。

选择“file→new”,在弹出的窗口中选择“VHDL File”建立“VHDL”文件。

在新建的VHDL文件中输入二进制格雷码转换的VHDL代码,将文件保存。

二进制转换为格雷码的代码:编译仿真对当前文件进行编译,编译通过以后建立仿真波形,保存为“”.为波形文件添加节点,将“end time”设置为100μs ,将输入输出编组,并为输入信号赋值,其中“start value”为“0000”,“count every”设置为5μs.其波形如下:仿真结果2、generate语句实现格雷码转换为二进制对于n位二进制转换为格雷码的码转换电路,转换表达式如下:Bn=GnBi=Gi⊕B(i+1)建立工程,输入代码先建立工程,工程命名为“gtob”,顶层文件名为“g_to_b2”。

选择“file→new”,在弹出的窗口中选择“VHDL File”建立“VHDL”文件。

在新建的VHDL文件中输入格雷码二进制转换的VHDL代码,将文件保存。

转换代码:编译仿真对当前文件进行编译,编译通过以后建立仿真波形,保存为“”.为波形文件添加节点,将“end time”设置为100μs ,将输入输出编组,并为输入信号赋值,其中“start value”为“0000”,“count every”设置为5μs.其波形如下:3、case语句实现译码电路代码描述:仿真波形:4、管脚配置利用实验箱的模式6来验证设计电路的正确性。

南理工EDA设计实验报告

南京理工大学EDA设计(Ⅰ)实验报告作者: 周竹青学号:914000720215 学院(系):教育实验学院专业: 自动化吴少琴指导老师:实验日期: 10.10--- 10.132016年 10月摘要本次EDA实验主要由四个实验组成,分别是单级放大电路的设计与仿真、差动放大电路的设计与仿真、负反馈放大电路的设计与仿真、阶梯波发生器电路的设计。

通过电路的设计和仿真过程,进一步强化对模拟电子线路知识的理解和应用,增强实践能力和对仿真软件的运用能力。

关键词EDA 设计仿真AbstractThe EDA experiment mainly consists of four experiments, respectively. The design and Simulation of single stage amplifier, differential amplifier circuit,the negative feedback amplifier circuit and ladder wave generator circuit. Through the circuit design and simulation process, We can further strengthen the understanding and application of analog electronic circuit knowledge and enhance practical ability and the ability to use simulation software.Keywords EDA simulation design目录实验一单级放大电路的设计与仿真 (4)实验二差动放大电路的设计与仿真 (17)实验三负反馈放大电路的设计与仿真 (26)实验四阶梯波发生器电路的设计与仿真 (38)结论 (58)参考文献 (58)实验一单级放大电路的设计与仿真一、实验目的1、掌握放大电路静态工作点的调试方法。

南京理工大学EDA(2)实验报告

南京理⼯⼤学EDA(2)实验报告南京理⼯⼤学EDA(2)实验报告--------多功能数字钟学⽣姓名:林晓峰学号:912104220143 专业:通信⼯程指导教师:2014年12⽉10⽇摘要本次实验利⽤QuartusII7.0软件设计了⼀个具有24⼩时计时、保持、清零、快速校时校分、整点报时、动态显⽰等功能的的多功能数字钟。

并利⽤QuartusII7.0软件对电路进⾏了详细的仿真,同时通过SMART SOPC实验箱对电路的实验结果进⾏验证。

报告分析了整个电路的⼯作原理,还分别说明了设计各⼦模块的⽅案和编辑、仿真、并利⽤波形图验证各⼦模块的过程。

并且介绍了如何将各⼦模块联系起来,合并为总电路。

最后对实验过程中产⽣的问题提出⾃⼰的解决⽅法。

并叙述了本次实验的实验感受与收获。

关键词:QuartusII7.0 多功能数字钟保持清零整点报时校时校分动态显⽰ SMART SOPCAbstractThis experiment uses the QuartusII7.0 software todesign one to have 24 hours time, the maintenance, the reset,the fast timing school minute,the integral point reportstime and so on digital clocks.And using the QuartusII software realizes the multi-purpose digital clock simulation. Through the SmartSOPC experiment box, I confirm the result of this experiment.The report analyzes the electric circuit principle of work,and also illustrates the design of each module and editing, simulation, and the process of using the waveformto testing each Sub module. Meanwhile,it describes how the modules together, combined for a total circuit. Finally the experimental problems arising in the process of presenttheir solutions. And describes the experience and resultof this experiment.Keywords:QuartusII7.0 Digital clock maintenancereset time alarm change minute and hour quickly dynamic display SMART SOPC⽬录封⾯ (1)摘要 (2)Abstract (3)⽬录 (4)1.设计要求 (5)2.实验原理 (6)3.模块电路设计 (7)3.1 脉冲发⽣电路 (7)3.2计数器 (10)3.3计时校正电路 (13)3.4整点报时电路 (17)3.5译码显⽰电路 (18)3.6附加电路 (19)4. 总电路图 (20)5.电路下载 (20)6.实验感想和收获 (21)6.1遇到的问题与解决⽅案 (22)6.2收获与感受 (23)6.3期望及要求 (23)7. 参考⽂献 (23)1.设计要求本次EDA设计利⽤Quartus II7.0软件设计⼀个多功能数字钟,并下载到Smart SOPC实验系统中进⾏验证。

三位计时电路设计,南京理工大学紫金学院vhdl实验报告,eda

EDA技术与应用实验报告实验名称:三位计时电路设计姓名:学号:班级:通信时间:2013南京理工大学紫金学院电光系一、实验目的1、学习利用顺序语句描述电路的方法。

2、学习进程、常用顺序语句的使用。

3、掌握分频电路的设计;掌握利用不完整条件语句构成时序逻辑电路的方法。

二、实验原理1、if语句if语句是具有条件控制功能的语句,它根据指定的条件及其条件是否成立来确定语句的执行顺序,格式如下。

1)格式1if 条件1 then第1组顺序语句;Elsif 条件2 then第2组顺序语句;……elsif 条件 n then第n组顺序语句;else第n+1组顺序语句;end if;在该形式的if语句中,只要满足条件1到条件n中的一个条件就执行一条顺序语句,且最优先的条件为条件1,次要的条件列到后面。

2)格式2(嵌套)if 条件1 thenif 条件2 then……一组顺序语句end if;end if;在该形式的if语句中,只有满足条件1到条件n中的所有条件才能执行相应的顺序语句,且最优先的条件为条件1,次要的条件列到后面。

3)格式3if 条件 then顺序语句;else顺序语句;end if;注意:只有不完整的条件语句才能构成时序逻辑电路,完整的条件语句只能构成组合逻辑电路。

2、进程语句进程主要用于描述顺序语句,其格式如下:标记:process (敏感信号表)声明语句;begin顺序语句end process;声明语句中可以定义一些局部量,可以包括数据类型、常数、变量、属性、子程序等,不能定义信号。

进程语句本为一无限循环语句,进程的启动由敏感信号的变化来启动,否则必须有一个wait语句来激励。

虽然进程中包含了顺序语句,但是进程本身是并行语句,即同一结构体中不同进程是并行运行的。

信号和变量3、信号信号代表电路内部信号传输线路,在元件之间起互连作用,相当于连线,可以通过端口和其他模块相连接。

说明:1)信号时一个全局量,可以在ENTITY和ARCHITECTURE中定义,不可以在进程和子程序的顺序语句中定义信号,但可以在VHDL语句的并行部分和顺序部分同时使用。

格雷码和二进制的相互转换-vhdl程序

1.B2G_converter1)Screenshot of iSim simulation results:note: from the beginning point at 1,000ns, input(i5binary) changes every other 50nsa)i5binary input from 0 to 6b)i5binary input from 7 to 13c)i5binary input from 14 to 20d)i5binary input from 21 to 27e)i5binary input from 28 to 312)VHDL for Binary-to-Gray-Code converter:------------------------------------------------------------------------------------ Company:-- Engineer:---- Create Date: 13:02:37 09/15/2015-- Design Name:-- Module Name: b2g_converter - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating-- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity b2g_converter isPort ( i5Binary : in STD_LOGIC_VECTOR (4 downto 0);o5GrayCode : out STD_LOGIC_VECTOR (4 downto 0));end b2g_converter;architecture Behavioral of b2g_converter issignal gbuffer: std_logic_vector (4 downto 0);begino5GrayCode<=gbuffer;gbuffer(4)<=i5Binary(4);label1:for i in 3 downto 0 generategbuffer(i)<= i5Binary(i+1) xor i5Binary(i);end generate;end Behavioral;2.G2B_converter1)Gray-code-to-Binary conversionFrom the combinational logic described for gray-code-to-binary conversion, we obtain:Thus, for a n-bit graycode number g, g=g(n-1)g(n-2)…g(2)g(1)g(0), the corresponding n-bit binary number b, b=b(n-1)b(n-2)…b(2)b(1)b(0) is computed using the following description:b(n-1)=g(n-1) for the MSB, andb(i)= g(i) b(i+1) for bits in position 0 to n-22)Screenshot of iSim simulation results:note: from the beginning point at 1,000ns, input(i5graycode) changes every other 50nsa)i5graycode input from 0 to 6b)i5graycode input from 7 to 13c)i5graycode input from 14 to 20d)i5graycode input from 21 to 27e)i5graycode input from 28 to 313)VHDL for Gray-Code-to-Binary converter:------------------------------------------------------------------------------------ Company:-- Engineer:---- Create Date: 15:20:03 09/15/2015-- Design Name:-- Module Name: g2b_converter - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------ library IEEE;use IEEE.STD_LOGIC_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating-- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity g2b_converter isPort ( i5GrayCode : in STD_LOGIC_VECTOR (4 downto 0);o5Binary : out STD_LOGIC_VECTOR (4 downto 0)); end g2b_converter;architecture Behavioral of g2b_converter issignal bbuffer: std_logic_vector (4 downto 0);begino5Binary <= bbuffer;bbuffer(4)<= i5GrayCode(4);label1:for i in 3 downto 0 generatebbuffer(i)<= bbuffer(i+1) xor i5GrayCode(i); end generate;end Behavioral;。

VHDL实验报告

VHDL实验报告5090309160 庄炜旭实验三. 4位可逆计数器,4位可逆二进制代码-格雷码转换器设计一.实验目的学习时序电路的设计,仿真和硬件测试,进一步熟悉VHDL设计技术1. 学习4位可逆计数器的设计2. 学习4位可逆二进制代码-格雷码转换器设计二.实验内容设计4位可逆计数器,及4位可逆二进制代码-格雷码转换器,并仿真,下载。

[具体要求]1.4位可逆计数器a)使用CLOCK_50作为输入时钟,其频率为50MHz(对于频率大于50Hz的闪烁,人眼会看到连续的光),因而,对其进行225的分频后,再用于时钟控制。

(可利用实验一)b)使用拨码开关SW17作为模式控制,置‘1’时为加法计数器,置‘0’时为减法计数器,同时使用LEDR17显示SW17的值。

c)使用KEY3作为异步复位开关(按下时为0,不按为1),当为加法计数器时,置“0000”,当为减法计数器时,置“1111”。

d)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

2.4位可逆二进制代码――格雷码转换器a)使用拨码开关SW17作为模式控制,置‘1’时为二进制代码―>格雷码转换,置‘0’时为格雷码―>二进制代码,同时使用LEDR17显示SW17的值。

b)使用拨码开关SW3, SW2, SW1, SW0作为输入的被转换数,SW3为高位,SW0为低位。

c)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

三.管脚设定SW[0]PIN_N25SW[1]PIN_N26SW[2]PIN_P25SW[3] PIN_AE14SW[17] PIN_V2LEDR[0] PIN_AE23LEDR[1] PIN_AF23LEDR[2] PIN_AB21LEDR[3] PIN_AC22LEDR[17] PIN_AD12KEY[3] PIN_W26CLOCK_50 PIN_N2四.相关知识二进制代码与格雷码相互转换格雷码(Gray Code,简称G码)是典型的循环码,它是由二进制码(Binary,简称 B 码)导出的。

南理工EDA实验报告

课程作业课程名称EDA 设计(I)实验题目名称EDA 设计(I)实验报告学生学院电子工程与光电技术学院专业班级电子信息工程666班学号66666666学生姓名xx指导教师xxx2016年9月EDA设计(Ⅰ)实验报告目录实验一单级放大电路设计与仿真 (4)一、实验要求 (4)二、实验原理图 (4)三、实验过程与结果 (3)1. 三极管特性测试 (5)2. 静态工作点的调节 (6)3. 电路基本参数测定 (9)四、数据表 (12)五、数据分析 (12)实验二差动放大电路设计与仿真 (13)一、实验要求 (13)二、实验原理图 (13)三、实验过程与结果 (14)1. 电路的静态分析 (14)2. 电路电压增益的测量 (20)四、数据表 (23)五、数据分析 (23)实验三负反馈放大电路设计与仿真 (25)一、实验要求 (25)二、实验原理图 (25)三、实验过程与结果 (26)1. 负反馈接入前后电路放大倍数、输入、输出电阻和频率特性的测定 (26)EDA设计(Ⅰ)实验报告2. 负反馈对对电路非线性失真的影响 (31)四、数据表 (34)实验四阶梯波发生器设计与仿真 (35)一、实验要求 (35)二、实验原理图 (35)三、实验过程与结果 (36)1. 方波发生器 (36)2. 微分电路 (36)3. 限幅电路 (36)4. 积分电路 (37)5. 比较器及电子开关电路 (37)四、数据分析 (38)五、实验小结 (45)实验一单级放大电路设计一、实验目的(1)设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz,峰值5mV ,负载电阻5.1kΩ,电压增益大于70。

(2)调节电路静态工作点,观察电路出现饱和失真、截止失真和正常放大的输出信号波形,并测试对应的静态工作点值。

(3)在正常放大状态下测试:3.1三极管的输入、输出特性曲线和 、rbe 、rce值;3.2电路的输入电阻、输出电阻和电压增益;3.3电路的频率响应曲线和fL、fH值。

南京理工大学EDA(Ⅰ) 优秀报告

实验报告目录设计一—单级放大电路设计 (1)一、设计要求 (1)二、实验原理图 (1)三、仿真测试图及数据 (2)四、数据整理 (13)五、数据分析 (15)设计二—差动放大电路设计 (16)一、设计要求 (16)二、实验原理图 (16)三、仿真测试图及数据 (17)四、数据整理 (25)五、数据分析 (27)设计三—负反馈放大电路设计 (29)一、设计要求 (29)二、实验原理图 (29)三、仿真测试图及数据 (30)四、数据整理 (39)设计四—阶梯波发生器设计 (40)一、设计要求 (40)二、实验原理图 (40)三、电路的工作原理及分段波形 (42)四、阶梯波波形参数 (47)五、思考题 (48)六、改进与创新 (49)设计一—单级放大电路设计一、设计要求1.设计一个分压偏置的单管电压放大电路,要求信号源频率20kHz,峰值5mV ,负载电阻1.8kΩ,电压增益大于50。

2.调节电路静态工作点,观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3.在正常放大状态下测试:①电路静态工作点值;②三极管的输入、输出特性曲线和 、r be 、r ce值;③电路的输入电阻、输出电阻和电压增益;④电路的频率响应曲线和f L、f H值。

二、实验原理图上图即为一个阻容耦合分压偏置的单管电压放大电路,主要由三极管Q1,偏置电阻R3、R4,射极电阻、反馈电阻R3,耦合电容C1、C3,旁路电容C2,负载电阻R6构成。

偏置电阻R3、R4将VCC分压后加到三极管基极,通过改变偏置电阻阻值即可改变静态工作点。

下文称此图为基本电路图。

三、仿真测试图及数据1、在要求信号源频率20kHz,峰值5mV ,负载电阻1.8kΩ时电压增益通过测量输入、输出电压即可求得电压增益,如下:由上图数据可求得电压增益:A u=u ou i=192.105mV3.535mV=54.34符合题目要求。

2、输入、输出电阻测量输入电阻:由上图数据可得:R i=u ii i=3.535mV968.136nA=3651Ω输出电阻:由上图数据可得:R o=u oi o=3.535mV743.943nA=4752Ω正常放大波形图:正常放大时静态工作点值:由此可以得到:β=I CQI BQ=1.0964mA5.21593μA=210在静态工作点过高时,输入信号的正半波超过了三极管的放大能力,进入饱和状态,造成饱和失真,对应的输出波形就是输出波形底部失真。

格雷码、二进制码转换

entity and_gate is port(a,b: IN std_logic; y: out std_logic); end and_gate; architecture rhl of and_gate is begin y<=a and b; end rhl;

条件句中的“=>”不是操作符,只相当于“THEN”作用。

南理工紫金学院

EDA设计实验

由于case属于顺序语句, 在VHDL中顺序语句只能存 在与进程中。

南理工紫金学院

VHDL 常用基本语句

EDA设计实验

进程语句

进程主要用于描述顺序语句,其格式如下:

标记:process (敏感信号表 ) --变量声明语句; begin --顺序语句 end process; 敏感信号(包括端口信号)指那些值发生改变后能引起 进程语句执行的信号。当敏感信号发生改变时,进程启 动,begin和end之间的语句从上到下顺序执行一次,然 后返回进程语句开始,等待下一次敏感信号的变化。因 此进程语句有两种状态:等待状态和执行状态。 南理工紫金学院

1 声明部分包括:结构体所用的内部信号及数据类型; 元件例化声明。

2 结构体部分主要包括:并行语句信号赋值; 进程(顺序语句); 元件例化语句。 3 最后以end结束结构体部分。 南理工紫金学院

EDA设计实验

逻辑运算符

And(与),Or(或),Not(非), Nand(与非),Nor(或非),Xor(异或), Xnor(同或)。

EDA设计实验

第二节 格雷码、二进制码转换

南理工紫金学院

EDA设计实验

实验内容

差分放大电路 ,南京理工大学紫金学院eda实验报告

恒流源单端输出静态: VC2=VCC-IcR3=7.49V VE1=VE2=-UBE-IB1R7=0.94V (VCC-UC1)/R3=IC1+VC1/R4 得:VC1=3.74V

动态分析: 1)双端输出:Ad=-β(R2//R4/2)/(R7+rbe+(1+β)*R6/2)=-9.35 Ri=2(R7+rbe+(1+β)*R6/2)=49.67 kΩ Ro=2R2=16.4kΩ 2)单端输出:Ad=-1/2*β(R2//R4)/(R7+rbe+(1+β)*R6/2)=-7.08 Ri=2(R7+rbe+(1+β)*R6/2)=49.67 kΩ Ro=R2=8.2kΩ 3、差模信号输入:测量单端输出;双端输出情况下,长尾和恒源差 放的电压放大倍数,填入表格。

UR10 R10 VEE R 5 R10 IE 3 UR10 UBE 3 IC 3 R1 IE1 IE 2 IC 3 2

UCE1 VC1 VE1

UCE2=VC2-VE

VCC VC 1 IC1 VC1 R2 R4

VC 2 VCC IC 2 R 3

三.实验内容 (一)题目 电路如图所示,三极管 3DG6D 的 rbb’=60Ω, ß=85,UBE=0.75V。 1 按要求连接电路。 2 计算求出长尾式,恒流源单端输出和双端输出电路的静态工作点, 电压放大倍数,输入电阻,输出电阻。 3 差模信号输入:测量单端输出;双端输出情况下,长为和恒源差

UCE2=VC2-VE

3 恒流源双端输出:

R10 VEE R 5 R10 VC1 VCC ICR 2 UR10 IE 3 UR10 UBE 3 IC 3 R1 VE1 IBR 7 UBE IE1 IE 2 IC 3 2 UCE1 VC VE

格雷码 二进制码转换

实验目的:

1)用组合电路设计4位格雷码/二进制码变换电路。 2)学习利用原理图和VHDL语言输入法设计简单逻辑电路 的方法。 实验内容:

1)采用原理图输入方法设计4位格雷码/二进制码变换电路。 2)采用VHDL语言输入方法设计格雷码/二进制码变换电路。

实验原理

Bi Gi Bi B(i 1) Gi

VHDL 语言的基本结构 例1

Library IEEE; use IEEE.std_logic_1164.all;

entity aaaa is port(a,b: IN std_logic; y: out std_logic); end aaaa; architecture rhl of aaaa IS begin y<=a nand b; end rhl;

B3 G 3 B 2 B3 G 2 B1 B 2 G1 B 0 B1 G 0

Gi Bi Gi B(i 1) Bi

G 3 B3 G 2 B3 B 2 G1 B 2 B1 G 0 B1 B 0

格雷码变换电路

XOR

g0

INPUT VCC

条件句中的‚=>”不是操作符,只相当于‚THEN”作用。

case-when 语句 例3 library ieee;

use ieee.std_logic_1164.all; entity and_gate is port(a:in std_logic_vector(1 downto 0); y:out std_logic); end and_gate; architecture rhl of and_gate is begin 进程中a为敏感信号,当a的值发生 process(a) 变化时执行case中的顺序语句 begin case a is 当a0为0,a1为0时, when"00"=>y<='0'; 输出y为0 when"01"=>y<='0'; when"10"=>y<='0'; 其他情况为 when"11"=>y<='1'; 不定状态 when others=>y<='X'; end case; 结束case语句 end process; e入 端a0和a1

并行乘法器-南京理工大学紫金学院vhdl实验报告-eda

EDA技术与应用实验报告实验名称:并行乘法器姓名:学号:班级:通信时间:2013理工大学紫金学院电光系一、实验目的1、学习包集和元件例化语句的使用。

2、学习FLU(全加器单元)电路的设计。

3、学习并行乘法电路的设计。

二、实验原理并行乘法器的电路原理图如下图所示,主要由全加器和与门构成。

并行乘法器原理图三、实验容1、and_2library ieee;use ieee.std_logic_1164.all;entity and_2 isport (a,b:in std_logic;y:out std_logic);end and_2;architecture and_2 of and_2 isbeginy <= a and b;end and_2;2、faulibrary ieee;use ieee.std_logic_1164.all;entity fau isport (a,b,cin:in std_logic;s,cout:out std_logic);end fau;architecture fau of fau isbegins <= a xor b xor cin;cout <= (a and b)or(a and cin)or(b and cin);end fau;3、top_rowlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity top_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end top_row;architecture structural of top_row isbeginU1: component and_2 port map(a,b(3),sout(2));U2: component and_2 port map(a,b(2),sout(1));U3: component and_2 port map(a,b(1),sout(0));U4: component and_2 port map(a,b(0),p);cout(2) <= '0';cout(1) <= '0';cout(0) <= '0';end structural;4、mid_rowlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity mid_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sin,cin:in std_logic_vector(2 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end mid_row;architecture structural of mid_row issignal and_out:std_logic_vector(2 downto 0);beginU1: component and_2 port map(a,b(3),sout(2));U2: component and_2 port map(a,b(2),and_out(2));U3: component and_2 port map(a,b(1),and_out(1));U4: component and_2 port map(a,b(0),and_out(0));U5: component fau port map(sin(2),cin(2),and_out(2), sout(1), cout(2));U6: component fau port map(sin(1),cin(1),and_out(1), sout(0), cout(1));U7: component fau port map(sin(0),cin(0),and_out(0), p, cout(0));end structural;5、lower_rowlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity lower_row isport (sin,cin:in std_logic_vector(2 downto 0);p:out std_logic_vector(3 downto 0));end lower_row;architecture structural of lower_row issignal local:std_logic_vector(2 downto 0);beginlocal(0) <= '0';U1: component fau port map(sin(0),cin(0),local(0), p(0),local(1));U2: component fau port map(sin(1),cin(1),local(1), p(1),local(2));U3: component fau port map(sin(2),cin(2),local(2), p(2),p(3));end structural;6、my_componentslibrary ieee;use ieee.std_logic_1164.all;package my_components iscomponent and_2 isport (a,b:in std_logic; y:out std_logic);end component;component fau isport (a,b,cin:in std_logic; s,cout:out std_logic); end component;component top_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end component;component mid_row isport (a:in std_logic;b:in std_logic_vector(3 downto 0);sin,cin:in std_logic_vector(2 downto 0);sout,cout:out std_logic_vector(2 downto 0);p:out std_logic);end component;component lower_row isport (sin,cin:in std_logic_vector(2 downto 0);p:out std_logic_vector(3 downto 0));end component;end my_components;7、multiplierlibrary ieee;use ieee.std_logic_1164.all;use work.my_components.all;entity multiplier isport (a,b:in std_logic_vector(3 downto 0);prod:out std_logic_vector(7 downto 0));end multiplier;architecture structural of multiplier istype matrix is array (0 to 3)ofstd_logic_vector (2 downto 0);signal s,c:matrix;beginU1: component top_row port map (a(0),b,s(0),c(0),prod(0));U2: component mid_row port map (a(1),b,s(0),c(0),s(1), c(1),prod(1));U3: component mid_row port map (a(2),b,s(1),c(1),s(2), c(2),prod(2));U4: component mid_row port map (a(3),b,s(2),c(2),s(3), c(3),prod(3));U5: component lower_row port map(s(3),c(3),prod(7 downto 4));end structural;8、仿真9、把multiplier代码改为百位、十位、个位输出代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use work.my_components.all;entity multiplier isport (a,b:in std_logic_vector(3 downto 0);hun,ten,one:out std_logic_vector(3 downto 0)); end multiplier;architecture structural of multiplier istype matrix is array (0 to 3)ofstd_logic_vector (2 downto 0);signal s,c:matrix;signal p:std_logic_vector(7 downto 0);beginU1: component top_row port map (a(0),b,s(0),c(0),p(0));U2: component mid_row port map (a(1),b,s(0),c(0),s(1), c(1),p(1));U3: component mid_row port map (a(2),b,s(1),c(1),s(2), c(2),p(2));U4: component mid_row port map (a(3),b,s(2),c(2),s(3), c(3),p(3));U5: component lower_row port map(s(3),c(3),p(7 downto 4));process(p)variable temp:std_logic_vector(7 downto 0);beginif p >"1100_0111" thenhun <="0010";temp:=p-"1100_1000";elsif p>"0110_0011" thenhun <="0001";temp:=p-"0110_0100";elsehun <="0000";temp:=p;end if;if temp>"0101_1001" thenten <="1001";temp:=temp-"0101_1010"; elsif temp>"0100_1111" then ten <="1000";temp:=temp-"1010_0000"; elsif temp>"0100_0101" then ten <="0111";temp:=temp-"0100_0110"; elsif temp>"0011_1011" then ten <="0110";temp:=temp-"0011_1100"; elsif temp>"0011_0001" then ten <="0101";temp:=temp-"0011_0010"; elsif temp>"0010_0111" then ten <="0100";temp:=temp-"0010_1000"; elsif temp>"0001_1101" then ten <="0011";temp:=temp-"0001_1110"; elsif temp>"0001_0011" then ten <="0010";temp:=temp-"0001_0100"; elsif temp>"0000_1001" then ten <="0001";temp:=temp-"0000_1010"; elseten <="0000";temp:=temp;end if;one <=temp(3 downto 0);end process;end structural;四、小结与体会通过本次实验,我对包集和元件例化语句的使用有了更深刻的了解。

二进制与格雷码转换

在精确定位控制系统中,为了提高控制精度,准确测量控制对象的位置是十分重要的。

目前,检测位置的办法有两种:其一是使用位置传感器,测量到的位移量由变送器经A/D转换成数字量送至系统进行进一步处理。

此方法精度高,但在多路、长距离位置监控系统中,由于其成本昂贵,安装困难,因此并不实用;其二是采用光电轴角编码器进行精确位置控制。

光电轴角编码器根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式三种。

而绝对式编码器是直接输出数字量的传感器,它是利用自然二进制或循环二进制(格雷码)方式进行光电转换的,编码的设计一般是采用自然二进制码、循环二进制码、二进制补码等。

特点是不要计数器,在转轴的任意位置都可读出一个固定的与位置相对应的数字码;抗干扰能力强,没用累积误差;电源切断后位置信息不会丢失,但分辨率是由二进制的位数决定的,根据不同的精度要求,可以选择不同的分辨率即位数。

目前有10位、11位、12位、13位、14位或更高位等多种。

其中采用循环二进制编码的绝对式编码器,其输出信号是一种数字排序,不是权重码,每一位没有确定的大小,不能直接进行比较大小和算术运算,也不能直接转换成其他信号,要经过一次码变换,变成自然二进制码,在由上位机读取以实现相应的控制。

而在码制变换中有不同的处理方式,本文着重介绍二进制格雷码与自然二进制码的互换。

一、格雷码(又叫循环二进制码或反射二进制码)介绍在数字系统中只能识别0和1,各种数据要转换为二进制代码才能进行处理,格雷码是一种无权码,采用绝对编码方式,典型格雷码是一种具有反射特性和循环特性的单步自补码,它的循环、单步特性消除了随机取数时出现重大误差的可能,它的反射、自补特性使得求反非常方便。

格雷码属于可靠性编码,是一种错误最小化的编码方式,因为,自然二进制码可以直接由数/模转换器转换成模拟信号,但某些情况,例如从十进制的3转换成4时二进制码的每一位都要变,使数字电路产生很大的尖峰电流脉冲。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA技术与应用

实验报告

实验名称:格雷码、二进制转换电路

姓名:

学号:

班级:通信

时间:2013

南京理工大学紫金学院电光系

实验目的

1)学习用VHDL代码描述组合逻辑电路的方法。

2)掌握whe n…else…和gen erate 并行语句的使用。

实验原理

1、格雷码、二进制码转换理论分析

4位格雷码二进制转换的真值表如图1。

G5G1Gi G*Bi Bl RO

fl Q Q U Q V Q0

0V D丄b a01

€0110Q i0

01e0a*1

打1100100

1110101

亦1G10110

416011ft

110]a00

t10丄1001

11111Q10

111u1a I]

10101140

10111101

10611110

i4001i11

图14

由真值表得到的表达式如下:

B3 G3

B2 B3 G2

B1 B2 G1

BO B1 G0

对于n位二进制码转换为格雷码的码转换电路,转换表达式如下:

g n a n

g i a i 1 a i

2、GENERIC GENERAT语句

a、GENERIC

GENERIC被称为参数传递映射语句,它描述响应的元件类属参数间的衔接和传送方式。

参数传递语句用于设计从外部端口改变原件内部参数或结构规模的元件,也可称其为类书元件。

该语句在改变电路结构或元件硬件升级方面显得尤为便捷。

其语句格式为:

generic map(param.list)port map(port list);

例:generic(n:integer:=7);

该语句定义了参数N为整数,且赋值为7。

b、GENERAT语句

电路某部分由同类元件构成,这类同类元件叫做规则结构,如:ROM,RA,M 移位寄存器

等规则结构可以用生成语句来描述。

生成语句可以用for_generate 语句描述。

其书写格式如下:

标号:for 循环变量in 离散范围generate

并行处理语句;

end generate 标号;

其中,标号是for_generate 语句的唯一标识符,是可选项;循环变量的值在每一次循环中都发生变化;离散范围用来指定变量循环的取值范围,循环变量实际上规定了循环的次数;循环变量每去一个只就执行一次并行语句。

该语句和for_loop 语句很类似,但是二者也有一定的区别。

For_generate 语句中执行的语句为并行语句,而for_loop 语句中执行的语句为顺序语句。

三、实验内容

1、建立工程、输入代码先建立工程,工程命名为“ b_to_g ”, 顶层文件名为“ b_to_g ”。

选择“ File->New ”,在弹出的窗口中选择“ VHDL File ”建立“ VHDL文件。

在新建的VHDL文件中输入格雷码、二进制码转换的VHDL代码。

将文件保存。

代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity b_to_g is

generic(n:integer:=7);

port(b:in std_logic_vector(n downto 0); g:buffer std_logic_vector(n downto 0)); end;

architecture rhg of b_to_g is

begin

g(n)<=b(n);

b1:for i in 0 to n-1 generate

g(i)<=b(i+1) xor b(i);

end generate b1;

end;

2、编译仿真

对当前文件进行编译,编译通过以后建立仿真波形文件,保存为" b_to_g.vwf ”。

为波形文件添加结点。

将“End time ”设置为100卩s。

将输入输出编组,并为输入信号赋值,其中“Start Value ” 为

“ 00000000”,“Count every ” 设置为 5 卩s。

如下图:

注意:“Count every ”值一定要比“ End time ”值小,且“ Count every ”值最好不要设置太小(如10ns),避免在时序仿真是由于延时造成结果不正确。

“ Count every ”值和

“ End

time ”值共同决定了输入信号值的数目。

注意:每次仿真时最好从“ Simulator Tool ”中导入要仿真的文件,而不是直接点击工具栏上的按钮,尤其是当工程中存在多个仿真文件时。

3、管脚配置

利用实验箱的模式5来验证设计电路的正确性。

用键1~键8表示输入管脚g0~g7,发光二极管D1~D8表示输出管脚b0~b7。

选择“ Assignment宀Assignment Editor ”弹出管脚配置图,在“ Location ”一栏中填

入相应器件的管脚。

如下图。

将未配置的管脚设置为高阻态。

注意:总线“ b”和总线“ g”不需要配置管脚。

注意:配置好管脚后一定要记得编译。

4、下载

将文件下载到实验箱,对实验箱进行操作,将键1~键8按钮设置为不同的电平,观察

D1~D8发光二极管的情况。

四、小结与体会

通过这次实验,我对理论课上老师所讲的gen erate并行语句有了更深一步的了解。

本次实验是我们的第二次实验,但是是第一次在Quartus II 软件上编写代码。

我掌握whe n…else…和gen erate并行语句的使用,并利用gen erate并行语句做了了8位二进制码/格雷码转换电路,且利用实验箱验证了所设计电路的正确性。