FM3130 中文资料 RTC

TPA2013D1_1资料

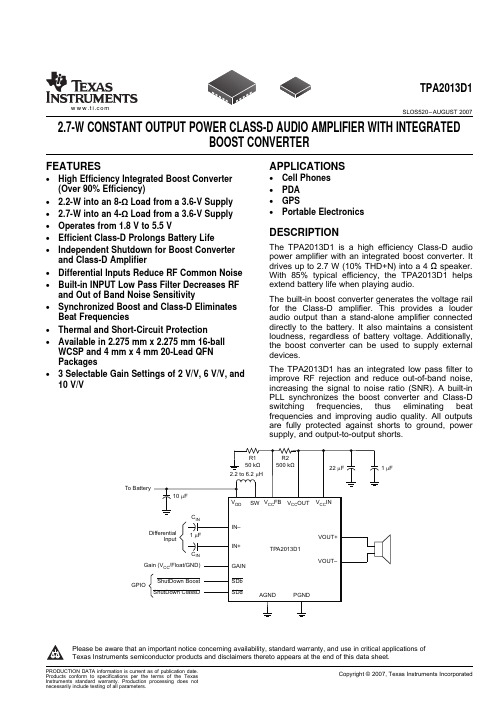

FEATURESAPPLICATIONSDESCRIPTIONGPIO2.7-W CONSTANT OUTPUT POWER CLASS-D AUDIO AMPLIFIER WITH INTEGRATEDBOOST CONVERTER•Cell Phones •High Efficiency Integrated Boost Converter (Over 90%Efficiency)•PDA •GPS• 2.2-W into an 8-ΩLoad from a 3.6-V Supply •Portable Electronics• 2.7-W into an 4-ΩLoad from a 3.6-V Supply •Operates from 1.8V to 5.5V•Efficient Class-D Prolongs Battery LifeThe TPA2013D1is a high efficiency Class-D audio •Independent Shutdown for Boost Converter power amplifier with an integrated boost converter.It and Class-D Amplifierdrives up to 2.7W (10%THD+N)into a 4Ωspeaker.•Differential Inputs Reduce RF Common Noise With 85%typical efficiency,the TPA2013D1helps extend battery life when playing audio.•Built-in INPUT Low Pass Filter Decreases RF and Out of Band Noise SensitivityThe built-in boost converter generates the voltage rail •Synchronized Boost and Class-D Eliminates for the Class-D amplifier.This provides a louder Beat Frequenciesaudio output than a stand-alone amplifier connected directly to the battery.It also maintains a consistent •Thermal and Short-Circuit Protectionloudness,regardless of battery voltage.Additionally,•Available in 2.275mm x 2.275mm 16-ball the boost converter can be used to supply external WCSP and 4mm x 4mm 20-Lead QFN devices.PackagesThe TPA2013D1has an integrated low pass filter to •3Selectable Gain Settings of 2V/V,6V/V,and improve RF rejection and reduce out-of-band noise,10V/Vincreasing the signal to noise ratio (SNR).A built-in PLL synchronizes the boost converter and Class-D switching frequencies,thus eliminating beat frequencies and improving audio quality.All outputs are fully protected against shorts to ground,power supply,and output-to-output shorts.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright ©2007,Texas Instruments IncorporatedProducts conform to specifications per the terms of the Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.DEVICE INFORMATIONV CC FBSWSWVCCOUTVCCINSDbIN+IN–PGNDPGNDSDdV DDPGNDRGP(QFN) Package(Top View)TPA2013D1RGPGAINAGND VOUT–VOUT–VOUT+VOUT+VOUT+YZH(WCSP) Package(Top View)TPA2013D1YZHTPA2013D1SLOS520–AUGUST2007These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.BOOST CONVERTER TERMINAL FUNCTIONSTERMINALI/O DESCRIPTIONNAME QFN WCSPIN+8D2I Positive audio inputIN–7D3I Negative audio inputVOUT+13,14,15B1O Positive audio outputVOUT–11,12C1O Negative audio outputSDb6D4I Shutdown terminal for the Boost ConverterSDd5C3I Shutdown terminal for the Class D AmplifierSW18,19A3–Boost and rectifying switch inputV CC OUT17A2–Boost converter output-connect to V CC INGAIN3B2I Gain selection pinV CC IN16A1–Class-D audio power amplifier voltage supply-connect to V CC OUTV CC FB2B3I Voltage feedbackV DD1B4–Supply voltageAGND4C4–Analog ground-connect all GND pins togetherPGND9,10,20D1,C2,A4–Power ground-connect all GND pins togetherThermal Solder the thermal pad on the bottom of the QFN package to the GND plane of the PCB.Die Pad N/A PPad It is required for mechanical stability and will enhance thermal performance.2Submit Documentation Feedback Copyright©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPA2013D1AGNDIN+IN–SDb V DDSWV OUTCC V FBCC V INCC VOUT+VOUT–PGNDSDdGAINTPA2013D1SLOS520–AUGUST 2007Functional Block DiagramTable 1.BOOST CONVERTER MODE CONDITIONCASE OUTPUT CURRENTMODE OF OPERATIONV DD <V CC Low Continuous (fixed frequency)V DD <V CC High Continuous (fixed frequency)V DD ≥V CC Low Discontinuous (variable frequency)V DD ≥V CCHighDiscontinuous (variable frequency)Table 2.DEVICE CONFIGURATIONBoost Class D SDb SDd CommentsConverter Amplifier low low OFF OFF Device is in shutdown mode Iq ≤1μABoost converter is off.Class-D Audio Power Amplifier (APA)can be driven by an low high OFF ON external pass transistor connected to the battery.high low ON OFF Class-D APA is off.Boost Converter is on and can be used to drive an external device.Boost converter and Class-D APA are on.Normal operation.Boost converter can be highhighONONused to drive an external device in parallel to the Class-D APA within the limits of the boost converter output current.Copyright ©2007,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):TPA2013D1ABSOLUTE MAXIMUM RATINGSDISSIPATION RATINGSAVAILABLE OPTIONSRECOMMENDED OPERATING CONDITIONSTPA2013D1SLOS520–AUGUST 2007over operating free-air temperature range (unless otherwise noted)(1)VALUE UNIT V DD Supply voltage–0.3to 6V V I Input voltage,Vi:SDb,SDd,IN+,IN–,V CC FB –0.3to V DD +0.3V Continuous total power dissipation See Dissipation Rating TableT A Operating free-air temperature range –40to 85°C T J Operating junction temperature range –40to 150°C T stg Storage temperature range–65to 150°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratings only,and functional operations of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.PACKAGE T A ≤25°C DERATING FACTOR (1)T A =70°C T A =85°C 16ball WCSP 1.5W 12.4mW/°C 1W 0.8W 20pin QFN2.5W20.1mW/°C1.6W1.3W(1)Derating factor measured with JEDEC High K board.T APACKAGED DEVICES (1)PART NUMBER SYMBOL 16-ball,2.275mm ×2.275mm WCSPTPA2013D1YZH BTH (±0.05mm tolerance)–40°C TO 85°C 20-pin,4mm ×4mm QFNTPA2013D1RGP (2)BTI(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI website at .(2)The RGP package is only available taped and reeled.To order,add suffix R to the end of the part number for a reel of 3000(e.g.,TPA2013D1RGPR).MINMAX UNIT V DD Supply voltage 1.8 5.5V V IH High-level input voltage SDb,SDd 1.3V V IL Low-level input voltage SDb,SDd0.35V |I IH |High-level input current SDb =SDd =5.8V,V DD =5.5V,V CC =5.5V 1μA |I IL |Low-level input current SDb =SDd =-0.3V,V DD =5.5V,V CC =5.5V20μA T AOperating free-air temperature–4085°C4Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPA2013D1DC CHARACTERISTICSTPA2013D1 SLOS520–AUGUST2007T A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNITClass-D audio power amplifierV CC3 5.5V voltage supply range,V CC INSDd=SDb=0V,V DD=1.8V,R L=8Ω0.04 1.5SDd=SDb=0V,V DD=3.6V,R L=8Ω0.04 1.5SDd=SDb=0V,V DD=4.5V,R L=8Ω0.02 1.5I SD Shutdown quiescent currentμASDd=SDb=0.35V,V DD=1.8V,R L=8Ω0.03 1.5SDd=SDb=0.35V,V DD=3.6V,R L=8Ω0.03 1.5SDd=SDb=0.35V,V DD=4.5V,R L=8Ω0.02 1.5Boost converter quiescent SDd=0V,SDb=1.3V,V DD=3.6V,V CC=5.5V,No 1.3I DD mAcurrent Load,No FilterV DD=3.6,V cc=5.5V,No Load,No Filter 4.36 Class D amplifier quiescentI CC mAcurrent VDD=4.5,V cc=5.5V,No Load,No Filter 3.66SDd=SDb=1.3V,V DD=3.6,V cc=5.5V,No Load,No16.523 Boost converter and audio FilterI DD power amplifier quiescent mASDd=SDb=1.3V,V DD=4.5,V cc=5.5V,No Load,No1118.5 current,Class D(1)FilterBoost converter switching500600700kHzfrequencyfClass D switching frequency250300350kHz UVLO Under voltage lockout 1.7V Gain input low level Gain=2V/V(6dB)00.35V GAIN Gain input mid level Gain=6V/V(15.5dB)(floating input)0.70.81V Gain input high level Gain=10V/V(20dB) 1.35VClass D Power on reset ON 2.8V POR Dthreshold(1)I DD is calculated using I DD=(I CC×V CC)/(V DD×η),where I CC is the class D amplifier quiescent current;η=40%,which is the boostconverter efficiency when class D amplifier has no load.To achieve the minimal40%η,it is recommended to use the suggested inductors in table4and to follow the layout guidelines.Copyright©2007,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):TPA2013D1BOOST CONVERTER DC CHARACTERISTICSCLASS D AMPLIFIER DC CHARACTERISTICSAC CHARACTERISTICSTPA2013D1SLOS520–AUGUST 2007T A =25°C (unless otherwise noted)PARAMETERTEST CONDITIONSMIN TYPMAX UNIT V CC Output voltage range 3.0 5.5V V FB Feedback voltage490500510mV I OL Output current limit,Boost_max 130015001700mA R ON_PB PMOS switch resistance 220m ΩR ON_NBNMOS resistance 170m ΩNo Load,1.8V <V DD <5.2Line regulation 3mV/V V,V CC =5.5VV DD =3.6V,0<I L <500mA,Load regulation30mV/A V CC =5.5VI LStart up current limit,Boost0.4×I BoostmAT A =25°C (unless otherwise noted)PARAMETERTEST CONDITIONSMIN TYPMAX UNITV in =±100mV,V DD =1.8V,V CC =3V,R L =8Ω0.5 2.2CMRInput common mode rangeV in =±100mV,V DD =2.5V,V CC =3.6V,R L =8Ω0.5 2.8V V in =±100mV,V DD =3.6V,V CC =5.5V,R L =8Ω0.54.7R L =8Ω,V icm =0.5and V icm =V CC –0.8,differential CMRRInput common mode rejection–75dB inputs shortedV CC =3.6V,Av =2V/V,IN+=IN–=V ref ,R L =8Ω16V CC =3.6V,Av =6V/V,IN+=IN–=V ref ,R L =8Ω16Output offset voltage V OOmVClass-DV CC =3.6V,Av =10V/V,IN+=IN–=V ref ,R L =8Ω16V CC =5.5V,Av =2V/V,IN+=IN–=V ref ,R L =8Ω16Gain =2V/V (6dB)32R inInput ImpedanceGain =6V/V (15.5dB)15k ΩGain =10V/V (20dB)9.5OUTP High-side FET On-state 0.36series resistanceR DS(on)OUTP Low-side FET On-state 0.36series resistanceI OUTx =–300mA;V CC =3.6VΩOUTN High-side FET On-state 0.36series resistanceR DS(on)OUTN Low-side FET On-state 0.36series resistance Low GainGAIN ≤0.35V 1.82 2.2V/V A VMid Gain GAIN =0.8V 5.76 6.3V/V High GainGAIN ≥1.35V9.51010.5V/V T A =25°C,V DD =3.6V,R L =8Ω,L =4.7μH (unless otherwise noted)PARAMETERTEST CONDITIONSMINTYP MAXUNIT t START Start up time1.8V ≤V DD ≤5.5V,C IN ≤1μF7.5msTHD+N =1%,V CC =5.5V,V DD =3.6V,85%R L =8Ω,Pout =1.7W,C boost =47μF ηEfficiencyTHD+N =1%,V CC =5.5V,V DD =4.2V,87.5%R L =8Ω,Pout =1.7W Thermal ShutdownThreshold150°C6Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPA2013D1CLASS D AMPLIFIER AC CHARACTERISTICSTPA2013D1TPA2013D1SLOS520–AUGUST 2007T A =25°C,V DD =3.6V,R L =8Ω,L =4.7μH (unless otherwise noted)PARAMETERTEST CONDITIONSMINTYP MAXUNIT KSVR Output referred power supply V DD =3.6V,V CC =5.5V,200mV PP ripple,f =217–95dBClass-D rejection ratioHzf =1kHz,P o =1.7W,V CC =5.5V1%f =1kHz,P o =1.2W,V CC =4.5V 1%THD+N Total harmonic distortion +noiseClass-D f =1kHz,P o =2.2W,V CC =5.5V 10%f =1kHz,P o =1W,V CC =5.5V0.1%VnOutput integrated noise floor Av =6dB (2V/V)31Class-DμVrmsOutput integrated noise floor Av =6dB (2V/V)23A-weightedTHD+N =10%,V CC =5.5V,V DD =3.6V ,R L =8Ω 2.2THD+N =1%,V CC =5.5V,V DD =3.6V ,R L =8Ω1.7THD+N =1%,V CC =4.5V,V DD =3.6V ,R L =8Ω 1.2P OMaximum output powerW THD+N =10%,V CC =5.5V,V DD =3.6V ,R L =4Ω 2.7THD+N =1%,V CC =5.5V,V DD =3.6V ,R L =4Ω 2.2THD+N =1%,V CC =4.5V,V DD =3.6V ,R L =4Ω1.9TEST SET-UP FOR GRAPHS(1)C I was shorted for any common-mode input voltage measurement.All other measurements were taken with a 1-μF C I (unless otherwise noted).(2)A 33-μH inductor was placed in series with the load resistor to emulate a small speaker for efficiency measurements.(3)The 30-kHz low-pass filter is required,even if the analyzer has an internal low-pass filter.An RC low-pass filter (100Ω,47-nF)is used on each output for the data sheet graphs.(4)L =4.7μH is used for the boost converter unless otherwise noted.Copyright ©2007,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):TPA2013D1TYPICAL CHARACTERISTICSP O − Output Power − W0204060801000.00.51.01.5E f f i c i e n c y − %G001P O − Output Power − W0204060801000.00.51.01.52.0E f f i c i e n c y − %G002P O − Output Power − W0.00.10.20.30.40.50.60.00.51.01.5P D − P o w e r D i s s i p a t i o n − WG003P O − Output Power − W0.00.10.20.30.40.50.60.00.5 1.01.52.0P D − P o w e r D i s s i p a t i o n − WG004P O − Output Power − W0.00.20.40.60.81.00.00.51.01.5I D D − S u p p l y C u r r e n t − AG005P O − Output Power − W0.00.20.40.60.81.01.20.00.5 1.01.52.0I D D − S u p p l y C u r r e n t − AG006TPA2013D1SLOS520–AUGUST 2007EFFICIENCYEFFICIENCYvsvsOUTPUT POWEROUTPUT POWERFigure 1.Figure 2.POWER DISSIPATIONPOWER DISSIPATIONvsvsOUTPUT POWEROUTPUT POWERFigure 3.Figure 4.SUPPLY CURRENTSUPPLY CURRENTvsvsOUTPUT POWEROUTPUT POWERFigure 5.Figure 6.8Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPA2013D1V DD − Supply Voltage − V 0.00.51.01.52.02.51.82.2 2.63.0 3.4 3.84.2 4.6P O − O u t p u t P o w e r − WG007V DD − Supply Voltage − V0.00.51.01.52.02.51.82.22.63.03.43.84.24.65.05.4P O − O u t p u tP o w e r − WG008V DD − Supply Voltage − V 0.00.51.01.52.02.51.82.2 2.63.03.43.84.24.6P O − O u t p u t P o w e r − WG009V DD − Supply Voltage − V0.00.51.01.52.02.51.82.22.63.03.43.84.24.65.05.4P O − O u t p u tP o w e r − WG010R L − Load Resistance − Ω0.00.51.01.52.02.53.048121620242832P O − O u t p u t P o w e r − WG011R L − Load Resistance − Ω0.00.51.01.52.02.53.048121620242832P O − O u t p u t P o w e r − WG012TPA2013D1SLOS520–AUGUST 2007TYPICAL CHARACTERISTICS (continued)OUTPUT POWEROUTPUT POWERvsvsSUPPLY VOLTAGESUPPLY VOLTAGEFigure 7.Figure 8.OUTPUT POWEROUTPUT POWERvsvsSUPPLY VOLTAGESUPPLY VOLTAGEFigure 9.Figure 10.OUTPUT POWEROUTPUT POWERvs vs LOADLOADFigure 11.Figure 12.Copyright ©2007,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):TPA2013D1P O − Output Power − W0.010.113G0130.010.113P O− Output Power − WG014P O − Output Power − W0.010.115G015T H D +N − %f − Frequency − Hz201001k20k0.10.010.001G016110k T H D +N − %10f − Frequency − Hz0.10.010.001G0171201001k20k10kT H D +N − %10201001k20k10k f − Frequency − Hz0.10.010.001G0181T H D +N − %10TPA2013D1SLOS520–AUGUST 2007TYPICAL CHARACTERISTICS (continued)TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsOUTPUT POWEROUTPUT POWERFigure 13.Figure 14.TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsOUTPUT POWERFREQUENCYFigure 15.Figure 16.TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsFREQUENCYFREQUENCYFigure 17.Figure 18.10Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPA2013D1201001k20k10kf − Frequency − Hz0.10.010.001G0191T H D +N − %10201001k20k10k f − Frequency − Hz0.10.010.001G0201T H D +N − %10201001k20k10kf − Frequency − Hz0.10.010.001G0211T H D +N − %10−120−100−80−60−40−200 f − Frequency − HzP S R R − d BG022201001k20k10k −120−100−80−60−40−200 f − Frequency − HzP S R R − d BG023201001k20k10k−120−100−80−60−40−200f − Frequency − HzC M R R − dBG024201001k20k10k SLOS520–AUGUST 2007TYPICAL CHARACTERISTICS (continued)TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsFREQUENCYFREQUENCYFigure 19.Figure 20.TOTAL HARMONIC DISTORTION +NOISEPOWER SUPPLY REJECTION RATIOvsvsFREQUENCYFREQUENCYFigure 21.Figure 22.POWER SUPPLY REJECTION RATIOCOMMON-MODE REJECTION RATIOvsvsFREQUENCYFREQUENCYFigure 23.Figure 24.−90−80−70−60−50−40−30−20−100 f − Frequency − HzC M R R − d BG025201001k20k10k50556065707580859095100I O − Output Current − A0.010.11B o o s t E f f i c i e n c y − %G02650556065707580859095100I O − Output Current − A0.010.11B o o s t E f f i c i e n c y − %G027V DD − Supply Voltage − V50607080901001.82.22.63.03.43.84.2B o o s t E f f i c i e n c y − %G028V DD − Supply Voltage (Boost) − V0.00.20.40.60.81.01.21.41.82.2 2.63.0 3.4 3.84.2I O M − M a x . C o n t i n u o u s O u t p u t C u r r e n t − AG029t − Time − ms02468101214161820V − V o l t a g e − VG030SLOS520–AUGUST 2007TYPICAL CHARACTERISTICS (continued)COMMON-MODE REJECTION RATIOBOOST EFFICIENCYvsvsFREQUENCYOUTPUT CURRENTFigure 25.Figure 26.BOOST EFFICIENCYBOOST EFFICIENCYvsvsOUTPUT CURRENTSUPPLY VOLTAGEFigure 27.Figure 28.MAXIMUM CONTINUOUS OUTPUT CURRENTvsSUPPLY VOLTAGE (BOOST)Start-Up TimeFigure 29.Figure 30.APPLICATION INFORMATION FULLY DIFFERENTIAL AMPLIFIERAdvantages of Fully Differential AmplifiersBOOST CONVERTERBoost Terms SLOS520–AUGUST2007The TPA2013D1is a fully differential amplifier with differential inputs and outputs.The fully differential amplifier consists of a differential amplifier with common-mode feedback.The differential amplifier ensures that the amplifier outputs a differential voltage on the output that is equal to the differential input times the gain.The common-mode feedback ensures that the common-mode voltage at the output is biased around V CC/2regardless of the common-mode voltage at the input.The fully differential TPA2013D1can still be used with a single-ended input;however,the TPA2013D1should be used with differential inputs when in a noisy environment,like a wireless handset,to ensure maximum noise rejection.•Input-coupling capacitors not required:–The fully differential amplifier allows the inputs to be biased at voltage other than mid-supply.The inputs of the TPA2013D1can be biased anywhere within the common mode input voltage range listed in the Recommended Operating Conditions table.If the inputs are biased outside of that range,input-coupling capacitors are required.•Midsupply bypass capacitor,C(BYPASS),not required:–The fully differential amplifier does not require a bypass capacitor.Any shift in the midsupply affects both positive and negative channels equally and cancels at the differential output.•Better RF-immunity:–GSM handsets save power by turning on and shutting off the RF transmitter at a rate of217Hz.The transmitted signal is picked-up on input and output traces.The fully differential amplifier cancels the signal better than the typical audio amplifier.The TPA2013D1consists of a boost converter and a Class-D amplifier.The boost converter takes a low supply voltage,V DD,and increases it to a higher output voltage,V CC.V CC is the power supply for the Class-D amplifier. The two main passive components necessary for the boost converter are the boost inductor and the boost capacitor.The boost inductor stores current,and the boost capacitor stores charge.As the Class-D amplifier depletes the charge in the boost capacitor,the boost inductor charges it back up with the stored current.The cycle of charge/discharge occurs at a frequency of f boost.The TPA2013D1allows a range of V CC voltages,including setting V CC lower than V DD.The following is a list of terms and definitions used in the boost equations found later in this document.C Minimum boost capacitance required for a given ripple voltage on V CC.L Boost inductorf boost Switching frequency of the boost converter.I CC Current pulled by the Class-D amplifier from the boost converter.I L Average current through the boost inductor.R1and R2Resistors used to set the boost voltage.V CC Boost voltage.Generated by the boost converter.Voltage supply for the Class-Damplifier.V DD Supply voltage to the IC.ΔI L Ripple current through the inductor.ΔV Ripple voltage on V CC due to capacitance.SETTING THE BOOST VOLTAGECC 0.5(R1+R2)V =R1´æöç÷èø(1)INDUCTOR SELECTION CCL CC DD V I =I V 0.8æö´ç÷´èø(2)DDCC DD L CC V(V V )L =I f V boost ´-D ´´(3)SLOS520–AUGUST 2007Use Equation 1to determine the value of R1for a given V CC .The maximum recommended value for V CC is 5.5V.The typical value of the V CC FB pin is 500mV.The current through the resistor divider should be about 100times greater than the current into the V CC FB pin,typically 0.01μA.Based on those two values,the recommended value of R2is 500k Ω.V CC must be greater than 3V and less than or equal to 5.5V.SURFACE MOUNT INDUCTORSWorking inductance decreases as inductor current increases.If the drop in working inductance is severe enough,it may cause the boost converter to become unstable,or cause the TPA2013D1to reach its current limit at a lower output power than expected.Inductor vendors specify currents at which inductor values decrease by a specific percentage.This can vary by 10%to 35%.Inductance is also affected by dc current and temperature.TPA2013D1INDUCTOR EQUATIONSInductor current rating is determined by the requirements of the load.The inductance is determined by two factors:the minimum value required for stability and the maximum ripple current permitted in the e Equation 2to determine the required current rating.Equation 2shows the approximate relationship between the average inductor current,I L ,to the load current,load voltage,and input voltage (I CC ,V CC ,and V DD ,respectively).Insert I CC ,V CC ,and V DD into Equation 2to solve for I L .The inductor must maintain at least 90%of its initial inductance value at this current.The minimum working inductance is 2.2μH.A lower value may cause instability.Ripple current,ΔI L ,is peak-to-peak variation in inductor current.Smaller ripple current reduces core losses in theinductor as well as the potential for e Equation 3to determine the value of the inductor,L.Equation 3shows the relationship between inductance L,V DD ,V CC ,the switching frequency,f boost ,and ΔI L .Insert the maximum acceptable ripple current into Equation 3to solve for L.ΔI L is inversely proportional to L.Minimize ΔI L as much as is necessary for a specific application.Increase theinductance to reduce the ripple current.Note that making the inductance too large will prevent the boost converter from responding to fast load changes properly.Typical inductor values for the TPA2013D1are 4.7μH to 6.8μH.Select an inductor with a small dc resistance,DCR.DCR reduces the output power due to the voltage drop across the inductor.SLOS520–AUGUST2007 CAPACITOR SELECTIONSURFACE MOUNT CAPACITORSTemperature and applied dc voltage influence the actual capacitance of high-K materials.Table3shows the relationship between the different types of high-K materials and their associated tolerances, temperature coefficients,and temperature ranges.Notice that a capacitor made with X5R material can lose up to 15%of its capacitance within its working temperature range.High-K material is very sensitive to applied dc voltage.X5R capacitors can have losses ranging from15to45% of their initial capacitance with only half of their dc rated voltage applied.For example,if5Vdc is applied to a10 V,1μF X5R capacitor,the measured capacitance at that point may show0.85μF,0.55μF,or somewhere in between.Y5V capacitors have losses that can reach or exceed50%to75%of their rated value.In an application,the working capacitance of components made with high-K materials is generally much lower than nominal capacitance.A worst case result with a typical X5R material might be–10%tolerance,–15% temperature effect,and–45%dc voltage effect at50%of the rated voltage.This particular case would result in a working capacitance of42%(0.9×0.85×0.55)of the nominal value.Select high-K ceramic capacitors according to the following rules:e capacitors made of materials with temperature coefficients of X5R,X7R,or better.e capacitors with dc voltage ratings of at least twice the application e minimum10V capacitorsfor the TPA2013D1.3.Choose a capacitance value at least twice the nominal value calculated for the application.Multiply thenominal value by a factor of2for safety.If a10μF capacitor is required,use20μF.The preceding rules and recommendations apply to capacitors used in connection with the TPA2013D1.The TPA2013D1cannot meet its performance specifications if the rules and recommendations are not followed.Table3.Typical tolerance and temperature coefficient of capacitance by materialMaterial COG/NPO X7R X5R Typical Tolerance±5%±10%80/–20% Temperature Coefficient±30ppm±15%22/–82%Temperature Range,°C–55/125°C–55/125°C-30/85°C()CC CC DD boost CCI V V C =2V f V ´-´D ´´(4)()CC CC DD boost CCI V V C =V f V ´-D ´´(5)SLOS520–AUGUST 2007TPA2013D1CAPACITOR EQUATIONSThe value of the boost capacitor is determined by the minimum value of working capacitance required for stability and the maximum voltage ripple allowed on V CC in the application.The minimum value of working capacitance is 10μF.Do not use any component with a working capacitance less than 10μF.For X5R or X7R ceramic capacitors,Equation 4shows the relationship between the boost capacitance,C,to load current,load voltage,ripple voltage,input voltage,and switching frequency (I CC ,V CC ,ΔV,V DD ,f boost respectively).Insert the maximum allowed ripple voltage into Equation 4to solve for C.A factor of 2is included to implement the rules and specifications listed earlier.For aluminum or tantalum capacitors,Equation 5shows the relationship between he boost capacitance,C,to load current,load voltage,ripple voltage,input voltage,and switching frequency (I CC ,V CC ,ΔV,V DD ,f boost respectively).Insert the maximum allowed ripple voltage into Equation 5to solve for C.Solve this equation assuming ESR is zero.Capacitance of aluminum and tantalum capacitors is normally not sensitive to applied voltage so there is no factor of 2included in Equation 5.However,the ESR in aluminum and tantalum capacitors can be significant.Choose an aluminum or tantalum capacitor with ESR around 30m Ω.For best perfornamce using of tantalum capacitor,use at least a 10V rating.Note that tantalum capacitors must generally be used at voltages of half their ratings or less.。

STM8S103中文资料

10 电气特性 .................................................................................................................32

10.1 参数条件............................................................................................................................32 10.1.1 最小和最大值 .............................................................................................................32 10.1.2 典型数值 ....................................................................................................................32 10.1.3 典型曲线 ....................................................................................................................32 10.1.4 负载电容 ....................................................................................................................32 10.1.5 引脚输入电压 .............................................................................................................32

MAX3232中文资料.pdf

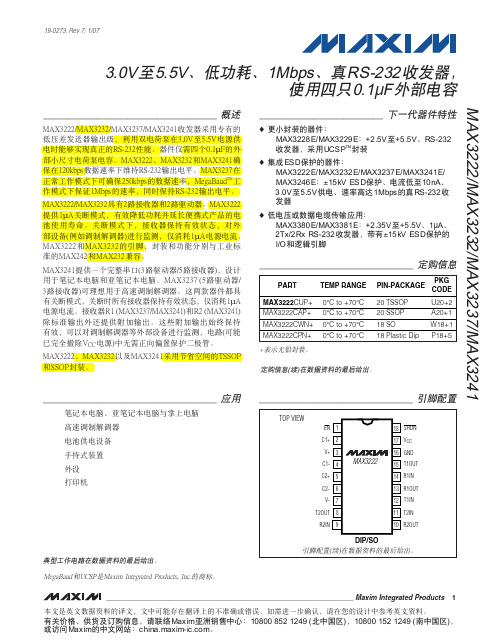

MAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容________________________________________________________________Maxim Integrated Products119-0273; Rev 7; 1/07MegaBaud和UCSP是Maxim Integrated Products, Inc.的商标。

本文是英文数据资料的译文,文中可能存在翻译上的不准确或错误。

如需进一步确认,请在您的设计中参考英文资料。

有关价格、供货及订购信息,请联络Maxim亚洲销售中心:10800 852 1249 (北中国区),10800 152 1249 (南中国区),或访问Maxim的中文网站:。

M A X 3222/M A X 3232/M A X 3237/M A X 32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Note 1:V+ and V- can have a maximum magnitude of 7V, but their absolute difference cannot exceed 13V.V CC ...........................................................................-0.3V to +6V V+ (Note 1)...............................................................-0.3V to +7V V- (Note 1)................................................................+0.3V to -7V V+ + V- (Note 1)...................................................................+13V Input VoltagesT_IN, SHDN , EN ...................................................-0.3V to +6V MBAUD...................................................-0.3V to (V CC + 0.3V)R_IN.................................................................................±25V Output VoltagesT_OUT...........................................................................±13.2V R_OUT....................................................-0.3V to (V CC + 0.3V)Short-Circuit DurationT_OUT....................................................................ContinuousContinuous Power Dissipation (T A = +70°C)16-Pin TSSOP (derate 6.7mW/°C above +70°C).............533mW 16-Pin Narrow SO (derate 8.70mW/°C above +70°C)....696mW 16-Pin Wide SO (derate 9.52mW/°C above +70°C)........762mW 16-Pin Plastic DIP (derate 10.53mW/°C above +70°C)...842mW 18-Pin SO (derate 9.52mW/°C above +70°C)..............762mW 18-Pin Plastic DIP (derate 11.11mW/°C above +70°C)..889mW 20-Pin SSOP (derate 7.00mW/°C above +70°C).........559mW 20-Pin TSSOP (derate 8.0mW/°C above +70°C).............640mW 28-Pin TSSOP (derate 8.7mW/°C above +70°C).............696mW 28-Pin SSOP (derate 9.52mW/°C above +70°C).........762mW 28-Pin SO (derate 12.50mW/°C above +70°C).....................1W Operating Temperature RangesMAX32_ _C_ _.....................................................0°C to +70°C MAX32_ _E_ _ .................................................-40°C to +85°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10s).................................+300°CMAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容_______________________________________________________________________________________3TIMING CHARACTERISTICS—MAX3222/MAX3232/MAX3241(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)ELECTRICAL CHARACTERISTICS (continued)(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)A X 3222/M A X 3232/M A X 3237/M A X 32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容4_______________________________________________________________________________________典型工作特性Ω, T A = +25°C, unless otherwise noted.)LOAD CAPACITANCE (pF)0246810121416182022150MAX3222/MAX3232SLEW RATEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E (V /µs )20003000100040005000510152025303540MAX3222/MAX3232SUPPLY CURRENT vs. LOAD CAPACITANCEWHEN TRANSMITTING DATALOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )20003000100040005000TIMING CHARACTERISTICS—MAX3237(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Note 2:MAX3222/MAX3232/MAX3241: C1–C4 = 0.1µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.MAX3237: C1–C4 = 0.1µF tested at 3.3V ±5%; C1–C4 = 0.22µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.Note 3:Transmitter input hysteresis is typically 250mV.MAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容_______________________________________________________________________________________5-7.5-5.0-2.502.55.07.50MAX3241TRANSMITTER OUTPUT VOLTAGEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )2000300010004000500046810121416182022240MAX3241SLEW RATEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E (V /µs )20003000100040005000510152025303545400MAX3241SUPPLY CURRENT vs. LOADCAPACITANCE WHEN TRANSMITTING DATALOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )20003000100040005000-7.5-5.0-2.502.55.07.50MAX3237TRANSMITTER OUTPUT VOLTAGE vs. LOAD CAPACITANCE (MBAUD = GND)LOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )200030001000400050000102030504060700MAX3237SLEW RATE vs. LOAD CAPACITANCE(MBAUD = V CC )LOAD CAPACITANCE (pF)S L E W R A T E (V /µs )500100015002000-7.5-5.0-2.502.55.07.50MAX3237TRANSMITTER OUTPUT VOLTAGE vs. LOAD CAPACITANCE (MBAUD = V CC )LOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )5001000150020001020304050600MAX3237SUPPLY CURRENT vs.LOAD CAPACITANCE (MBAUD = GND)LOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )200030001000400050000246810120MAX3237SLEW RATE vs. LOAD CAPACITANCE(MBAUD = GND)LOAD CAPACITANCE (pF)S L E W R A T E (V /µs )2000300010004000500010302040506070MAX3237SKEW vs. LOAD CAPACITANCE(t PLH - t PHL )LOAD CAPACITANCE (pF)1000150050020002500____________________________________________________________________典型工作特性(续)(V CC = +3.3V, 235kbps data rate, 0.1µF capacitors, all transmitters loaded with 3k Ω, T A = +25°C, unless otherwise noted.)M A X 3222/M A X 3232/M A X 3237/M A X 32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容6_________________________________________________________________________________________________________________________________________________________________引脚说明MAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容_______________________________________________________________________________________7_______________________________详细说明双电荷泵电压转换器MAX3222/MAX3232/MAX3237/MAX3241的内部电源由两路稳压型电荷泵组成,只要输入电压(V CC )在3.0V至5.5V范围以内,即可提供+5.5V (倍压电荷泵)和-5.5V (反相电荷泵)输出电压。

STM8S103F2P6

4.10 TIM1 — 16位高级控制定时器............................................................................................11

4.11

TIM2 — 16位通用定时器...................................................................................................11

6 存储器和寄存器映像................................................................................................19

6.1

存储器映像 ........................................................................................................................19

21个高吸收电流输出 非常强健的I/O设计,对倒灌电流有非常

强的承受能力

开发支持 单线接口模块(SWIM)和调试模块(DM),

可以方便地进行在线编程和非侵入式调 试

本文档英文原文下载地址: /stonline/products/literature/ds/15441.pdf

参照2009年6月 STM8S103x 数据手册英文第3版 本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录

STM8S103xx数据手册

目录

1 简介...........................................................................................................................4

安立s331d中文说明书(驻波仪)

Site MasterS113C,S114C,S331C,S332C,天线、电缆和频谱分析仪用户指南专门用于传输线和其它射频器件的手持式测试仪目录第一章—概述简介………………………………………………………………..1-1说明………………………………………………………………..1-1标准附件……………………………………………………………1-1选件…………………………………………………………………1-2可选附件……………………………………………………………1-2性能指标…………………………………………………………..1-3维护事项……………………………………………………………1-6校准…………………………………………………………………1-6自动校准InstaCal 模块…………… ………………………………1-7年检………………………………………………………………….1-7第二章—功能和操作简介…………………………………………………………….…….2-1测试连接器面板…………………………………………………….2-1前面板概述………………………………………………………….2-2功能区硬键……………………………………………………………2-3 键盘区硬键…………………………………………………………2-4软键…. ………………………………………………………………2-6功率监测菜单……………………………………………………….2-15符号………………………………………………………………….2-19自检………………………………………………………………….2-19错误代码…………………………………………………………….2-19自检错误…………..…………………………………………….2-19范围错误……..………………………………………………….2-21自动校准InstaCal错误消息………….…………………………2-22电池信息…………………………………………….………………2-24新电池充电…………………………………………………………2-24在Site Master上给电池充电…………………………………….2-24用充电器给电池充电………………………………………………2-24电池充电指示……………………………………………………2-25电池寿命…………………………………………………………..2-25关于电池的重要信息……………………………………………..2-26第三章—操作入门简介…………………………………………………………3-1开机过程……………………………………………………3-1选择频率/距离………………………………………………3-2校准…………………………………………………………..3-2校准确认……………………………………………….3-3手动校准过程………………………………………….3-4自动校准InstaCal 模块确认…………………………3-5自动校准InstaCal模块校准过程……………………. 3-6有测试端口延长电缆的校准………………………3-6设置刻度…………………………………………………3-7自动刻度……………………………………………….3-7幅度刻度………………………………………………3-7保存和调用设置………………………………………….3-7保存设置……………………………………………...3-7调用设置……………………………………………..3-8保存和调用显示…………………………………………3-8保存显示…………………………………………….3-8调用显示……………………………………………3-8设置距离和电缆类型……………………………..3-9改变单位…………………………………………………..3-9改变显示语言……………………………………………..3-9打印………………………………………………………..3-10打印屏幕……………………………………………..3-10打印机开关设置……………………………………..3-11使用软背包……………………………………………….3-12第四章—电缆测量和天线测量简介……………………………………………………….4-1传输线扫描的基本原理………………………………….4-1进行传输线扫描所需的信息…………………………….4-2典型传输线扫描的测试过程…………………………….4-3系统回波损耗测量………………………………….4-3插入损耗测量………………………………………4-4故障点定位(DTF)传输线测试…………………4-8天线子系统回波损耗测试………………………..4-10第五章—频谱分析仪测量简介……………………………………………………….5-1占用带宽………………………………………………….5-1通道功率测量…………………………………………….5-2Site Master的通道功率测量…………………………5-2邻道功率测量…………………………………………….5-4带外杂波散射测量……………………………………….5-6带内/通道外测量…………………………………………5-7场强测量…………………………………………………5-8天线校准………………………………………………….5-9第六章—功率测量简介………………………………………………………..6-1功率测量…………………………………………………..6-1第七章—Site Master软件工具简介…………………………………………………………7-1特点…………………………………………………………7-1系统需求……………………………………………………7-1安装…………………………………………………………7-2通讯口设置……………………………………………7-2接口电缆安装………………………………………….7-3使用软件工具……………………………………………….7-3从Site Master下载图形曲线………………………………..7-3图形获取……………………………………………………..7-3图形属性…………………………………………………….7-4曲线叠加或图形叠加…………………………………..7-4保存曲线………………………………………………7-5常规电缆列表…………………………………………7-6输入天线因子…………………………………………7-7上载天线因子………………………………………...7-8创建数据库…………………………………………..7-8打印格式……………………………………………..7-8附录 A—参考数据同轴电缆技术数据…………………………………………………A-1附录B—视窗简介…………………………………………………………………B-1样例…………………………………………………………………B-1第一章概述简介本章对Site Master S113C、S114C、S331C和S332C型号及其性能指标、选用附件、日常维护和校准要求进行了说明。

CMM1530-LC-00S0中文资料

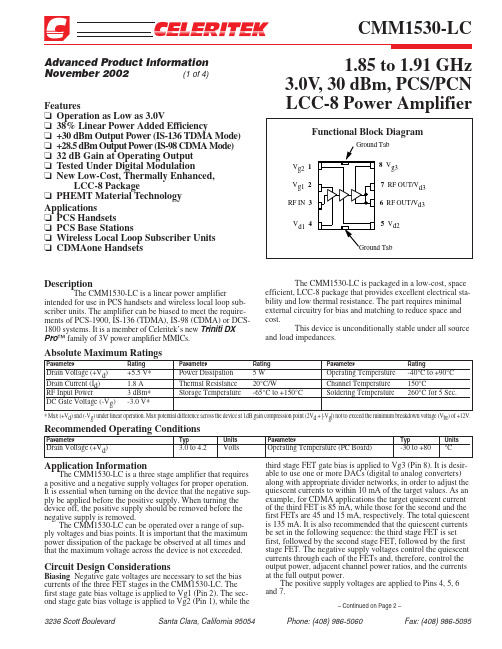

Features❏Operation as Low as 3.0V❏38% Linear Power Added Efficiency❏+30 dBm Output Power (IS-136 TDMA Mode) ❏+28.5 dBm Output Power (IS-98 CDMA Mode)❏32 dB Gain at Operating Output ❏Tested Under Digital Modulation ❏New Low-Cost, Thermally Enhanced,LCC-8 Package❏PHEMT Material Technology Applications ❏PCS Handsets ❏PCS Base Stations❏Wireless Local Loop Subscriber Units ❏CDMAone Handsets DescriptionThe CMM1530-LC is a linear power amplifierintended for use in PCS handsets and wireless local loop sub-scriber units. The amplifier can be biased to meet the require-ments of PCS-1900, IS-136 (TDMA), IS-98 (CDMA) or DCS-1800 systems. It is a member of Celeritek’s new Triniti DX Pro ™family of 3V power amplifier MMICs.The CMM1530-LC is packaged in a low-cost, spaceefficient, LCC-8 package that provides excellent electrical sta-bility and low thermal resistance. The part requires minimal external circuitry for bias and matching to reduce space and cost.This device is unconditionally stable under all sourceand load impedances.1.85 to 1.91 GHz3.0V , 30 dBm, PCS/PCN LCC-8 Power AmplifierAdvanced Product Information November 2002(1 of 4)d g d g br Application InformationThe CMM1530-LC is a three stage amplifier that requires a positive and a negative supply voltages for proper operation.It is essential when turning on the device that the negative sup-ply be applied before the positive supply. When turning the device off, the positive supply should be removed before the negative supply is removed.The CMM1530-LC can be operated over a range of sup-ply voltages and bias points. It is important that the maximum power dissipation of the package be observed at all times and that the maximum voltage across the device is not exceeded.Circuit Design ConsiderationsBiasing Negative gate voltages are necessary to set the bias currents of the three FET stages in the CMM1530-LC. The first stage gate bias voltage is applied to Vg1 (Pin 2). The sec-ond stage gate bias voltage is applied to Vg2 (Pin 1), while thethird stage FET gate bias is applied to Vg3 (Pin 8). It is desir-able to use one or more DACs (digital to analog converters)along with appropriate divider networks, in order to adjust the quiescent currents to within 10 mA of the target values. As an example, for CDMA applications the target quiescent current of the third FET is 85 mA, while those for the second and the first FETs are 45 and 15 mA, respectively. The total quiescent is 135 mA. It is also recommended that the quiescent currents be set in the following sequence: the third stage FET is set first, followed by the second stage FET, followed by the first stage FET. The negative supply voltages control the quiescent currents through each of the FETs and, therefore, control the output power, adjacent channel power ratios, and the currents at the full output power.The positive supply voltages are applied to Pins 4, 5, 6and 7.– Continued on Page 2 –3236 Scott Boulevard, Santa Clara, California 95054ParameterConditionMinTypMaxUnitsFrequency Range 1.85 1.91GHz Gain@ Digital power output2831dB Gain Ripple*1805-1880 MHz & 1850-1910 MHz 1.5dB Gain VariationOver supply voltage 2dB/V Over temperature 0.03dB/°C Power Output Control Range Vdd = 0 V to +3.5 V50dB Power Output Meets IS-136 TDMA mask +30.0dBm Meets IS-98 CDMA mask+28.5dBm Harmonics2nd @ Digital power output, no output trapping, Po=+28.5 dBm -30dBc 3rd @ Digital power output, no output trapping, Po=+28.5 dBm -40dBc Noise Power in Receive Band 30 kHz bandwidth-94dBmLinearityCDMA modulation @ +28.5 dBm Pout, 1.25 MHz offset -45dBc/30KHz TDMA modulation @ +30 dBm Pout - Adjacent -26dBc TDMA modulation @ +30 dBm Pout - Alternate -45dBc Spurious Signal VSWR = 3:1 in-band, VSWR = 10:1 out-of-band-80dBc Noise Figure3.0dB Input Return Loss 10dB Output Return Loss 8dB Efficiency (Vdd = 3.0 V)Pout = +30.0 dBm - TDMA 3638%Pout = +28.5 dBm - CDMA 3235%Positive Supply Current (I d )Pout IS-136 TDMA 750mA Pout IS-98 CDMA 595mA Quiescent Current (I q )No RF CDMA mode 130mA No RF TDMA mode200mA Negative Supply Current (-I g )Includes external resistor divider 1.1 2.0mA Negative Supply Voltage (-V g )Into external resistor divider-0.5-0.8-1.4VElectrical CharacteristicsUnless otherwise specified, the following specifications are guaranteed at room temperature with drain voltage (+V d ) = 3.5 V in Celeritek test fixture.* Specifications guaranteed over the temperature range of -20°C to +80°C(3 of 4)IS-98 CDMA Spectral Mask(Vdd=3.5V, 1,880 MHz, Po=+28.5 dBm)TDMA Power Output and Efficiency vs Input Power(3.0V, 1.91 GHz)Input Output, dBm0152535-13-117.5-10-7-452.535.0A d j a c e n t C h a n e l Id & IS-136 TDMA ACPR vs Power Output (3.5V, 1.91 GHz)-6020060010001930-40-20Adjacent channel power (worst case, Fc ±30 kHz)Alternate channel power (worst case, Fc ±60 kHz)21.7524.527.25Power Output, dBm (30 kHz BW)IdId & IS-98 CDMA ACPR vs Power Output (3.5V, 1.91 GHz)Power Output, dBm (1.25 MHz BW)-55100400800-50-45Adjacent channel power (worst case ±1.25 MHz)28.57.12514.521.625CDMA Power Output, 2nd and 3rd Harmonicsvs Input Power (3.5V, 1.91 GHz)Input Output, dBm-60152535-26.5-2.5-45P o w e r O u t p u t , d B m5-20.5-14.5-8.5-302nd3rd(Vdd=3.5V, 1,752 MHz, Po=+28.5 dBm)3236 Scott Boulevard, Santa Clara, California 95054Physical DimensionsRecommended Matching TopologyNote: This schematic represents the topology of the matching circuit recommended by Celeritek.Evaluation Board SchematicER = 4.60Thickness = 0.031 in.cc TXRF OUTRF IN 1.5 K 65V 元器件交易网。

涓流充电计时芯片DS1302中文手册

I特性★实时时钟计算年、月、日、时、分、秒、星期,直到 2100 年,并有闰年调节功能★31 x 8 位 通用暂存 RAM ★串行输入输出使管脚数最少★ 2.0V 至 5.5V 宽电压范围操作★在 2.0V 时工作电流小于 300nA★读写时钟或 RAM 数据时有单字节或多字节(脉冲串模式)数据传送方式★8 管脚 DIP封装或可选的 8 管脚表面安装 SO 封装★简单的 3 线接口★与 TTL 兼容 (VCC = 5V)★可选的工业温度范围:-40°C to +85°C ★与 DS1202 兼容★美国保险商试验室(UL®)认证订货信息型号温度范围管脚封装顶端标志+表示无铅/符合RoHS 标准的封装.*顶端标识上的N 表示工业温度范围器件,A 表示无铅器件. UL 是美国保险商试验室的注册商标.详细描述DS1302涓流充电计时芯片包含一个实时时钟/日历和31字节的静态RAM.通过简单的串行接口与微处理器通讯.这个实时时钟/日历提供年月日,时分秒信息.对于少于31天的月份月末会自动调整,还有闰年校正.由于有一个AM/PM 指示器,时钟可以工作在12小时制或者24小时制。

使用同步串行通讯简化了DS1302与微处理器的接口。

与时钟/RAM 通讯只需要三根线: CE, I/O (数据线), and SCLK (串行时钟). 数据输出输入时钟/RAM 一次1字节或者在脉冲串中多管脚定义D S 1302涓流充电计时芯片达31字节. DS1302被设计工作在非常低的电能下,在低于1μW 时还能保持数据和时钟信息. DS1302是DS1202的后继者. 除了DS1202的基本计时功能以外, DS1302有额外特点比如,双管脚主电源和备用电源,可编程涓流充电器V CC1,还附加7字节的暂存器.操作图1显示了串行计时器的主要元素:移位寄存器,控制逻辑,振荡器,实时时钟,还有RAM.典型工作电路图1框图: 典型工作性能(V C C = 3.3V , T A = +25°C ,除非另外声明.)电源控制输入移位寄存器命令控制逻辑实时时钟管脚描述管脚 名称 功能1V CC2双供电配置中的主电源供应管脚,V CC1连接到备用电源,在主电源失效时保持时间和日期数据.D S1302工作于V CC1和V CC2中较大者.当V CC2比V CC1高0.2V时,V CC2 给 D S1302供电.当V CC1比V CC2高时, V CC1给D S1302供电.2X1 3X2与标准的32.768k H z石英晶体相连.内部振荡器被设计与指定的6p F 装载电容的晶体一起工作.更多关于晶体选择和布局注意事项的信息请参考应用笔记58页:D a l l a s实时时钟晶振注意事项.D S1302也可以被外部的32.768k H z振荡器驱动.这种配置下,X1与外部震荡信号连接,X2悬浮.4G N D电源地5C E输入.C E信号在读写时必须保持高电平.此管脚内部有一个40kΩ(典型值)的下拉电阻连接到地.注意:先前的数据手册修正把C E当作R S T.管脚的功能没有改变.6I/O输入/推挽输出.I/O管脚是三线接口的双向数据管脚.此管脚内部有一个40kΩ(典型值)的下拉电阻连接到地.7S C L K输入.S C L K用来同步串行接口上的数据动作.此管脚内部有一个40kΩ(典型值)的下拉电阻连接到地.8V CC1低功率工作在单电源和电池工作系统和低功率备用电池.在使用涓流充电的系统中,这个管脚连接到可再充能量源.U L认证在使用锂电池时确保避免反向充电电流.振荡电路D S1302使用一个外部32.768k H z晶体.振荡电路工作时不需要任何外接的电阻或者电容表1 详细指明了几个外部晶体的参数.图1 显示了震荡电路的功能简图.如果使用指定规格的晶体,启动时间通常少于1秒钟.时钟精确度时钟的精确度取决于晶振的精确度,以及振荡电路容性负载与晶振校正的容性负载之间匹配的精确度。

SAT31技术说明书(3.00) 2011-02-17

SAT31测控保护装置技术说明书(3.00)-2011年1月-•装置的操作使用,请参见《产品使用手册》。

•本说明书的内容:1. SAT31概述 (1)SAT31装置概述2. SAT31-2变压器测控保护装置 (11)SAT31-2功能说明3. SAT31-3变压器测控保护装置 (42)SAT31-3功能说明4.附录A 插件E的配置应用 (69)5.附录B 插件B的配置应用 (73)6.附录C 插件F的配置应用 (75)7.附图概述SAT31测控保护装置适用于110kV及以下电压等级变压器单侧的后备保护及测量、控制,可满足保护及远动双重标准的要求。

1.1功能配置功能SAT31-2 SAT31-3过流保护◆◆过流复压闭锁◆◆过流方向闭锁◆过负荷◆◆过负荷启动风冷◆过负荷闭锁调压◆零序过流保护◆◆间隙零流保护(或小电阻零流)◆零序过压保护◆非电量保护◆◆低电压保护◆断线判别◆◆母线保护(充电保护/ 简易保护)◆故障录波◆◆变压器单侧测控◆◆可接打印机◆注:◆表示该型号装置具备此功能。

1.2技术数据1.2.1. 额定参数装置电源直流220V或110V(订货时请注明)交流电压100V交流电流5A或1A(订货时请注明)额定频率50Hz功率消耗直流电源回路:正常工作时,不大于25W;保护动作时,不大于30W交流电流回路:额定5A时每相不大于0.75VA;额定1A时每相不大于0.5VA交流电压回路:每相不大于0.5VA1.2.2. 性能参数交流量测量精度电压、电流:±0.2%功率及因数:±0.5%频率:±0.01Hz过载能力测控电流回路:1.2倍额定电流时,连续工作;20倍额定电流时,允许1s保护电流回路:2倍额定电流时,连续工作;10倍额定电流时,允许10s;40倍额定电流时,允许1s交流电压回路:1.2倍额定电压时,连续工作;1.4倍额定电压时,允许10s;2倍额定电压时,允许1s直流电源回路:0.8~1.2倍的额定电压时,连续工作(装置经受过载电流/电压后,无绝缘损坏,装置性能不下降)开关量采集信号电平:直流220V或110V或24V(订货时请注明)接入方式:无源空接点SOE站内分辨率:不大于2ms脉冲量采集信号电平:直流24V脉冲要求:宽度应不小于5ms;脉冲周期不小于50ms接入方式:无源空接点或有源脉冲保护精度电流精度:±3%或±0.02 In电压精度:±3%或±0.001 Un角度精度:±5°动作时间:零时限时不大于40ms;定时限时,±2%或±30ms出口接点容量直流220V,5A,不允许断弧绝缘性能绝缘电阻:符合DL/T478-2001中4.10.2和GB/T13729-2002中3.6.1的规定介质强度:符合DL/T478-2001中4.10.3和GB/T13729-2002中3.6.2的规定冲击电压:符合DL/T478-2001中4.10.4和GB/T13729-2002中3.6.3的规定电磁兼容性能辐射电磁场:装置能承受GB/T17626.3-1998中规定的试验等级为Ⅲ级的试验脉冲群干扰:装置能承受GB/T14598.13-1998规定的严酷等级为Ⅲ级的1MHz及100KHz试验浪涌:装置能承受GB/T17626.5-1999中规定的试验等级为Ⅳ级的试验快速瞬变:装置能承受GB/T14598.10-1996中规定的严酷等级为Ⅳ级的试验静电放电:装置能承受GB/T14598.14-1998中规定的严酷等级为Ⅳ级的试验射频传导:装置能承受GB/T17626.6-1998中规定的严酷等级为Ⅲ级的射频传导干扰试验工频干扰:装置能承受IEC60255-22-7:2003中规定的严酷等级为A级的工频干扰试验工频磁场:装置能承受GB/T17626.8-1998中规定的试验等级为Ⅴ级的工频磁场干扰试验脉冲磁场:装置能承受GB/T17626.9-1998中规定的严酷等级为Ⅳ级的脉冲磁场干扰试验传导发射:传导发射限值满足GB/T14598.16-2002中的规定机械性能 振动响应:装置能承受GB/T11287-2000中3.2.1规定的严酷等级为1级的振动响应试验振动耐久:装置能承受GB/T11287-2000中3.2.2规定的严酷等级为1级的振动耐久试验冲击响应:装置能承受GB/T14537-1993中4.2.1规定的严酷等级为1级的冲击响应试验冲击耐久:装置能承受GB/T14537-1993中4.2.2规定的严酷等级为1级的冲击耐久试验碰撞: 装置能承受GB/T14537-1993中4.3规定的严酷等级为1级的碰撞试验1.3 装置显示及操作装置的液晶和键盘操作的详细说明,请参见《产品使用手册》。

MAXIM DS3231 说明书

_________________________________概述DS3231是低成本、高精度I 2C 实时时钟(RTC),具有集成的温补晶体振荡器(TCXO) 和晶体。

该器件包含电池输入端,断开主电源时仍可保持精确的计时。

集成晶体振荡器提高了器件的长期精确度,并减少了生产线的元件数量。

DS3231提供商用级和工业级温度范围,采用16引脚、300mil 的SO 封装。

RTC 保持秒、分、时、星期、日期、月和年信息。

少于31天的月份,将自动调整月末日期,包括闰年补偿。

时钟的工作格式可以是24小时或带AM /PM 指示的12小时格式。

提供两个可编程日历闹钟和一路可编程方波输出。

地址与数据通过I 2C 双向总线串行传输。

精密的、经过温度补偿的电压基准和比较器用来监视V CC 状态,检测电源故障、提供复位输出,并在必要时自动切换到备用电源。

另外,RST 监视引脚可以作为手动按钮输入以产生外部复位信号。

_________________________________应用服务器电表远程信息处理系统GPS_________________________________特性♦0°C 至+40°C 范围内精度为±2ppm ♦-40°C 至+85°C 范围内精度为±3.5ppm ♦为连续计时提供备用电池输入♦工作温度范围商用级:0°C 至+70°C 工业级:-40°C 至+85°C♦低功耗♦实时时钟提供秒、分、时、星期、日期、月、年信息,并提供有效期到2100年的闰年补偿♦两个日历闹钟♦可编程方波输出♦快速(400kHz) I 2C 接口♦3.3V 工作电压♦数字温度传感器输出:精度为±3°C ♦老化修正寄存器♦RST 输入/输出DS3231高精度、I 2C 集成RTC/TCXO/晶体______________________________________________Maxim Integrated Products1Rev 1; 2/05______________________________定购信息引脚配置在数据资料的最后部分给出。

ST串行实时时钟(RTC)应用指南AN3060说明书

2015年11月DocID16253 Rev 1 [English Rev 3] 1/25 AN3060 应用笔记串行实时时钟(RTC )应用指南 Doug Sams前言ST 串行实时时钟(RTC )系列产品广受用户欢迎。

多年来,关于这些器件的许多问题已被支持它们的应用程序组解决了。

本文档汇集了一些已解决的最普遍问题,包括晶振的布线考虑到上电时正确的软件访问。

这会帮助读者理解RTC 的一些精微之处,以及怎样保持其可靠运行。

AN3060 目录目录1电池连接和充电保护 (5)1.1串联电阻 (5)1.2电池上的去耦电容 (5)1.3阻断二极管 (6)1.4面向ST实时时钟的Underwriters Laboratories文件 (6)1.5电池安装 (7)2布局考虑 (8)2.1RTC晶振的某些基本布局考虑是什么? (8)3振荡器电路 (9)3.1除了晶振之外,还需要添加什么其他元件来使RTC振荡器正确工作? (9)4负超调 (11)4.1负超调会影响我的实时时钟工作吗?如何影响?如何防止该影响? 11 5切换电压 (12)5.1切换电压是否依赖于电池电平?或者它始终是一个固定值?RTC的最大电池电压是多少? (12)6振荡器失效检测 (15)6.1什么是OF位?它如何工作? (15)7电池低电平检测 (16)7.1电池低电平位是如何工作的?它能检测缺失的电池吗? (16)8挂起(HT)位 (18)8.1挂起位(HT)有什么作用?如何使用它? (18)9RTC初始化 (21)9.1初次上电时访问RTC的最佳时序是什么?后续上电呢? (21)10版本历史 (24)DocID16253 Rev 1 [English Rev 3] 2/25表格索引表1:取消选择和切换阈值总结 (13)表2:M41T81S寄存器映射 (16)表3:M41ST85W寄存器映射 (18)表4:文档版本历史 (24)表5:中文文档版本历史 (24)DocID16253 Rev 1 [English Rev 3] 3/25图表索引图1:RTC/NVRAM中的电池切换电路 (5)图2:VBAT通路上二极管的影响 (6)图3:SNAPHAT SOIC封装 (6)图4:带有固定片的钮扣电池 (7)图5:布局考虑 (8)图6:内置负载电容 (9)图7:典型寄生二极管 (11)图8:负超调保护 (11)图9:典型切换电路 (12)图10:切换电路 (13)图11:振荡器失效检测电路 (15)图12:电池监测功能 (17)图13:时钟和非时钟寄存器 (19)图14:M41T83/M41T82上电默认值 (21)图15:初次上电 (22)图16:从备份上电 (23)DocID16253 Rev 1 [English Rev 3] 4/251 电池连接和充电保护ST串行实时时钟的电池连接非常简单。

美国ATC Diversified SLA系列三相电压监测器-中文手册说明书

Style "A"Style "N"Style "E"Phase Monitors • Available up to 480 VAC(625 VAC with "E" style)153154Diversified Electronics 800.727.5646 STYLE "E"STYLE "E"STYLE "E"STYLE "N"STYLE "N"Figure 4Figure 5Figure 1 RB-08 or OT-08Figure 2 RB-11Figure 3 70-463-1155Diversified Electronics 800.727.5646 ORDERING INFORMATIONMODEL NUMBER OPERATING VOLTAGETYPE OF ADJUSTMENT DROP-OUT VOLTAGE AGENCYAPPROVAL OUTPUT RATINGS1 Ø LOW 3 Ø LOWSLA-120-ALA 95-130 AdjLock Shaft79-10885-117—DPDT,345 VA Inductive;10 Amps Resistive @ 240 VAC.Figure 2SLA-120-ASA Screwdriver SPDT,345 VA Inductive;10 Amps Resistive @ 240 VAC,Figure 1SLA-120-ASB SPDT,345 VA Inductive;10 Amps Resistive @ 240 VAC,Figure 3SLA-230-ALA 190-270 Adj.Lock Shaft158-224171-243DPDT,345 VA Inductive;10 Amps Resistive @ 240 VAC,Figure 2SLA-230-ASA ScrewdriverSPDT,345 VA Inductive;10 Amps Resistive @ 240 VAC,Figure 1SLA-230-ASB SPDT,345 VA Inductive;10 Amps Resistive @ 240 VAC,Figure 3SLA-380-ASA 350-440 Adj.290-365315-396—SPDT,360 VA Inductive;10 Amps Resistive @ 240 VAC,Figure 1SLA-440-ASA 430-480 Adj.357-398387-432SUA-120-ALA 95-130 Adj.Lock Shaft79-10885-117SPDT,345 VA Inductive;10 Amps Resistive @ 240 VAC,Figure 1SUA-120-ALAU*SUA-230-ALA 190-270 Adj.158-224171-243SUA-230-ALAU*SUA-380-ASA 350-440 Adj.Screwdriver290-365315-396SPDT,10 AmpsResistive @ 240 VAC,Figure 1SUA-440-ASA430-480 Adj.357-398387-432*UL Listed only when used with RB-08 relay socket;5 Amps Resistive @ 240 VAC.All voltages referenced on this page are phase-to-phase.Models also available with fixed operating voltages.Consult factory.MODEL NUMBER OPERATING VOLTAGE DROP-OUT VOLTAGE RESET AGENCYAPPROVAL OUTPUT RATINGS1 Ø LOW 3 Ø LOW SLA-120-ALE 95-130 Adj.79-10885-117Automatic DPDT,211 VA Inductive;10 Amps Resistive @ 120 VAC.Figure 4SLA-120-ALER Manual DPDT,211 VA Inductive;10 Amps Resistive @ 120 VAC.Figure 4SLA-230-ALE 190-270 Adj.158-224171-243Automatic DPDT,345 VA Inductive;5 Amps Resistive @ 240 VAC.Figure 4SLA-230-ALER Manual DPDT,345 VA Inductive;5 Amps Resistive @ 240 VAC.Figure 4SLA-380-ALE 350-440 Adj.290-365315-396Automatic DPDT,360 VA Inductive;3 Amps Resistive @ 600 VAC.Figure 4SLA-380-ALER Manual SPDT,360 VA Inductive;3 Amps Resistive @ 600 VAC.Figure 5SLA-440-ALE 430-480 Adj.357-398387-432Automatic DPDT,360 VA Inductive;3 Amps Resistive @ 600 VAC.Figure 4SLA-440-ALER Manual SPDT,360 VA Inductive;3 Amps Resistive @ 600 VAC.Figure 5SLA-575-ALE525-625 Adj.436-519473-563AutomaticDPDT,360 VA Inductive;3 Amps Resistive @ 600 VAC.Figure 4All voltage referenced are phase-to-phase.—Models also available with fixed operating voltages.Consult factory.MODEL NUMBER OPERATING VOLTAGETYPE OF OPERATIONDROP-OUT VOLTAGE AGENCYAPPROVAL1 Ø LOW 3 Ø LOWSLA-120-AFN 120Fixed 100108SLA-208-AFN 208Fixed 173187SLA-220-AFN 220Fixed 183198SLA-240-AFN240Fixed 199216SPDT 180VA @ 120VAC; 72VA @ 24VAC; All voltage referenced are phase-to-phase.SPDT 180 va @ 120 vac, 72 va @ 24 vac.STYLE A PLUG-INSTYLE E SURFACE MOUNTED ENCLOSURESTYLE N EPOXY ENCAPSULATED——IND .CONT . EQ 496Y IND . CONT . EQ 496YIND . CONT . EQ 496YIND . CONT . EQ 496Y IND . CONT . EQ 496Y IND . CONT . EQ 496Y IND . CONT . EQ 496Y IND . CONT . EQ 496Y IND . CONT . EQ 496Y IND . CONT . EQ 496Y IND . CONT . EQ 496YP H A S E V O L T A G E M O N I T O R SS L A S e r i e s。

CA3130AMZ中文资料

OFFSET NULL INV. INPUT NON-INV. INPUT V-

1 2 3 4

8

STROBE V+ OUTPUT OFFSET NULL

+

7 6 5

*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications. NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

Applications

• Ground-Referenced Single Supply Amplifiers • Fast Sample-Hold Amplifiers • Long-Duration Timers/Monostables • High-Input-Impedance Comparators (Ideal Interface with Digital CMOS) • High-Input-Impedance Wideband Amplifiers • Voltage Followers (e.g. Follower for Single-Supply D/A Converter) • Voltage Regulators (Permits Control of Output Voltage Down to 0V) • Peak Detectors • Single-Supply Full-Wave Precision Rectifiers • Photo-Diode Sensor Amplifiers

FM3130 中文资料 RTC

南京周立功

地址:南京市珠江路 280 号珠江大厦 2006 室 电话:(025)83613221 83613271 83603500 传真:(025)83613271

20060918引脚配置引脚名称功能x1x2晶振连接acs警报器校验方波sda串行数据scl串行时钟vbak电池供电vdd供电电压vss订购信息fm3130环保8引脚soicfm3130环保8引脚tdfn结构图海纳电子资讯网wwwfpgaarmcom为您提供各种ic的应用资料海纳电子资讯网wwwfpgaarmcom为您提供各种ic的应用资料广州周立功单片机发展有限公司fmm3311330fm313064kbfram集成rtc警报器rev

广州周立功单片机发展有限公司

目录

目录

1. 特性..............................................................................................................................................1 2. 概述..............................................................................................................................................1 3. 引脚配置......................................................................................................................................2 4. 引脚描述......................................................................................................................................3 5. 简述..............................................................................................................................................3 6. 存储器操作..................................................................................................................................3 7. 实时时钟操作..............................................................................................................................4

天馈测试仪中文说明

安立Site Master(基站大师)S331D/S332D天馈线分析仪基站大师是无线技术服务商,承包商及设备安装人员推荐使用的天馈线分析仪。

用户指南质量保证书封面上列出的三种安立公司的产品享受自发货日起一年的材料及技术问题方面的保修。

安立公司的责任涵盖了在保修期内对故障产品的维修及更换。

客户素要提前支付将产品发到安立公司维护的相关运费。

相关责任由原购买方承担,期间的间接损坏安立公司不负有法律责任。

保证书的适用范围前面提到的保修内容不适用于连接器件的正常磨损破坏,也不适用于由于用户的不合理或不充分的维护,不经授权的修改或使用不当,或是超出产品规定的使用环境下运行设备所产生的问题。

除此之外没有发表其它的保修证书,这里任何的改动都将是购买者单方面的独家的修改。

商标认证Windows,windows95.windowsNT,windows98/2000/ME/xp都是微软公司的注册商标。

anritsu,flexcal, instacal, site maste都是安立公司的注册商标。

注意事项安立公司为客户及公司相关人士准备这本手册,是为了指导相关产品及电脑程序的安装、使用、及维护。

其中出现的任何图形、说明及信息归安立公司所有,禁止任何不经授权的引用这些内容。

未提前获得经安立公司的书面许可不得再版、复制、全部或部分引用这些内容来制造或销售相关产品或程序。

更新如要更新手册内容,可以去:http:/查看。

第一章基本信息简介这一部分主要对“基站大师S331D及S332D”这两种设备的性能、可选附件、定期检修以及精度要求方面进行了介绍,在整本手册中,基站设备可以是“S331D 及S332D”这两种型号。

设备频率范围S331D 天馈线分析模式:25—4000MHZS332D 天馈线分析模式:25---4000MHZ光/频谱分析模式:100KHZ—3000MHZ描述“基站大师”S331D是一款手提式天馈线分析仪,S332D是一款手提式天馈线、频谱分析仪。

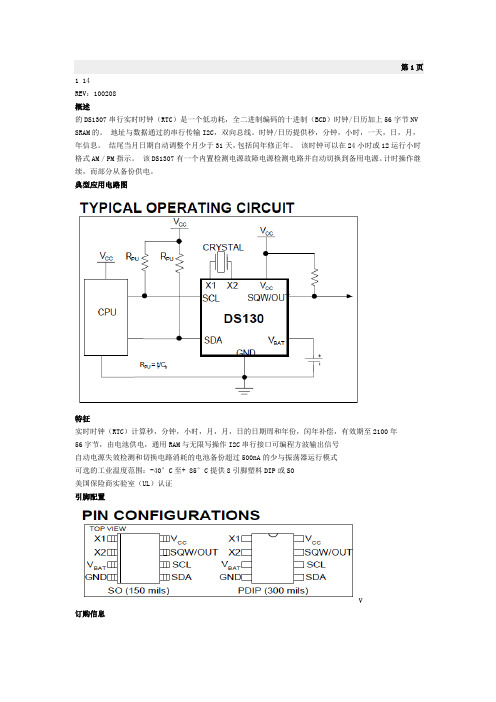

DS1307中文版(最新整理)

第1页1 14REV:100208概述的DS1307串行实时时钟(RTC)是一个低功耗,全二进制编码的十进制(BCD)时钟/日历加上56字节NV SRAM的。

地址与数据通过的串行传输I2C,双向总线。

时钟/日历提供秒,分钟,小时,一天,日,月,年信息。

结尾当月日期自动调整个月少于31天,包括闰年修正年。

该时钟可以在24小时或12运行小时格式AM / PM指示。

该DS1307有一个内置检测电源故障电源检测电路并自动切换到备用电源。

计时操作继续,而部分从备份供电。

典型应用电路图特征实时时钟(RTC)计算秒,分钟,小时,月,月,日的日期周和年份,闰年补偿,有效期至2100年56字节,由电池供电,通用RAM与无限写操作I2C串行接口可编程方波输出信号自动电源失效检测和切换电路消耗的电池备份超过500nA的少与振荡器运行模式可选的工业温度范围:-40°C至+ 85°C提供8引脚塑料DIP或SO美国保险商实验室(UL)认证引脚配置V订购信息+表示无铅/符合RoHS标准的封装。

* A“+”上的任何地方顶部标记表示无铅封装。

一个“N”的顶标随时随地表示的工业温度范围设备。

第2页绝对最大额定值任何引脚对地电压范围........................................- 0.5V至7.0V +工作温度范围(无冷凝)Commercial....................................................0°C 至+ 70°C产业 .........................................................-40°C 至+ 85°C储存温度 Range.......................................... -55°C至+ 125°C焊接温度(DIP, leads)...........................................+260°C 10秒焊接温度(表面贴装)............. .Refer到JPC / JEDEC J-STD-020规格。

XK3130型(KINGBIRD)称重显示仪

XK3130型(KINGBIRD)称重显示仪§1.概述KINGBIRD(金鸟)是梅特勒托-利多公司针对台秤和地上衡的应用而开发设计的称重显示仪。

它不仅具有基本的称重功能,而且提供了动物称重,计数,峰值保持和累加,手动/自动打印等功能,使您的效率大大提高。

1.1 KINGBIRD主要特点·易安装性:多种电压源-可以选择不同的电压供电。

可选交流电压:1OOVAC,120VAC,220VAC。

安装简单-有台式,立柱式和墙式安装形式。

传感器和串行接口均使D型插座,即插即用。

显示器-使用荧光显示器,亮度高。

键盘-轻触薄膜键盘,键盘面板采用耐用的树酯材料,抗物理和化学损伤。

·灵活性:设定-模块化树形结构参数设定,方便用户寻找设定参数,可设置缺省参数,方便快捷。

输入/输出-串行口提供称重数据输出。

·稳定性:IS09001认证-KINGBIRD的设计、制造和测试均是在梅特勒-托利多通过IS09001质量认证的工厂进行。

工厂装配-KINGBIRD的所有零部件(包括选件)都在工厂安装调试好。

可维护性-内置诊断程序,易于发现和解决问题。

标准-KINGBIRD的没计符合有关国际计量和电气安全标准,以及电磁兼容性标准。

·环保性:IS014000认证-KINGBIRD的设计、制造和测试均是在梅特勒-托利多通过IS014000环保认证的工厂进行。

1.2 KINGBlRD技术特性1.2.1硬件特点· 7位荧光段码显示器· 6个轻触薄膜键盘·一体化PCB板结构标准模拟传感器输入接口,可驱动4只350Ω的传感器标准串行口:(1).型号为KTGN-1000的KINGBIRD有-个标准的串行口COM1(RS232)(2).型号为KTGN-1100的KINGBIRD除COM1口外还有COM2第二串口,COM2的通讯形式有20mA /RS232和RS422.20mA/RS232为-路输出,RS422为另-路输出.1.2.2外观特性·锌铝合金外壳,抗干扰强,更适于工业场合应用·标准台式安装,不锈钢支架(选件)用于墙式安装1.2.3电气特性·称重功能最多可接4个350D的模拟传感器最大显示分度数:10,000d按钮皮重功能皮重内锁功能自动去皮功能自动清皮功能手动和自动累加功能单位转换功能自动零跟踪动态检测毛重或净重零指示TraxDSP防震动技术·多种称重模式动物称重简单计数峰值保持功能·操作接口明了、直观的操作界面模块化设定菜单·串行数据口功能多种输出格式连续/命令方式输出手动/白动打印功能KTGN-1100型仪表可同时接串口打印机和火屏幕打印内锁功能1.3技术指标1.3.1 电源电压KINGBIRD可选择多种电源电压:电压范围85~264VA(:,频率为.49Hz~6311z,最_人功率12瓦。

Maxim DS1307 实时钟芯片说明书

FEATURES§ Real-time clock (RTC) counts seconds,minutes, hours, date of the month, month, day of the week, and year with leap-year compensation valid up to 2100§ 56-byte, battery-backed, nonvolatile (NV)RAM for data storage § Two-wire serial interface§ Programmable squarewave output signal § Automatic power-fail detect and switch circuitry§ Consumes less than 500nA in battery backup mode with oscillator running§ Optional industrial temperature range:-40°C to +85°C§ Available in 8-pin DIP or SOIC§ Underwriters Laboratory (UL) recognizedORDERING INFORMATIONDS1307 8-Pin DIP (300-mil)DS1307Z 8-Pin SOIC (150-mil)DS1307N 8-Pin DIP (Industrial)DS1307ZN8-Pin SOIC (Industrial)PIN ASSIGNMENTPIN DESCRIPTIONV CC - Primary Power Supply X1, X2 - 32.768kHz Crystal Connection V BAT - +3V Battery Input GND - Ground SDA - Serial Data SCL - Serial ClockSQW/OUT - Square Wave/Output DriverDESCRIPTIONThe DS1307 Serial Real-Time Clock is a low-power, full binary-coded decimal (BCD) clock/calendar plus 56 bytes of NV SRAM. Address and data are transferred serially via a 2-wire, bi-directional bus.The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The end of the month date is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator. The DS1307 has a built-in power sense circuit that detects power failures and automatically switches to the battery supply.DS130764 x 8 Serial Real-Time ClockOPERATIONThe DS1307 operates as a slave device on the serial bus. Access is obtained by implementing a START condition and providing a device identification code followed by a register address. Subsequent registers can be accessed sequentially until a STOP condition is executed. When V CC falls below 1.25 x V BAT the device terminates an access in progress and resets the device address counter. Inputs to the device will not be recognized at this time to prevent erroneous data from being written to the device from an out of tolerance system. When V CC falls below V BAT the device switches into a low-current battery backup mode. Upon power-up, the device switches from battery to V CC when V CC is greater than V BAT + 0.2V and recognizes inputs when V CC is greater than 1.25 x V BAT . The block diagram in Figure 1 shows the main elements of the serial RTC.DS1307 BLOCK DIAGRAMFigure 1TYPICAL OPERATING CIRCUITSIGNAL DESCRIPTIONSV CC, GND – DC power is provided to the device on these pins. V CC is the +5V input. When 5V is applied within normal limits, the device is fully accessible and data can be written and read. When a 3V battery is connected to the device and V CC is below 1.25 x V BAT, reads and writes are inhibited. However, the timekeeping function continues unaffected by the lower input voltage. As V CC falls below V BAT the RAM and timekeeper are switched over to the external power supply (nominal 3.0V DC) at V BAT.V BAT – Battery input for any standard 3V lithium cell or other energy source. Battery voltage must be held between 2.0V and 3.5V for proper operation. The nominal write protect trip point voltage at which access to the RTC and user RAM is denied is set by the internal circuitry as 1.25 x V BAT nominal. A lithium battery with 48mAhr or greater will back up the DS1307 for more than 10 years in the absence of power at 25ºC. UL recognized to ensure against reverse charging current when used in conjunction with a lithium battery.See “Conditions of Acceptability” at /TechSupport/QA/ntrl.htm.SCL (Serial Clock Input) – SCL is used to synchronize data movement on the serial interface.SDA (Serial Data Input/Output) – SDA is the input/output pin for the 2-wire serial interface. The SDA pin is open drain which requires an external pullup resistor.SQW/OUT (Square Wave/Output Driver) – When enabled, the SQWE bit set to 1, the SQW/OUT pin outputs one of four square wave frequencies (1Hz, 4kHz, 8kHz, 32kHz). The SQW/OUT pin is open drain and requires an external pull-up resistor. SQW/OUT will operate with either Vcc or Vbat applied. X1, X2 – Connections for a standard 32.768kHz quartz crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance (CL) of 12.5pF.For more information on crystal selection and crystal layout considerations, please consult Application Note 58, “Crystal Considerations with Dallas Real-Time Clocks.” The DS1307 can also be driven by an external 32.768kHz oscillator. In this configuration, the X1 pin is connected to the external oscillator signal and the X2 pin is floated.RECOMMENDED LAYOUT FOR CRYSTALCLOCK ACCURACYThe accuracy of the clock is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Additional error will be added by crystal frequency drift caused by temperature shifts. External circuit noise coupled into the oscillator circuit may result in the clock running fast. See Application Note 58, “Crystal Considerations with Dallas Real-Time Clocks” for detailed information.Please review Application Note 95, “Interfacing the DS1307 with a 8051-Compatible Microcontroller”for additional information.RTC AND RAM ADDRESS MAPThe address map for the RTC and RAM registers of the DS1307 is shown in Figure 2. The RTC registers are located in address locations 00h to 07h. The RAM registers are located in address locations 08h to 3Fh. During a multi-byte access, when the address pointer reaches 3Fh, the end of RAM space, it wraps around to location 00h, the beginning of the clock space.DS1307 ADDRESS MAP Figure 2CLOCK AND CALENDARThe time and calendar information is obtained by reading the appropriate register bytes. The RTC registers are illustrated in Figure 3. The time and calendar are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in the BCD format. Bit 7 of register 0is the clock halt (CH) bit. When this bit is set to a 1, the oscillator is disabled. When cleared to a 0, the oscillator is enabled.Please note that the initial power-on state of all registers is not defined. Therefore, it is important to enable the oscillator (CH bit = 0) during initial configuration.The DS1307 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12- or 24-hour mode select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10 hour bit (20-23 hours).On a 2-wire START, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to re-read the registers in case of an update of the main registers during a read.00H07H 08H 3FHDS1307 TIMEKEEPER REGISTERSFigure 3CONTROL REGISTERThe DS1307 control register is used to control the operation of the SQW/OUT pin.BIT 7BIT 6BIT 5BIT 4BIT 3BIT 2BIT 1BIT 0OUTSQWERS1RS0OUT (Output control): This bit controls the output level of the SQW/OUT pin when the square wave output is disabled. If SQWE = 0, the logic level on the SQW/OUT pin is 1 if OUT = 1 and is 0 if OUT = 0.SQWE (Square Wave Enable): This bit, when set to a logic 1, will enable the oscillator output. The frequency of the square wave output depends upon the value of the RS0 and RS1 bits. With the square wave output set to 1Hz, the clock registers update on the falling edge of the square wave.RS (Rate Select): These bits control the frequency of the square wave output when the square wave output has been enabled. Table 1 lists the square wave frequencies that can be selected with the RS bits.SQUAREWAVE OUTPUT FREQUENCY Table 1RS1RS0SQW OUTPUT FREQUENCY001Hz 01 4.096kHz 108.192kHz 1132.768kHz00000000000002-WIRE SERIAL DATA BUSThe DS1307 supports a bi-directional, 2-wire bus and data transmission protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS1307 operates as a slave on the 2-wire bus. A typical bus configuration using this 2-wire protocol is show in Figure 4.TYPICAL 2-WIRE BUS CONFIGURATION Figure 4Figures 5, 6, and 7 detail how data is transferred on the 2-wire bus.§Data transfer may be initiated only when the bus is not busy.§During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is high will be interpreted as control signals.Accordingly, the following bus conditions have been defined:Bus not busy: Both data and clock lines remain HIGH.Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.Data valid: The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit. Within the 2-wire bus specifications a regular mode (100kHz clock rate) and a fast mode (400kHz clock rate) are defined. The DS1307 operates in the regular mode (100kHz) only.Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.DATA TRANSFER ON 2-WIRE SERIAL BUS Figure 5Depending upon the state of the R/W bit, two types of data transfer are possible:1.Data transfer from a master transmitter to a slave receiver. The first byte transmitted by themaster is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first.2.Data transfer from a slave transmitter to a master receiver. The first byte (the slave address) istransmitted by the master. The slave then returns an acknowledge bit. This is followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a “not acknowledge” is returned.The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released. Data is transferred with the most significant bit (MSB) first.The DS1307 may operate in the following two modes:1.Slave receiver mode (DS1307 write mode): Serial data and clock are received through SDA andSCL. After each byte is received an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and *direction bit (See Figure 6). The address byte is the first byte received after the start condition is generated by the master. The address byte contains the 7 bit DS1307 address, which is 1101000, followed by the *direction bit (R/W) which, for a write, is a 0. After receiving and decoding the address byte the device outputs an acknowledge on the SDA line. After the DS1307 acknowledges the slave address + write bit, the master transmits a register address to the DS1307 This will set the register pointer on the DS1307. The master will then begin transmitting each byte of data with the DS1307 acknowledging each byte received. The master will generate a stop condition to terminate the data write.DATA WRITE – SLAVE RECEIVER MODE Figure 62.Slave transmitter mode (DS1307 read mode): The first byte is received and handled as in the slavereceiver mode. However, in this mode, the *direction bit will indicate that the transfer direction is reversed. Serial data is transmitted on SDA by the DS1307 while the serial clock is input on SCL.START and STOP conditions are recognized as the beginning and end of a serial transfer (See Figure 7). The address byte is the first byte received after the start condition is generated by the master. The address byte contains the 7-bit DS1307 address, which is 1101000, followed by the *direction bit (R/W) which, for a read, is a 1. After receiving and decoding the address byte the device inputs an acknowledge on the SDA line. The DS1307 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The DS1307 must receive a “not acknowledge” to end a read.DATA READ – SLAVE TRANSMITTER MODE Figure 7ABSOLUTE MAXIMUM RATINGS*Voltage on Any Pin Relative to Ground -0.5V to +7.0VStorage Temperature -55°C to +125°CSoldering Temperature 260°C for 10 seconds DIPSee JPC/JEDEC Standard J-STD-020A forSurface Mount Devices*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.Range Temperature V CCCommercial0°C to +70°C 4.5V to 5.5V V CC1Industrial-40°C to +85°C 4.5V to 5.5V V CC1 RECOMMENDED DC OPERATING CONDITIONS(Over the operating range*) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Supply Voltage V CC 4.5 5.0 5.5VLogic 1V IH 2.2V CC + 0.3VLogic 0V IL-0.5+0.8VV BAT Battery Voltage V BAT 2.0 3.5V*Unless otherwise specified.DC ELECTRICAL CHARACTERISTICS(Over the operating range*) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Input Leakage (SCL)I LI1m AI/O Leakage (SDA &I LO1m ASQW/OUT)Logic 0 Output (I OL = 5mA)V OL0.4VActive Supply Current I CCA 1.5mA7 Standby Current I CCS200m A1 Battery Current (OSC ON);I BAT1300500nA2 SQW/OUT OFFI BAT2480800nABattery Current (OSC ON);SQW/OUT ON (32kHz)Power-Fail Voltage V PF 1.216 x V BAT 1.25 x V BAT 1.284 x V BAT V8*Unless otherwise specified.AC ELECTRICAL CHARACTERISTICS(Over the operating range*) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES SCL Clock Frequency f SCL0100kHzBus Free Time Between a STOP andt BUF 4.7m sSTART ConditionHold Time (Repeated) START Condition t HD:STA 4.0m s3 LOW Period of SCL Clock t LOW 4.7m sHIGH Period of SCL Clock t HIGH 4.0m st SU:STA 4.7m sSet-up Time for a Repeated STARTConditionData Hold Time t HD:DAT0m s4,5 Data Set-up Time t SU:DAT250nsRise Time of Both SDA and SCL Signals t R1000nsFall Time of Both SDA and SCL Signals t F300nsSet-up Time for STOP Condition t SU:STO 4.7m s Capacitive Load for each Bus Line C B400pF6C I/O10pFI/O Capacitance (T A = 25ºC)12.5pFCrystal Specified Load Capacitance(T A = 25ºC)*Unless otherwise specified.NOTES:1.I CCS specified with V CC = 5.0V and SDA, SCL = 5.0V.2.V CC = 0V, V BAT = 3V.3.After this period, the first clock pulse is generated.4. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to theV IHMIN of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.5.The maximum t HD:DAT has only to be met if the device does not stretch the LOW period (t LOW) of theSCL signal.6.C B – Total capacitance of one bus line in pF.7.I CCA – SCL clocking at max frequency = 100kHz.8.V PF measured at V BAT = 3.0V.TIMING DIAGRAM Figure 8DS1307 64 X 8 SERIAL REAL-TIME CLOCK 8-PIN DIP MECHANICAL DIMENSIONSPKG8-PIN DIMMIN MAX A IN.MM0.3609.140.40010.16B IN.MM0.2406.100.2606.60C IN.MM0.1203.050.1403.56D IN.MM0.3007.620.3258.26E IN.MM0.0150.380.0401.02F IN.MM0.1203.040.1403.56G IN.MM0.0902.290.1102.79H IN.MM0.3208.130.3709.40J IN.MM0.0080.200.0120.30K IN.MM 0.0150.380.0210.53DS1307Z 64 X 8 SERIAL REAL-TIME CLOCK8-PIN SOIC (150-MIL) MECHANICAL DIMENSIONSPKG8-PIN (150 MIL)DIM MIN MAXA IN. MM 0.1884.780.1964.98B IN. MM 0.1503.810.1584.01C IN. MM 0.0481.220.0621.57E IN. MM 0.0040.100.0100.25F IN. MM 0.0531.350.0691.75G IN. MM 0.050 BSC1.27 BSCH IN. MM 0.2305.840.2446.20J IN. MM 0.0070.180.0110.28K IN. MM 0.0120.300.0200.51L IN. MM 0.0160.410.0501.27phi0°8°56-G2008-001。

zl38005中文资料_数据手册_IC数据表