多时钟系统设计

基于51单片机的多功能电子钟设计

基于51单片机的多功能电子钟设计1. 本文概述随着现代科技的发展,电子时钟已成为日常生活中不可或缺的一部分。

本文旨在介绍一种基于51单片机的多功能电子钟的设计与实现。

51单片机因其结构简单、成本低廉、易于编程等特点,在工业控制和教学实验中得到了广泛应用。

本文将重点阐述如何利用51单片机的这些特性来设计和实现一个具有基本时间显示、闹钟设定、温度显示等功能的电子钟。

本文的结构安排如下:将详细介绍51单片机的基本原理和特点,为后续的设计提供理论基础。

接着,将分析电子钟的功能需求,包括时间显示、闹钟设定、温度显示等,并基于这些需求进行系统设计。

将详细讨论电子钟的硬件设计,包括51单片机的选型、时钟电路、显示电路、温度传感器电路等。

软件设计部分将介绍如何通过编程实现电子钟的各项功能,包括时间管理、闹钟控制、温度读取等。

本文将通过实验验证所设计的电子钟的功能和性能,并对实验结果进行分析讨论。

通过本文的研究,旨在为电子钟的设计提供一种实用、经济、可靠的方法,同时也为51单片机的应用提供一个新的实践案例。

2. 51单片机概述51单片机,作为一种经典的微控制器,因其高性能、低功耗和易编程的特性而被广泛应用于工业控制、智能仪器和家用电器等领域。

它基于Intel 8051微处理器的架构,具备基本的算术逻辑单元(ALU)、程序计数器(PC)、累加器(ACC)和寄存器组等核心部件。

51单片机的核心是其8位CPU,能够处理8位数据和执行相应的指令集。

51单片机的内部结构主要包括中央处理单元(CPU)、存储器、定时器计数器、并行IO口、串行通信口等。

其存储器分为程序存储器(ROM)和数据存储器(RAM)。

程序存储器通常用于存放程序代码,而数据存储器则用于存放运行中的数据和临时变量。

51单片机还包含特殊功能寄存器(SFR),用于控制IO端口、定时器计数器和串行通信等。

51单片机的工作原理基于冯诺伊曼体系结构,即程序指令和数据存储在同一块存储器中,通过总线系统进行传输。

多功能电子时钟实训报告

一、实训目的本次实训旨在通过学习单片机技术,设计并实现一个基于单片机的多功能电子时钟系统。

通过实训,使学生掌握以下知识和技能:1. 熟悉单片机的基本原理和编程方法;2. 掌握电子时钟系统的硬件设计、软件编程和调试方法;3. 提高动手能力和实际应用能力。

二、实训内容1. 系统硬件设计(1)核心控制器:选用AT89C51单片机作为系统的核心控制器。

(2)时钟芯片:使用DS1302实时时钟芯片,提供精确的时间信号。

(3)液晶显示屏:选用1602液晶显示屏,用于显示时间、日期、温度等信息。

(4)按键模块:设计包含时间设置键、日期设置键、闹钟设置键等的按键模块。

(5)温度传感器:使用DS18B20温度传感器,用于检测环境温度。

(6)电源模块:为整个系统提供稳定的工作电压。

2. 系统软件设计(1)主程序:负责系统初始化、时钟显示、闹钟提醒、温度检测等功能。

(2)中断程序:负责时钟中断、闹钟中断、温度中断等。

(3)显示程序:负责液晶显示屏的显示内容更新。

(4)按键处理程序:负责按键扫描、按键消抖、按键功能处理等。

三、实训过程1. 硬件搭建(1)根据设计图纸,焊接电路板。

(2)连接单片机、时钟芯片、液晶显示屏、按键模块、温度传感器和电源模块。

(3)检查电路连接是否正确,确保系统硬件正常工作。

2. 软件编程(1)编写主程序、中断程序、显示程序和按键处理程序。

(2)使用C语言进行编程,并利用Keil软件进行编译。

(3)将编译好的程序烧录到单片机中。

3. 调试与优化(1)在Proteus仿真软件中,对系统进行仿真调试。

(2)检查程序运行是否正常,优化程序代码。

(3)对硬件电路进行调整,确保系统稳定运行。

四、实训结果1. 系统功能实现(1)显示当前时间、日期和温度。

(2)设置闹钟时间,并在设定时间响起。

(3)计时器功能,可以记录时间。

(4)温度检测功能,实时显示环境温度。

2. 系统稳定性通过仿真和实际测试,系统稳定运行,满足设计要求。

时钟系统设计及仿真

黑龙江科技学院 综合性、设计性实践报告实践项目名称时钟系统设计及仿真所属课程名称ASIC实践日期2011.9.13-2011.9.16班级学号姓名成绩电气与信息工程学院实践基地实践概述:【实践目的及要求】实践目的:1、学习软件Max+plusⅡ的使用方法;2、掌握使用Max+plusⅡ进行编译和仿真的方法与技巧;3、掌握基本的VHDL语言并编写程序4、了解实践箱的各部分基本构造并使用它完成程序下载。

实验要求:1、应用VHDL语言设计一个具有时、分、秒功能的计时系统。

2、应用Max+plusⅡ开发进行编译,仿真,装配,并下载到实践箱。

3、计时系统可采用模块设计,并连接成顶层原理图。

4.可自行扩展功能。

【实践环境】(使用的软件)Max+plusⅡ【实验原理】实践内容:clkset:in std_logic;setmin:in std_logic;reset:in std_logic;secout:out STD_LOGIC_vector(6 downto 0);enmin:out std_logic);end xsecond1;architecture xsecond_arch of xsecond1 issignal sec:STD_LOGIC_vector(6 downto 0);signal sec1:STD_LOGIC;signal emin:STD_LOGIC;beginprocess(reset,sec,emin,setmin,clkset)beginif reset ='0' thenenmin<='0';secout<="0000000";sec1<='0';elsesec1<='1';secout<=sec;if clkset='1'and clkset'event thenif setmin='0' thenenmin<='1';elseenmin<=emin;end if;end if;end if;end process;process(clk,sec1)alias lcount:std_logic_vector(3 downto 0)is sec(3 downto 0); alias hcount:std_logic_vector(2 downto 0)is sec(6 downto 4); beginif sec1='0' thensec<="0000000";elseif (clk='1'and clk'event)thenif lcount=9 thenlcount<="0000";if hcount/=5 thenhcount<=hcount+1;elsehcount<="000";emin<='1';end if;elselcount<=lcount+1;emin<='0';end if;end if;end if;end process;end xsecond_arch;分60程序如下:Library ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_arith.ALL;USE ieee.std_logic_unsigned.ALL;entity xminute isport(clk:in std_logic;clkmin:in std_logic;sethour:in std_logic;reset:in std_logic;minout:out STD_LOGIC_vector(6 downto 0); enhour:out std_logic);end xminute;architecture xminute_arch of xminute issignal min:STD_LOGIC_vector(6 downto 0);signal ehour:STD_LOGIC;signal min1:STD_LOGIC;beginprocess(reset,clk,sethour,min,ehour)beginif reset ='0' thenenhour<='0';minout<="0000000";min1<='0';elsemin1<='1';if clk='1'and clk'event thenif sethour='0' thenenhour<='1';elseenhour<=ehour;end if;end if;end if;end process;process(clkmin,min1)alias lcountm:std_logic_vector(3 downto 0)is min(3 downto 0); alias hcountm:std_logic_vector(2 downto 0)is min(6 downto 4); beginif min1='0' thenmin<="0000000";elseif (clkmin='1'and clkmin'event)thenif lcountm=9 thenlcountm<="0000";if hcountm/=5 thenhcountm<=hcountm+1;ehour<='0';elsehcountm<="000";ehour<='1';end if;elselcountm<=lcountm+1;ehour<='0';end if;end if;end if;end process;end xminute_arch;时程序如下:Library ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_arith.ALL;USE ieee.std_logic_unsigned.ALL;entity xhour isport(clkhour:in std_logic;reset:in std_logic;hourout:out STD_LOGIC_vector(5 downto 0));end xhour;architecture xhour_arch of xhour issignal hour:STD_LOGIC_vector(5 downto 0);beginprocess(reset,clkhour,hour)alias lcount:std_logic_vector(3 downto 0)is hour(3 downto 0); alias hcount:std_logic_vector(1 downto 0)is hour(5 downto 4); beginif reset='0' thenhourout<="000000";hour<="000000";elseif (clkhour='1'and clkhour'event)thenif lcount=9 thenlcount<="0000";hcount<=hcount+1;elseif hour="100011"thenhour<="000000";elselcount<=lcount+1;end if;end if;end if;hourout<=hour;end if;end process;end xhour_arch;分时设定程序:Library ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_arith.ALL;USE ieee.std_logic_unsigned.ALL;entity xsettime isport(reset:in std_logic;hour:in STD_LOGIC_vector(5 downto 0);min:in STD_LOGIC_vector(6 downto 0);sec:in STD_LOGIC_vector(6 downto 0);clk:in std_logic;sel:out STD_LOGIC_vector(2 downto 0);d_out:out STD_LOGIC_vector(3 downto 0)); end xsettime;architecture xsettime_arch of xsettime issignal sel1: STD_LOGIC_vector(2 downto 0); beginprocess(clk,reset,sel1,hour,min,sec)beginif reset='0' thensel<="000";d_out<="0000";sel1<="000";elseif (clk='1'and clk'event)thenif sel1<5 thensel1<=sel1+1;elsesel1<="000";end if;end if;sel<=sel1;case sel1 iswhen "000"=>d_out(3)<='0';d_out(2)<='0';d_out(1)<=hour(5);d_out(0)<=hour(4);when "001"=>d_out<=hour(3 downto 0);when "010"=>d_out(3)<='0';d_out(2)<=min(6);d_out(1)<=min(5);d_out(0)<=min(4);when "011"=>d_out<=min(3 downto 0);when "100"=>d_out(3)<='0';d_out(2)<=sec(6);d_out(1)<=sec(5);d_out(0)<=sec(4);when "101"=>d_out<=sec(3 downto 0);when others=>null;end case;end if;end process;end xsettime_arch;显示模块程序:Library ieee;USE ieee.std_logic_1164.ALL;entity xdeled isport(d_in:in STD_LOGIC_vector(3 downto 0); a:out std_logic;b:out std_logic;c:out std_logic;d:out std_logic;e:out std_logic;f:out std_logic;g:out std_logic);end xdeled;architecture xdeled_arch of xdeled isbeginprocess(d_in)type data_out is array(0 to 6)of std_logic; variable outp:data_out;begincase d_in iswhen "0000"=>outp:="1111110";when "0001"=>outp:="0110000";when "0010"=>outp:="1101101";when "0011"=>outp:="1111001";when "0100"=>outp:="0110011";when "0101"=>outp:="1011011";when "0110"=>outp:="1011111";when "0111"=>outp:="1110000";when "1000"=>outp:="1111111";when "1001"=>outp:="1111011";when "1010"=>outp:="1110111";when "1011"=>outp:="0011111";when "1100"=>outp:="1001110";when "1101"=>outp:="0111101";when "1110"=>outp:="1001111";when "1111"=>outp:="1000111";when others=>null;end case;a<=outp(0);b<=outp(1);c<=outp(2);d<=outp(3);e<=outp(4);f<=outp(5);g<=outp(6);end process;end xdeled_arch;指示灯与报警模块程序:Library ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_arith.ALL;USE ieee.std_logic_unsigned.ALL;entity xalert isport(clk:in std_logic;d_in:in STD_LOGIC_vector(6 downto 0);speak:out std_logic;d_out:out STD_LOGIC_vector(2 downto 0)); end xalert;architecture xalert_arch of xalert istype state is(s1,s2,s3,s4);signal next_state,current_state:state;beginprocess(clk,current_state,d_in)beginif d_in/="0000000" thenspeak<='0';next_state<=s1;current_state<=s1;d_out<="000";elseif (clk='1'and clk'event)thenspeak<='1';current_state<=next_state;end if;case current_state iswhen s1=>d_out<="000";next_state<=s2;when s2=>d_out<="001";next_state<=s3;when s3=>d_out<="010";next_state<=s4;when s4=>d_out<="100";next_state<=s1;when others=>d_out<="000";null;end case;end if;end process;end xalert_arch;分频模块程序:library ieee;use ieee.std_logic_1164.all;entity d_time isport(clk:in std_logic;qlk:out std_logic);end d_time;architecture d_time of d_time issignal x:std_logic;beginprocess(clk)variable cnt:integer range 0 to 77; beginif clk'event and clk='1'thenif cnt<77 thencnt :=cnt+1;elsecnt:=0;x<=not x;end if;end if;qlk<=x;end process;end d_time;【实践过程】(实践步骤、记录、数据、分析)1、完成各个模块程序的调试编译利用所得的图完成系统的设计结果如原理图所示,该系统的输入信号为时钟信号、被测频率输入信号、数码管7个段位数码管段位译码输出信号。

多功能数字电子钟_VHDL

四、各功能模块的源程序代码 :

-- CONTOR 模块 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity contor is

1 )“小时” 校时状态: 进入“小时”校时状态后,显示 “小时” 的数码管闪烁,每按动“ k” 键一次,“小时” +1,若不按动“ k”键 则小时数不变,一直按下“ k” 键则小时数一 4Hz 的频率递增计数。

2 )“分”校时状态:进入“分”校时状态后,显示“分”的数 码管闪烁,每按动“ k” 键一次,“分” +1,若不按动“ k”键则分数 不变,一直按下“ k” 键则分数一 4Hz的频率递增计数。

chs,cms,css,f4 :in std_logic; bsg,bmg,bhg,bsd,bmd,bhd :buffer std_logic_vector(3 downto 0); comout :out std_logic); end time_com; architecture time_comx of time_com is begin com:process(hh,mh,sh,hl,ml) begin if(bhg=hh and bhd=hl and bmg=mh and bmd=ml and bsg=sh)then comout<='1'; else comout<='0'; end if; end process; set:process(f4) begin if(f4'event and f4='1')then if(chs='1'and k='0')then if(bhg="0010" and bhd="0011")then bhd<="0000";bhg<="0000"; elsif(bhd="1001")then bhd<="0000";bhg<=bhg+1; elsif(bhd="0000"or bhd="0001" or bhd="0010"or bhd="0011"or bhd="0100"or bhd="0101"or bhd="0110"or bhd="0111"or bhd="1000")then bhd<=bhd+1; end if; end if; end if; end process; process(f4) begin if(f4'event and f4='1')then if(cms='1'and k='0')then if(bmg="0101" and bmd="1001")then

时钟系统方案

时钟系统方案第1篇时钟系统方案一、方案背景随着信息化建设的不断深入,时钟系统已成为各类业务系统中不可或缺的组成部分。

为确保业务数据的准确性和系统运行的稳定性,需建立一套合法合规的时钟系统方案,以实现各系统间的时间同步和统一管理。

二、方案目标1. 确保时钟系统合法合规,遵循国家相关法律法规和行业标准。

2. 实现各业务系统间的时间同步,保证数据的一致性和准确性。

3. 提高时钟系统的可靠性和稳定性,降低系统故障风险。

4. 方便时钟系统的管理和维护,降低运维成本。

三、方案设计1. 时钟源选择采用我国国家标准时间源(如国家授时中心),确保时钟源的准确性和可靠性。

2. 时钟同步协议采用NTP(网络时间协议)或PTP(精确时间协议)等国际通用的时间同步协议,实现各业务系统间的时间同步。

3. 系统架构采用分布式架构,分为时钟源、时钟服务器、时钟客户端三级,确保时钟系统的可扩展性和高可用性。

4. 时钟服务器时钟服务器负责接收时钟源的时间信息,并进行本地时间同步。

建议采用双机热备的配置,提高系统可靠性。

5. 时钟客户端时钟客户端部署在各业务系统服务器上,定期从时钟服务器获取时间信息,实现业务系统的时间同步。

6. 网络设计采用专用网络或虚拟专用网络(VPN)实现时钟系统的数据传输,确保数据安全和传输效率。

7. 安全防护针对时钟系统进行安全防护,包括防火墙、入侵检测、数据加密等,确保系统安全。

四、实施步骤1. 需求分析调研现有业务系统对时钟系统的需求,明确时钟同步的范围、精度等要求。

2. 方案设计根据需求分析,设计时钟系统方案,包括硬件设备选型、软件配置、网络架构等。

3. 设备采购与安装采购符合国家标准的时钟设备,进行安装、调试,确保设备正常运行。

4. 系统部署按设计方案部署时钟系统,包括时钟源、时钟服务器、时钟客户端等。

5. 测试验证对时钟系统进行功能测试、性能测试、安全测试等,确保系统满足业务需求。

6. 培训与交付对运维人员进行时钟系统的培训,确保其具备管理和维护能力。

基于STC89C52多功能电子时钟系统程序+原理图

一、设计任务设计制作一台以控制器为核心的多功能电子时钟系统二、设计要求:①.系统具有3种工作模式状态(正常时钟显示模式、系统校准模式、秒表计时模式);系统所有功能,均能够通过上位PC机对其操作修改与实时动态显示。

(PC主机端可利用高级语言进行人机界面设计)②.在正常时钟显示模式时,时钟具有显示年、月、日、时、分、秒的功能。

③.在正常时钟显示模式时,系统具有整点报时的功能,在离整点前10秒时,自动发出鸣叫声,步长1秒,每间隔1秒鸣叫一次,前4响是低音,后1响为高音,共鸣叫5次,最后1响结束时为整点。

高音频率为1KHz;④.在系统校准模式时,系统具有快速校准时间的功能。

⑤.在秒表计时模式时,可兼做比赛时间记录表。

秒表记时的精度为0.1秒,由3个键分别控制秒表的启动、清零、记录功能,可连续记录3组时间,并能够显示记录时间。

⑥.系统显示器采用LCD液晶显示器1602或其它显示器件,并采用键盘对相关数据进行设置与操作。

原理图设计制作一台以控制器为核心的多功能电子时钟系统二、设计要求:①.系统具有3种工作模式状态(正常时钟显示模式、系统校准模式、秒表计时模式);系统所有功能,均能够通过上位PC机对其操作修改与实时动态显示。

(PC主机端可利用高级语言进行人机界面设计)(注:此三种模式可以通过SET键盘来回切换,在正常时钟模式,第二排显示S:time,校准模式显示S:adjst,秒表模式,是TN~T3:四个秒表模式);②.在正常时钟显示模式时,时钟具有显示年、月、日、时、分、秒的功能。

(注:这个已经全部显示了,含星期)③.在正常时钟显示模式时,系统具有整点报时的功能,在离整点前10秒时,自动发出鸣叫声,步长1秒,每间隔1秒鸣叫一次,前4响是低音,后1响为高音,共鸣叫5次,最后1响结束时为整点。

高音频率为1KHz;(注:这个都实现了,要验证的话就是将时钟调整到59分后验证即可)④.在系统校准模式时,系统具有快速校准时间的功能。

时钟同步系统方案设计分享

时钟同步系统在福建某通信局投入使用由我公司自主研发生产的一套时钟同步系统在福建某通信局成功投入使用。

本次时钟同步系统,主要是根据福建某通信局发展需要,应对项目实施需求,具有针对性的配置的一套完整的时钟同步系统,分享如下:

1.时钟同步系统的需求原因

应对通信局客户对北斗GPS时钟同步系统的需求逐渐增多,现有槽道已无法满足未来的客户需求,后期运行也大大增加施工安全隐患。

经过市场调研,选由我公司自行配置一套北斗GPS时钟同步系统,要求各网段授时设备独立运行,可供多用户共同使用,同时楼顶线路只允许架设1套GPS北斗卫星天线。

2.时钟同步系统的配置方案

因工程配置的局限性,本次时钟同步系统需求配置6台北斗GPS

时钟同步设备,且只能共用一套卫星天线,因此我们在系统内配置了GPS北斗双模有源分配器将其分开,具体连接方式如下图:

时钟同步系统配置方案

3.时钟同步系统的授时方法(同步科技,小安,189********(微信同

时钟同步系统整体采用NTP授时方式,需要同步时间的授时终端,通过获取时间同步设备的IP地址,来实现局域网内所有网络设备

的时间统一,网络配置图如下所示:

时钟同步系统的网络配置图

4.时钟同步系统配置清单

鉴于以上需求,配置1套完整的时钟同步系统,清单如以下表格:

高精确的时间对于通信局系统的正常运行有着十分重要的意义,

本次时间同步系统主要是基于GPS北斗的时间同步系统,

能够实时地对主站计算机终端时间进行校正, 目前在通信局配置有着很大的需要。

以上为此次给通信局配置的时间同步系统的一个说明,相关用户可作为参考。

时钟系统施工方案

时钟系统施工方案时钟系统是指将时间信号通过有线或无线方式传输给各个时钟终端,实现时间同步显示的系统。

在不同的场所中,如学校、医院、商场、企事业单位等,都需要一个准确可靠的时钟系统来保证时间的同步和统一。

施工方案:一、系统设计:1. 需求调研:根据客户的需求和场所的特点,了解系统所需的功能和性能要求,进行需求调研。

2. 系统布局:根据场地平面图,确定时钟布放的位置,考虑信号传输距离和传输方式,合理布局时钟终端的位置。

3. 选型设计:根据场所要求和预算限制,选择合适的时钟终端、服务器和信号传输设备等。

4. 系统联网:根据现场情况确定有线或无线网络方案,将时钟系统与现有网络进行连接。

5. 系统配置:根据客户要求,对时钟终端进行设置和调试,确保时间同步和显示的准确性。

二、施工准备:1. 材料准备:准备所需的时钟终端、服务器、信号传输设备、布线材料等,确保施工的顺利进行。

2. 确定施工人员:根据施工需要,确定施工人员的数量和技术水平,保证施工的质量和进度。

3. 施工工具:准备各种必要的施工工具,如电钻、电缆剥皮器等,方便施工人员进行安装和调试。

三、施工步骤:1. 安装时钟终端:根据布局设计,将时钟终端按照规定的位置安装到墙壁上或悬挂在天花板上。

2. 布线连接:根据系统设计,将时钟终端与服务器、信号传输设备进行布线连接,保证信号的传输畅通。

3. 联网设置:对服务器进行设置和调试,使其能够正确接收时间信号并通过网络传输给时钟终端。

4. 确认同步:观察各个时钟终端的显示,在不同位置和距离下确认时间的同步和显示准确性。

5. 系统调试:对整个时钟系统进行功能和性能的调试,确保系统运行稳定和可靠。

四、施工验收:1. 功能测试:对时钟系统进行功能测试,如时间同步、显示准确性等,确保系统满足设计要求。

2. 效果评估:根据客户的评估标准,评估时钟系统在实际使用中的效果和用户体验。

3. 验收交付:满足客户要求的情况下,进行系统的验收和交付,完成时钟系统的施工任务。

毕业设计---基于STC89C52RC单片机多功能时钟设计论文

多功能数字钟设计报告目录第一部分摘要 (4)第二部分1.设计任务 (4)1.1基本要求 (4)1.2发挥部分 (4)1.3创新部分 (4)2.方案论证与比较 (4)2.1显示部分 (4)2.2数字时钟 (4)2.3温度采集 (5)2.4闹铃部分 (5)2.5电源模块 (5)3.总体方案 (5)3.1工作原理 (5)3.2总体设计 (5)4.系统硬件设计 (6)4.1 STC89C52RC单片机最小系统 (6)4.2测温模块 (6)4.3时钟模块 (7)4.4存储器模块 (7)4.5 LCD显示模块 (8)4.6电源模块 (8)4.7整体电路 (8)5.系统软件设计 (9)5.1主程序流程 (9)5.2时间设定程序流程 (10)5.3温度测量程序流程 (10)5.4闹铃设定程序流程 (11)5.5生日设定程序流程 (11)6.测试与结果分析 (12)6.1基本部分测试与分析 (12)6.2发挥部分测试与分析 (12)6.3创新部分测试与分析 (12)7.设计总结 (12)8.参考资料 (13)附录 (14)附一 (14)获取时钟芯片DS1302时间信息的程序 (14)附二 (15)多功能数字时钟使用方法 (15)摘要本设计采用LCD液晶屏幕显示系统,以STC89C52RC单片机为核心,由键盘、温度采集、定时闹铃、日期提醒等功能模块组成。

基于题目基本要求,本系统对时间显示、闹铃方式进和温度采集系统行了重点设计。

此外,扩展了整点报时、非易失闹铃信息存储、国内外重要节日提醒等功能。

本系统大部分功能由软件来实现,吸收了硬件软件化的思想,大部分功能通过软件来实现,使电路简单明了,系统稳定性大大提高。

本系统不仅成功的实现了要求的基本功能,多数发挥部分也得到了实现,而且还具有一定的创新功能。

关键字:STC89C52RC单片机、LCD液晶显示、双电源供电、温度采集、非易失定时闹铃、生日提醒、重要节日提醒、整点报时1、任务设计1.1基本要求:设计并制作一个多功能数字钟。

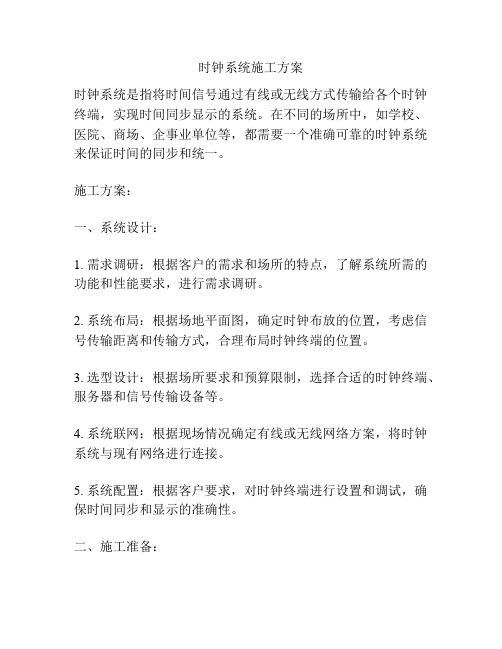

1-1数字钟的系统框图2、设计提示

教材:《VHDL硬件描述语言与数字逻辑电路设计》候伯亨 顾新西安电子科技大学参考书:《EDA与数字系统设计》李国丽等机械工业出版社一、多功能数字钟的设计1、数字系统设计问题设计一个能进行时、分、秒计时的12h制或24h制的数字钟,并具有定时与闹钟功能,能在设定的时间发出闹铃音,能非常方便地对时、分和秒进行手动调节,以校准时间,每逢整点.产生报时音报时。

其系统框图如图1-1所示。

1-1数字钟的系统框图2、设计提示此设计问题可分为主控电路、计数器模块和扫描显示三大部分,其中计数器部分的设计是已经非常熟悉的问题,只要掌握六十进制、十二进制的计数规律,用同步计数或异步计数都可以实现,扫描显示模块也已经介绍过,所以主控电路中各种特殊功能的实现是这个设计问题的关键。

用两个电平信号A、B进行模式选择,其中,AB=00为模式0,系统为计时状态;AB =01为模式1,系统为手动校时状态;AB=10为模式2,系统为闹钟设置状态。

设置一个turn信号,当turn=0时,表示在手动校对时,选择调整分部分;当turn=1 时,表示在手动校对时,选择调整时部分。

设置一个change信号,在手动校时或闹钟设置模式下,每按一次,计数器加1。

设置一个reset信号,当reset=0时,整个系统复位;当reset=1时,系统进行计时或其他特殊功能操作。

设置一个关闭闹钟信号reset1,当reset1=0时,关闭闹铃信号:reset1=1可对闹铃进行设置。

设置状态显示信号(发光二极管):LD_alert指示是否设置了闹铃功能;LD_h指示当前调整的是时信号;LD_m指示当前调整的是分信号。

当闹铃功能设置后(LD_atert=1,系统应启动一个比较电路,当计时与预设闹铃时间相等时,启动闹铃声,直到关闭闹铃信号有效。

整点报时由分和秒计时同时为0〔或60)启动,与闹铃声共用一个扬声器驱动信号out。

系统计时时钟为clk=1Hz,选择另—个时钟clk_1k=1024Hz作为产生闹铃声、报时音的时钟信号。

课程设计(论文)基于lcd液晶显示的多功能数字钟的设计(附pcb图及电路原理图)

目录1前言 (1)2总体方案设计 (2)2.1设计内容 (2)2.2设计内容 (2)2.3方案论证 (3)2.4方案选择 (4)3单元模块设计 (5)3.1各单元模块功能介绍及电路设计 (5)3.1.1 温度采集电路 (5)3.1.2 DS1302时钟电路 (5)3.1.3 串行通信接口电路 (6)3.1.4 USB连接电路 (6)3.1.5 按键电路 (7)3.1.6液晶显示显示电路 (7)3.2特殊器件介绍 (7)3.2.1 STC89C52单片机芯片 (7)3.2.2 DS1302介绍 (8)3.2.3 温度传感器DS18B20 (9)3.2.4 液晶显示LCD1602 (9)4软件设计 (10)4.1软件选择 (10)4.2软件设计流程 (10)4.2.1 温度采集流程 (11)4.2.2 日期数据处理流程 (12)5系统的仿真及调试 (13)5.1系统仿真 (13)5.2硬件调试 (13)5.3软件调试 (14)6结论 (16)7总结与体会 (17)7.1设计小结 (17)7.2设计收获及改进 (17)7.3致谢 (17)8参考文献 (18)附录: (19)1前言单片机是指一个集成在一块芯片上的完整计算机系统。

尽管他的大部分功能集成在一块小芯片上,但是它具有一个完整计算机所需要的大部分部件:CPU、内存、内部和外部总线系统,目前大部分还会具有外存。

同时集成诸如通讯接口、定时器,实时时钟等外围设备。

而现在最强大的单片机系统甚至可以将声音、图像、网络、复杂的输入输出系统集成在一块芯片上。

单片机也被称为微控制器(Microcontroller),它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

概括的讲:一块芯片就成了一台计算机。

它的体积小、质量轻、价格便宜、为学习、应用和开发提供了便利条件。

单片机诞生于20世纪70年代末,经历了SCM、MCU、SOC三大阶段。

STC单片机完全兼容51单片机,并有其独到之处,其抗干扰性强,加密性强,超低功耗,可以远程升级,内部有专用复位电路,价格也较便宜,由于这些特点使得 STC 系列单片机的应用日趋广泛。

单片机课程设计 多功能数字钟的设计

摘要电子钟在日常生活中最常见,应用也最广泛。

作为一种定时工具被广泛的使用在生产生活的各方面。

人类最初依靠太阳的角度来进行定时,所以受天气的影响比较大,为了克服依靠自然现象定时的缺点人们发明的机器钟表,电子钟表一系列的定时工具。

而电子钟表具有价格便宜,质量轻,定时误差小等优点,被广泛的应用在生产,生活的各个方面。

由于电子钟的能提供精确定时又被广泛的运用在测量之中。

此电子钟采用单片机进行设计,8 段数码通过单片机进行刷新显示。

其设计的产品除了单片机之外没有用到其他集成块,使其成本可以大大降低,而其便于维修。

成品可以被广泛的用于公共场所,匾额装饰,以及教案等方面。

本文主要就是设计一款数字钟, AT89C51 单片机为核心,以配备 LED 显示模块、键盘输入模块、等功能模块。

数字钟采用 24 小时制方式显示时间,定时信息以及年月日显示等功能。

文章的核心主要从硬件设计和软件编程两个大的方面。

1目录摘要...... 1 1 设计要求及方案确定...... 3 1.1 设计要求...... 3 1.2 方案确定...... 3 2 硬件电路设计及描述...... 3 2.1 确定元器件的型号及参数...... 3 2.1.1 单片机的选择...... 3 2.1.2 AT89C51 单片机的介绍...... 5 2.1.3 LED 数码管显示模块...... 7 2.1.4 键盘输入模块 (8)2.1.5 闹铃模块...... 8 2.1.6 电源电路...... 8 2.1.7 蜂鸣器的介绍...... 9 2.2 硬件电路图 (10)3 软件设计...... 10 3.1 程序结构设计...... 10 3.1.1 程序结构...... 10 3.1.2 主要程序模块清单...... 11 3.2 程序...... 14 4 参考文献...... 17 结束语 (18)211.1 设计要求设计要求及方案确定利用单片机设计制作具有下列功能的数字钟:①自动计时,由 6 位 LED 显示器显示时、分和秒②具备调整功能,可以直接由 0~9 数字键设置当前时间;③具备定时闹钟功能。

使用Quartus进行多功能数字钟设计

.EDA设计使用Quartus II进行多功能数字钟设计院系:机械工程专业:车辆工程姓名:张小辉学号:115101000151指导老师:蒋立平、花汉兵时间:2016年5月25日摘要本实验是电类综合实验课程作业,需要使用到QuartusⅡ软件,(Quartus II 是Altera公司的综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程)。

本实验需要完成一个数字钟的设计,进行试验设计和仿真调试,实验目标是实现计时、校时、校分、清零、保持和整点报时等多种基本功能,并下载到SmartSOPC实验系统中进行调试和验证。

关键字:电类综合实验QuartusⅡ数字钟设计仿真AbstractThis experiment is electric comprehensive experimental course work and need to use the Quartus II software, Quartus II is Altera integrated PLD / FPGA development software, schematic and VHDL, Verilog HDL and AHDL (Altera hardware description language support) etc. a variety of design input form, embedded in its own synthesizer and simulator can complete hardware configuration complete PLD design process from design entry to). The need to complete the design of a digital clock, and debug the design of experiment and simulation, the experimental goal is to achieve timing, school, reset, keep and the whole point timekeeping and other basic functions, and then download to the smartsopc experimental system debugging and validation.Key words: Electric power integrated experiment Quartus II Digital clock design Simulation目录EDA设计 (1)摘要 (2)目录 (4)一、设计要求[1] (5)二、工作原理[2] (6)三、各模块说明[3] (7)1、分频模块 (7)2、计时模块 (9)3、动态显示模块[3] (11)4、校分与校时模块 (11)5、清零模块 (13)6、保持模块 (13)7、报时模块 (13)四、总电路的形成 (15)五、调试、编程下载 (16)六、试验中出现的问题及解决办法 (17)七、实验收获与感受 (18)八、参考文献 (19)一、设计要求[1]1.设计一个数字计时器,可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、清零、快速校时、快速校分、整点报时等基本功能。

时钟系统设计实验报告

时钟系统设计实验报告1. 实验目的本实验的主要目的是设计和实现一个时钟系统,实现对时钟时间的显示、调节和闹钟功能的控制。

2. 实验原理时钟系统由微控制器、显示模块、按键模块、计时模块和闹钟模块组成。

其中,微控制器负责控制整个系统的运行,显示模块用于显示当前的时间,按键模块用于调节时钟和闹钟的时间,计时模块用于计时,闹钟模块用于设置和响铃闹钟。

3. 实验器材本实验所需要的器材如下:- 微控制器(例如Arduino Uno)- 4位7段LED显示模块- 按键模块- 电阻、电容等元件- 杜邦线、面包板等实验连接线材4. 实验步骤4.1 硬件连接首先,将显示模块与微控制器连接起来。

根据显示模块的引脚定义,将其与微控制器的IO口相连。

然后,连接按键模块。

按键模块通常有四个引脚,将其与微控制器的IO口相连。

最后,将定时器和闹钟模块与微控制器连接起来,确保能够通过微控制器控制闹钟的设置和响铃。

4.2 软件编程在编程软件中,编写控制时钟系统的代码。

在代码中,需要实现读取按键状态、显示时间、闹钟设置和响铃等功能。

可以使用Arduino开发环境编写代码,并通过串口监视器进行调试。

4.3 测试与调试将程序烧录至微控制器后,通过连接电源,测试时钟系统的各项功能。

可以通过按下按键,调节时间和设置闹钟,并观察显示模块和闹钟模块的反应。

根据实际情况,对代码进行调试,确保时钟系统的各项功能都能正常运行。

5. 实验结果经过测试与调试,时钟系统能够正常显示当前时间,并能通过按键调节时间。

闹钟模块也能够正常设置和响铃,并且在响铃时,能够通过按键停止闹钟。

整个时钟系统运行稳定,能够满足基本的时钟显示和闹钟功能需求。

6. 实验总结通过本次实验,我们设计并实现了一个基本的时钟系统。

通过掌握了硬件的连接和编程技巧,我们能够很好地控制和调节时钟的显示和闹钟的设置。

实验过程中,我们也遇到了不少问题和困难,但通过思考和调试,最终解决了这些问题。

本次实验还可以进一步拓展,例如添加温湿度传感器,实现温湿度显示功能;或者添加无线通信模块,实现时间同步和远程控制等功能。

基于多时钟源的时间同步系统设计与应用

XU a —u B o l o .ZHA NG o n n 。 Da — o g ,YUAN e — u n W ng a g ,

DE n — ig ,L U o gj n , NG Xigxn 。 I T n - YU eh i u Yu —a

26

电

力

科

学

与

技

术

学

报

2 1 年 9月 01

随着 电力 系统覆 盖范 围越 来越 广 , 自动 化装 置

差就能得 到精 确 的 UT 所 以影 响北斗 卫 星系统 授 C,

时精度 的关键 是信 号 传 输 时延 的计 算 . 常 计算 时 通 延 的方 法有 单 向授 时和 双 向授 时.

关 键 词 : 多时钟源对时 ;P ; ; G s北斗 时间同步 系统

中 图分类号 : N 1. T g93 4

文 献标识 码 : A

文 章编号 :6394 (010—05 5 17—1021)302— 0

De i n a d a lc to f tm e s nc 0 i a i n s g n pp i a i n o i y hr n z tO

的应用 越来 越普 及 , 仅 传统 的电 力 自动 化设 备具 不

有 时 间同步 的需 求 , 且 同步相位 测量 、 而 行波 测距 和

行 波保 护等 设备 对 时间 同步精度 要求也 提高 到 了微

秒级 的需求 . 各种 时 间同步技 术 中 , 星授时 由于 在 卫

北斗单 向授 时 是一 种 元 源 授 时方 法 , 常应 用 通

多功能电子时钟毕业论文设计

多功能电子时钟毕业论文设计目录摘要 ................................................... 错误!未定义书签。

Abstract ................................................. 错误!未定义书签。

绪论 .. (1)1. 多功能电子时钟研究的背景和意义 (1)2. 电子时钟的功能 (2)第一章电子时钟设计方案分析 (3)1.1 FPGA设计方案 (3)1.2 单片机设计方案 (3)第二章基于单片机的电子时钟硬件设计 (5)2.1 主要IC芯片选择 (5)2.1.1 微处理器选择 (5)2.1.2 时钟芯片选择 (6)2.1.2.1 DS1302简介及引脚说明 (7)2.1.2.2DS1302的控制字和读写时序说明 (8)2.1.2.3DS1302的片寄存器 (10)2.2 电子时钟硬件电路设计 (12)2.2.1 时钟电路设计 (13)2.2.2 显示电路设计 (14)2.2.3 按键电路设计 (15)2.2.4 闹铃电路设计 (17)2.2.5 复位电路设计 (18)第三章电子时钟软件设计 (20)3.1 主程序设计 (20)3.2 子程序设计 (21)3.2.1日历子程序设计 (21)3.2.2 显示子程序设计 (21)3.2.3 键盘扫描子程序 (22)3.2.4 闹铃子程序设计 (22)第四章系统调试 (26)4.1 硬件调试 (27)4.1.1 单片机基础电路调试 (27)4.1.2 显示电路调试 (28)4.1.3 DS1302电路调试 (30)4.1.4 按键电路调试 (31)4.2 软件调试 (32)4.2.1 键盘子程序调试 (32)4.2.2 时钟日历子程序调试 (32)结论 (33)参考文献 (34)附录一程序 (35)附录二多功能电子时钟元器件一览表 (60)附录三多功能电子时钟硬件原理图 (61)致谢 (63)绪论时间是人类生活必不可少的重要元素,如果没有时间的概念,社会将不会有所发展和进步。

多功能智能时钟系统设计之欧阳与创编

2021.03.08多功能智能时钟系统设计作者姓名:XXX专业名称:XXXX指导教师:XX讲师欧阳与创编2021.03.08摘要随着对时间的要求越来越精确,人们创造了时钟。

现在,电子时钟更是人类最基本,最必不可少的一个工具。

在上个世纪,电子时钟大多数采用的是分离元件。

而这样制造出来的电子时钟体积庞大,使用起来也很麻烦。

随着科技和电子行业的飞速发展,现在的电路都是高度集成的。

不仅节约空间资源,成本也很低。

然电子产品给我们的生活带来了更多的便利。

本设计的主控系统采用的是单片机,利用它自带的定时器来进行设计。

单片机具有成本低廉、体积小、操作简便等优点。

它能够形成各式各样的自动控制系统。

设计中将采用单片机中最为典型也是我们在课堂上学习过的51系列的单片机,本次设计以STC89C51单片机为核心,以时钟芯片DS1302为依托,借助外围少量的按键电路实时校准,通过LCD1602液晶显示器来显示日期和时间。

在程序的部分,我采用的是C语言来进行编写。

使用C语言更有利于我的理解,编写以及修改。

本论文主要从系统设计方案的选择,硬件、软件部分的介绍说明以及实物的演示上来详细的描述了整个设计的大致内容。

设计主要研究的是智能时钟以及日历显示功能。

我们利用了单片机的控制能力和时钟芯片的及时通信的特点,按键来控制时间和日历在液晶显示屏上的显示。

最后,在整点的时欧阳与创编2021.03.08 候通过蜂鸣器进行报时。

关键词:单片机电子时钟 C语言欧阳与创编AbstractWith the demand for more precise, people create a clock. Now, the electronic clock is human the most basic, most essential as a tool. In the last century, most electronic clock use is separation of components. And this produced electronic clock bulky, use is also very troublesome. Along with the rapid development of science and technology and electronic industry, now circuit are height integrated. Not only save space resource, cost is also very low. Although electronic products to our life brought more convenience.Procedures will be used in the design of the main control system is a single chip, using its own timer design. SCM has low cost, the volume is small, easy to operate, etc.. It can form a variety of automatic control system. The design uses a microcontroller is the most typical and I were in the classroom study of 51 series microcontroller, the design STC89C51 microcontroller as the core to the clock chip DS1302 as the basis, by means of a peripheral small amounts of key circuit real-time calibration through LCD1602 LCD display to display the date and time. In part, I use C language to write. The use of C language is more conducive to my understanding, writing and revision.This paper mainly from the selection of the design scheme of the system, hardware, software part欧阳与创编of the description and physical demonstration up detailed describes the general content of the whole design. Design is the main research is intelligent clock and calendar display function. We use the MCU control can timely communication of power and clock chip keys to control the time and calendar on the LCD screen display. Finally, when the whole point of the buzzer timekeeping.Keywords: single chip microcomputer, electronic clock, C language目录摘要Abstract II目录III前言01 论文设计概述21.1 设计任务21.2 设计要求21.3 系统整体框图22 系统方案选择42.1 总体方案设计42.2 主要模块的方案设计42.2.1 主控芯片方案4欧阳与创编2.2.2 显示模块方案53 系统模块电路介绍及设计73.1 单片机模块73.1.1 单片机基础知识介绍73.1.2 STC89C51介绍93.1.3 单片机最小系统电路103.2 时钟模块133.2.1 DS1302介绍133.2.2 DS1302电路原理153.3 液晶显示模块163.3.1 LCD1602引脚及说明163.3.2 LCD1602电路原理183.4 蜂鸣器报警模块193.5 矩形按键电路模块204 系统软件设计224.1 软件设计流程224.2 系统设计程序264.2.1 主程序264.2.2 LCD1602驱动程序264.2.3 DS1302驱动程序275 系统仿真结果及说明285.1 仿真软件介绍285.1.1 Protues软件介绍285.1.2 Keil软件介绍295.2 时钟系统的仿真316 系统实物调试及结果346.1 系统实物346.1 系统实物调试结果及说明34总结37参考文献39欧阳与创编致谢40附件1主程序41附件2 LCD1602驱动程序44附件3 DS1302驱动程序48欧阳与创编2021.03.08前言现在,电子产业随着科学技术的发展而变得日益强大。

一种生成多频率同步时钟系统设计方法[发明专利]

![一种生成多频率同步时钟系统设计方法[发明专利]](https://img.taocdn.com/s3/m/b3ce3513770bf78a642954d7.png)

专利名称:一种生成多频率同步时钟系统设计方法专利类型:发明专利

发明人:张怀东,陈宇,薛永辉

申请号:CN201911316874.7

申请日:20191219

公开号:CN110958018A

公开日:

20200403

专利内容由知识产权出版社提供

摘要:本发明公开了一种生成多频率同步时钟系统设计方法,多频率同步时钟系统由锁相环、FPGA芯片以及时钟芯片构成;时钟芯片的输入端与外部时钟输出端进行连接,多级时钟芯片之间通过锁相环进行连接,第一级时钟芯片的输出端与FPGA芯片的输入端进行连接,FPGA芯片的输出端与末级时钟芯片的输入端进行连接。

本发明的有益效果是:通过时钟芯片和锁相环及FPGA进行配和,实现多通道不同频率时钟输出,并且所有时钟输出保持同步,前端时钟采用低频传输,大大提高时钟通道可扩充数量及时钟稳定性,并且不同频时钟之间能够保持同步状态,从而可以大大提高软件化雷达阵列数量及灵活性。

申请人:中船重工(武汉)凌久电子有限责任公司

地址:430000 湖北省武汉市洪山区珞瑜路718号

国籍:CN

代理机构:北京中北知识产权代理有限公司

代理人:李新昂

更多信息请下载全文后查看。