vhdl语言编写 9秒倒计时器

VHDL数字秒表设计说明

VHDL数字秒表设计专业:自动化班级学号: 5090629姓名:丹2011年 6 月14 日VHDL语言课程设计-秒表设计一、设计实验目的:在MAX+plusII软件平台上,熟练运用VHDL语言,完成数字时钟设计的软件编程、编译、综合、仿真,使用EDA实验箱,实现数字秒表的硬件功能。

二、设计实验说明及要求:1、数字秒表主要由:分频器、扫描显示译码器、一百进制计数器、六十进制计数器(或十进制计数器与6进制计数器)、十二进制计数器(或二十四进制计时脉计数器)电路组成。

在整个秒表中最关键的是如何获得一个精确的100HZ冲,除此之外,数字秒表需有清零控制端,以及启动控制端、保持保持,以便数字时钟能随意停止及启动。

2、数字秒表显示由时(12或24进制任选)、分(60进制)、秒(60进制)、百分之一秒(一百进制)组成,利用扫描显示译码电路在八个数码管显示。

3、能够完成清零、启动、保持(可以使用键盘或拨码开关置数)功能。

4、时、分、秒、百分之一秒显示准确。

三、我的设计思路:1、四个十进制计数器:用来分别对百分之一秒、十分之秒、秒和分进行计数;2、两个6进制计数器:用来分别对十秒和十分进行计数;3、一个24进制计数器,用来对小时进行计数;3、分频率器:用来产生100Hz的计数脉冲;4、显示译码器:完成对显示译码的控制。

四、设计过程:1.分频器:由10MHz变为100Hz,10MHz的周期是10的(-7)次方,而100Hz的周期是10的(-2)次方,而且方波是高低相间,只有高电平有效,所以100Hz 的周期需要取一半,即0.02秒,这样算出的分频倍数就是50000分频器代码:将10MHz脉冲变成100Hz程序:library ieee;use ieee.std_logic_1164.all;entity fenpin isport(clr,clk: in bit;q: buffer bit);end fenpin;architecture a of fenpin issignal counter:integer range 0 to 49999;beginprocess(clr,clk)beginif (clk='1' and clk'event) thenif clr='1' thencounter<=0;elsif counter=49999 thencounter<=0;q<= not q;elsecounter<=counter+1;end if;end if;end process;end a;分频器的仿真图:2.十进制计数器:原理为加法计数器,从0加到9,计到10个数时由cout进位程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity c10 isport(clr,start,clk: in bit;cout: out bit;daout: out std_logic_vector(3 downto 0));end c10;,architecture a of c10 issignal temp:std_logic_vector(3 downto 0);begindaout<=temp;process(clk,clr)beginif clr='1' thentemp<="0000";cout<='0';elsif (clk'event and clk='1') thenif start='1' thenif temp>="1001" thentemp<="0000";cout<='1';elsetemp<=temp+1;cout<='0';end if;end if;end if;end process;end a;十进制计数器仿真图:3.六进制计数器:原理为加法计数器,从0 加到5计到第六个数时由cout进位。

基于VHDL的数字计时器的设计

收稿日期:2007-12-28作者简介:夏晓玲(1967-),女,湖北鄂州人,鄂州大学电子电气工程系副教授,硕士,研究方向:单片机。

第15卷第2期Vol.15No.2鄂州大学学报JournalofEzhouUniversity2008年3月Mar.20081设计原理分析数字钟的设计主体主要分为两部分:计数部分和译码部分。

计数部分是数字钟的核心,它的主要功能是实现对时钟脉冲的累加产生秒、分、时信号[1]。

因此,计数部分又分为以下三个部分:(1)秒计数器。

它是一个六十进制计数器,而且需要采用两位BCD码形式进行设计,计数范围:00-59秒。

(2)分计数器。

分计数的实现与秒计数的实现原理基本相同,唯一的区别就是在这部分增加了校时功能。

(3)时计数器。

这部分的设计采用的是24小时制,所以它是一个二十四进制计数器,其计数范围:00-23小时。

同样,这部分也增加了校时功能。

译码部分的主要功能是将秒、分、时计数器的BCD码进行译码、转换。

通过数码管将数据结果显示出来。

2VHDL语言的实现通过原理分析可知,在具体编程过程中,利用VHDL语言强大的功能,将计数器和译码器有机地结合在一起,使得程序设计简化,同时,增加了程序的可读性[2]。

2.1秒计数器秒计数器是六十进制计数器,除了正常计数以外,要求每60秒产生一个计数脉冲传递给分计数器。

因此,在秒计数器中,计数部分要设计出时钟输入端clk、个位数据输出端mg(3downto0)、十位数据输出端ms(2downto0)和进位输出端mso,其相应的VHDL语言描述的原理图如图1所示。

对秒计数器进行设计,采用了两位BCD码的方式。

个位向十位的进位采用异步串行进位方式。

在秒的个位计数器的描述中,首先要在名为mjy1的实体中定义其端口。

其中,clk是秒的时钟信号输入端,mgo是秒个位向十位的进位输出端,mg是秒的个位输出端:libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all:entitymjy1isport(clk:std_logic;mgo:outstd_logic;mg:outstd_logic_vector(3domnto0));endmjy1;接下来是在结构体中定义了一个std_logic_vector类型的局部信号mgn和一个std_logic类型的局部信号C,以便使后面的进程描述更加灵活:基于VHDL的数字计时器的设计夏晓玲(鄂州大学电子电气工程系,湖北鄂州436000)摘要:文章论述了数字计时器的设计原理、设计步骤以及用VHDL语言设计数字计时器的方法。

秒计时控制器vhdl

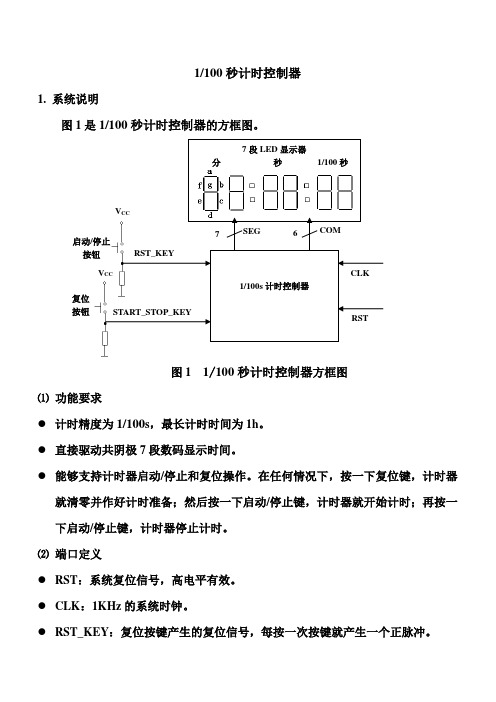

1/100秒计时控制器1. 系统说明图1是1/100秒计时控制器的方框图。

图1 1/100秒计时控制器方框图⑴ 功能要求● 计时精度为1/100s ,最长计时时间为1h 。

● 直接驱动共阴极7段数码显示时间。

● 能够支持计时器启动/停止和复位操作。

在任何情况下,按一下复位键,计时器就清零并作好计时准备;然后按一下启动/停止键,计时器就开始计时;再按一下启动/停止键,计时器停止计时。

⑵ 端口定义● RST :系统复位信号,高电平有效。

● CLK :1KHz 的系统时钟。

● RST_KEY :复位按键产生的复位信号,每按一次按键就产生一个正脉冲。

1/100s 计时控制器CLKRST7段LED 显示器分 秒 1/100秒RST_KEYSTART_STOP_KEYV CCV CC 启动/停止 按钮复位 按钮7SEGCOM6●START_STOP_KEY:启动/停止按键产生的启动/停止信号,每按一次按键就产生一个正脉冲。

●SEG:LED显示器的7段(abcdefg)显示驱动信号,高电平有效。

●COM:7段数码管的公共端控制信号。

2. 系统的总体方案、系统划分和算法设计图2是1/100秒计时控制器的总体结构框图,系统主要由时钟产生模块(CLK_GEN)、控制模块(CONTROLLER)、按键同步消抖动模块(KEY_IN)、计时模块(TIMER)和显示模块(DISPLAY)构成。

图2 1/100秒计时控制器的总体结构框图⑴时钟产生模块(CLK_GEN)时钟产生模块的作用是对输入的1kHz时钟信号CLK进行分频,输出一个25Hz 的时钟KEY_CLK和一个100Hz的时钟CNT_CLK。

时钟产生信号的结构图如图3所示。

图3 时钟产生信号的结构图时钟产生模块由两个同步加法计数器模块(COUNTER )构成,1kHz 的时钟信号CLK 先经10分频后得到100Hz 的CNT_CLK ,再经4分频后得到25Hz 的计数脉冲KEY_CLK 。

用VHDL语言编写的数字钟程序

永州职业技术学院课程设计课程名称:EDA技术实用教程题目:基于FPGA的数字钟设计系、专业:电子技术系应用电子年级、班级:07级电子大专学生姓名:**指导老师:***时间:2008年12月目录一、系统设计………………………………………………………..1.1设计要求……………………………………………………1.1.1任务………………………………………………..1.1.2要求……………………………………………….1.1.3题目分析…………………………………………二.方案论证与比较…………………………………2.1方案一…………………………………………2.2 方案二…………………………………………2.3 方案三…………………………………………三、设计思路……………………………………………………3.1硬件模块………………………………………………3.2软件模块………………………………………………….四、调试情况………………………………………………….五、系统调试…………………………………………………六、心得体会……………………………………………………... 附:参考文献……………………………………………………..用VHDL语言编写的数字钟程序摘要:本设计要求一个12进制或24进制的具有时、分、秒计时功能的数字钟,并要求能进行时、分、秒调整,每逢时有报时功能。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

本设计基于FPGA芯片的数字钟的设计,通过多功能数字钟的设计思路,详细叙述了整个系统的硬件、软件实现过程,实现了时间的显示和修改功能、报时功能等,并尽可能的减少误差,使得系统可以达到实际数字钟的允许误差范围内。

关键词:FBGA、数码管、按键一、系统设计1.1 设计要求1.1.1 任务设计并制作一个数字钟,通过设计,掌握电子设计的一般思路,学习电子设计的一般方法。

VHDL数字秒表设计

VHDL语言课程设计-秒表设计一、设计实验目的:在MAX+plusII软件平台上,熟练运用VHDL语言,完成数字时钟设计的软件编程、编译、综合、仿真,使用EDA实验箱,实现数字秒表的硬件功能。

二、设计实验说明及要求:1、数字秒表主要由:分频器、扫描显示译码器、一百进制计数器、六十进制计数器(或十进制计数器与6进制计数器)、十二进制计数器(或二十四进制计数器)电路组成。

在整个秒表中最关键的是如何获得一个精确的100H Z计时脉冲,除此之外,数字秒表需有清零控制端,以及启动控制端、保持保持,以便数字时钟能随意停止及启动。

2、数字秒表显示由时(12或24进制任选)、分(60进制)、秒(60进制)、百分之一秒(一百进制)组成,利用扫描显示译码电路在八个数码管显示。

3、能够完成清零、启动、保持(可以使用键盘或拨码开关置数)功能。

4、时、分、秒、百分之一秒显示准确。

三、我的设计思路:1、四个十进制计数器:用来分别对百分之一秒、十分之秒、秒和分进行计数;2、两个6进制计数器:用来分别对十秒和十分进行计数;3、一个24进制计数器,用来对小时进行计数;3、分频率器:用来产生100Hz的计数脉冲;4、显示译码器:完成对显示译码的控制。

四、设计过程:1.分频器:由10MHz变为100Hz,10MHz的周期是10的(-7)次方,而100Hz 的周期是10的(-2)次方,而且方波是高低相间,只有高电平有效,所以100Hz 的周期需要取一半,即0.02秒,这样算出的分频倍数就是50000分频器代码:将10MHz脉冲变成100Hz程序:library ieee;use ieee.std_logic_1164.all;entity fenpin isport(clr,clk: in bit;q: buffer bit);end fenpin;architecture a of fenpin issignal counter:integer range 0 to 49999;beginprocess(clr,clk)beginif (clk='1' and clk'event) thenif clr='1' thencounter<=0;elsif counter=49999 thencounter<=0;q<= not q;elsecounter<=counter+1;end if;end if;end process;end a;分频器的仿真图:2.十进制计数器:原理为加法计数器,从0加到9,计到10个数时由cout进位程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity c10 isport(clr,start,clk: in bit;daout: out std_logic_vector(3 downto 0)); end c10;,architecture a of c10 issignal temp:std_logic_vector(3 downto 0); begindaout<=temp;process(clk,clr)beginif clr='1' thentemp<="0000";cout<='0';elsif (clk'event and clk='1') thenif start='1' thenif temp>="1001" thentemp<="0000";cout<='1';elsetemp<=temp+1;cout<='0';end if;end if;end process;end a;十进制计数器仿真图:3.六进制计数器:原理为加法计数器,从0 加到5计到第六个数时由cout进位。

基于verilog HDL计时器和倒计时的系统设计

实验报告2019 -2020 学年第2学期开课单位电子信息学院适用年级、专业2017级电子信息科学与技术Z 课程名称FPGA技术及应用-课内实验主讲教师课程序号BS6222003X3-03课程代码BS6222003X3实验名称计时器和倒计时的系统设计实验学时2学时学号姓名实验五计时器和倒计时的系统设计①掌握用Verilog HDL文本输入法设计计时电路的方法,并通过电路仿真和硬件验证,进一步了解计时器的功能和特性。

②掌握用Verilog HDL文本输入法设计倒计时电路的方法,并通过电路仿真和硬件验证,进一步了解倒计时电路的功能和特性。

二、实验原理1.计时器24小时计时器的电路框图如图8.1所示。

图8.1 24小时计时器的电路框图24小时计时器由2个60进制加计数器和1个24进制加计数器构成,输入CLK为1HZ(秒)的时钟,经过60进制加计数后产生1分钟的进位时钟信号,再经过60进制加计数后产生1小时的进位时钟信号送给24进制加计数器进行加计数,当加计数到达23:59:59后,再来-一个秒脉冲,产生时的进位输出。

将两个60进制加计数器和一个24进制加计数器的输出送数码管显示,得到计时器的显示结果。

其中,秒脉冲由EDA实调仪上的20MHz晶振分频得到。

2.倒计时器24小时倒计时器的电路框图如图8.2所示。

图8.2 24 小时倒计时器的电路框图24小时倒计时器由2个60进制减计故器和1个24进制减计数器构成,输入CLK为1Hz(秒)的时钟,经过60进制减计数后产生1分钟的借位时钟信号,再经过60进制减计数后产生I小时的借位时钟信号送给24进制减计数器进行减计数,当减计数到达00:00:00后,产生时的借位输出,同时24小时倒计时器停止倒计时,并发出提醒信号。

将两个60进制减计数器和一个24进制减计数器的输出送数码管显示,得到倒计时的显示结果。

其中,秒脉冲由EDA实训仪上的20MHz晶振分频得到。

三、实验设备①EDA实调仪1台。

用VHDL设计数字秒表

实验五数字秒表的设计1、分频计的设计(1)分频计的源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY FP ISPORT(CLK: IN STD_LOGIC;NEWCLK: OUT STD_LOGIC);END FP;ARCHITECTURE ART OF FP ISSIGNAL CNTER: INTEGER RANGE 0 TO 10#29999#;BEGINPROCESS(CLK) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CNTER=10#29999# THEN CNTER<=0;ELSE CNTER<=CNTER + 1;END IF;END IF;END PROCESS;PROCESS(CNTER) ISBEGINIF CNTER=10#29999# THEN NEWCLK<='1';ELSE NEWCLK<='0';END IF;END PROCESS;END ART;(2)分频计的封装图(1)六进制计数器的源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY TN6 ISPORT(CLK: IN STD_LOGIC;CLR: IN STD_LOGIC;ENA: IN STD_LOGIC;CQ: OUT INTEGER RANGE 0 TO 15;CARRY_OUT: OUT STD_LOGIC); END TN6;ARCHITECTURE ART OF TN6 ISSIGNAL CQI: INTEGER RANGE 0 TO 15; BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR='1' THEN CQI<=0;ELSIF CLK'EVENT AND CLK='1' THEN IF ENA='1' THENIF CQI<5 THEN CQI<=CQI+1;ELSE CQI<=0;END IF;END IF;END IF;END PROCESS;PROCESS(CQI) ISBEGINIF CQI=5 THEN CARRY_OUT<='1';ELSE CARRY_OUT<='0'; END IF;END PROCESS;CQ<=CQI;END ART;(2)六进制的封装图(1)十进制计数器源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY TN10 ISPORT(CLK: IN STD_LOGIC;CLR: IN STD_LOGIC;ENA: IN STD_LOGIC;CQ: OUT INTEGER RANGE 0 TO 15;CARRY_OUT: OUT STD_LOGIC); END TN10;ARCHITECTURE ART OF TN10 ISSIGNAL CQI: INTEGER RANGE 0 TO 15; BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR='1' THEN CQI<=0;ELSIF CLK'EVENT AND CLK='1' THEN IF ENA='1' THENIF CQI<9 THEN CQI<=CQI+1;ELSE CQI<=0;END IF;END IF;END IF;END PROCESS;PROCESS(CQI) ISBEGINIF CQI=9 THEN CARRY_OUT<='1';ELSE CARRY_OUT<='0'; END IF;END PROCESS;CQ<=CQI;END ART;(2)十进制计数器的封装图(1)扫描电路的源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SCAN ISPORT(scanclk:in std_logic;count1,Count2,count3,count4,count5,count6:in std_logic_VECTOR(3 DOWNTO 0);S:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY SCAN;ARCHITECTURE DA TAFLOW OF SCAN ISSIGNAL SS:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINPROCESS(scanclk)beginIF(scanclk'EVENT AND scanclk='1')THENIF(SS="101")THENSS<="000";ELSESS<=SS+1;END IF;END IF;END PROCESS;S<=SS;DOUT<=COUNT1 WHEN SS="000" ELSECOUNT2 WHEN SS="001" ELSECOUNT3 WHEN SS="010" ELSECOUNT4 WHEN SS="011" ELSECOUNT5 WHEN SS="100" ELSECOUNT6;END DATAFLOW;5、位码选择电路的设计(1)位码选择电路的源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY YIMA ISPORT(INP: IN STD_LOGIC_VECTOR(2 DOWNTO 0);OUTP: OUT BIT_VECTOR(7 DOWNTO 0)); END YIMA;ARCHITECTURE ART OF YIMA ISBEGINOUTP(0)<='1' WHEN INP="000" ELSE '0';OUTP(1)<='1' WHEN INP="001" ELSE '0';OUTP(2)<='1' WHEN INP="010" ELSE '0';OUTP(3)<='1' WHEN INP="011" ELSE '0';OUTP(4)<='1' WHEN INP="100" ELSE '0';OUTP(5)<='1' WHEN INP="101" ELSE '0';OUTP(6)<='1' WHEN INP="110" ELSE '0';OUTP(7)<='1' WHEN INP="111" ELSE '0';END ART;(2)位码电路的封装图6、七位数码管译码显示电路(1)七位数码管显示电路的源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DELED ISPORT(NUM: IN STD_LOGIC_VECTOR(3 DOWNTO 0);A,B,C,D,E,F,G: OUT STD_LOGIC);END DELED;ARCHITECTURE ART OF DELED ISSIGNAL LED : STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINPROCESS(NUM)BEGINCASE NUM ISWHEN "0000" => LED <= "";WHEN "0001" => LED <= "";WHEN "0010" => LED <= "";WHEN "0011" => LED <= "";WHEN "0100" => LED <= "";WHEN "0101" => LED <= "";WHEN "0110" => LED <= "";WHEN "0111" => LED <= "";WHEN "1000" => LED <= "";WHEN "1001" => LED <= "";WHEN "1010" => LED <= "";WHEN "1011" => LED <= "";WHEN "1100" => LED <= "";WHEN "1101" => LED <= "";WHEN "1110" => LED <= "";WHEN OTHERS => LED <= "";END CASE;END PROCESS;A<=LED(6);B<=LED(5);C<=LED(4);D<=LED(3);E<=LED(2);F<=LED(1);G<=LED(0); END ART;(2)七位数码管电路的封装图7、数字秒表系统的连接的原理图9、数字秒表电路的分析本次设计的数字秒表由分频器、六进制计数器、十进制计数器、扫描电路、位码选择电路、七段数码管显示电路六个模块组成。

VHDL课程设计--数字秒表

基于VHDL语言的数字秒表实现2013-5-1基于VHDL语言的数字秒表实现1 设计方案1.1 系统功能要求设计一块数字秒表,能够精确反映计时时间,并完成复位、计时功能。

秒表计时的最大范围为1小时,精度为0.01秒,并可显示计时时间的分、秒、0.1秒等度量。

( 1) 具有秒表系统功能要求显示功能, 用6个数码管分别显示分、秒、0.01秒; 计时范围为00: 00: 00~ 59: 59:99。

( 2) 计时精度是0.01s;( 3) 具有启/ 停开关, 复位开关。

1. 2 总体框图根据系统设计要求, 系统的底层设计主要由六十进制计数器模块、二十四进制计数器模块、分频模块、LED显示模块组成。

系统顶层设计图如图所示:图中左边为三个输入信号en,clk,reset;分为启/ 停开关,时钟信号和复位开关。

主要模块有:模60计数器(count60),模100计数器(count100),分频器(clk_div),复位控制(control),译码器(yima),防抖模块(fdou),状态变换模块(change)。

右边是六个LED显示输出信号。

2 模块功能设计由模60计数器模块与模100计数器模块进行计数;实验室仪器可产生标准的1kHz的时钟信号,通过分频器模块产生所需的100Hz的时钟信号;复位模块可进行计数器复位操作;译码器是为了将四位二进制信号转换为LED所需的七位二进制编码;防抖模块用于消除用户按键时的抖动消除,为方便仿真,此处原始时钟信号3周期以上可产生信号;状态变换模块是为了用户按键后信号的变换及保持。

2. 1 模60计数器该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count60 ISPORT( en,Reset,clk: in STD_LOGIC;qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);qb: out STD_LOGIC_VECTOR(3 DOWNTO 0);rco: OUT STD_LOGIC);END count60;ARCHITECTURE a OF count60 ISBEGINprocess(clk)variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);variable tmb: STD_LOGIC_VECTOR(3 DOWNTO 0);beginIf Reset ='0'then tma:="0000"; tmb:="0000";elsif clk'event and clk='1' thenif en='1' thenrco<=tmb(2)and tmb(0)and tma(3)and tma(0);if tma="1001" then tma:="0000";if tmb="0101" then tmb:="0000";else tmb:=tmb+1;end if;else tma:=tma+1;end if;end if;end if;qa<=tma;qb<=tmb;end process;END a;2. 2 模100计数器该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count100 ISPORT( en,Reset,clk: in STD_LOGIC;qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);qb: out STD_LOGIC_VECTOR(3 DOWNTO 0);rco: OUT STD_LOGIC);END count100;ARCHITECTURE a OF count100 ISBEGINprocess(clk)variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);variable tmb: STD_LOGIC_VECTOR(3 DOWNTO 0);beginIf Reset ='0'then tma:="0000"; tmb:="0000";elsif clk'event and clk='1' thenif en='1' thenrco<=tmb(3)and tmb(0)and tma(3)and tma(0);if tma="1001" then tma:="0000";if tmb="1001" then tmb:="0000";else tmb:=tmb+1;end if;else tma:=tma+1;end if;end if;end if;qa<=tma;qb<=tmb;end process;END a;2. 3 分频器模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY clk_div ISPORT(clk :IN STD_LOGIC;clk_out :OUT STD_LOGIC);END clk_div;ARCHITECTURE rtl OF clk_div ISSIGNAL clk_temp :STD_LOGIC;BEGINPROCESS(clk)VARIABLE counter: INTEGER RANGE 0 TO 15; BEGINIF (clk'EVENT AND clk='1') THENIF (counter = 9) THENCounter := 0;Clk_out <= '1';ELSECounter :=counter +1 ;Clk_out <= '0';END IF;END IF;END PROCESS;END rtl;2. 4 复位控制该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY control ISPORT( CLK,RST:in std_logic;CLK_OUT:out std_logic);END control;ARCHITECTURE behav OF control ISsignal clk_data:std_logic;SIGNAL CNT : INTEGER := 0;BEGINPROCESS(CLK)BEGINIF RST = '0' THEN CNT<=0 ;ELSIF CLK'EVENT AND CLK='1' THENIF CNT=2 THEN clk_data<=NOT clk_data;CNT<=0;ELSE CNT<=CNT+1;END IF;END IF;CLK_OUT<=clk_data;END PROCESS;END behav;2. 5 译码器该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY yima ISPORT( num:in STD_LOGIC_VECTOR(3 downto 0);led:out STD_LOGIC_VECTOR(6 downto 0));END yima ;ARCHITECTURE a OF yima ISBEGINprocess(num)begincase num iswhen"0000"=>led<="0111111";when"0001"=>led<="0000110";when"0010"=>led<="1011011";when"0011"=>led<="1001111";when"0100"=>led<="1100110";when"0101"=>led<="1101101";when"0110"=>led<="1111101";when"0111"=>led<="0100111";when"1000"=>led<="1111111";when"1001"=>led<="1101111";when others=>led<="0000000";end case;end process;END a;2. 6 防抖模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY fdou ISPORT(CLK,DIN:IN STD_LOGIC;DOUT:OUT STD_LOGIC);END ENTITY fdou;ARCHITECTURE ARC OF fdou ISSIGNAL CP:STD_LOGIC;SIGNAL JSQ:INTEGER RANGE 0 TO 3;BEGINPROCESS(CLK)BEGINIF (CLK' EVENT AND CLK= '1' ) THEN IF DIN='1' THENIF JSQ=3 THENJSQ<=JSQ;ELSEJSQ<=JSQ+1;END IF;IF JSQ=1 THENCP<='1';ELSECP<='0';END IF;ELSEJSQ<=0;END IF;END IF;DOUT<=CP;END PROCESS;END ARC ;2. 7 状态变换模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY change ISPORT( clk_in,clk:IN STD_LOGIC;clk_out:OUT STD_LOGIC);END ENTITY change;ARCHITECTURE a OF change ISSIGNAL cp:STD_LOGIC;BEGINPROCESS(CLK)BEGINIF (CLK' EVENT AND CLK= '1' ) THEN IF (clk_in ='1') THENcp<='0';ELSEcp<='1';END IF;END IF;clk_out<=CP;END PROCESS;END a ;3仿真波形及分析各部分模块完成后, 用Quartus 对程序编译、仿真、得到的仿真波形,各模块仿真波形及顶层仿真波形如下:3.1模60计数器模块仿真clk:时钟信号rst:复位信号低电平清零en:置数端低电平不让它继续计数qb、qa:分别为输出数的十位个位,qb取值范围为0-5,qa取值范围为0-9rco:进位信号,当qb=5,qa=9, rco=0时,clk上升沿来到后,qb=0, qa=0, rco=1;当qb=0,qa=0, rco=1时,clk上升沿来到后,qb=0, qa=1, rco=03.2模100计数器模块仿真clk:时钟信号cst:复位信号低电平清零en:置数端低电平不让它继续计数qb、qa:分别为输出数的十位个位,qb取值范围为0-9,qa取值范围为0-9rco:进位信号,当qb=9,qa=9, rco=0时,clk上升沿来到后,qb=0, qa=0, rco=1;当qb=0,qa=0, rco=1时,clk上升沿来到后,qb=0, qa=1, rco=03.3分频器模块仿真因时钟脉冲(为1khz)通过分频器分频后频率(为100hz)。

VHDL-数字秒表设计

通达学院2017/2018学年第一学期课程设计实验报告模块名称VHDL课程设计专业学生班级学生学号学生姓名指导教师目录一、课程设计目的与要求 (1)1.1 课程设计目的 (1)1.2 基本要求 (1)二、设计方案--数字秒表的设计 (1)2.1 设计功能 (1)2.2 秒表基本原理及设计方法 (2)2.3 数字秒表设计原理 (2)三、开发环境 (3)四、模块结构 (4)4.1 数字秒表RTL级电路 (4)4.2 计时器模块 (6)4.3 取数模块 (8)4.4 编码模块 (9)4.5 数码管显示控制模块 (13)4.6 数码管地址选择模块 (15)五、设计仿真和实验 (16)5.1 计时器模块仿真 (16)5.2 秒表仿真 (17)5.3 pin引脚接口图 (18)5.4 实验结果图 (18)六、总结与体会 (20)6.1 错误分析 (20)6.2 心得体会 (20)七、参考文献 (21)一、课程设计目的与要求1.1 课程设计目的《EDA 技术综合设计与实践》(注:EDA 即电子设计自动化,Electronics Design Automation)是继《模拟电子技术基础》、《数字电子技术基础》、《电子技术基础实验》、《EDA》等课程后,电子类等专业学生在电子技术实验技能方面综合性质的实验训练课程,是电子技术基础的一个部分,其目的和任务是通过一周的时间,让学生掌握EDA 的基本方法,熟悉一种EDA 软件(Quartus II),并能利用EDA 软件设计一个电子技术综合问题,并在实验板上成功下载,为以后进行工程实际问题的研究打下设计基础。

1.2 基本要求(1)通过课程设计使学生能熟练掌握一种EDA 软件(Quartus II)的使用方法,能熟练进行设计输入、编译、管脚分配、下载等过程。

(2)通过课程设计使学生能利用EDA 软件(Quartus II)进行至少一个电子技术综合问题的设计(内容可由老师指定或自由选择),设计输入采用VerilogHDL 硬件描述语言输入法。

运动员赛跑计时秒表的VHDL设计

运动员赛跑计时秒表的VHDL设计

要求

(1)秒表的输入只有时钟(clk)和一个按键(key),假设key已经经过防抖动和脉冲宽度处理,每按一次key产生持续一个时钟周期的高电平脉冲,可以满足设计的需要,不需要对key再做任何处理。

(2)秒表输出用0-59的整数表示,不需要对十位和个位分别计数,不需要7段译码。

(3)键key的功能如下:

(A)按第一下key,开始计数,并输出计数值;

(B)第一个运动员到终点时按第二下key,秒表记住第一个运动员到终点的时间,但还在继续计数并输出计数值;

(C)第二个运动员到终点时按第三下key,停止计数,这时输出的计数值就是第二个运动员用的时间;

(D)然后按第四下key,秒表输出第一个运动员到终点的时间,即按第二下key时记住的计数值;

(E)按第五下key,秒表清0,开始新的周期。

(4)画出秒表的状态转移图,标明各个状态的转移条件和输出。

(5)用VHDL完成秒表的设计。

状态转移图

源程序

仿真结果。

基于VHDL的电子计时器的设计课程设计

EDA技术及应用课程设计题目:基于VHDL的数字计时器班级:电气1202班姓名:李玉靖学号:20121131080指导老师:汪媛(课程设计时间:2015年1月5日——2015年1月9日)华中科技大学武昌分校目录1引言............................................ (1)1.1 EDA简介............................................................................. . (1)1.2 VHDL简介............................................................................. . (2)1.3 VHDL的特点 (3)1.4 VHDL的设计结构 (4)1.5 VHDL的设计步骤 (4)2设计主要内容 (5)3内部各功能模块 (6)3.1六十进制计数模块 (6)3.2二十四进制计数模块 (8)3.3分频器模块............................................................................. .. (10)3.4LED显示模块............................................................................. ..114顶层系统联调 (15)5结语............................................ (21)6参考文献............................................ .227附录............................................ (23)1.引言随着科学技术的迅猛发展,电子工业界经历了巨大的飞跃。

VHDL课程设计--数字秒表

基于VHDL语言的数字秒表实现2013-5-1基于VHDL语言的数字秒表实现1 设计方案1.1 系统功能要求设计一块数字秒表,能够精确反映计时时间,并完成复位、计时功能。

秒表计时的最大范围为1小时,精度为0.01秒,并可显示计时时间的分、秒、0.1秒等度量。

( 1) 具有秒表系统功能要求显示功能, 用6个数码管分别显示分、秒、0.01秒; 计时范围为00: 00: 00~ 59: 59:99。

( 2) 计时精度是0.01s;( 3) 具有启/ 停开关, 复位开关。

1. 2 总体框图根据系统设计要求, 系统的底层设计主要由六十进制计数器模块、二十四进制计数器模块、分频模块、LED显示模块组成。

系统顶层设计图如图所示:图中左边为三个输入信号en,clk,reset;分为启/ 停开关,时钟信号和复位开关。

主要模块有:模60计数器(count60),模100计数器(count100),分频器(clk_div),复位控制(control),译码器(yima),防抖模块(fdou),状态变换模块(change)。

右边是六个LED显示输出信号。

2 模块功能设计由模60计数器模块与模100计数器模块进行计数;实验室仪器可产生标准的1kHz的时钟信号,通过分频器模块产生所需的100Hz的时钟信号;复位模块可进行计数器复位操作;译码器是为了将四位二进制信号转换为LED所需的七位二进制编码;防抖模块用于消除用户按键时的抖动消除,为方便仿真,此处原始时钟信号3周期以上可产生信号;状态变换模块是为了用户按键后信号的变换及保持。

2. 1 模60计数器该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count60 ISPORT( en,Reset,clk: in STD_LOGIC;qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);qb: out STD_LOGIC_VECTOR(3 DOWNTO 0);rco: OUT STD_LOGIC);END count60;ARCHITECTURE a OF count60 ISBEGINprocess(clk)variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);variable tmb: STD_LOGIC_VECTOR(3 DOWNTO 0);beginIf Reset ='0'then tma:="0000"; tmb:="0000";elsif clk'event and clk='1' thenif en='1' thenrco<=tmb(2)and tmb(0)and tma(3)and tma(0);if tma="1001" then tma:="0000";if tmb="0101" then tmb:="0000";else tmb:=tmb+1;end if;else tma:=tma+1;end if;end if;end if;qa<=tma;qb<=tmb;end process;END a;2. 2 模100计数器该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count100 ISPORT( en,Reset,clk: in STD_LOGIC;qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);qb: out STD_LOGIC_VECTOR(3 DOWNTO 0);rco: OUT STD_LOGIC);END count100;ARCHITECTURE a OF count100 ISBEGINprocess(clk)variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);variable tmb: STD_LOGIC_VECTOR(3 DOWNTO 0);beginIf Reset ='0'then tma:="0000"; tmb:="0000";elsif clk'event and clk='1' thenif en='1' thenrco<=tmb(3)and tmb(0)and tma(3)and tma(0);if tma="1001" then tma:="0000";if tmb="1001" then tmb:="0000";else tmb:=tmb+1;end if;else tma:=tma+1;end if;end if;end if;qa<=tma;qb<=tmb;end process;END a;2. 3 分频器模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY clk_div ISPORT(clk :IN STD_LOGIC;clk_out :OUT STD_LOGIC);END clk_div;ARCHITECTURE rtl OF clk_div ISSIGNAL clk_temp :STD_LOGIC;BEGINPROCESS(clk)VARIABLE counter: INTEGER RANGE 0 TO 15; BEGINIF (clk'EVENT AND clk='1') THENIF (counter = 9) THENCounter := 0;Clk_out <= '1';ELSECounter :=counter +1 ;Clk_out <= '0';END IF;END IF;END PROCESS;END rtl;2. 4 复位控制该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY control ISPORT( CLK,RST:in std_logic;CLK_OUT:out std_logic);END control;ARCHITECTURE behav OF control ISsignal clk_data:std_logic;SIGNAL CNT : INTEGER := 0;BEGINPROCESS(CLK)BEGINIF RST = '0' THEN CNT<=0 ;ELSIF CLK'EVENT AND CLK='1' THENIF CNT=2 THEN clk_data<=NOT clk_data;CNT<=0;ELSE CNT<=CNT+1;END IF;END IF;CLK_OUT<=clk_data;END PROCESS;END behav;2. 5 译码器该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY yima ISPORT( num:in STD_LOGIC_VECTOR(3 downto 0);led:out STD_LOGIC_VECTOR(6 downto 0));END yima ;ARCHITECTURE a OF yima ISBEGINprocess(num)begincase num iswhen"0000"=>led<="0111111";when"0001"=>led<="0000110";when"0010"=>led<="1011011";when"0011"=>led<="1001111";when"0100"=>led<="1100110";when"0101"=>led<="1101101";when"0110"=>led<="1111101";when"0111"=>led<="0100111";when"1000"=>led<="1111111";when"1001"=>led<="1101111";when others=>led<="0000000";end case;end process;END a;2. 6 防抖模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY fdou ISPORT(CLK,DIN:IN STD_LOGIC;DOUT:OUT STD_LOGIC);END ENTITY fdou;ARCHITECTURE ARC OF fdou ISSIGNAL CP:STD_LOGIC;SIGNAL JSQ:INTEGER RANGE 0 TO 3;BEGINPROCESS(CLK)BEGINIF (CLK' EVENT AND CLK= '1' ) THEN IF DIN='1' THENIF JSQ=3 THENJSQ<=JSQ;ELSEJSQ<=JSQ+1;END IF;IF JSQ=1 THENCP<='1';ELSECP<='0';END IF;ELSEJSQ<=0;END IF;END IF;DOUT<=CP;END PROCESS;END ARC ;2. 7 状态变换模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY change ISPORT( clk_in,clk:IN STD_LOGIC;clk_out:OUT STD_LOGIC);END ENTITY change;ARCHITECTURE a OF change ISSIGNAL cp:STD_LOGIC;BEGINPROCESS(CLK)BEGINIF (CLK' EVENT AND CLK= '1' ) THEN IF (clk_in ='1') THENcp<='0';ELSEcp<='1';END IF;END IF;clk_out<=CP;END PROCESS;END a ;3仿真波形及分析各部分模块完成后, 用Quartus 对程序编译、仿真、得到的仿真波形,各模块仿真波形及顶层仿真波形如下:3.1模60计数器模块仿真clk:时钟信号rst:复位信号低电平清零en:置数端低电平不让它继续计数qb、qa:分别为输出数的十位个位,qb取值范围为0-5,qa取值范围为0-9rco:进位信号,当qb=5,qa=9, rco=0时,clk上升沿来到后,qb=0, qa=0, rco=1;当qb=0,qa=0, rco=1时,clk上升沿来到后,qb=0, qa=1, rco=03.2模100计数器模块仿真clk:时钟信号cst:复位信号低电平清零en:置数端低电平不让它继续计数qb、qa:分别为输出数的十位个位,qb取值范围为0-9,qa取值范围为0-9rco:进位信号,当qb=9,qa=9, rco=0时,clk上升沿来到后,qb=0, qa=0, rco=1;当qb=0,qa=0, rco=1时,clk上升沿来到后,qb=0, qa=1, rco=03.3分频器模块仿真因时钟脉冲(为1khz)通过分频器分频后频率(为100hz)。

VHDL 秒表设计

深圳大学实验报告课程名称:基于VHDL的FPGA设计实验项目名称:VHDL秒表设计学院:信息工程学院专业:电子信息工程指导教师:初萍报告人:陈耀省学号:**********班级:电子三班实验时间:2012年11月实验报告提交时间:2012年11月16日教务部制1、进一步熟悉ISE软件的使用,熟悉FPGA开发流程;2、掌握编写VHDL代码的步骤,学会绘制ASM图;3、学会使用元件实现系统的设计。

二、实验设备1、装有ISE软件的PC机一台;2、Nexys2开发板一块。

三、实验内容与要求设计一个秒表基本要求:它具有计时功能。

此秒表有两个按键(reset, start)按下reset键后,秒表清零,按下start键后,开始计时,再次按下start键后,停止计时,用FPGA开发板上的两个七段数码管显示时间(以秒为单位),计时由0 到 99 循环。

高级要求(可选):实现基本要求的前提下,增加一个按键(select),用于轮流切换两个七段数码管分别显示百分之一秒,秒,或对于Nexys2 和 Nexy3开发板,按下select键之后,四个七段数码管同时显示秒和百分之一秒。

规格说明:1.通过按下reset键(异步复位),将秒表清零,准备计时,等检测到start键按下并松开后,开始计时。

如果再次检测到start键按下并松开后,停止计时。

通过不断检测start键,来确定秒表是否开始计时2.在秒表计时时,七段数码管能够循环的由00…99,00…99…。

3.开始默认两个七段数码管显示秒,检测到select键按下并松开后,数码管切换到显示百分之一秒,当再次检测到select键按下并松开后,数码管切换到重新显示秒。

4.在秒表停止时,数码管依然能够正常切换显示秒,百分之一秒。

5.本实验使用FPGA开发板:Nexys2 或 Nexys3或旧板。

1、设计系统框图,设计采取自上而下的设计方案,整个秒表系统的原理图如下所示。

主要包括五个模块——start键功能模块、分频模块、selct键功能模块、计数模块、数码管驱动模块。

VHDL计时器程序

library ieee;use ieee.std_logic_1164.all;entity clkgen isport(clk:in std_logic;newclk:out std_logic);end entity clkgen;architecture art of clkgen issignal cnter:integer range 0 to 10#29999#; beginprocess(clk) isbeginif clk'event and clk='1' thenif cnter=10#29999# then cnter<=0;else cnter<=cnter+1;end if;end if;end process;process(cnter) isbeginif cnter=10#29999# then newclk<='1';else newclk<='0';end if;end process;end architecture art;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt6 isport(clk:in std_logic;clr:in std_logic;ena:in std_logic;cq:out std_logic_vector(3 downto 0);carry_out:out std_logic);end entity cnt6;architecture art of cnt6 issignal cqi:std_logic_vector(3 downto 0); beginprocess(clk,clr,ena) isbeginif clr='1' then cqi<="0000";elseif clk'event and clk='1' thenif ena='1' thenif cqi="0101" then cqi<="0000";else cqi<=cqi+'1';end if;end if;end if;end process;cq<=cqi;end architecture art;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk:in std_logic;clr:in std_logic;ena:in std_logic;cq:out std_logic_vector(3 downto 0);carry_out:out std_logic);end entity cnt10;architecture art of cnt10 issignal cqi:std_logic_vector(3 downto 0);beginprocess(clk,clr,ena) isbeginif clr='1' then cqi<="0000";elseif clk'event and clk='1' thenif ena='1' thenif cqi="1001" then cqi<="0000";else cqi<=cqi+'1';end if;end if;end if;end process;process(cqi) isbeginif cqi="0000" then carry_out<='1';else carry_out<='0';end if;end process;cq<=cqi;end architecture art;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY TIMES ISPORT(CLR: IN STD_LOGIC;CLK: IN STD_LOGIC;ENA: IN STD_LOGIC;DISPLAY: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --七段码管显示输出SEG_SEL: BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0) );--七段码管扫描驱动END ENTITY TIMES;ARCHITECTURE ART OF TIMES ISCOMPONENT CLKGEN ISPORT(CLK:IN STD_LOGIC;NEWCLK:OUT STD_LOGIC);END COMPONENT CLKGEN;COMPONENT CNT10 ISPORT(CLK,CLR,ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC);END COMPONENT CNT10;COMPONENT CNT6 ISPORT(CLK,CLR,ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC);END COMPONENT CNT6;SIGNAL S0:STD_LOGIC;SIGNAL S1,S2,S3,S4,S5:STD_LOGIC;SIGNAL DISP_TEMP : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DISP_DECODE : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL DOUT : STD_LOGIC_VECTOR(23 DOWNTO 0);BEGINU0:CLKGEN PORT MAP(CLK=>CLK,NEWCLK=>S0);U1:CNT10 PORT MAP(S0,CLR,ENA,DOUT(3 DOWNTO 0),S1);U2:CNT10 PORT MAP(S1,CLR,ENA,DOUT(7 DOWNTO 4),S2);U3:CNT10 PORT MAP(S2,CLR,ENA,DOUT(11 DOWNTO 8),S3);U4:CNT6 PORT MAP(S3,CLR,ENA,DOUT(15 DOWNTO 12),S4);U5:CNT10 PORT MAP(S4,CLR,ENA,DOUT(19 DOWNTO 16),S5);U6:CNT6 PORT MAP(S5,CLR,ENA,DOUT(23 DOWNTO 20));PROCESS(SEG_SEL) IS --扫描读取数值BEGINCASE (SEG_SEL+1) ISWHEN "000"=>DISP_TEMP<= DOUT(23 DOWNTO 20);WHEN "001"=>DISP_TEMP<= DOUT(19 DOWNTO 16);WHEN "010"=>DISP_TEMP<="1111";WHEN "011"=>DISP_TEMP<= DOUT(15 DOWNTO 12);WHEN "100"=>DISP_TEMP<= DOUT(11 DOWNTO 8);WHEN "101"=>DISP_TEMP<="1111";WHEN "110"=>DISP_TEMP<= DOUT(7 DOWNTO 4);WHEN "111"=>DISP_TEMP<= DOUT(3 DOWNTO 0);END CASE;END PROCESS;PROCESS(CLK)BEGINIF(CLK'EVENT AND CLK='1') THEN --扫描累加SEG_SEL<=SEG_SEL + 1;DISPLAY<=DISP_DECODE;END IF;END PROCESS;PROCESS(DISP_TEMP) --显示转换BEGINCASE DISP_TEMP ISWHEN "0000"=>DISP_DECODE<="00111111"; --0WHEN "0001"=>DISP_DECODE<="00000110"; --1WHEN "0010"=>DISP_DECODE<="01011011"; --2WHEN "0011"=>DISP_DECODE<="01001111"; --3WHEN "0100"=>DISP_DECODE<="01100110"; --4WHEN "0101"=>DISP_DECODE<="01101101"; --5WHEN "0110"=>DISP_DECODE<="01111101"; --6WHEN "0111"=>DISP_DECODE<="00000111"; --7WHEN "1000"=>DISP_DECODE<="01111111"; --8WHEN "1001"=>DISP_DECODE<="01101111"; --9WHEN "1010"=>DISP_DECODE<="01000000"; ---WHEN OTHERS=>DISP_DECODE<="00000000"; --全灭END CASE;END PROCESS;END ARCHITECTURE ART;。

vhdl语言编写9秒倒计时器

vhdl语言编写9秒倒计时器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;--------------------------------------------------------------------------------------------ENTITY CNT9 ISPORT(CLK,en: INSTD_LOGIC;PLD,ENB : INSTD_LOGIC; -------PLD表示复位信号WARN: OUT STD_LOGIC;S0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));------------译码输出,S0为个位END CNT9;--------------------------------------------------------------------------------------------ARCHITECTURE A OF CNT9 ISSIGNAL SS : STD_LOGIC_VECTOR (3 DOWNTO 0) ;-------------SS表示个位BEGINPRO1: PROCESS (CLK,en,ENB)VARIABLE TMPA: STD_LOGIC_VECTOR (3 DOWNTO 0);VARIABLE TMPWARN: STD_LOGIC;BEGINIF en='1' THEN TMPA:="1001";TMPWARN:='0';ELSIF CLK'EVENT AND CLK='1' THENTMPA:=TMPA-1;if tmpa='0' then TMPWARN:='1';END IF;END IF;SS<=TMPA;WARN<=TMPWARN;PROCESS(SS)BEGINCASE SS IS --------------------------个位显示部分WHEN "0000" => S0 <="0111111";--显示0 WHEN "0001" => S0 <="0000110";--显示1 WHEN "0010" => S0 <="1011011";--显示2 WHEN "0011" => S0 <="1001111";--显示3 WHEN "0100" => S0<="1100110";--显示4 WHEN "0101" => S0 <="1101101";--显示5 WHEN "0110" => S0 <="1111101";--显示6 WHEN "0111" => S0 <="0000111";--显示7 WHEN "1000" => S0 <="1111111";--显示8 WHEN "1001" => S0 <="1101111";--显示9 WHEN OTHERS =>S0<="0000000";END CASE ;END PROCESS;END A;。

VHDL秒表计时器

ca<='1'; ELSE qs<=qs+1; ca<='0'; END IF; END IF; END IF; END PROCESS; PROCESS(ca) BEGIN q<=qs; carry<=ca AND en; END PROCESS; END rtl; ctrl子模块 该模块的功能是产生计时计数模块的计数允许信号cnten library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; entity ctrl is port(sysres,res,stst,cntclk:in std_ulogic; centen:out std_ulogic); end ctrl; architecture rtl of ctrl is signal enb1:std_ulogic; begin process(stst,sysres,res) begin if(sysres='1' or res='1') then enb1<='0'; elsif(stst'event and stst='1') then enb1<=not enb1; end if; end process; centen<=enb1 and cntclk;

end entity; architecture a of keyin is signal res0,res1,stst0,stst1 :std_logic; begin process(clk) begin if(clk'event and clk='0')then res1<=res0; res0<=reset; stst1<=stst0; stst0<=start_stop; end if; end process; process(res0,res1,stst0,stst1) begin res<=clk and res0 and (not res1); stst<=clk and stst0 and (not stst1); end process; end a; clkgen模块设计 该模块的功能是产生100Hz的计时允许信号cntclk和25Hz的宽度为1ms的 键输入时钟信号keycek. LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY cnt10 IS PORT (reset,en,clk:IN STD_LOGIC; carry:OUT STD_LOGIC; q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END CNT10; ARCHITECTURE rtl OF cnt10 IS SIGNAL qs :STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL ca :STD_LOGIC; BEGIN PROCESS(clk)

9s倒计时

《电子设计基础》课程报告设计题目:9s倒计时钟设计(采用4522)学生班级:学生学号:学生姓名:指导教师:时间:2011-6-26信息工程学院一.设计题目及要求设计一个9s倒计数时钟,采用4522芯片,在倒计到0s时自动回到8s进行倒计计数。

二.题目分析与方案选择4522是一种本身能够倒计数的芯片,是从1111到0000,要制作9s倒计数时钟,可以采用同步置数来实现。

在输入端置数1000就可以实现,PE 为高电平有效。

三.主要元器件介绍这就是4522COMS可预置计数管,PE为置数端。

P0~P3是输入端,Q1~Q3是输出端。

PE是置数端。

CP当然就是信号端,给时钟信号。

下面是他的功能表:4511引脚图:功能介绍如下:BI:4脚是消隐输入控制端,当BI=0 时,不管其它输入端状态如何,七段数码管均处于熄灭(消隐)状态,不显示数字。

LT:3脚是测试输入端,当BI=1,LT=0 时,译码输出全为1,不管输入 DCBA 状态如何,七段均发亮,显示“8”。

它主要用来检测数码管是否损坏。

EL:锁定控制端,当EL=0时,允许译码输出。

EL=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值。

DA、DB、DC、DD、为8421BCD码输入端。

OA、OB、OC、OD、OE、OF、OG:为译码输出端,输出为高电平有效。

CD4511的内部有上拉电阻,在输入端与数码管笔段端接上限流电阻就可工作。

CD4511是一个用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,特点如下:具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。

可直接驱动LED显示器。

四.电路设计及计算1.在仿真软件multisim上设计的电路图如下图:在输入端输入5HZ、5V的脉冲信号,因为是9秒倒计数即是1000-0111-0110-0101-0100-0011-0010-0001-0000所以将输入端置数为P3P2P1P0=1000,在输出端加上一个反馈,经过反向和与门反馈回置数端。