简易数字存储示波器研究

简易数字存储示波器实验报告

目录一.数字存储示波器简介及设计思路 (3)2.实验设计原理 (5)三、系统各模块的简单说明 (5)四.最终实现功能说明 (8)五.实验设计实现功能模块具体分析 (9)六、实验硬件分配及总体仿真波形 (15)一、数字存储示波器简介及设计思路数字存储示波器是20世纪70年代初发展起来的一种新型示波器。

这种类型的示波器可以方便地实现对模拟信号波形进行长期存储并能利用机内微处理器系统对存储的信号做进一步的处理,例如对被测波形的频率、幅值、前后沿时间、平均值等参数的自动测量以及多种复杂的处理。

而我们此次要设计的便是一种简易的数字存储示波器。

数字存储示波器可实现以下功能。

通过对来自信号源的信号进行采集(可分为实时取样和等效时间取样),将获得的值存储在内置RAM内,后期操作有对波形的显示、波形的测量(如测量频率、幅值、上升下降时延等)和波形处理(如双踪两波形的相加、相减、X-Y显示等等)。

其工作示意图如下所示:而我们设计的简易数字存储示波器实现的功能有对单一信道信号进行采样存储显示(分实时显示和存储后期调用显示)、对信号进行频率测量并显示数值、对波形进行上移、下移、扩展、收缩操作、示例波形演示(包括正弦波、锯齿波、方波)。

我们所用的硬件有实验箱上的高速的模数转换器TLC5510、FPGA芯片、单片机、LCD显示屏、FPGA内置RAM、外围扩展的RAM和键盘。

以下框图为实验箱硬件使用说明图:下移、扩展、收缩和测频的处理。

二、实验设计原理设计总体逻辑思路如下:系统开始工作时,通过按键选择是否开始检测波形,若是,则首先由频率检测器检测频率,然后根据测得的频率选择适当的采样频率。

信号源产生的信号通过A/D采样,采样结果保存在FPGA内置的存储器中。

待存储完一帧数据时进行输出到LCD上显示。

待显示100ms后暂停100ms以消除视觉暂留效应,然后准备下一帧数据的存储和显示。

如若需要存储波形,则在当前显示的同时,将采样得到的数据送往片外的SDRAM存储,直至存储结束或者存储容量达到上限。

数字存储示波器 实验报告

数字存储示波器实验报告数字存储示波器实验报告引言:数字存储示波器是现代电子测量领域中常见的一种仪器。

它通过将模拟信号转换为数字信号,并进行存储和处理,能够更准确地显示和分析电路中的信号波形。

本实验旨在通过使用数字存储示波器,对不同信号的波形进行观测和分析,并探究其在电子实验中的应用。

一、实验原理:数字存储示波器的工作原理主要包括信号采样、信号转换和信号显示三个过程。

首先,示波器通过采样装置对模拟信号进行采样,将其转换为离散的数字信号。

然后,通过模数转换器将离散的信号转换为数字信号,并将其存储在示波器的存储器中。

最后,示波器通过显示器将存储的数字信号转换为波形图形进行显示。

二、实验步骤:1. 连接电路:将待测的电路与示波器进行连接,确保信号源与示波器的输入端正确连接。

2. 设置示波器参数:根据待测信号的特点,设置示波器的采样频率、触发方式和时间基准等参数。

3. 开始测量:打开示波器电源,观察显示屏上的波形图形,并对波形进行分析和测量。

4. 调整参数:根据需要,调整示波器的参数,如水平和垂直灵敏度、触发电平等,以获得更清晰和准确的波形图形。

5. 结束实验:关闭示波器电源,断开电路连接,整理实验器材。

三、实验结果:通过实验,我们得到了多个不同信号的波形图形,并进行了分析和测量。

以下是实验中得到的一些典型结果:1. 正弦波信号:我们首先对一个正弦波信号进行观测。

通过示波器的显示,我们可以清晰地看到波形的周期、幅度和相位等特征。

通过测量,我们还可以得到波形的频率和峰峰值等具体数值。

2. 方波信号:接下来,我们对一个方波信号进行观测。

方波信号具有明显的上升沿和下降沿,通过示波器的显示,我们可以观察到方波的占空比和频率等信息。

同时,我们还可以通过示波器的测量功能,得到方波的上升时间和下降时间等参数。

3. 脉冲信号:最后,我们对一个脉冲信号进行观测。

脉冲信号具有较短的脉宽和较高的幅度,通过示波器的显示,我们可以观察到脉冲信号的上升时间、下降时间和脉宽等特征。

简易数字存储示波器设计

简易数字存储示波器设计摘要本文介绍了一种简易的数字存储示波器的设计。

示波器是一种广泛使用的电子测试仪器,用于显示电压随时间变化的波形。

数字存储示波器通过将波形样本存储在内存中,然后再进行显示,具有更高的分辨率和更多的功能。

本设计基于嵌入式系统,并通过一块液晶显示屏显示波形。

引言示波器是电子工程师和电子爱好者常用的测试设备之一。

然而,传统的示波器通常比较昂贵,且功能复杂。

为了满足一些简单的测试需求,我们设计了一款简易的数字存储示波器。

数字存储示波器具有存储和显示波形的功能,并且可以通过嵌入式系统实现。

本设计的核心部分是使用嵌入式开发板、模数转换器和液晶显示屏构建的简易数字存储示波器。

设计方案硬件设计嵌入式开发板本设计使用一块嵌入式开发板作为主要的处理器和控制单元。

开发板上应具备足够的计算能力和接口,以支持模数转换器、存储器和显示屏的连接。

模数转换器模数转换器(ADC)负责将输入的模拟信号转换为数字信号。

常见的ADC芯片有多种型号可选,选择合适的芯片以满足高精度和合适的采样率要求。

存储器用于存储模拟信号的样本数据。

根据要求,可以选择适当的存储器类型,如SRAM或SD卡。

显示屏显示屏用于显示存储器中的波形样本。

一块液晶显示屏是一个常见的选择,因为它可以提供高清晰度的图像和良好的视觉效果。

软件设计数据采集软件的第一步是通过ADC采集模拟信号,并将其转换为数字信号。

通过选择适当的采样率和转换精度,可以确保捕捉到所需的信号信息。

数据存储采集到的模拟信号样本将存储在嵌入式开发板的存储器中。

可以根据需要选择适当的存储器类型,以满足手头的需求。

从存储器中读取波形样本,然后将其显示在液晶显示屏上。

通过适当的算法和图形库,可以实现波形的平滑显示和良好的视觉效果。

操作流程本设计的操作流程如下:1.将待测试的电路连接到示波器的输入端口。

2.启动示波器,并设置合适的采样率和采样时间。

3.通过液晶显示屏查看波形样本。

4.根据需要对波形进行测量或分析。

数字存储示波器实验报告

数字存储示波器实验报告实验目的:1. 学习数字存储示波器的基本原理和使用方法。

2. 掌握数字存储示波器测量和显示波形的方法。

3. 理解数字存储示波器与模拟示波器的区别。

实验原理:数字存储示波器可以将模拟信号转换为数字信号,并通过数字方式存储和显示波形。

数字存储示波器使用的是采样信号方式,即每隔一段时间采集一次波形信号,将其转换成数字信号后保存在存储器中。

用户可以通过控制数字存储示波器的触发条件,来实现对特定波形的捕获和显示。

数字存储示波器与模拟示波器相比,具有很多优点。

例如,数字存储示波器可以使用自动测量功能,快速测量各种参数(如频率、周期、峰值等),并提供精确的数值结果。

数字存储示波器还可以捕获稀疏信号和故障信号,以及存储和重放波形,方便分析和调试。

实验步骤:1.将数字存储示波器接通电源,并将信号源与示波器连接。

调整信号源输出电压,并选择示波器的输入通道和延时/触发模式。

2.触发示波器并捕获波形。

通过控制示波器的触发条件和触发电平,调整示波器的采样时间和位置,以捕获特定波形的全部信息。

在捕获到波形后,用户可以对其进行保存和重放,也可以对波形进行缩放和移动,以便于更好地观察和分析。

3.测量波形的主要参数。

示波器可以通过内置的自动测量功能,对波形的主要参数(如峰-峰值、频率、周期、占空比等)进行快速测量。

用户还可以手动测量波形的特定参数,获得更加准确和具体的结果。

实验结果:通过本次实验,我们学会了数字存储示波器的基本原理和使用方法,并掌握了数字存储示波器测量和显示波形的方法。

我们还理解了数字存储示波器与模拟示波器的区别,并比较了它们的优缺点。

同时,通过实验数据的处理和分析,我们得到了电路波形的主要参数,并可以据此对电路性能进行分析和优化。

这对我们日后的电路设计和调试都非常有帮助。

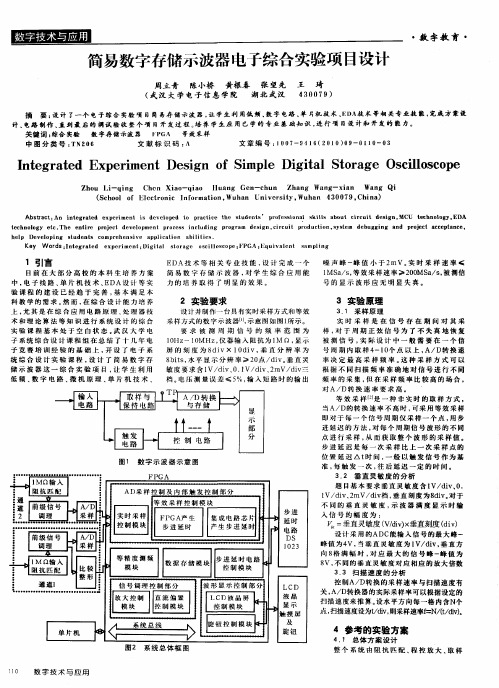

简易数字存储示波器电子综合实验项目设计

2 实验要求

设 计 并 制 作 一 台 具 有 实 时 采 样 方 式和 等 效 采样方式的数字示 波器_示意 图如图1 示。 1 1 , 所

3 实验原理

3. 采 样 原 理 1

实 时 采 样 是 在 信 号 存 在 期 间 对 其 采

要 求 被 测 周 期 信 号 的 频 率 范 围 为 1 Iz l M Hz, 器 输 入 阻 抗 为 1 0 , 示 O ~ 0 I 仪 M 显 屏 的 刻 度 为 8 V× l d V, 直 分 辨 率 为 di i 垂 0

.

e in,ic i p o u to sse d b g i g nd r jc a c pa c tc n lg e c Th e tr p oe t e eo me p oe s n l d n p o a e h oo y t . e n ie rj c d v lp nt r cs i cu i g rgrm d sg cr u t r d cin, yt m e u g n a p oe t ce tn e,

ห้องสมุดไป่ตู้

计, 电路 制 作 、 到 最 后 的 调 试 验 收 整 个 项 目开 发 过 程 。 养 学 生 应 用 已 学 的 专 业 基 础 知 识 , 行 项 目设 计 和 开 发 的 能 力 。 直 培 进 关 键 词 : 合 实验 数 字 存 储 示 波 器 FP 等 效采 样 综 GA 中 图 分 类 号 : 20 TN 6 文 献 标 识 码 : A

he p Devel l opi s udent c ng t s ompr ehens ve app i at or abi i i s. i l i l c Ite

K y W o d I t g a e e p r me t Di t l s o a e o c lo c p FP e r s: n e r t d x e t n ; gia t r g s il s o e; GA ; u va e t Eq i l n

简易数字存储示波器设计

简易数字存储示波器设计数字存储示波器是一款用于测量电信号的仪器,它可以将收集到的信号进行数字化处理,并将结果显示在屏幕上。

本文将介绍一个简易的数字存储示波器的设计。

1. 设计目标设计一个简易的数字存储示波器,使其能够接收并显示电信号的波形,并具备一定的存储功能。

该示波器需要具备以下功能:能够调节触发电平、可以调节扫描速度、能够通过按钮进行保存和回放存储的波形。

设计需要保证简易、易于操作、能够满足基本的测量需求。

2. 硬件设计(1)电路板设计:设计一个电路板用于信号的采集和存储。

该电路板包括模拟前端电路用于信号的采集,数字转换电路将模拟信号转换为数字信号,以及存储器用于存储采集到的数据。

(2)显示屏和按键:电路板上需要配备一个液晶显示屏,用于显示采集到的波形图像。

同时,设计按键用于调节触发电平、扫描速度以及保存和回放。

3. 软件设计(1)数据采集:通过模拟前端电路采集信号,并使用数字转换电路将模拟信号转换为数字信号。

采用适当的采样率,将数据进行采样,并存储到存储器中。

(2)数据显示:通过显示屏将存储器中的数据显示为波形图像。

根据采样率和扫描速度,将存储器中的数字信号转换为波形,并在屏幕上显示。

(3)触发控制:通过按键调节触发电平,设置触发条件,使得波形显示能够达到最佳效果。

设计合适的触发电路用于触发信号。

(4)数据存储和回放:设计按键和存储器用于保存和回放采集到的波形。

按下保存键后,将当前的波形数据保存到存储器中,按下回放键后,将存储器中的波形数据重新显示在屏幕上。

4. 使用方法使用该简易数字存储示波器,首先将信号源连接到示波器的输入端,然后通过按键进行触发电平的调节和扫描速度的设置。

在适当的触发条件下,示波器将开始采集并显示信号的波形。

当波形满足要求后,可以通过按键将波形数据保存到存储器中。

保存后的波形可以通过按键进行回放,重新显示在屏幕上。

5. 总结通过以上的设计和实现,可以得到一个简易的数字存储示波器。

简易数字存储示波器报告

号的的光迹要重叠。 3.4 控制器的设计

控制器的作用:控制、数据处理; 控制器的组成:控制器自身、人机接口。 1) 键盘 性质:矩阵扫描非编码键盘 组成:(8 个键)

对键盘的解释: (1)按下的键状态为“0”; (2)s/div 和 V/div 为+1 键 编码关系见表 6.1; (3)默认的仪器工作状态:0.2ms/div 、0.1V/div; (4)扩展移动键每按一次+5; (5)底层控制器(CPLD)扫描键盘,有键按下时向顶底层控制器 申请中断; (6)仪器的复位键(RESET)不属于键盘管理。

1

(2)总的不可调误差: ADC0808 为± 2 LSB,ADC 0809 为±1LSB。 (3)转换时间: 取决于芯片时钟频率,如 CLK=500kHz 时,TCONV=128 μs。 (4)单一电源: +5V。 (5)模拟输入电压范围: 单极性 0~5V;双极性±5V,±10V(需外 加一定电路)。 (6)具有可控三态输出缓存器。

INPUT3

R1

13k

+18v

C2

100pF

U1:A

8

R2

3

13k

1 2

4

C1

100pF

R4

50k

LF353

R3

50k

-18V

OUTPUT3

4)电平移位电路

为了适应 A/D 的要求,在进行模数转换之前必须将双极性信号 通过电平移位为单极性的,设计中将其移位为正极性信号。电路图及 仿真图如下:

-18V

3.1

前

向

通

道

作用:对被测信号进行调理、量化,并将量化结果写入存储器,

以备显示之用,它是核心部分。(初步构思)下图为前向通道的系统

数字存储示波器 实验报告

数字存储示波器实验报告数字存储示波器实验报告引言:示波器是电子工程师和科学家们在实验室中经常使用的一种仪器,用于观察和测量电信号的波形。

传统的示波器采用模拟技术,但随着数字技术的发展,数字存储示波器逐渐取代了传统示波器的地位。

本实验报告将介绍数字存储示波器的原理、特点以及在实验中的应用。

一、数字存储示波器的原理数字存储示波器是通过将输入信号转换为数字信号进行处理和存储,然后再将数字信号转换为模拟信号输出,从而实现对波形的观察和测量。

其基本原理如下:1. 采样:数字存储示波器通过采样电路对输入信号进行采样,将连续的模拟信号转换为离散的数字信号。

采样频率越高,采样精度越高,可以更准确地还原原始信号的波形。

2. 数字化:采样后的信号经过模数转换器(ADC)转换为数字信号。

模数转换器将每个采样点的电压值转换为相应的数字代码,以便后续的数字处理和存储。

3. 存储:数字存储示波器使用内部存储器或外部存储介质(如硬盘、闪存等)对采样后的数字信号进行存储。

存储器的容量决定了示波器可以存储的波形长度。

4. 数字处理:存储的数字信号可以进行多种数字信号处理操作,例如平均、峰值检测、FFT变换等。

这些处理操作可以提取出信号的特征,帮助工程师进行更深入的分析和测量。

5. 数字到模拟转换:经过数字处理后,数字信号再通过数模转换器(DAC)转换为模拟信号,输出到示波器的显示屏上。

通过示波器的控制面板,用户可以观察和测量信号的波形、幅值、频率等参数。

二、数字存储示波器的特点与传统示波器相比,数字存储示波器具有以下特点:1. 高精度:数字存储示波器采用数字信号处理,可以实现更高的采样精度和分辨率,对细微的信号变化更敏感。

2. 大容量存储:数字存储示波器内置存储器容量较大,可以存储更长时间的波形数据。

这对于长时间的信号观察和分析非常有用。

3. 方便回放:数字存储示波器可以将存储的波形数据进行回放,以便工程师反复观察和分析。

这对于捕捉瞬态信号、故障诊断等应用非常重要。

简易数字示波器的设计论文

简易数字示波器的设计摘要示波器是用量最多、用途最广的测量仪器之一,是观察和测量电子波形不可缺少的工具。

传统的模拟示波器在观测周期性重复频率较高的波形方面仍然得到普遍使用,但对于不能重复出现的单次信号、持续的非周期信号以及重复频率较低的周期信号则显得无能为力。

数字存储示波器正是基于上述要求而出现的。

数字示波器是新型智能化示波器,其技术基础是数据的采集,该技术可以应用于更广泛的数据采集产品中,具有深远意义。

本论文对示波器的工作原理进行了介绍,提出了一种基于STC12C5A60S2单片机和12864点阵液晶屏的数字示波器设计方案,实现对被测信号的采样、存储以及显示;扫描频率可调,幅度可调;设置10ms/div、2ms/div、1ms/div、500μs/div、400μs/div五档扫描速度,仪器的频率范围为DC~3kHz。

其依据是利用STC12C5A60S2芯片的AD转换器对输入的模拟信号进行采样,将采样值存入缓冲区经程序处理后在LCD液晶屏上显示出对应的波形。

实验结果表明本设计电路结构简单,运算速度高,频率显示准确,可以实现快速读取,波形显示刷新速度较快。

设计中采用的模块化设计方法,提高了设计效率。

整个系统成本廉价,并且实现了数字示波器的所有功能要求,达到了较高的性能指标。

关键词:单片机,液晶显示,数字示波器,AD采样THE DESIGN OF SIMPLE DIGITAL OSCILLOSCOPEABSTRACTThe oscilloscope is one of the most widely used measuring instruments, is an indispensable tool of observation and measurement of electronic waveform. Traditional analog oscilloscope observation cyclical high repetition frequency waveform is still widely used, but for a single signal that can not be repeated, sustained non-periodic signal, and low repetition frequency of periodic signals look powerless. Digital storage oscilloscope is based on the above requirements emerge. The digital oscilloscope is a new intelligent oscilloscope, its technology is based on the data acquisition, and the technology can be applied to a wider range of data acquisition products and has far-reaching significance.The paper describes the working principle of the oscilloscope, it puts forward a solution that based microcontroller STC12C5A60S2 and 12864 dot matrix LCD screen, digital oscilloscope design to achieve the measured signal, sampling, storage and display; scanning frequency is adjustable, amplitude adjustable; set 10ms/div、2ms/div、1ms/div、500μs/div、400μs/div fifth gear scanning speed, the frequency range of the instrument for DC ~ 3kHz. It is based on the AD converter in STC12C5A60S2 chip sample the input analog signal, the sampled values are stored in the buffer, then shows the corresponding waveform on the LCD screen after procedures.Experimental results show that this design is a simple circuit structure, high-speed operation, accurate frequency display, can be quickly read, waveform display refresh rate faster. Equivalent sampling techniques used in the design, can be a good high-speed periodic signal measurements require high-speed sampling, to reduce the requirements for the A / D conversion rate, reduce thehardware cost of the oscilloscope. The modular design approach adopted in the design, improves design efficiency highly. The whole system is very cheap, and fulfills all the functional requirements of the digital oscilloscope to achieve a higher performance.KEY WORDS:Single-chip Microcomputer, LCD, Digital Oscilloscope, AD Sample目录第1章绪论 (1)§1.1 课题背景 (1)§1.2 课题研究的目的和意义 (2)§1.3 课题的主要研究工作 (2)第2章系统设计方案的研究 (3)§2.1 系统设计的总体思路 (3)§2.2 系统设计任务 (3)§2.3系统设计的原理 (4)§2.4总体方案的选定 (5)§2.4.1 方案论证 (5)§2.4.2 系统框图 (5)第3章硬件电路设计 (7)§3.1 单片机的选型 (7)§3.1.1 STC12C5A60S2的内部结构 (7)§3.1.2 STC12C5A60S2的管脚说明 (8)§3.1.3 STC12C5A60S2的时钟 (9)§3.1.4 STC12C5A60S2的复位 (10)§3.2 A/D采样 (11)§3.2.1 A/D采样的基本原理 (11)§3.2.2 STC12C5A60S2的A/D结构和操作方法 (12)§3.3 12864液晶显示模块 (14)§3.3.1液晶显示模块概述 (14)§3.3.2显示RAM (14)§3.3.3点阵LCD的显示原理 (15)§3.4信号保持电路 (16)§3.5串口通信电路 (18)§3.6键盘控制电路 (19)第4章系统软件设计 (21)§4.1 软件架构 (21)§4.2 主程序的设计 (22)§4.3 波形显示程序的设计 (23)§4.4 按键检测程序的设计 (25)§4.5 软硬联调结果 (26)结论 (28)参考文献 (29)致谢 (30)附录 (31)第1章绪论§1.1课题背景本世纪70年代起,数字集成电路和微处理机技术获得了迅速发展,示波器也开始应用这些新技术来适应各种需要。

简易数字存储示波器研发设计报告

简易数字存储示波器设计报告摘要本设计分为四个模块,分别是:信号前向调整模块,数据采集模块,数据输出模块和控制模块。

信号前向调整模块采用高速低噪音模拟开关(MAX4545)和宽带运算放大器(MAX817)构成可编程运算放大器,对幅度不等的输入信号分别进行不同等级的放大处理。

数据采集模块采用可编程器件(EPM7128SLC84-15)控制高速A/D(TLC5510)对不同频率的输入信号分别以相应的采样速度予以采样,并将采样数据存在双口RAM(IDT7132)中。

数据输出模块采用另一片可编程器件(EPM7128SLC84-15)控制两片D/A(DAC0800)分别输出采样信号和锯齿波,在示波器上以X-Y的方式显示波形。

控制模块以AT89C52单片机为控制核心,协调两片可编程器件的工作,并完成其它的测量,计算及控制功能。

矚慫润厲钐瘗睞枥庑赖。

一.总体方案设计与论证:方案一:数字示波器采用数字电路,将输入信号先经过A/D变换器,把模拟波形变换成数字信息,暂存于存储器中。

显示时通过D/A变换器将存储器中的数字信息变换成模拟波形显示在模拟示波器的示波管上。

对于存储器的地址计数及数据存取可通过数字电路对时钟脉冲计数产生地址,并选通存储器来实现;对输入信号何时触发采集可通过模拟比较器及其它简单的模拟电路实现。

但是,这种方法的硬件电路过于复杂,调试起来也不方便,不利于系统的其它功能扩展,因而不可采取。

聞創沟燴鐺險爱氇谴净。

方案二:采用AT89C52单片机。

单片机软件编程灵活,自由度大。

可通过软件编程实现对模拟信号的采集,存储数据的输出以及各种测量,逻辑控制等功能。

但是,系统要求的频带上限为50KHZ,根据采样定理,采样速度的下限为100KHZ,需要用高速A/D进行采样。

假设单片机系统用12M的晶体振荡器作为系统时钟,那麽一条指令就需要1us或2us,根本无法控制A/D高速工作。

因此,单纯用软件是不可能实现该系统的。

简易数字存储示波器实验报告.doc

简易数字存储示波器实验报告基于FPGA的简易数字存储示波器的设计ⅰ.数字存储示波器的介绍和设计思路ⅱ。

实验设计原则三。

系统模块四简述。

最终实施功能描述八。

实验设计实现功能模块具体分析9六.实验硬件和整体仿真波形的分配15数字存储示波器简介及设计思路数字存储示波器是XXXX早期开发的一种新型示波器。

这种示波器可以方便地实现模拟信号波形的长期存储,并且可以通过使用机内微处理器系统进一步处理存储的信号,例如自动测量参数,例如频率、幅度、前后沿时间、平均值等。

和各种复杂的过程。

这次我们将设计一个简单的数字存储示波器。

数字存储示波器可以实现以下功能。

通过从信号源收集信号(可分为实时采样和等效时间采样),获得的值存储在内置的随机存取存储器中。

后期操作包括波形显示、波形测量(如测量频率、幅度、上升和下降时间延迟等)。

)和波形处理(例如两个波形的加法、减法、X- 3,以及系统的每个模块的简要描述...............六.实验硬件和整体仿真波形的分配15数字存储示波器简介及设计思路数字存储示波器是XXXX早期开发的一种新型示波器。

这种示波器可以方便地实现模拟信号波形的长期存储,并且可以通过使用机内微处理器系统进一步处理存储的信号,例如自动测量参数,例如频率、幅度、前后沿时间、平均值等。

和各种复杂的过程。

这次我们将设计一个简单的数字存储示波器。

数字存储示波器可以实现以下功能。

通过从信号源收集信号(可分为实时采样和等效时间采样),获得的值存储在内置的随机存取存储器中。

后期操作包括波形显示、波形测量(如测量频率、幅度、上升和下降时间延迟等)。

)和波形处理(如加法、减法和双迹X两种波形)。

我们设计的简易数字存储示波器具有单通道信号的采样、存储和显示(包括实时显示、存储和后期调用显示)、信号的频率测量和数值显示、波形的向上、向下、扩展和收缩以及采样波形的演示(包括正弦波、锯齿波和方波)等功能。

我们使用的硬件包括实验箱上的高速模数转换器TLC55。

简易数字存储示波器

简易数字存储示波器摘要本简易数字存储示波器由信号输入电路、数据采集与存储电路、A/D与转D/A换电路以及AT89C51单片机系统组成。

本仪器利用软件的强大功能,配合普通示波器可以实现任意波形输入信号的单次触发存储显示、存储回放,并按要求进行了扫描速度和垂直灵敏度的档位设置,波形显示无明显失真。

关键词:简易采集存储单片机转换电路一、方案设计与比较论证数字存储示波器的一般设计原理是:先用A/D转换器将被测信号数字化,并写入数字存储器,在需要显示时,再从存储器中读出,经过D/A转换器还原为模拟信号,送到示波器的相应输入口。

1.模拟通道:系统需要对模拟信号的实时采集存储,模拟通道的性能直接影响系统的性能。

方案一:利用集成放大器AD524组成模拟通道。

考虑到本题目的要求,垂直灵敏度的档位不是很多。

可以利用AD公司生产的AD524,其组成的差分放大器,外电路简单,可以实现本题要求,但其价格非常高,用在此处性价比不是太高,所以不采用此电路。

方案二:利用模拟开关和运算放大器组成增益可控的放大器,这样可以较为方便的控制增益,可以利用较少的级数达到较好的要求,这样有利于减少误差便于逐级累加。

本电路采用常用集成电路,电路非常成熟,性价比高,所以本电路采用了该方案。

2、控制模块方案论证方案一:采用大规模可编程逻辑器件作为系统的控制核心。

目前,大规模可编程逻辑器件容量不断增大,速度不断提高,且多具有ISP 功能,也可以在不改变硬件电路的情况下改变功能。

但其对数据的采集速率要求较高,对数据的处理相对较弱,必须使用高速大规模可编程逻辑器件作为控制核心。

普通的可编程逻辑器件难以满足对采样速率的要求。

高速可编程逻辑器件时钟频率不过几十兆,其价格昂贵,普及程度不高。

考虑到以上因素,没有采用此方案方案二:利用现在较为流行的单片机控制高速A/D转换器和RAM实现高速数据采集。

单片机虽速度不是特别快,但使用较少的外围器件就可以实现复杂的逻辑和时序控制功能,是较为理想的方案,所以本电路采用该方案。

物理实验数字示波器

实验13 数字存储示波器实验目的1.了解示波器的基本工作原理和结构;2.学习示波器的基本使用方法;3.学习使用示波器测量正弦波信号的电压和周期;4.学习使用示波器观察李萨如图形。

实验仪器GDS2062数字存储示波器、F05A型数字信号发生器等实验原理1.数字存储示波器的基本原理数字存储示波器(简称数字示波器)与模拟示波器的结构完全不同,它是以微处理器系统(CPU)为核心,再配以数据采集系统、显示系统、时基电路、面板控制电路、存储器及外接控制器等组成。

其简单工作原理见图。

输入的模拟信号首先经垂直增益电路进行放大或衰减变成适于数据采集的模拟信号,随后的数据采集是将连续的模拟信号通过取样保持电路离散化,经A/D变换器变成二进制数码,再将其存入存储器中,采集是在时基电路的控制下进行的,采集的速率可通过“秒/格”旋钮来控制。

采集到的是一串数据流(二进制编码信息),在CPU的控制下依次写入随机存储器中,这些数据就是数字化的波形数据,CPU再不断地将这些数据以定速依次读出,通过显示电路将其还原成连续的模拟信号,使其在显示器上显示出来,屏幕在显示波形的同时,还通过微处理器对采集到的波形数据进行各种运算和分析,并将结果在显示器的适当位置上数字显示出来。

面板上的按钮和旋钮的功能设置都可直接在显示器上数字显示,数字示波器还有RS-232、GPIB等标准通信接口,可根据需要将波形数据送到计算机作更进一步的处理或送打印机打印记录。

2.GDS2062数字存储示波器基本操作图13-1 数字示波器的工作原理图A区:功能控制打开示波器后面的电源开关,按ON/键,示波器通电自检,按AUTOSET 键,示波器自动显示合适的波形。

(1)垂直控制区的操作 通道选择:按下CH1,黄色指示灯亮,示波器显示黄色线为CH1通道信号,按“AUTOSET ”键,示波器自动显示合适的波形。

同样按下CH2,蓝色指示灯亮,示波器显示蓝色线为CH2通道信号。

简易数字存储示波器

简易数字存储示波器摘要:本系统基于采样定理,通过高速A/D转换实现实时采样法,完成了一个简易数字存储示波器的基本功能。

由于采用12位A/D转换器,其垂直分辨率可达512级/div。

该示波器同时具有单次触发、连续触发、锁存及双踪示波等显示方式,并可通过外置旋钮对显示波形进行上下左右移动操作。

通过外部程控放大电路和内部采样率的改变可以实现垂直灵敏度三档可调及水平扫描速度五级可调。

同时,我们还扩展了X-Y显示、频率测量及幅度测量等功能。

整个系统采用键盘结合旋钮的操作方式,界面友好。

关键字:示波器;采样;触发Abstract:This system,based on the sampling theorem,realized real-time sampling method via high-speed A/D convertion,performing the general function of simple digital storage oscillograph.Its vertical resolution reaches 512 level/div.Besides four display modes including single triggering,serial triggering,latch and dual trace,the waveform can be moved vertically and horizontally through external knob.The adjusting of three-level vertical sensitivity and five-level horizontal scaning velocities can be achieved by external programmable amplifying and internal alteration of sampling rate.Furthermore,we also extend the function of X-Y display,measuring frequency and amplitude.The entire system adopts the operation mode of keyboard combining knob,of which the interface is friendly.Keywords:oscillograph;sampling;trigger一、方案论证与选择1.题目任务要求及相关指标的分析题目要求设计并制作一个示波器,能实现现有的示波器中一些简易的功能。

数字存储示波器毕业论文

摘要数字存储示波器是随着数字电路的发展而发展起来的一种具有存储功能的新型示波器。

原先人们看好的模拟示波器的一些优点,目前数字示波器已完全能够做到,特别是在捕获非重复信号、避免信号的虚化和闪烁、在时间上从触发事件反问寻迹——实现在电路中隔离故障等方面,数字示波器显示出了模拟示波器无可比拟的优势。

因此,数字示波器由于其优势的性能、良好的性能价格化,刚一问世,就显示出它强大的生命力,各行各业均迫切需要,有其广阔的发展前途。

本简易数字存储示波器,以单片机为控制核心,由通道调理、触发、波形显示等功能模块组成。

本系统对触发系统、水平扫描速度和垂直灵敏度的自动设置功能(AUTOSET)及波形参数测量等功能进行了重点设计。

设计中采用了模块化设计方法,并使用了多种EDA工具,提高了设计效率。

整个设计实现了存储示波器的所有功能要求,达到较高的性能指标。

关键词:存储器,转换器,数字存储示波器,单片机ABSTRACTIt is that one developed with development of the digital circuit is new-type oscillograph which stores the function that the figure stores the oscillograph . Original ancestors see some advantages of the good simulation oscillograph , the digital oscillograph can already be accomplished at present, catching and is not repeating the signal, avoiding melting and glimmers specially emptily, reply the mark of seeking from the incident of touching off on time of the signal --Realizing it in isolating the trouble in the circuit etc., the digital oscillograph demonstrates the incomparable advantage of the simulation oscillograph . So digital oscillograph because performance , good performance price of advantage their, just coming out , demonstrated its strong vitality, all trades and professions needed urgently , there is its wide development prospect. .T his simple and easy figure stores the oscillograph, regard one-chip computer as the core of controlling, nursed one's health, touched off by the pass-way, the wave form shows, etc. the function module makes up . Such functions as automatic establishment function (AUTOSET ) and wave form parameter that this system scanned the speed and vertical sensitivity in touching off system , level are measured have been designed especially. Have adopt the module design method in the design, has used many kinds of EDA tools, have improved design efficiency. The whole of functions of designing and realizing storing the oscillograph require , reach the higher performance indexKeyword: the memory , the converter, the figure stores the oscillograph , Micro Computer Unite毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

数字存储示波器实验报告

数字存储示波器实验报告数字存储示波器实验报告引言:示波器是电子工程师和科学家在测量和分析电信号时不可或缺的工具。

传统的示波器使用模拟技术,但随着技术的发展,数字存储示波器逐渐取代了传统示波器的地位。

数字存储示波器通过将信号转换为数字形式进行处理和存储,具有更高的精确度和更多的功能。

本实验旨在探究数字存储示波器的原理和应用。

一、实验目的本实验旨在:1.了解数字存储示波器的原理和工作方式;2.掌握数字存储示波器的基本操作方法;3.熟悉数字存储示波器的应用场景。

二、实验原理数字存储示波器是通过将输入信号转换为数字形式进行处理和存储的。

它由输入部分、采样部分、数字处理部分和显示部分组成。

1.输入部分输入部分负责接收待测信号,并将其转换为电压形式。

通常使用探头将待测信号与示波器连接,探头会将信号转换为与示波器输入电路兼容的电压信号。

2.采样部分采样部分负责对输入信号进行采样。

数字存储示波器通过采样率来确定每秒采样的次数。

采样率越高,示波器对信号的还原能力越好。

3.数字处理部分数字处理部分负责将模拟信号转换为数字信号,并进行处理和存储。

它包括模数转换器(ADC)和数字信号处理器(DSP)。

ADC将模拟信号转换为数字信号,DSP对数字信号进行处理和存储。

4.显示部分显示部分负责将处理后的数字信号转换为可视化的波形图。

数字存储示波器通常使用液晶显示屏或计算机显示屏来显示波形图。

三、实验步骤1.连接示波器和待测信号:将示波器的探头连接到待测信号源上,确保连接正确且稳定。

2.设置示波器参数:打开示波器,并根据需要设置采样率、时间基准、触发模式等参数。

这些参数将影响示波器对信号的采样和显示。

3.观察波形图:示波器将采样和处理后的信号转换为波形图显示在屏幕上。

通过观察波形图,可以分析信号的频率、振幅、相位等特征。

4.测量信号参数:示波器可以提供多种测量功能,如测量频率、周期、峰峰值、有效值等。

根据需要选择相应的测量功能,并进行测量。

便携式数字存储示波器设计

大学毕业论文便携式数字存储示波器设计摘要随着科学技术的发展,作为常用的检测工具,示波器的面貌也焕然一新。

由于数字技术的采用,示波器成为集显示、测量、运算、分析、记录等各种功能于一体的智能化测量仪器。

数字存储示波器(DSO)将取代模拟示波器。

目前,国内具有自主知识产权的数字存储示波器产品还非常少,高昂的价格阻碍了数字存储示波器在生产和试验中广泛的应用。

在研究剖析数字存储示波器产品工作原理的基础上,本文提出了一种新的设计思路,并详细论述了其设计和实现过程。

本文设计的便携式数字存储示波器采用CPU+CPLD(复杂可编程逻辑器件)的智能仪器结构,使用液晶显示器(LCD)显示。

CPU﹢CPLD系统的最大特点是结构灵活,有较强的通用性,适用于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统易于维护和扩展。

Winbond公司的单片机W77E58作为系统的核心,调控整个系统正常运行,同时完成对数据的处理。

Altera公司的EPM7064S作为系统的外围控制器,实现对系统的FIFO(先进先出存储器)与采样时钟的控制。

采用液晶屏显示,为用户提供友好的界面,并实现了系统的小型化和便携式。

本文详细地介绍了数字存储示波器的工作原理及其技术特点,接着给出了本系统硬件和软件设计的结构及思路。

硬件设计方面,本文主要讨论了信号调理电路、A/D变换电路、时基电路及触发电路的设计等。

通过具体的开发设计,解决了关于实时嵌入式系统的一些有意义的实际问题,基本实现了本文的设计目标。

关键词:数字存储示波器;单片机;复杂可编程逻辑器件;液晶显示AbstractWith the development of science and technology, the oscilloscopes, as common instruments, have made great progress. With digital technology, the oscilloscopes have become a kind of intelligent instrument with functions: waveform display, parameter measure, detecting, analyze, storage, and so on. The Digital Storage Oscil loscope (DSO) will replace Analog Oscilloscope. At present, domestic DSO product's type, which has our own independent property right, is too few. The DSO is hindered to apply wildly in our production and test by high price. On the basis of the analysis of DSO's fundamental principle, the design and implementation of a kind of portable digital storage oscilloscope system was discussed in detailed in the dissertation.The system discussed in the dissertation has the architecture built with CPU and CPLD (complex programmable logic device), and use liquid crystal display (LCD). The structure's most important feature is flexible structure and general usage. It enables designer to develop product within shorter time, and the system can be expanded easily.The theory and characteristic of DSO are amply introduced, then the hardware-software design frame and thought are given. Signal condition circuit, A/D circuit, time-base circuit and trigger circuit are discussed. Some signality practical problems about the real time embedded system are resolved while developing the portable DSO. The paper's design object is basically achieved.Key Words: DSO;Single-chip Microcomputer;CPLD;LCD目录摘要 (I)Abstract ..................................................................................................................... I I第1章绪论 (1)1 .1示波器简介 (1)1.2示波器的国内外研究现状 (2)1.3课题背景及主要工作 (5)第2章数字存储示波器的原理及相关应用技术 (7)2.1数字存储示波器的基本原理 (7)2.2数字存储示波器的主要技术指标 (8)2.3数字存储示波器的主要特点 (11)2.4取样原理及数字示波器的取样方式 (13)2.4.1取样原理 (13)2.4.2数字示波器的取样方式 (14)2.5示波器的工作模式 (16)第3章系统方案设计及关键部件的选用和介绍 (18)3.1系统方案设计 (18)3.1.1实时信号处理系统概述 (18)3.1.2系统总体方案 (19)3.2系统关键部件的选用及介绍 (22)3.2.1 CPU部件 (22)3.2.2可编程逻辑器件 (25)3.2.3模数转换部件 (30)3.2.4系统缓存部件 (33)第4章数字存储示波器的硬件电路设计 (40)4.1前端信号的调理电路 (40)4.1.1高阻衰减电路 (41)4.1.2 阻抗变换 (42)4.1.3前置放大与1、2、5衰减电路 (42)4.1.4驱动放大 (44)4.2数据采集与存储电路的实现 (44)4.3时基电路设计 (45)4.3.1时基调整与系统采样速率 (45)4.3.2系统采样速率调节的实现 (47)4.3.3时钟分频电路设计 (48)4.4触发系统设计 (50)4.4.1触发信号的产生与整形 (50)4.4.2触发方式的实现 (52)4.5单片机系统I/0口的扩展 (53)4.5.1 8255可编程并行I/O扩展接口 (53)4.5.2串入并出扩展I/O口 (54)4.6入机接口 (55)4.7通讯接口 (57)第5章示波器的软件设计 (59)5.1软件设计概述 (59)5.2系统软件结构设计 (60)5.2.1上电初始化主要工作流程 (62)5.2.2数据处理及显示程序的实现 (63)5.2.3键盘的响应 (64)5.3混合编程技术 (65)5.3.1 C51和汇编语言的性能比较 (65)5.3.2混合编程的规则 (66)5.4示波器算法的研究 (67)5.5绘图的实现 (70)5.5.1波形显示方法 (70)5.5.2液晶显示器汉字输出技术 (71)第6章系统可靠性与抗干扰设计 (73)6.1硬件的抗干扰设计 (73)6.1.1信号完整性分析 (74)6.1.2高速电路设计注意事项 (75)6.2系统软件抗干扰设计 (76)结论 (79)致谢 (81)参考文献 (82)第1章绪论1 .1示波器简介人类在认识自然和改造自然的过程中,必定要进行测量活动。

数字存储示波器的使用实验报告

数字存储示波器的使用实验报告篇1示波器的使用预习思考题1.示波器的功能是什么?2.扫描同步如何理解?3.什么是李萨如图?1.电子示波器是用来直接显示,观察和测量电压波形机器参数的电子仪器。

2.用每一个触发脉冲产生于同触发电压所对应的触发信号的同相位点,故每次扫描起点会准确地落在同相位点于是每次扫描的起始点会准确地落在同相位点,于是每次扫描出的波形完全重复而稳定地显示被测波的波形。

就是触发扫描实现同步的原理。

3.当示波器在Y轴与X轴同时输入正弦信号电压且他们的频率式简单的整数比时荧光屏上出现各式各样的图形这类图形称作“李萨如图”实验数据记录实验仪器:YB4320F双追踪示波器,SG1642函数信号发生器实验步骤:1.用示波器观察信号波形(1)调节扫描旋钮,使示波器的扫描线至长短适当的稳定水平亮线(2)将信号发生器接到ch1或ch2输入上,频率选用数百或数千赫兹方式开关及触发源开关的位置与信号输入通道一致的出稳定的波形。

(3)改变输入信号电压的波形,如正弦波,三角波,方波调节扫描微调,以得到2个。

(4)可以在调节其他该扫描熟悉示波器2.用李萨如图测定频率(1)当示波器在Y轴与X轴同时输入正弦信号电压,且他们的频率式简单的整数比的的荧光屏上出现各种形式的图形,这类图形称作“李萨如图”(2)当fg:fx=1:1时输入fg=50hz.fx=50hz,绘出一种李萨如图(3)当fg:fx=1:2时输入fg=300hz.fx=200hz,绘出一种李萨如图。

思考题1.示波器为接通前,有那些注意事项?2.波形不稳定时,应调节那个旋钮?3.为了观察李萨如图,应该怎样设置按钮?4.欲关闭示波器,首先应把那个旋钮扭到最小?1、确定是否接地2、是否正确连接探头3、查看所有的终端额定值4、在是使用一个通道的情况下触发源选的通用一致5、应调节水平微调使之稳定,再调节CH通道6、首先示波器应该在XY轴输入正弦电压,且加上fg与fx上的频率成整数比7、将示波器探头脱开测量电路,将输入选择开关,达到接地位置,关机,如果是模拟示波器的话,需要将聚集旋钮和亮度旋钮调低,然后在关闭电源。

简易数字存储示波器论

1 引言1.1 选题的背景意义和研究现状1.1.1 选题的背景和意义1909年的诺贝尔物理奖得主Karl Ferdinand Braun于1897年发明世界上第一台阴极射线管示波器,至今许多德国人仍称CRT为布朗管(Braun Tube)。

根据IEEE 的文献记载1972年英国的Nicolet公司发明了第一台的数字示波器(DSO) ,到1996年惠普科技(安捷伦科技前身)发明了全球第一台混合信号示波器(MSO),数字示波器自上个世纪七十年代诞生以来,其应用越来越广泛,已成为测试工程师必备的工具之一。

时间到了21世纪这是一个科学和技术都在飞速发展的时代,随着电子技术、计算机技术、通信技术和自动化技术的高速发展,电子测量仪器也有了巨大的发展。

数字式示波器就以其存储波形及多种信号分析、计算、处理等优良的性能从而逐步取代模拟示波器。

用数字示波器能完成对信号的一次性采集,把波形存储起来,还可以通过移位操作观察波形的任何一部分等等。

数字存储示波器是随着数字集成电路技术的发展而出现的新型智能化示波器,己经成为电子测量领域的基础测试仪器。

随着新技术、新器件的发展,它正在向宽带化、模块化、多功能和网络化的方向发展。

数字存储示波器的优势是可以实现高带宽及强大的分析功能。

现在高端数字存储示波器的实时带宽已达到20GHz ,可以广泛应用于各种千兆以太网、光通讯等测试领域。

而低端数字存储示波器几乎可以应用于国民经济各个领域的通用测试,同时可广泛应用于高校及职业学校的教学,为社会培养众多的后备人才。

数字存储示波器的技术基础是数据采集,其设计技术可以应用于更广泛的数据采集产品中,具有深远的意义。

为了巩固大学4年来所学的知识,将课本上的理论知识运用到实际中,而且能掌握和了解本专业的仪器测量这块的先进发展趋势,我选择了简易数字存储示波器这个题目作为的大学毕业设计题目。

1.1.2 国内外研究现状自从1972年世界上第一台数字存储示波器(DSO ,又称数字示波器)问世以来,经历了三个发展阶段。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

简易数字存储示波器研究

基于MCU8051和FPGA的控制平台,采用实时采样与等效采样两种方式实现了时频率为10Hz-10MHz的波形数据的实时采样,存储与回放。

做到垂直灵敏度含1v/div,0.1v/div和2my/div三档,扫描速度合20ms/div,2uv/div,100ns/div 三档。

系统的频率测量精度达0.001Hz,电压测量精度达0.05V。

自带100KHz 方波信号为系统测频时钟与电压基准源的进行自动校准,此外,还实现了对波形数据的单次触发存储与调出功能和AUTO显示功能。

标签:数字存储;示波器;等效采样;实时采样

1引言

数字存储示波器是20世纪70年代初发展起来的一种新型示波器。

这种类型的示波器可以方便地实现对模拟信号波形进行长期存储并能利用机内微处理器系统对存储的信号做进一步的处理,例如对被测波形的频率、幅值、前后沿时间、平均值等参数的自动测量以及多种复杂的处理。

数字存储示波器的出现使传统示波器的功能发生了重大变革。

2数字存储示波器基本工作原理

数字存储示波器在信号进入示波器后立刻通过高速A/D转换器将模拟信号快速采样、存储。

通过单片机对信号进行处理,得到信号的波形参数,存储并通过D/A转换器后可由示波器显示,从而实现模拟示波器的功能。

但相对于模拟示波器,数字示波器测量精度高,还可对信号进行存储。

本系统的原理方框图如图1所示:

3系统功能模块与硬件电路

基于数字示波器的基本原理,可以把整个系统分为频率测量、采样保持、触发方式选择、位置调节、显示控制几个主要的模块。

模拟信号通过信号调理模块(阻抗变换、程控放大、触发电路),将模拟信号的幅值大小调整到高速AD(AD9225)的输入范围0V-4V。

然后通过AD9225对信号进性采样。

我们采用外部有源晶振作为高速AD的采样时钟来控制恒定的采样率4MHz(晶振的固有振荡频率),在FPGA内部增加波形存储控制模块,当满足触发条件时FP-GA以下抽样的方式对AD转换得到的数据进行存储,抽样频率由可水平分辩率来控制(若为AUTO功能,则与信号的频率有关)。

将抽样的数据分别存储到双口RAM中,在送人行列扫描电路(2片DAC0800)前经过了波形显示控制模块,它的作用是对RAM的数据及读入起始地址的进行处理。

从而实现波形在模拟示波器上的左右平移。

同时在FPGA内部实现了512点的FFT计算,成功得分析了输入信号的频谱。

系统的连接框图如图2所示:

3.1频率测量部分

此系统对低频信号采用测周法,对中高频信号采用等精度测频法。

测周法,即以待测信号的周期为门限时间T,用计数器记录在此门限时间T内的高频标准时钟脉冲数,从而确定待测信号的频率。

当选定高频时钟脉冲而被测信号频率较低时可以获得很高的精度,而被测信号频率过高时由于测量时间不够会有精度不够的问题,适用于低频信号的测量。

等精度测频法,这种方法和测周期法很相似,不同的是测周期法测量时间T为被测信号的一个周期,而等精度测量法的测量时间T是由人为设定和被测信号共同决定的。

即在人为设定的时间内,闸门的开启和闭合由被测信号的上升沿来控制,计数器真正开始计数的时刻不是预置闸门的开始时刻,而是预置闸门打开后被测信号的第一个上升沿到来的时刻;同样闸门的关不时刻不是预置闸门的结束时刻,而是预置闸门关闭后被测信号的第一个上升沿到来的时刻,这种计数方法叫做相关计数法。

最后根据计数结果、标准时钟频率和被测信号上升沿个数就可以精确得到被测信号的频率。

3.2采样部分

采用等差距采样实现信号采集。

以信号的某相位点为触发,用一足够快的脉冲作为计数脉冲(该脉冲可由低频脉冲经过锁相环倍频得到),每次FPGA内部控制器被触发后,计数器清零,同时开始对高频脉冲进行计数,每次计到一定的脉冲数,开始采样。

而每一次计到的脉冲数为一等差数列,从而采到波形数据中的各相位点。

由于每次采样都由被测信号触发,该方案采样点的位置严格可控,难点在于要求对软件控制时序严格控制。

4系统指标测试

给仪器一个有效值为2V,不同频率的正弦波信号,测得系统的水平分辨率如表1。

给仪器一个频率为10K的正弦波信号,测量系统垂直分辨率如表2。

由测量数据可知频率精度完全达到要求。

5結语

采用上述方法设计的数字存储示波器,以51单片机为核心,充分发挥了FPGA的高速和稳定性。

通过软硬件的结合实现了数字存储示波器的设计,系统功能完善,稳定性高,方便控制,满足了工程需要。