第13讲全定制版图设计基础_2详解

集成电路后端设计简介.pptx

N型MOS管物理结构和电路符号

栅极 源极

导体 绝缘体

栅极

栅极

n

n

p 掺杂半导体衬底

n 型MOS管

漏极 源极

漏极 源极

漏极

衬底 耗尽型电路符号

衬底 增强型电路符号

第6页/共74页

P型MOS管物理结构和电路符号

栅极 源极

导体 绝缘体

栅极

栅极

p

p

n 掺杂半导体衬底

p 型MOS管

漏极

源极

第37页/共74页

CMOS传输门

CMOS传输门工作原理: 在图中的CMOS传输门采用了P管和N管对,控制信号和C分别控制P管和N管,使两管同时关断和开通。

由于PMOS管对输入信号S高电平的传输性能好,而NMOS管对输入信号S低电平的传输性能好,从而使信 号S可以获得全幅度的传送而没有电平损失。

第38页/共74页

第14页/共74页

MOS晶体管性能分析

描述NMOS器件在三个区域中性能的理想表达式为:

Ids=

0

(a)截止区

Vgs-VT≤0

(b)线性区

0<Vgs-VT< Vds (c)饱和区

第15页/共74页

MOS器件电压-电流特性

N型MOS管和P型MOS管工作在线性区和饱和区时的电压-电流特性曲线:

线性区 ︱Vds︱=︱Vgs-Vt︱

(0V)。值得指出的是,任一种逻辑状态,不管

是Vi为VDD或为VSS,两个晶体管必有一个截止。

因此,在任一逻辑状态下,只有非常小的电流从

VDD流向VSS,所以耗电很少。对高密度应用来说,

CMOS的低功耗是它最重要的优点。

第24页/共74页

第13讲 软件产品线

1.网构软件模型 网构软件模型

基于面向对象模型,提出了一种基于Agent、以软件体系结构为中 心的网构软件模型,如图所示。

2.网构软件中间件 网构软件中间件

图为网构软件中间件模型:

3.网构软件开发方法 网构软件开发方法

图为网构软件开发方法体系。

4. 进一步的工作

进一步的工作主要是加强现有成果的深度和广度。在深度方 面,完善以软件体系结构为中心的网构软件技术体系,重点突破网 构软件智能可信模型、网构中间件自治管理技术、以及网构软件开 发方法的自动化程度。在广度方面,多网融合的大趋势使得软件将 运行在一个包含Internet、无线网、电信网等多种异构网络的复杂 网络环境,网构软件是否需要以及能否从Internet延伸到这种复杂 网络环境,成为我们下一步的主要目标。

2. 软件产品线

软件产品线是一组具有共同体系构架和可复用组件的软件 系统,它们共同构建支持特定领域内产品开发的软件平台。软 件产品线的产品则是根据基本用户需求对产品线架构进行定制, 将可复用部分和系统独特部分集成而得到。软件产品线方法集 中体现一种大规模、大粒度软件复用实践,是软件工程领域中 软件体系结构和软件重用技术发展的结果。 与软件体系结构的发展类似,软件产品线的发展也很大地 得益于军方的支持。如美国国防部支持的两典型项目:基于特 定领域软件体系结构的软件开发方法的研究项目(DSSA)和 关于过程驱动、特定领域和基于重用的软件开发方法的研究项 目(STARS)。这两个项目在软件体系结构和软件重用两方面 极大地推动了软件产品线的研究和发展。

应用 体系 结构 提取 车间

应用体系 结构库

构件 生产 车间

构 件 库组装 车间应用 体系标准规范

与 图 13-1 软件生产线

全定制版图设计学习

– 这类集成电路也是采用ASIC技术设计和制造的,但它是作为标准产品买 给多个用户,它被列入制造商的产品目录中。

– 如LAN用电路、图形处理用集成电路、通信用CODEC等

• 按设计风格分类

–通用集成全定制(full-custom)方式。 • 它主要是基于晶体管级的芯片设计,芯片中的全部器件及互 连线的版图都是按照系统要求进行人工设计的,尽量达到密 度高、速度快、面积小和功耗低的要求,因此批量生产时经

• 点击File new library 弹出new library 窗口,建立library-命名为20121125hwx

•通常

在name框键work,右边选Attach to an existingtechfile,我这里没有工艺库,所以选择第一个。 • 在弹出的窗口中Technology Library中选择自己的工艺 库,我这里在相应窗口写入自己的工艺文件。

Full‐custom设计流程

电路设计

• 依据系统功能与指标要求选定电路结构

– 并行/串行;单端/差分;„ • 依据结构分配指标,决定各单元的类型与 电路形式 – 放大器类型、电路;比较器类型、电路;„

• 依据交、直流参数设定元件值

– 晶体管W/L;电阻阻值;电容容值

电路仿真

• 依据所给定的元件模型来验证所设计的电路的功 能和指标 • 提供电路结构、电路类型、元件参数等修改的依

点击OK后,出现如下界面,说明库已建好。

首先建立一个不非门nand单元,如下所示:

• 点击File new cellview 弹出create new file窗口 • Library name: 20121125hwx; cell name: nand; tool: 选Composer‐Schematic

版图设计课件 PPT

一、双极集成电路工艺的基本流程

实现选择性掺杂的三道基本工序

(3)掺杂:在半导体基片的一定区域掺入一定浓度的杂质 元素,形成不同类型的半导体层,来制作各种器件。掺 杂工艺主要有两种:扩散和离子注入。

扩散:在热运动的作用下,物质的微粒都有一种从高浓 度的地方向低浓度的地方运动的趋势。在IC生产中,扩 散的同时进行氧化。

结论:对采用PN结隔离的双极IC基本工艺,与制作NPN 晶体管的基本工艺相比,只需增加外延工艺,当然工艺步 骤要增加不少。

一、双极集成电路工艺的基本流程

PN结隔离双极IC工艺基本流程

衬底材料(P型硅)- 埋层氧化-埋层光刻 -埋层掺杂(Sb)外延 (N型硅)隔离氧化-隔离光刻 -隔离掺杂(B)- 基区氧化-基区光刻 -基区掺杂(B)和发射区氧化-

一、双极集成电路工艺的基本流程

工艺类型简介

按照制造器件的结构不同可以分为: 双极型:由电子和空穴这两种极性的载流子作为在有源

区中运载电流的工具。 MOS型:PMOS工艺、NMOS工艺、CMOS工艺 BiCMOS集成电路:双极与MOS混合集成电路

按照MOS的栅电极的不同可以分为: 铝栅工艺、硅栅工艺(CMOS制造中的主流工艺)

(2) 光刻2:场氧光刻,又称为有源区光刻。将以后作为有源区区域的 氧(3化) 氧层化和氮层化生硅长层。保在留没,有其氮余化区硅域层的保氧护化的层区和氮化硅全部去除。 域(即场区)生长一层较厚的氧化层。图中 表面没有氧化层的区域即为有源区。

三、CMOS集成电路工艺流程

3. 生长栅氧化层和生成多晶硅栅电极 确定了有源区以后,就可以制作MOS晶体管。首先按下述步骤生长栅 氧化层和制作栅电极。 (1) 生长栅氧化层。去除掉有源区上的氮化硅层及薄氧化层以后,生长 一层作为栅氧化层的高质量薄氧化层。 (2) 在栅氧化层上再淀积一层作为栅电极材料的多晶硅。 (3) 光刻3:光刻多晶硅,只保留作栅电极以及起互连作用的多晶硅。 光刻后的剖面图如图所示。

全定制版图设计

掩膜图

掩膜上的图形决定着芯片上器件或连接物 理层的尺寸。因此版图上的几何图形尺寸与 芯片上物理层的尺寸直接相关。

二.设计规则

设计规则是如何向电路设计及版图设计 工程师精确说明工艺线的加工能力,就是 设计规则描述的内容。包括几何设计规则、 电学设计规则、布线规则。 不同的工艺,就有不同的设计规则。

新建一个库文件

库名定义为mydesign,然后连接到0.18的库中

新建一个cell,用来制作反相器

利用Add-instance添加元件,添加一个pmos

修改长度为350nm,宽为1um

同样生成一个nmos,长350nm,宽500nm

生成以后进行连线,添加IO口之后得到如下图

进入XL进行编辑

在virtuoso中使用gen from source命令生成器件, IO口修改为第一层金属,然后apply

点OK之后出现下图

进行display设置

修改display levels 和 单元间距

OK

然后就可以对器件进行 放置,连线等

设置一个命令,此后每当你选择一个命令之后都会弹出 一个菜单,根据需要可以修改相应的参数。

编 号 2.1 描 述 尺寸 3.5 目的与作用 保证器件尺寸, 减少窄沟道效应 减少寄生效应 P+、N+有 源区宽度 P+、N+有 源区间距

2.2

3.5

Poly层的设计规则

编号 3.1 3.2 3.3 3.4 3.5 描 述 尺 寸 目的与作用 多晶硅最小宽 度 多晶硅间距 与有源区最小 外间距 多晶硅伸出有 源区 与有源区最小 内间距 3.0 2.0 1.0 1.5 3.0 保证多晶硅线的必要电导 防止多晶硅联条 保证沟道区尺寸 保证栅长及源、漏区的截 断 保证电流在整个栅宽范围 内均匀流动

第二讲 版图设计基础xin

要了解采用的管壳和压焊工艺。封装形式 可分为金属圆筒塑(TO-5型)、扁平封装型和双 列直插型(DIP)等多种,管芯压点分布必须和管 壳外引脚排列相吻合。当采用热压焊时,压焊 点的面积只需70μm×70μm,超声压焊需 100μm×100μm ~125μm×25μm,金丝球焊 需125μm ×125μm,金丝球焊牢固程度高, 金丝在靠近硅片压点处是垂直的,可压到芯片 纵深处(但必须使用温度SiO2纯化层),使用起 来很灵活。

36

图1.10

37

CMOS IC 版图设计技巧

1、布局要合理 (1)引出端分布是否便于使用或与其他相关电路兼 容,是否符合管壳引出线排列要求。 (2)特殊要求的单元是否安排合理,如p阱与p管漏 源p+区离远一些,使pnp,抑制Latch-up,尤其是输 出级更应注意。 (3)布局是否紧凑,以节约芯片面积,一般尽可能 将各单元设计成方形。 (4)考虑到热场对器件工作的影响,应注意电路温 度分布是否合理。

41

(2)尽量不要使多晶硅位于p+区域上 多晶硅大多用n+掺杂,以获得较低的电阻率 。若多晶硅位于p+区域,在进行p+掺杂时多晶 硅已存在,同时对其也进行了掺杂——导致杂 质补偿,使多晶硅。 (3)金属间距应留得较大一些(3或4) 因为,金属对光得反射能力强,使得光刻 时难以精确分辨金属边缘。应适当留以裕量。

m1

55

须解释的问题:

1. 有源区和场区是互补的,晶体管做在有源区处, 金属和多晶连线多做在场区上。 2. 有源区和P+,N+注入区的关系:有源区即无场氧 化层,在这区域中可做N型和P型各种晶体管,此 区一次形成。 3. 至于以后何处是NMOS晶体管,何处是PMOS晶 体管,要由P+注入区和N+注入区那次光刻决定。 4. 有源区的图形(与多晶硅交叠处除外)和P+注 入区交集处即形成P+有源区, P+注入区比所交有 源区要大些。

集成电路课程设计--cmos反相器的电路设计及版图设计

目录摘要 (3)绪论 (5)1软件介绍及电路原理 (6)1.1软件介绍 (6)1.2电路原理 (6)2原理图绘制 (8)3电路仿真 (10)3.1瞬态仿真 (10)3.2直流仿真 (11)4版图设计及验证 (12)4.1绘制反相器版图的前期设置 (12)4.2绘制反相器版图 (13)4.3 DRC验证 (15)结束语 (17)参考文献 (18)摘要CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。

关键词:CMOS反相器ORCAD L-EDIT版图设计AbstractThe huge development potential of CMOS technology itself is the foundation of sustainable development of IC high speed. The manufacturing level of development of the integrated circuit to the deep sub micron technology, CMOS low power consumption, high speed and high integration have been fully reflected. In this paper, the circuit simulation and layout design of ORCAD and L-EDIT CMOS inverter based on simple introduction, through the circuit design and layout design process of CMOS inverter, we will understand and a basic method and operation process, familiar with IC CAD.Keywords: CMOS inverter layout ORCAD L-EDIT绪论20世纪是IC迅速发展的时代。

《基于Tanner的集成电路版图设计技术》课件第一章 集成电路设计前沿技术

1.2集成电路设计行业概况

1.2.3 我国集成电路设计行业发展情况

我国集成电路设计行业的起步较晚,但是发展速度很快,过去10年 的年复合增长率达到了29%。2004~2014年中国集成电路设计企业销售额 及增速,如图1.2所示。

1.2集成电路设计行业概况

1.2.1 集成电路设计行业概况

集成电路设计行业是集成电路行业的子行业,集成电路行业包括集 成电路设计业、集成电路制造业、集成电路封装业、集成电路测试业、 集成电路加工设备制造业、集成电路材料业等子行业。集成电路设计行 业处于产业链的上游,主要根据终端市场的需求设计开发各类芯片产品, 兼具技术密集型和资金密集型等特征,对企业的研发水平、技术积累、 研发投入、资金实力及产业链整合运作能力等均有较高的要求。

1.2集成电路设计行业概况

1.2.3 我国集成电路设计行业发展情况

2015年排名 1 2 3 4 5 6 7 8 9 10

厂商 Qualcomm OSR Avago/Broadcom

MTK Nvidia AMD Hisilicon(海思) Apple/TSMC Marvell Xilinx Spreadtrum(紫光展讯) 合计

1.2集成电路设计行业概况

1.2.2 集成电路设计行业的市场分类

集成电路按照应用领域大致分为标准通用集成电路和专用集成电路。 其中标准集成电路是指应用领域比较广泛、标准型的通用电路,如存储 器(DRAM)、微处理器(MPU)及微控制器(MCU)等;专用集成电 路是指某一领域会某一专门用途而设计的电路,系统集成电路(SoC) 属于专用集成电路。

版图设计

2.λ准则:用单一参数λ表示版图规则, 所有的几何尺寸都与λ成线性比例。

2. 设计规则

设计规则分类

最小宽度

最小间距 拓扑设计规则(绝对值)

最短露头

离周边最短距离

λ设计规则(相对值)

最小宽度w=mλ 最小间距s=nλ 最短露头t=lλ 离周边最短距离d=hλ

2. 设计规则 违背设计规则带来的误差(3)

符合设计规则

不符合设计规则 有源区接触不良

2. 设计规则 违背设计规则带来的误差(4)

接触孔下不得有多晶或有源区边缘

3. 基本工艺层版图

N阱

3. 基本工艺层版图

有源区

用于制作nFET和pFET 有源区(Active) 被场氧(FOX)所隔开

3. 基本工艺层版图

尺寸确定:确定晶体管尺寸(W、L)、互连尺 寸(连线宽度)以及晶体管与互连之间的相对 尺寸等

1. 版图设计入门 版图设计的目标

设计目标:

满足电路功能、性能指标、质量要求 尽可能节省面积,以提高集成度,降低成本 尽可能缩短连线,以减少复杂度,缩短延时、

改善可靠性

1. 版图设计入门 EDA工具的作用

有源区上多晶硅层(晶体管的栅极)的宽度通常取最 小宽度。

2. 设计规则

CMOS反相器版图设计

确定晶体管最小尺寸的设计规则

2. 设计规则

CMOS反相器版图设计

P型MOS管必须放在n阱区。

PMOS的有源区、n阱和n+区的最小重叠区决定 n阱的最小尺寸。

n+有源区同n阱间的最小间距决定了nMOS管和 pMOS管间的距离。

掩膜版图的最后一步是在金属中形成输出节点 VDD和GND接触孔间的局部互连。

《集成电路版图设计》(第二章)PPT课件

方式二:选择Attach

基于Cadence系统的 全定制版图设计基础

基于Cadence系统的 全定制版图设计基础

三、显示文件准备

LSW窗口:

✓ nwell是N 阱,PMOS管做在N阱中; ✓ ndiff是N型扩散区,也叫N型有源区(active),用来做NMOS管; ✓ pdiff是P型扩散区,也叫P型有源区,用来做PMOS管; ✓ nimp是N型扩散区注入层; ✓ pimp是P型扩散区注入层; ✓ poly是多晶层,主要用来做管子的栅极; ✓ cont是接触孔contact; ✓ metal1是一铝层; ✓ via1是一铝层和二铝层之间的连接孔,称为通孔; ✓ metal2是二铝层; ✓ pad是压焊点所在的层; ✓ 其它还包括一些特殊器件上的标识层等等

3、单元的宽长比设 置原则——最常见 宽长比的设置

逻辑图中每一 个管子宽长比 的设置

基于Cadence系统的 全定制版图设计基础

3、单元的宽长 比设置原则— —最常见宽长 比的设置(续)

单元符号的建立和 Label的设置

基于Cadence系统的 全定制版图设计基础

3、单元的宽长比 设置原则——其它 宽长比的设置

基于Cadence系统的 全定制版图设计基础

第一部分、D508项目逻辑图的准备

一、逻辑图输入工具启动

二、一个传输门逻辑图及符 号的输入流程

三、D508项目单元逻辑图的准备 四、D508项目总体逻辑图的准备

第二部分、D508项目版图输入准备

一、设计规则准备 二、工艺文件准备 三、显示文件准备

第三部分、版图设计步骤及操作

三、显示文件准备(续)

基于Cadence系统的 全定制版图设计基础

Display Resource Editor 窗口:

版图设计

集成电路版图设计什么是集成电路版图设计?所谓的集成电路版图设计是根据逻辑与电路功能和性能要求以及工业水平要求来设计芯片制造时光刻用的掩模版图,实现IC设计的最终输出其中版图是一组相互套合的图形,各层版图表示不同的工艺步骤,每层版图用不同的图案表示。

DRS和LVS开始前需要做哪些准备?DRC开始前需要准备好版图文件和DRC规则文件,LVS开始前需要准备好版图文件、电路图文件和runset文件为什么需要进行版图数据处理?在形成整体的版图并通过DRC、LVS的验证后,版图设计过程就完成了,但这个时候的版图GDS数据还不能拿去制作掩模版,还需要对GDS数据进行处理。

该版图GDS数据中的层次跟最终模板的层次并不是完全一致的,该版图GDS 数据还需要进行工艺涨缩处理,以满足掩模版制作需求。

集成电路设计流程:功能要求、电路设计、电路仿真、版图设计、版图验证、后仿及优化。

光刻工艺流程:底膜处理、涂胶、前烘、曝光、显影、坚膜、显影检测、刻蚀、去胶、最终检验。

工艺要求:特征尺寸、集成度、晶圆尺寸工艺文件夹包含:技术文件、显示文件DRC步骤:建立DRC运行目录、修改规则文件、导出gds2文件、编译规则文件、执行DRC检查、DRC结构分析狗骨电阻的优点:能够控制电流走向,使电阻误差减小。

集成电路发展的趋势是什么?制程工艺越来越精细、集成度越来越高、电路功能越来越强大、越来越趋向于智能化集成电路中的电阻分为哪几种?有扩散电阻、多晶硅电阻、阱电阻简述为什么尽可能多地设计阱接触?能大大减小寄生电阻的阻值,有效抑制闩锁。

在绘制PMOS版图时,为什么在接触区域进行SN注入?SN注入降低了接触电阻,接触孔容易刻蚀,形成欧姆接触。

简述什么是闩锁效应?闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。

什么是保护环,保护环的主要作用?能抑制闩锁效应的设计方式就是保护环作用: 1.阻碍少子保护环 2.载流子注入类型为少子 3.保护类型为少子 4.电位保持PN结反偏 5.起分流作用。

ASIC的版图设计方法

❖ 简单、规模较小而又有一定批量的专用电路

在设计者力所能及的情况下做到最优 ( 时间与正确性把

2020/6/2握4 的折中)

浙大微电子

3/52

最基本的CMOS IC制作工艺流程

1、P阱 (或N阱)

2、有源区 (制作MOS晶体管的区域)

3、N-场注入 ( 调整P型MOS管场区的杂质浓度,减小寄生效应 )

7/52

多晶硅栅(GT) ZDLX-1H

2020/6/24

浙大微电子

8/52

P+源漏区(SP) ZDLX-1H

2020/6/24

浙大微电子

9/52

N+源漏区(SN) ZDLX-1H

取P+源漏区的反版

2020/6/24

浙大微电子

10/52

金属1(A1) ZDLX-1H

2020/6/24

浙大微电子

❖ 先将IC设计中可能会遇到的所有基本逻辑单元(包括 I/O单元)的版图用全定制的方法设计好后存入库中

按照最佳设计原则(速度、面积)

遵照一定的外形尺寸约束

❖ 实际设计ASIC时

从单元库中调出所要的单元版图

按照一定的拼接规则拼接

留出平行且宽度可调的布线通道(水平与垂直走线分层)

2020/6/24

硕士生梁筱、杨伟伟(2009.9-2012.3)

2020/6/24

浙大微电子

36/52

MPW Multi-Purpose Wafer

2020/6/24

浙大微电子

37/52

二、半定制设计方法(标准单元法)

Semi-Custom Design Approach

❖ 标准单元法也叫库单元法,用在数字IC设计中。

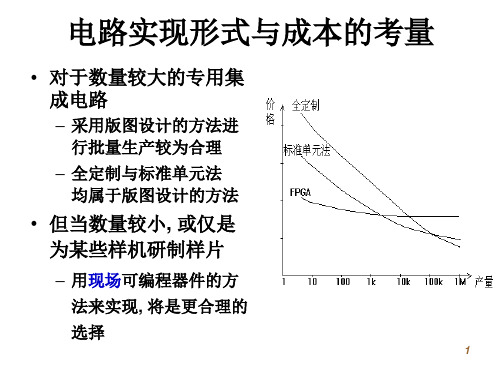

讲ASIC的可编程器件实现方法

– 组合逻辑输出 – 时序逻辑输出 – 三态输出 – 双向输入/输出

18

可编程器件与现场可编程器件

• 可编程器件家族

– 可编程只读存储器ROM系列 – 可编程逻辑器件PLD系列 – 规模和功能都上了一个档次的CPLD系列 – 现场可编程门阵列FPGA系列

20

FPGA与CPLD的区别

程序存储 资源类型 集成度 使用场合 速度 其他资源 保密性

CPLD 不需要 组合电路资源丰富

低 完成控制逻辑

慢 - 可加密

FPGA SRAM,外挂EEPROM

触发器资源丰富 高

完成比较复杂的算法 快

锁相环 一般不能加密

21

可编程器件与现场可编程器件

• 可编程器件家族

–输入 –输出 –双向 –三态

26

其它辅助元器件和连线

• PIPs -- Programmble Interconnect Points 可编程的内连点

• BIBs -- Bidirectional Interconnect Buffers 双向内连缓冲器

• VLL -- Vertical Long Line 垂直长线, 在垂直方向起快速通道作用

2. 反熔丝(Anti-Fuse)技术

也称熔通技术,这类器件是用逆熔丝作为开关 元件。这些开关元件在未编程时处于开路状态, 编程时,在需要连接处的开关元件两端加上编 程电压将其融通(前页右)。

7

EPROM (可擦除式现场编程)

采用可逆工作机理的“浮栅”雪崩注入MOS电

路

写入1:

衬底接地,D端加高压,雪崩击 穿,隧道效应,浮栅积累正电荷, 形成反型层沟道

《集成电路版图设计》课件(第二章)

基于Cadence系统的 全定制版图设计基础

方式二:选择Attach

基于Cadence系统的 全定制版图设计基础

基于Cadence系统的 全定制版图设计基础

三、显示文件准备

LSW窗口:

nwell是N 阱,PMOS管做在N阱中; ndiff是N型扩散区,也叫N型有源区(active),用来做NMOS管; pdiff是P型扩散区,也叫P型有源区,用来做PMOS管; nimp是N型扩散区注入层; pimp是P型扩散区注入层; poly是多晶层,主要用来做管子的栅极; cont是接触孔contact; metal1是一铝层; via1是一铝层和二铝层之间的连接孔,称为通孔; metal2是二铝层; pad是压焊点所在的层; 其它还包括一些特殊器件上的标识层等等

基于Cadence系统的 全定制版图设计基础

数字部分

四、D508项目总体逻辑图

基于Cadence系统的 全定制版图设计基础

模拟部分

基于Cadence系统的 全定制版图设计基础

第二部分、D508项目版图输入准备

一、设计规则准备

4)逻辑图输入完成后的检查

基于Cadence系统的 全定制版图设计基础

从Design菜单当中选择Check and Save, 会显示错误(errors)或者警告(warnings) 的数量。若有错误或者警告,则会在逻辑 图上相应的地方显示一个黄色的叉号,并 且高亮(HighLight)显示。

基于Cadence系统的 全定制版图设计基础

3、单元的宽长比 设置原则——其它 宽长比的设置

基于Cadence系统的 全定制版图设计基础

1位全加器的电路和版图设计解析

集成电路设计基础论文题目:CMOS全加器设计学院:信息科学与工程学院专业:集成电路工程姓名:耿烨亮学号:1311082135CMOS全加器设计摘要:现代社会随着电路的集成度越来越高,功耗和信号延迟成为超大规模集成电路的关键。

加法运算是数字系统中最基本的运算,为了更好地利用加法器实现减法、乘法、除法等运算,需要对全加器进行功能仿真设计和分析。

另外通过全加器可以对其它相关电路有所了解。

因此只有深刻理解了全加器的性能才能进一步减小功耗和信号延迟[1]。

本文用对一位全加器进行了全面的分析。

并且通过使用Cadence公司的工具IC 5141与Hspice来实现全定制的整个设计流程。

关键词:全加器;全定制;CadenceAs the circuit’s integration is increasing in the modern society,Power consumption and signal delay is crucial to the design of high-performance very large scale integration circuits. Addition operation is the basic operation of the digital system, In order to achieve much better use of the adder subtraction, multiplication, division and other operations, The need for full adder functional simulation design and analysis is necessary .what’s more, we can understand the other related circuitry through the full adder , Therefore, only a deep understanding of the performance of the full adder can we reduce the power consumption and signal delay.The paper has a comprehensive analysis to the full adder. And through the use of Cadence tool IC 5141 and Hspice to achieve full custom throughout the design process.Key words: the full adder ; Full – Custom; Cadence集成电路设计方法大致可分为定制(Custom)、半定制(Semi-custom)、可编程逻辑器件(PLD)等设计方法,如图1.1所示。

版图设计中的设计规则

VDD

OUT

5.1

《集成电路设计基础》

28

电学设计规则

•

电学设计规则给出的是将具体的 工艺参数及其结果抽象出的电学 参数,是电路与系统设计、模拟 的依据。

《集成电路设计基础》

29

电学设计规则描述

《集成电路设计基础》

30

电学设计规则描述

《集成电路设计基础》

31

电学设计规则

与上述的几何设计规则一样,对于不同 的工艺线和工艺流程,数据的多少将有 所不同,对于不同的要求,数据的多少 也会有所差别。

《集成电路设计基础》 9

1. 设计规则或规整格式设计规则

70年代末,Meed和Conway倡导以无量纲的“” 为单位表示所有的几何尺寸限制,把大多数尺寸(覆 盖,出头等等)约定为的倍数。通常取栅长度L的 一半,又称等比例设计规则。由于其规则简单,主要 适合于芯片设计新手使用,或不要求芯片面积最小, 电路特性最佳的应用场合。在这类规则中,把绝大多 数尺寸规定为某一特征尺寸“”的某个倍数。与工 艺线所具有的工艺分辨率有关,线宽偏离理想特征尺 寸的上限以及掩膜版之间的最大套准偏差。 优点:版图设计独立于工艺和实际尺寸。

标示图

Locos

N+或P+有源区层

Poly

多晶硅层

Contact

接触孔层

Metal

金属层

Pad

焊盘钝化层 《集成电路设计基础》 13

版图几何设计规则

NWELL层相关的设计规则

编 号 描 述 尺 寸 目的与作用

1.1

N阱最小宽度

10.0

保证光刻精度和器件尺寸

1.2

N阱最小间距

10.0

防止不同电位阱间干扰

版图设计培训资料(1)

第一部分:了解版图

3. 版图的工具:

– Cadence

✓ Virtuoso ✓ Dracula ✓ Assura ✓ Diva

– Mentor

✓ calibre

– Spring soft

✓ laker

版图设计培训资料(1)

第一部分:了解版图

4. 版图的设计流熟程悉所需文件

对电路的了解 版图布局布线

NMOS版图

版图设计培训资料(1)

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管 1) NMOS管

✓ 以TSMC,CMOS,N单阱工艺 为例

✓ PMOS管,做在N阱中,沟道 为N型,源漏为P型

2) 包括层次:

✓ NWELL,N阱 ✓ PIMP,P+注入 ✓ DIFF,有源区 ✓ Poly,栅 ✓ M1,金属 ✓ CONT,过孔

第二部分:版图设计基础

2.1器件

2.1.2 电阻 选择合适的类型,由电阻阻值、方块电阻值,

确定 W、L;R=L/W*R0

电阻类型

版图设计培训资料(1)

电阻版图

第二部分:版图设计基础

2.1器件

2.1.3 电容

1) 电容值计算C=L*W*C0

2) 电容分类:

✓ poly电容 ✓ MIM电容

• 基于单位面积电容值 ✓ MOS电容

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

版图设计培训资料(1)

第一部分:了解版图

1. 版图的定义:版图是在掩膜制造产品上实现 电路功能且满足电路功耗、性能等,从版图上 减少工艺制造对电路的偏差,提高芯片的精准 性。

电路图

版图设计知识点

版图设计知识点版图设计是指在平面设计中对于页面布局、元素排列以及配色等方面的设计。

在版图设计中,有许多重要的知识点需要注意和掌握。

本文将就版图设计的知识点进行详细论述。

一、页面尺寸与比例在版图设计中,页面尺寸与比例是首要考虑的因素之一。

根据设计需求和输出媒介的不同,选择适合的页面尺寸是非常重要的。

常见的页面尺寸包括A4、A5、网页尺寸等。

除了尺寸外,比例也需要考虑。

常见的比例有黄金比例、对称比例等,选择合适的比例可以使得版面更加平衡美观。

二、栏目设置与结构栏目设置是版图设计中的重要环节。

通过合理设置栏目,可以使得信息的展示更加清晰、有序。

在进行栏目设置时,需要考虑到内容的重要性、相似性以及层次关系。

常用的栏目设置有单栏、双栏、多栏等,根据设计需求选择合适的栏目布局。

三、文字排版文字排版是版图设计中不可忽略的一环。

合理的文字排版可以提升版面的可读性和美观度。

在进行文字排版时,需要注意字体的选择与搭配、字号的调整以及字距的设置等。

同时,还需要注意段落的分隔与缩进、文字的对齐方式等,确保文字排版整齐、清晰。

四、色彩运用色彩是版图设计中的重要元素之一,能够给人带来不同的情绪和感受。

在进行色彩运用时,需要考虑到色彩的搭配、主次关系以及色彩的饱和度和明度等因素。

同时,还需要注意色彩的运用要与设计主题相符合,避免色彩过于花哨或不协调而影响整体设计效果。

五、图片与图形元素图片与图形元素在版图设计中起到了画龙点睛的作用。

通过巧妙的图片与图形元素的运用,可以提升版面的视觉效果和吸引力。

在选择图片与图形元素时,需要注意其与设计主题的契合度,避免过多或不相关的图片与图形元素的使用。

同时,还需要注意图片的清晰度以及图形元素的简洁性和美观性。

六、空白与留白空白与留白是版图设计中的重要设计元素之一。

合理的运用空白与留白可以使版面更加清爽、简洁。

空白的选择需要考虑到信息的紧凑性与层次关系,留白的运用则需要考虑到版面的平衡性与美感。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用于:

设计规则检查(DRC) 版图电路图对照(LVS) 及寄生参数抽取(PEX)

2020/9/30

3

Ningbo University

Installation of Calibre

• 准备安装文件: E038_MenCAlibre2006.tar

1、解压tar文件 [username@hostname ~/mentor]$ tar xf E038_MenCAlibre2006.tar

2020/9/30

2

Ningbo University

Introduction of Calibre

• What is Calibre

•Calibre xRC •Calibre xL •Calibre RVE •Calibre Interactive

A Product from Mentor Graphics

2020/9/30

12

Ningbo University

Begin to Schematic

❖启动 Cadence环境

•假设在ncsu目录下设计

•打开终端

[usrername@hostname ~/]$ mkdir ncsu [usrername@hostname ~/]$ cd ncsu [usrername@hostname ~/ncsu]$ ln -s [ncsu-cdk-1.5.1]/cdssetup/cdsenv .cdsenv [usrername@hostname ~/ncsu]$ ln -s [ncsu-cdk-1.5.1]/cdssetup/cdsinit .cdsinit [usrername@hostname ~/ncsu]$ cp [ncsu-cdk-1.5.1]/cdssetup/cds.lib . [usrername@hostname ~/ncsu]$ icfb&

6 显示文件(display.drf),一般位于pdk安装 目录或工作目录下

2020/9/30

8

Ningbo University

Before layout

❖ 1 系统启动 命令 icde icds icms icca

规模 s s m xl

2020/9/30

9

功能

基本数字模拟设 计输入 icde 加数字设计 环境 前端模拟、混合、 微波设计 前端设计加布局 规划

设置License文件:

setenv LM_LICENSE_FILE “/home/USERNAME/mentor/L2006.1_25/LICENSE_FILE” 在CIW中输入, 或在.cdsinit中加入

load("/home/username/mentor/L2006.1_25/pkgs/icv.ixl/lib/calibre.skl")

3、单独使用GUI

[username@hostname ~/mentor]$ calibre -gui&

2020/9/30

4

Ningbo University

Installation of Calibre

❖Cadence Virtuoso中载入Calibre

2020/9/30 或在该文件中加入行

5

❖ 3 系统级启动命令

命令

规模

swb

s

msfb

l

icfb

xl

2020/9பைடு நூலகம்30

11

功能

Pcb 设计

混合型号IC设 计 前端到后端大 多数工具

Ningbo University

Begin to layout

❖目标 理解 Layout Editor 环境

学会如何使用 Layout Editor 学会运行交互 DRC&LVS 学会定制版图编辑环境

Chap.13 全定制版图设计基础 (2)

Outline

• Calibre介绍与安装 • 绘制5级反相器电路图 (schematic) • 绘制5级反相器电路图 (layout) • 用DIVA对layout进行DRC • 对layout进行抽出 (extract) • 电路与版图对照 (LVS)

作库的指针

2020/9/30

6

Ningbo University

Before layout

❖ 环境设置 1 .cshrc 文件设置

.cshrc文件中指定 Cadence 软件和 licence 文件所在的路径 一般存在于/home/USERNAME/下。 2 .cdsenv 文件设置

.cdsenv 文件包含了 Cadence 软件的一些初始设置,该文件用 SKILL 语言写,Cadence 可直接执行

2020/9/30

7

Ningbo University

Before layout

5 工艺文件(technology file)

技术文件包含了设计必需的很多信息,对设计,尤 其是版图设计很重要。它包含层的定义,符号化器 件定义,几何、物理、电学设计规则,以及一些针 对特定 Cadence 工具的规则定义,如自动布局布线 的规则,版图转换成 GDSII 时所使用层号的定义。 存在于pdk安装目录

可存在于ic5141平台安装目录,用户目录,工作目录下,优先 载入工作目录,用户目录,再IC5141安装目录 3 .cdsinit 文件设置

可存在于ic5141平台安装目录,用户目录,工作目录下,优先 载入工作目录,用户目录,及IC5141安装目录 4 cds.lib 文件设置

可存在于ic5141平台安装目录,用户目录,工作目录下,优先 载入工作目录,用户目录,及IC5141安装目录

Ningbo University

Before layout

❖ 2 版图工具启动

命令

规模

功能

layout

s

layoutPlus m

2020/9/30

10

基本版图设计 (具有交互 DRC 功能)

基本版图设计 (具有自动化设 计工具和交互验 证工具)

Ningbo University

Before layout

2、设置环境变量及License文件*

设置环境变量: # mentor calbre 2006.1

在.cshrc文件中加入以下设置

setenv MGC_HOME "/home/hjp/mentor/L2006.1_25"

setenv PATH "$MGC_HOME/bin:$MGC_HOME/lib:${PATH}:"

Ningbo University

Before layout

❖Terms and Definitions

库(library):特定工艺相关的单元集合 单元(cell):构成系统或芯片模块的设计对象 视图(view):单元的一种预定义类型的表示 CIW:命令解释窗口 属性(attributes):预定义的名称-值对的集合 搜索路径(search path):指向当前工作目录和工