哈工大CPU设计报告

哈工大《操作系统》实验3

向kernel/printk.c中添加日志打印功能,将以下代码添加到原文件中:

在kernel/fork.c、kernel/sched.c和kernel/exit.c中,找到正确的状态转换点,并添加合适的状态信息,把它输出到log文件之中。

fork.c的修改如下:

exit.c的修改如下:

sched.c的修改如下:

在虚拟机上运行ls -l /var”或“ll /var”查看process.log是否建立,及它的属性和长度;

修改时间片

include/linux/sched.h宏INIT_TASK中定义的:

0,15,15, 分别对应state、counter和priority,将priority值修改,即可实现对时间片大小的调整。

0,15,15, 分别对应state、counter和priority,

priority值修改,即可实现对时间片大小的调整。

在修改时间片将priority由15改为150后,Process 9~20 中Turnaround, Waiting, CPU Burst, I/O Burst变化不大,原因可能是程序中I/O操作占用的时间对于总时间影响的权重过大,导致处理时间体现的并不明显。

或者变化不大的原因是,子进程连续占用cpu的时间要比时间片大很多。

哈工大数字逻辑电路与系统实验报告

哈工大数字逻辑电路与系统实验报告引言本实验旨在通过对数字逻辑电路与系统的学习与实践,加深对数字逻辑电路原理和应用的理解,掌握数字逻辑电路实验的设计与调试方法。

本报告将详细介绍实验步骤、实验结果以及实验心得体会。

实验目的1.掌握基本的数字逻辑电路设计方法;2.熟悉数字逻辑电路的布线和调试方法;3.学会使用EDA软件进行数字逻辑电路的仿真和验证。

实验器材•FPGA开发板•EDA软件实验过程实验一:逻辑门的基本控制本实验采用FPGA开发板进行实验,以下是逻辑门的基本控制步骤:1.打开EDA软件,新建工程;2.选择FPGA开发板型号,并进行相应配置;3.在原理图设计界面上,依次放置与门、或门、非门和异或门,并连接输入输出引脚;4.面向测试向量实现逻辑门的控制和数据输入;5.运行仿真并进行调试。

实验二:数字逻辑电路实现本实验以4位全加器为例,进行数字逻辑电路的实现,以下是实验步骤:1.打开EDA软件,新建工程;2.选择FPGA开发板型号,并进行相应配置;3.在原理图设计界面上,放置输入引脚、逻辑门和输出引脚,并进行连接;4.根据全加器的真值表,设置输入信号,实现加法运算;5.运行仿真并进行调试。

实验三:数字逻辑电路的串联与并联本实验旨在通过对数字逻辑电路的串联与并联实现,加深对逻辑门的理解与应用。

以下是实验步骤:1.打开EDA软件,新建工程;2.选择FPGA开发板型号,并进行相应配置;3.在原理图设计界面上,放置多个逻辑门,并设置输入输出引脚;4.进行逻辑门的串联与并联连接;5.根据逻辑门的真值表,设置输入信号,进行运算;6.运行仿真并进行调试。

实验结果经过实验测试,实验结果如下:1.实验一:逻辑门的基本控制–与门的功能得到实现;–或门的功能得到实现;–非门的功能得到实现;–异或门的功能得到实现。

2.实验二:数字逻辑电路实现–4位全加器的功能得到实现;–正确进行了加法运算。

3.实验三:数字逻辑电路的串联与并联–逻辑门的串联与并联功能得到实现;–通过逻辑门的串联与并联,实现了复杂的逻辑运算。

哈工大威海计算机操作系统原理实验报告2

计算机操作系统原理

实验报告

专业:1104202

学号:110420212

姓名:李敖

哈尔滨工业大学(威海)

实验二进程及其资源管理

一、实验目的

1.理解资源共享与互斥特性以及操作系统管理资源的基本方法。

2.学会使用高级语言进行多线程编程的方法。

3.掌握利用VC++或Java线程库实现一个管理器,用来实现操作系统对进程及其资源的管理功能。

4.通过该实验,学生可在源代码级完成进程及其资源管理方案的分析、功能设计、编程实现,控制进程间的同步、互斥关系。

二、实验要求

1.知识基础:学生应在完成对进程和线程、调度、死锁等章节的学习后进行。

2.开发环境与工具:

硬件平台——个人计算机。

软件平台——Windows操作系统,根据需要,任选安装VC++语言、java 语言或C语言开发环境。

三、实验内容

1.开发一个函数,建立进程控制块和资源控制块结构,并实现相关数据结构的初始化。

2.开发一系列操作,由进程调用这些操作,达到控制进程申请或释放各种资源的目的。

四、程序流程图

1.进程初始化

2.优先级策略调度

五、实验结果

创建进程1

创建进程2

查看正在运行的进程

替换进程

删除进程

进程调度进程1

进程2

进程3

FCFS

HPF

六、结果分析

有上述程序运行结果可知,此次试验已经基本达到了实验要求,能够实现进程的创建、查看、替换、删除操作以及进程的调度。

不过,在进程的创建中,要求每个资源要用到3个资源,对于再多的资源就无法保证了。

操作系统实验报告哈工大

计算机操作系统课程实验报告专业信息管理与信息系统班级 1203601学号 120360117姓名乐云指导教师周学权计算机操作系统课程实验报告专业信息管理与信息系统班级 1203601学号 120360114姓名郭鑫指导教师周学权操作系统实验实验1 使用虚拟机安装系统 4学时【实验目的】1.了解虚拟机软件的使用。

2.了解使用虚拟机安装Windows及Ubuntu操作系统。

【实验内容】1. 安装虚拟机软件VirtualBox。

2. 配置VirtualBox环境安装WindowsXP,并在虚拟机中启动windowsXP。

3. 配置VirtualBox环境安装Ubuntu 10.10,并在虚拟机中启动Ubuntu。

【实验环境】VirtualBox4.0Windows XPUbuntu 8.04【实验过程】一、创建虚拟机首先运行VirtualBox,单击左上角的“新建”。

单击下一步。

出现如下图的界面,在名称后输入自己起的名字,如test选择自己想要安装的系统类型和版本,本次试验是安装windows xp系统设置完成后,单击下一步。

接下来是设置虚拟机的内存大小,本次实验操作的计算机内存为4GB,所以我选择分配给我的虚拟机的内存为512MB,然后单击下一步。

接着创建虚拟硬盘,选择创建新的虚拟硬盘,单击下一步。

选择虚拟硬盘的类型,默认选择了VDI类型,单击下一步。

接下来选择为动态扩展类型,因为计算机的存储空间不大。

单击下一步。

动态扩展:如果你为你的虚拟磁盘分配的是10G空间,虚拟磁盘占用真实磁盘空间的范围就为0~10G。

固定大小:如果你为你的虚拟磁盘分配的是10G空间,虚拟磁盘占用真实磁盘空间永远不是10G,不管虚拟磁盘空间是否被全部使用。

选择虚拟机在本地磁盘中的位置和大小,单击下一步。

确认虚拟机的详细情况,点击下一步。

这时我们已经成功的创建了一个虚拟机了,接下来我们要开始配置这个虚拟机安装操作系统选择刚才创建的虚拟机,然后单击上方的“开始”弹出了首次运行向导,单击下一步。

哈工大数电自主实验-数字流水灯

Harbin Institute of Technology数字电路自主设计实验院系:航天学院班级:姓名:学号:指导教师:哈尔滨工业大学一、实验目的1.进一步掌握数字电路课程所学的理论知识。

2.熟悉几种常用集成数字芯片的功能和应用,并掌握其工作原理,进一步学会使用其进行电路设计。

3.了解数字系统设计的基本思想和方法,学会科学分析和解决问题。

4.培养认真严谨的工作作风和实事求是的工作态度。

5.数电课程实验为我们提供了动手实践的机会,增强动手实践的能力。

二、实验要求设计流水灯,即一排灯按一定的顺序逐次点亮,且可调频、暂停、步进。

三、实验步骤1.设计电路实现题目要求,电路在功能相当的情况下设计越简单越好;2. 画出电路原理图(或仿真电路图);3.元器件及参数选择;4.电路仿真与调试;5.到实验时进行电路的连接与功能验证,注意布线,要直角连接,选最短路径,不要相互交叉,注意用电安全,所加电压不能太高,以免烧坏芯片;6.找指导教师进行实验的检查与验收;7.编写设计报告:写出设计与制作的全过程,附上有关资料和图纸,心得体会。

四、实验原理设计流水灯的方法有很多种,我的设计思路是:利用555定时器产生秒脉冲信号,74LS161组成8进制计数器,74LS138进行译码,点亮电平指示灯。

并通过调节555的电阻,实现频率可调。

通过两与非门,实现暂停、步进功能。

1.秒信号发生器(1)555定时器结构(2)555定时器引脚图(3)555定时器功能表(4)555定时器仿真图2. 74LS161实现8进制加计数74LS161是常用的四位二进制可预置的同步加法计数器,它可以灵活地运用在各种数字电路,以及单片机系统中实现分频器等很多重要的功能。

(1)74LS161同步加法器引脚图管脚图介绍:始终CP和四个数据输入端P0-P3清零CLR使能EP,ET置数PE数据输出端Q0-Q3进位输出TC(2)74LS161功能表(5)74LS161仿真图对74LS161进行八进制计数改组,需要一个与非门,即芯片74LS00,也就是将74LS161的输出端通过与非门,当输出为8时将输出为高电平的端口与非后接到74LS161的清零段。

CPU实验报告范文

CPU实验报告范文一、实验目的本次实验的目的是设计和实现一个简单的中央处理器(CPU),通过实践掌握CPU的基本工作原理和实现方法。

二、实验原理1.CPU的基本概念中央处理器(CPU)是计算机的核心部件,负责执行计算机指令和控制计算机的操作。

它由运算器、控制器和寄存器组成。

运算器负责执行算术和逻辑运算,包括加法、减法、乘法、除法等。

控制器负责指挥CPU的工作,通过控制总线实现对内存和其他外部设备的访问。

寄存器是CPU内部的存储器,用于暂时存放指令、数据和中间结果。

2.CPU的实现方法CPU的实现采用组合逻辑电路和时序逻辑电路相结合的方法。

组合逻辑电路是由逻辑门构成的电路,它的输入只依赖于当前时刻的输入信号,输出也只与当前时刻的输入信号有关。

而时序逻辑电路则包含存储元件,其输出不仅与当前时刻的输入信号有关,还与之前的输入信号有关。

CPU的实现过程主要包括以下步骤:(1)设计指令集:确定CPU支持的指令集,包括指令的格式和操作码。

(2)设计控制器:根据指令集设计控制器,确定各个指令的执行过程和控制信号。

(3)设计运算器:根据指令集设计运算器,确定支持的算术和逻辑运算。

(4)设计寄存器:确定需要的寄存器数量和位数,设计寄存器的输入输出和工作方式。

3.实验环境和工具本次实验使用的环境和工具如下:(1)硬件环境:计算机、开发板、示波器等。

(2)软件环境:Win10操作系统、Vivado开发工具等。

三、实验步骤1.设计指令集根据实验要求,我们设计了一个简单的指令集,包括加法、减法、逻辑与、逻辑或和移位指令。

每个指令有特定的操作码和操作数。

2.设计控制器根据指令集设计了一个控制器。

控制器根据指令的操作码产生相应的控制信号,控制CPU内部寄存器、运算器和总线的操作。

3.设计运算器根据指令集设计了一个运算器。

运算器包括加法器、减法器、与门和或门等。

它通过输入的操作数和控制信号完成相应的运算操作。

4.设计寄存器根据实验需求确定了所需的寄存器数量和位数。

哈尔滨工业大学(威海)操作系统实验报告及答案

哈尔滨工业大学(威海)操作系统实验报告说明:本实验报告实验答案,是本人在上实验时的测试数据,由于操作系统实验中后面实验与当时所做实验的计算机的配置有关,因此本实验报的数据仅供参考。

实验1进程的描述与控制Windows 2000编程(实验估计时间:100分钟)1.1 背景知识Windows 2000 可以识别的应用程序包括控制台应用程序、GUI应用程序和服务应用程序。

控制台应用程序可以创建GUI,GUI应用程序可以作为服务来运行,服务也可以向标准的输出流写入数据。

不同类型应用程序间的惟一重要区别是其启动方法。

Windows 2000是以NT技术构建的,它提供了创建控制台应用程序的能力,使用户可以利用标准的C++工具,如iostream库中的cout和cin对象,来创建小型应用程序。

当系统运行时,Windows 2000的服务通常要向系统用户提供所需功能。

服务应用程序类型需要ServiceMail()函数,由服务控制管理器(SCM)加以调用。

SCM是操作系统的集成部分,负责响应系统启动以开始服务、指导用户控制或从另一个服务中来的请求。

其本身负责使应用程序的行为像一个服务,通常,服务登录到特殊的LocalSystem账号下,此账号具有与开发人员创建的服务不同的权限。

当C++编译器创建可执行程序时,编译器将源代码编译成OBJ文件,然后将其与标准库相链接。

产生的EXE文件是装载器指令、机器指令和应用程序的数据的集合。

装载器指令告诉系统从哪里装载机器代码。

另一个装载器指令告诉系统从哪里开始执行进程的主线程。

在进行某些设置后,进入开发者提供的main()、Servicemain()或WinMain()函数的低级入口点。

机器代码中包括控制逻辑,它所做的事包括跳转到Windows API函数,进行计算或向磁盘写入数据等。

Windows允许开发人员将大型应用程序分为较小的、互相有关系的服务模块,即动态链接库(DLL)代码块,在其中包含应用程序所使用的机器代码和应用程序的数据。

哈工大单片机教程—chap2—MCS-51单片机的硬件结构

其字节地址的末位是0H或8H可位寻址。

下面介绍SFR块中的某些寄存器。

表2-2

SFR的名称及其分布

1.堆栈指针SP

指示堆栈顶部在内部RAM块中的位置

复位后,SP中的内容为07H。

(1)保护断点

(2)现场保护 堆栈向上生长 2. 数据指针DPTR 高位字节寄存器用DPH表示,低位字节寄存器用 DPL表示。 3. I/O端口P0~P3 P0~P3分别为I/O端口P0~P3的锁存器。

(1) P0口:双向8位三态I/O口,此口为地址总线 (低8位)及数据总线分时复用口,可驱动8个LS 型TTL负载。 (2) P1口:8位准双向I/O口,可驱动4个LS型TTL 负载。 (3) P2口:8位准双向I/O口,与地址总线(高8 位)复用,可驱动4个LS型TTL负载。

(4) P3口:8位准双向I/O口,双功能复用口,可驱 动4个LS型TTL负载。

2.4.4

位地址空间

211个(128个+83个)寻址位。位地址范围为: 00H~FFH。 内部RAM的可寻址位128个(字节地址20H~2FH)见表 2-3(P24)。

特殊功能寄存器SFR为83个可寻址位,见表2-4 (P24)。

表2-3

内部RAM的可寻址位及位地址

表2-4 SFR中的位地址分布

注意:准双向口与双向三态口的差别。 • 当3个准双向I/O口作输入口使用时,要向该口先写 “1”。

• 准双向I/O口无高阻 “浮空”状态。

2.3 MCS-51的CPU 由运算器和控制器所构成 2.3.1 运算器 对操作数进行算术、逻辑运算和位操作。

1.算术逻辑运算单元ALU

2.累加器A

使用最频繁的寄存器,可写为Acc。

P0口某一位的电路包括:

哈工大《操作系统》实验1

(5)重新编写一个setup.s,然后将其中的显示的信息改为:“Now we are in SETUP”。

再次编译,重新用make命令生成BootImage,结合提示信息和makefile文修改build.c,具体将setup.s改动如下:mov cx,#27mov bx,#0x0007 ! page 0, attribute 7 (normal)mov bp,#msg1mov ax,#0x1301 ! write string, move cursorint 0x10dieLoop:j dieLoopmsg1:.byte 13,10,13,10.ascii "Now we are in SETUP".byte 13,10,13,10将build.c改动如下:if(strcmp("none",argv[3]) == 0)//添加判断return 0;if ((id=open(argv[3],O_RDONLY,0))<0)die("Unable to open 'system'");// if (read(id,buf,GCC_HEADER) != GCC_HEADER)// die("Unable to read header of 'system'");// if (((long *) buf)[5] != 0)// die("Non-GCC header of 'system'");for (i=0 ; (c=read(id,buf,sizeof buf))>0 ; i+=c )if (write(1,buf,c)!=c)die("Write call failed");close(id);fprintf(stderr,"System is %d bytes.\n",i);if (i > SYS_SIZE*16)die("System is too big");return(0);(6)验证:用make是否能成功生成BootImage,运行run命令验证运行结果。

cpu设计实验报告

cpu设计实验报告CPU设计实验报告摘要:本实验旨在设计一个基本的中央处理器(CPU),并通过实验验证其性能和功能。

在设计过程中,我们使用了Verilog硬件描述语言和ModelSim仿真工具。

通过对CPU的设计和仿真实验,我们验证了CPU的正确性和性能,并对其进行了性能分析和优化。

1. 引言CPU是计算机系统中最核心的部件之一,它负责执行计算机指令和控制数据流动。

因此,设计一个高效、稳定的CPU对于计算机系统的性能至关重要。

本实验旨在通过Verilog硬件描述语言和ModelSim仿真工具,设计一个基本的CPU,并验证其性能和功能。

2. 设计过程我们首先对CPU的功能和性能进行了分析和规划,确定了CPU的基本架构和指令集。

然后,我们使用Verilog语言编写了CPU的硬件描述,并通过ModelSim进行了仿真验证。

在设计过程中,我们重点关注了CPU的时序逻辑、数据通路和控制逻辑,确保CPU能够正确地执行指令并保持稳定的性能。

3. 实验结果通过对CPU的设计和仿真实验,我们验证了CPU的正确性和性能。

我们使用了一系列的测试用例对CPU进行了功能和性能测试,并对其进行了性能分析和优化。

实验结果表明,我们设计的CPU能够正确地执行各种指令,并在性能上达到了预期的目标。

4. 总结和展望本实验通过Verilog硬件描述语言和ModelSim仿真工具,设计并验证了一个基本的CPU。

通过实验,我们对CPU的设计和性能有了更深入的了解,并对其进行了性能分析和优化。

未来,我们将进一步完善CPU的设计,提高其性能和功能,以满足计算机系统的需求。

综上所述,本实验为我们提供了一个宝贵的机会,通过实际设计和验证,深入了解了CPU的工作原理和性能特点,为我们今后的学习和研究打下了坚实的基础。

希望通过不懈的努力,我们能够设计出更加高效、稳定的CPU,为计算机系统的发展做出更大的贡献。

哈工大《操作系统》实验1

(5)重新编写一个setup.s,然后将其中的显示的信息改为:“Now we are in SETUP”。

再次编译,重新用make命令生成BootImage,结合提示信息和makefile文修改build.c,具体将setup.s改动如下:mov cx,#27mov bx,#0x0007 ! page 0, attribute 7 (normal)mov bp,#msg1mov ax,#0x1301 ! write string, move cursorint 0x10dieLoop:j dieLoopmsg1:.byte 13,10,13,10.ascii "Now we are in SETUP".byte 13,10,13,10将build.c改动如下:if(strcmp("none",argv[3]) == 0)//添加判断return 0;if ((id=open(argv[3],O_RDONLY,0))<0)die("Unable to open 'system'");// if (read(id,buf,GCC_HEADER) != GCC_HEADER)// die("Unable to read header of 'system'");// if (((long *) buf)[5] != 0)// die("Non-GCC header of 'system'");for (i=0 ; (c=read(id,buf,sizeof buf))>0 ; i+=c )if (write(1,buf,c)!=c)die("Write call failed");close(id);fprintf(stderr,"System is %d bytes.\n",i);if (i > SYS_SIZE*16)die("System is too big");return(0);(6)验证:用make是否能成功生成BootImage,运行run命令验证运行结果。

哈工大威海计算机操作系统原理实验报告4.

计算机操作系统原理实验报告

班级:1104202 学号:110420212 姓名:李敖哈尔滨工业大学(威海实验四页面置换算法

、实验目的

1•掌握内存管理基本功能和请求分页式管理的基本原理以及页面置换算法。

2.学会在Linux操作系统下使用C函数和系统调用的编程方法。

3.掌握利用C语言设计实现不同置换策略的页面置换算法。

4.验证虚存存储管理机制及其性能。

对于生成的引用串,计算、比对不同页面

置

换算法的缺页率。

、实验要求

1.学生应完成如下章节的学习:进程和线程、调度、存储管理。

2.安装Linux操作系统,使用C语言编程,利用相关系统调用实现设计。

三、实验内容

1•创建空闲存储管理表、模拟内存、页表等。

2.提供一个用户界面,用户利用它可输入不同的页面置换策略和其他附加参

数。

3.运行置换程序,输出缺页率结果。

四、程序流程图

1.最佳页面置换算法流程图

开始

1

2.先进先出页面置换算法流程图

开蛤

初始化进种块

3.最近最久未使用页面置换算法流程图

初縮化进出块

五、实验结果

最佳页面置换算法分区

先进先出页面置换算法

最近最久未使用页面置换算法六、结果分析本程序已基本实现了页面的置换

算法,包括最佳页面置换算法、先进先出页面置换算法和最近最久未使用页面置换算法。

页表最大空间为5,随机进程最大

序列为50。

哈工大软件设计开发ii中期报告

哈尔滨工业大学计算机科学与技术学院2012年秋季学期《软件设计与开发实践II》中期报告目录1. 进展情况概述 (3)2. 分析模型....................................... 错误!未定义书签。

. 用例模型 (3)用例图 (3)用例描述 (4)用例描述 (6)活动图.................................... 错误!未定义书签。

3. 静态结构模型 (7). 分析类图 (7). 设计类图 (8)4. 动态行为模型 (9). 系统时序图 (9). 对象时序图 .................................. 错误!未定义书签。

. 状态图 ...................................... 错误!未定义书签。

. 过程设计 .................................... 错误!未定义书签。

5. 数据库设计 (11). 数据库设计方案 (12). 逻辑结构设计 ................................ 错误!未定义书签。

. 表设计 (14). 视图设计[如未设计视图此节删去] .............. 错误!未定义书签。

6. 界面设计 (17). 典型界面1 ................................... 错误!未定义书签。

. 典型界面2 ................................... 错误!未定义书签。

7. 体系结构设计 (11). 体系结构风格设计 ............................ 错误!未定义书签。

. 功能结构设计 ................................ 错误!未定义书签。

. 包/构件设计 ................................. 错误!未定义书签。

哈工大电路实验1实验报告

竭诚为您提供优质文档/双击可除哈工大电路实验1实验报告篇一:哈工大数字电路实验报告实验二数字逻辑电路与系统上机实验讲义实验二时序逻辑电路的设计与仿真课程名称:院系:班级:姓名:学号:教师:哈尔滨工业大学20XX年12月实验二时序逻辑电路的设计与仿真3.1实验要求本实验练习在maxplusII环境下时序逻辑电路的设计与仿真,共包括6个子实验,要求如下:3.2同步计数器实验3.2.1实验目的1.练习使用计数器设计简单的时序电路2.熟悉用mAxpLusII仿真时序电路的方法3.2.2实验预习要求1.预习教材《6-3计数器》2.了解本次实验的目的、电路设计要求3.2.3实验原理计数器是最基本、最常用的时序逻辑电路之一,有很多品种。

按计数后的输出数码来分,有二进制及bcD码等区别;按计数操作是否有公共外时钟控制来分,可分为异步及同步两类;此外,还有计数器的初始状态可否预置,计数长度(模)可否改变,以及可否双向等区别。

本实验用集成同步4位二进制加法计数器74Ls161设计n分频电路,使输出信号cpo的频率为输入时钟信号cp频率的1/n,其中n=(学号后两位mod3.2.4实验步骤1.打开mAxpLusII,新建一个原理图文件,命名为exp3_2.gdf。

2.按照实验要求设计电路,将电路原理图填入下表。

3.新建一个波形仿真文件,命名为exp3_2.scf,加入时钟输入信号cp及输出信号cpo,并点击mAxpLusII左侧工具条上的时钟按钮,将cp的波形设置为周期性方波。

4.运行仿真器得到输出信号cpo的波形,将完整的仿真波形图(包括全部输入输出信号)附于下表。

3.3时序电路分析实验3.3.1实验目的练习用mAxpLusII进行时序逻辑电路的分析。

3.3.2实验预习要求1.预习教材《6-3-1异步二进制计数器》2.了解本次实验的目的、电路分析要求3.3.3实验原理分析如下时序电路的功能,并判断给出的波形图是否正确。

CPU处理器实验设计实验报告

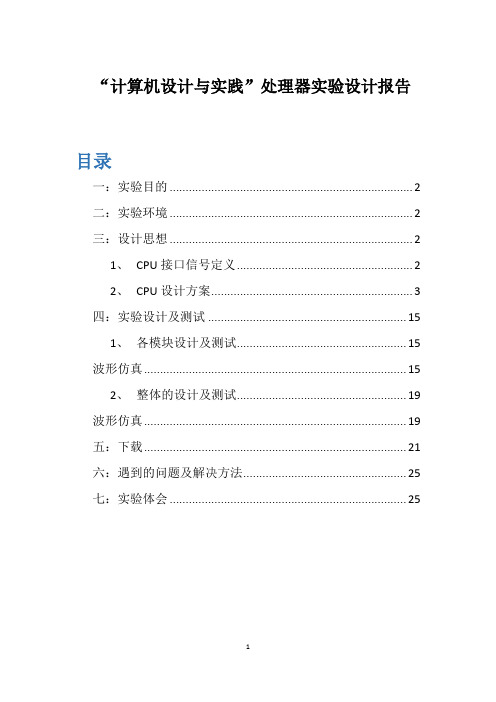

“计算机设计与实践”处理器实验设计报告目录一:实验目的 (2)二:实验环境 (2)三:设计思想 (2)1、CPU接口信号定义 (2)2、CPU设计方案 (3)四:实验设计及测试 (15)1、各模块设计及测试 (15)波形仿真 (15)2、整体的设计及测试 (19)波形仿真 (19)五:下载 (21)六:遇到的问题及解决方法 (25)七:实验体会 (25)一:实验目的1.掌握Xilinx ISE集成开发环境使用方法2.掌握VHDL语言3.掌握FPGA编程方法及硬件调试手段4.深刻理解处理器结构和计算机系统的整体工作原理二:实验环境Xilinx ISE集成开发环境,ModelSim或ISim仿真工具、COP2000实验平台或SD2100数字逻辑设计实验平台或Diligent Nexys3开发板。

三:设计思想1、C PU接口信号定义2、 C PU 设计方案① 指令格式设计1.2. 其他指令15 11 10 28 7 031511 10 8 7 0②微操作定义③节拍划分④各模块设计a)时钟模块模块示意图:模块功能:产生4个节拍,其中,当rst=1时,节拍跳转到T3,并将pc置0.接口说明:信号名位数方向来源/去向备注Clk1I处理器板系统时钟Rst1I处理器板高电平复位T4O取址,运算,4个节拍存储,回写模块b)取指模块模块示意图:模块功能:从内存取出指令。

Rst=1时,pc置0.取出的IR传送给运算,存储,回写模块提供数据,当IRreq=1时,开始从内存取出指令。

当pcupdate=1时,pc接收pcnew的数据,更新pc。

信号名位数方向来源/去向备注T01I时钟模块第一节拍T11I时钟模块第二节拍Rst1I处理器板高有效复位信号PCupdate1I回写模块PC更新信号PCnew16I回写模块PC更新值IRnew16I存储控制模块IR更新值IRreq1O取址模块IR允许信号IR16O存储控制模块导出IR到其他模块PC16O取址模块PC到运算模块c)运算模块模块示意图:模块功能:进行各种运算,并产生进位信号cy和零信号z。

ASIC实验报告(8位CPU的设计)

ASIC设计实验报告学院:电子工程学院学号:2014*******姓名:***指导老师:***2014年11月13日一、实验目的:通过对ASIC实验课的学习,应当学会以下几点:1.熟悉Linux操作系统的应用环境,基本命令行的应用,以及对vi编辑器熟练应用。

2.熟练掌握Verilog编程语言,包括基本组合逻辑电路的实现方法,基本时序逻辑电路的实现方法,怎样使用预定义的库文件,利用always块实现组合逻辑电路的方法已经着重了解assign与always 两种组合逻辑电路实现方法之间的区别,深入了解阻塞赋值与非阻塞赋值的概念以及应用的差别,有限状态机(FSM)实现复杂时序逻辑的方法,以及学会在Linux 系统环境当中应用Synopsys工具VCS进行仿真。

3.熟悉电路设计当中的层次化、结构化的设计方法。

4.熟悉CPU当中有哪些模块组成,模块之间的关系,以及其基本的工作原理。

5.学会利用汇编语言设计程序,注意代码规范性要求。

二、实验要求:按照实验指导书上的要求即:CPU各个模块的Verilog语言代码的编写、编译及仿真正确,并在规定的时间内完成。

要求对CPU进行语言级系统仿真结果正确之后,利用该实验当中采用的八个汇编关键字,编写一个能够实现某种功能的小程序。

然后对其中的控制器电路进行综合,并检查Timing 和Power,进行门级仿真。

三、实验内容:设计一个8位RISC_CPU 系统。

(RISC: Reduced Instruction Set Computer),它是一种八十年代才出现的CPU,与一般的CPU相比,不仅只是简化了指令系统,而且通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。

从实现的方法上,它的时序控制信号部件使用了硬布线逻辑,而不是采用微程序控制方式,故产生控制序列的速度要快的多,因为省去了读取微指令的时间。

此CPU所具有的功能有:(1)取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机设计与实践CPU设计报告

指令格式设计:

注:Ri代表3位该寄存器号的二进制表示,X,sign为8位立即数,add为8为地址

一整体框图

二各模块详细说明(数据流关系、接口说明)

1 时钟管理模块

1.1结构框图:

1.2功能描述:时钟模块为一节拍发生器,以输入时钟信号作为触发,四个节拍循环往复,当“rst”为1时节拍复位。

1.3数据流关系:

1.4接口说明:

port(

rst: in std_logic; --复位信号

clk: in std_logic; --输入时钟信号

k: out std_logic_vector(3 downto 0) --节拍输出

);

2 取址模块

2.1

visit_mem_flag

pc_out

ir_out

2.2功能描述:取指模块主要负责取指操作,当复位信号为1时,pc置零;若pc更新标志(pc_in_flag)为1,则更新当前的pc值;在第一个节拍,将当前pc给到访存控制模块,同时送访存请求信号(visit_mem_flag),取得指令;同时将取得的指令送往运算模块、回写模块,pc送往回写模块。

2.3数据流关系:

Port (rst: in std_logic; --复位

k0,k1: in std_logic; --节拍控制

pc_in_flag: in std_logic; --PC回写允许

ir_in : in std_logic_vector(15 downto 0); --IR进入

pc_in : in std_logic_vector(15 downto 0); --PC回写

visit_mem_flag: out std_logic; --访存信号

pc_out : out std_logic_vector(15 downto 0); --PC输出

ir_out : out std_logic_vector(15 downto 0) --IR输出

);

3 运算模块

3.1结构框图:

3.2功能描述:复位信号为1时,alutou、addr、Cy、Z清零;当回写信号为1时,将回写的数据回写入寄存器中;在第二节拍完成指令的译码工作,并根据译码结果置if_reg(是否更新寄存器),if_pc(是否更新PC),m_r(是否读请求),m_w(是否写请求)四个标志位,并对相关的指令置好addr、aluout和ToHX,以及对一些改变运算标志位的指令置好Cy和Z这两个标志位。

3.3数据流关系:

3.4接口说明:

Port (

rst : in std_logic; --复位信号

k0,k1,k2,k3: in std_logic; --节拍控制 rewrite_flag : in std_logic; --寄存器回写允许 rewrite_data : in std_logic_vector(7 downto 0); --寄存器回写数据

ir_in : in std_logic_vector(15 downto 0); --指令IR进入

aluout : out std_logic_vector(7 downto 0); --运算结果输出 addr : out std_logic_vector(15 downto 0); --准备好的地址输出 if_reg : out std_logic; --是否回写寄存器

if_pc : out std_logic; --是否回写pc

m_r : out std_logic; --给存储管理模块读信号

m_w : out std_logic; --给存储管理模块写信号

toHX : out std_logic_vector(15 downto 0);

Cyflag: out std_logic;

Zflag: out std_logic

);

4 存储控制模块

4.1

4.2功能描述:

此模块主要完成从访存控制模块进行不同指令的存数与取数的请求。

4.3数据流关系:

4.4接口说明: Port( rst: in std_logic; --复位信号 m_w_in : in std_logic; --写请求

m_r_in : in std_logic; --读请求

k2 : in std_logic; --节拍控制

aluout_in : in std_logic_vector(7 downto 0); --Aluout 输入 dataFromMem : in std_logic_vector (7 downto 0);

c_w_out: out std_logic;

c_r_out: out std_logic;

dataToMem : out std_logic_vector (7 downto 0); outToHX : out std_logic_vector (7 downto 0) --输出到回写模块 );

5 访存管理模块

5.1结构框图:

ABUS

ABUS

nMREQ

ABUS

ABUS

ABUS

nBHE

ABUS

ABUS

ABUS

5.2功能描述:当取址模块发出取址请求时,根据PC取出指令送给取址模块;根据存储管理模块给的读写请求对存储器进行读写操作。

5.3数据流关系:

5.4接口说明:

port(

k0,k1,k2: in std_logic; --节拍控制 qz_visit_flag: in std_logic; --取址模块取址信号输入 c_r_in : in std_logic;

c_w_in : in std_logic;

pc_in: in std_logic_vector(15 downto 0); --pc输入

addr_in: in std_logic_vector(15 downto 0); --运算模块地址输入

data_in: in std_logic_vector(7 downto 0); --存数的时候用

DBUS: inout std_logic_vector(15 downto 0);

ABUS: out std_logic_vector(15 downto 0);

nMREQ: out std_logic; --片选

nRD: out std_logic; --读信号

nWR: out std_logic; --写信号

nBHE: out std_logic; --高位访问允许

nBLE: out std_logic; --低位访问允许 data_out: out std_logic_vector(7 downto 0); --取得数据输出

ir_out: out std_logic_vector(15 downto 0) --取得指令输出

);

end fangcun;

6 回写模块

6.1结构框图:

6.2功能描述:第四节拍时完成PC或者是Reg的回写,并完成PC+1的过程。

6.4接口说明:

port(

k3: in std_logic;

if_pc_in: in std_logic;

if_reg_in: in std_logic;

from_M: in std_logic_vector(7 downto 0);

pc_in: in std_logic_vector(15 downto 0); --用于处理jz,jc

jmp_in: in std_logic_vector(16 downto 0);

ir_in: in std_logic_vector(15 downto 0);

pc_update: out std_logic; --PC回写标志

reg_update: out std_logic; --Reg回写标志 pcnew: out std_logic_vector(15 downto 0);

Rdata: out std_logic_vector(7 downto 0)

);

end huixie;

三设计、调试、波形、下载过程中遇到的问题及解决方法。

1.下载到板子上时,IR只显示低8位。

在访存模块中未将DBUS的高八位赋值,只将低八位赋值为data_in,将其的高八位并上“00000000”即可。

2.数据总线的数据显示不对。

在读完数据后,未将DBUS赋值为高阻。

在访存模块中,在读取数据总线数据后,随即将其赋值为高阻状态。

3.运算产生Cy=1时,随即加上Cy=1这一结果,本应该在下一运算中加上。

将对于Cy的处理放于另一个Process中处理,专门处理对于Process的赋值情况,避免了上述情况的发生。

4.部分区域出现多重的嵌套if或case语句时,结果不对。

增加相同的判定条件,从而减少嵌套的层数,可以有效避免。

5.出现多值驱动的报错。

一个信号不能在多个Process里头赋值。

6.处理跳转指令时跳转错误。

之前跳转指令的处理放在运算模块中,但是怎么调都不好使,之后将跳转指令的处理放到回写模块中,便好使了。

四波形

总波形1

总波形2

时钟管理模块

取址模块

运算模块

存储管理模块

访存控制模块

回写模块。