design-compiler的安装和使用资料

使用Design Compiler进行电路综合

使用Design Compiler进行电路综合——By WangJZ magic14@2011-4-19 本文以一个简单设计为例,介绍Synopsys公司的综合工具Design Compiler(以下简称DC)的基本使用流程。

DC综合过程可划分为三个部分:一,读取设计文件,将设计代码转换为DC自带的基本逻辑单元表示的门电路;二,设计者对设计进行约束,包括时序约束和面积约束;三,DC根据设计者提供的约束,对电路进行优化,并映射为流片厂家工艺库逻辑门表示的电路。

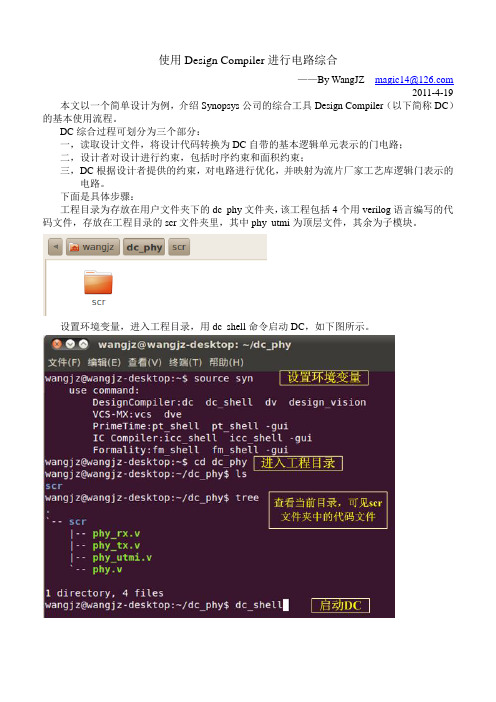

下面是具体步骤:工程目录为存放在用户文件夹下的dc_phy文件夹,该工程包括4个用verilog语言编写的代码文件,存放在工程目录的scr文件夹里,其中phy_utmi为顶层文件,其余为子模块。

设置环境变量,进入工程目录,用dc_shell命令启动DC,如下图所示。

使用set search_path命令设置搜索路径,用set target_library命令设置目标库(流片厂所提供的工艺库)所在路径,用set link_library命令设置链接库路径,如下图所示。

用read_verilog命令读取设计文件,虽然设计文件并不在当前目录dc_phy中,但由于设置了搜索路径(set search_path “$ search_path ./scr”),所以DC仍能找scr文件夹中的设计文件,如下图所示。

用current_design命令告知DC,设计的顶层模块为phy_utmi,并用link命令链接到工艺库,如下图所示:对设计进行时序约束和面积,由于本设计比较简单,所以仅进行几个简单约束作为演示。

约束完后使用compile命令进行综合,如下图所示:综合完成后,使用write命令输出门级网表,使用write_sdc命令输出设计约束,获取门级网表和约束文件后,就可以使用Cadence公司的Encounter软件进行自动布局布线了。

过程如下图所示。

Design Compiler使用简要说明

Design Compiler 使用简要说明Design Compiler可以针对层次化的组合电路或者时序电路的速度、面积和可布性进行优化。

按照所定义的电路的测量特征所要达到的目标,Design Compiler综合一个电路并将其放入目标库中,这样可以生成适用于你的计算机辅助设计工程(CAE)工具的原理图或网表。

综合的过程如下图:•读入设计及其子设计。

•设置顶层的设计特性参数•设置实际时序和面积目标参数•执行check_design验证设计,识别并且更正错误•进行Design Compiler优化在db、verilog、vhdl文件夹下设计内容都是一样的,只是形式不一样。

Db文件夹:ALARM_BLOCK.db ALARM_COUNTER.db ALARM_SM.dbALARM_STATE_MACHINE.db COMPARATOR.dbHOURS_FILTER.db MUX.db TIME_BLOCK.dbTIME_COUNTER.dbTIME_STATE_MACHINE.db CONVERTOR.pla CONVERTOR_CKT.db TOP.dbVerilog文件夹:ALARM_BLOCK.v ALARM_COUNTER.v ALARM_SM.vALARM_STATE_MACHINE.v COMPARATOR.vHOURS_FILTER.v MUX.vTIME_BLOCK.vTIME_COUNTER.vTIME_STATE_MACHINE.v CONVERTOR.pla CONVERTOR_CKT.v TOP.vVhdl文件夹:ALARM_BLOCK.vhd ALARM_BLOCK.vhd ALARM_SM.vhdALARM_STATE_MACHINE.vhd COMPARATOR.vhdHOURS_FILTER.vhd MUX.vhd TIME_BLOCK.vhdTIME_COUNTER.vhdTIME_STATE_MACHINE.vhd CONVERTOR.pla CONVERTOR_CKT.vhd TOP.vhd设置path参数将 Synopsys_installroot/arch/syn/bin加到.cshrc文件中。

cadence15.5.1 Design Entry CIS入门教程

Cadense15.5.1 Design Entry CIS 入门的入门教程(北京索为高科系统技术有限公司 雒海涛) 一、cadence15.5.1 安装 1、安装文件组成:四张光盘,我下载的这个版本四张光盘如下:第一张为【强大的电子设计系统 Cadence.SPB.15.5.1].zwtspb15.bin】其他三场看最名称 最后一个字母 b c d 就是顺序了。

2、安装 cadence 虚拟光驱打开第一张光盘, 里面有个 crack 破解拷贝出来, 不需要安装 license server, 直接安装 product 即可, 安装过程中需要输入的地方一概不需要输入, 一路 next 直到安 装完成。

将 拷 贝 出 来 的 license 文 件 放 到 一 个 合 适 的 位 置 ( 建 议 放 在 安 装 目 录 下 D:\Cadence\license\license.dat) 。

添加环境变量:LM_LICENSE_FILE=D:\Cadence\license\license.dat 3、修改文件 如果使用 cadence 的 project manager 模块,启动后 setup 的时候会出个错误,是路 一个路径错误问题,到 D:\Cadence\SPB_15.5.1\share\library 目录下找到 cds.lib 文件,用 记 事 本 打 开 , 修 改 里 面 的 第 九 行 DEFINE spiceelem ./spiceelem 改 为 DEFINE spice_elem ./spice_elem(spice_elem 这个文件夹可以在这个目录下找到) ,这样就好了。

二、启动 Design Entry CIS Cadence 安装完成后菜单如下: (发现什么没?这个软件肯定很大,恶笑中……..)选择 Design Entry CIS,接下来我们的原理图绘制就要在 Design Entry CIS 完成了。

synopsys design_compiler

Synopsys design_compiler安装记录2015年4月10日22:35 阅读35安装环境:Fedora 21 x86_64Shell : bashHostname :localhost.localdomain安装准备:1)首先查看本机以太网网卡mac地址,打开终端输入ifconfig命令,查看网卡名为eth0的地址。

2)查看本机主机名,终端下输入hostname或cat /etc/hosts进行查看3)查看自己的shell类型echo $04)更新系统输入sudo yum update5) 获得root权限输入su然后执行cd /opt 在该目录下建立安装目录如mkdirdesign_compilertmp&& cd design_compiler&&mkdirscl dv安装过程:6) 我的安装文件是crack ,installer_v3.0 , scl11.5 , syn_vG-2012.06-SP2。

将安装文件全部拷贝到/opt/tmp下,方法:cp path/安装文件名/opt/tmp/然后执行cd /opt/tmp/installer_v3.0 在该目录下执行ls 找到setup.sh 或installer文件,执行./install -gui或./setup.sh 然后进入图形安装界面7) 直接点击Start ,然后在第2个界面中在Site Administrator 选项中任意输入自己看顺眼的字符,其他不用修改,直接点击Next进入第3个界面,在Source 选项中为待安装文件的路径,点击Browse先找到scl11.5(该过程中“..“代表上一个目录“.”代表该本级目录)。

找到后点击Done确定安装文件目录,接下来一直next直到出现有关platform平台的选项,根据自己的系统平台进行选择,64位的话直接选amd64即可,然后继续next。

综合工具-DesignCompiler学习教程

综合⼯具-DesignCompiler学习教程Design Compiler 13讲中的部分内容:1、逻辑综合的概述DC⼯作流程分为三步2、DC的三种启动⽅式GUIdc_shellBatch mode3、DC-Tcl语⾔的基本结构1、⾼层次设计的流程图2、DC在设计流程中的位置3、使⽤DC进⾏基本的逻辑综合的流程图与相应的命令①准备设计⽂件②指定库⽂件③读⼊设计④定义设计环境⑤设置设计约束⑥选择编译策略⑦编译⑧分析及解决设计中存在的问题⑨存储设计数据(1)启动环境配置简述(2).synopsys_dc.setup配置⽂件的书写(3).synopsys_dc.setup的讲解(1)标准单元库①概述⼀个ASIC综合库包括如下信息:·⼀系列单元(包括单元的引脚)。

·每个单元的⾯积(在深亚微⽶中,⼀般⽤平⽅微⽶表⽰,在亚微⽶⼯艺下,⼀般⽤门来称呼,⾄于具体的单位,可以咨询半导体制造商)。

·每个输出引脚的逻辑功能。

·每个输⼊到输出的传递延时,输出到输出的传递延时;inout到输出的传递延时。

②内容与结构Synopsys的⼯艺库是⼀个.lib⽂件,经过LC编译后,产⽣.db⽂件。

⼯艺库⽂件主要包括如下信息:·单元(cell)(的信息):(主要有)功能、时间(包括时序器件的约束,如建⽴和保持)、⾯积(⾯积的单位不在⾥⾯定义,可按照规律理解,⼀般询问半导体⼚商)、功耗、测试等。

·连线负载模型(wire load models):电阻、电容、⾯积。

·⼯作环境/条件(Operating conditions):制程(process)(电压和温度的⽐例因数k,表⽰不同的环境之间,各参数缩放的⽐例)·设计规则约束(Design ):最⼤最⼩电容、最⼤最⼩转换时间、最⼤最⼩扇出。

⼯艺库的结构如下所⽰:(2)DC的设计对象在了解了综合库之后,下⾯介绍⼀下DC的设计对象,虽然这个设计对象相对于综合库没有那么重要,但是还是要了解⼀下的。

Design_Compile】实例笔记

Design_Compile】实例笔记DC 综合DC 又称为设计综合将设计的RTL代码综合成门级网表的过程。

在DC 流程中一般要经过以下几个步骤,以项目A为例做如下分析:1】在项目子目录下创建DC文件夹,在DC文件夹下分别创建db in lib_syn log netlist rpt和script 文件夹以及一个makefile 文件用来运行DC 脚本。

2】第二步就是复制相应工艺技术库文件到lib_syn ,一般有2种文件各3个分别包括了typical worst 和best情况,一类是db,文件一类是lib 文件也可以在lc_shell 下读取lib 得到相应的db文件。

3】第三步将需要综合的设计RTL代码(Verilog 文件)复制到in 文件夹4】第四步在script 创建综合脚本,脚本创建过程将在后面介绍5】第五步编写运行脚本的makefile 文件6】第六步运行脚本而后查看综合报告,是否有违例现象出现,如果有修改脚本加以修复直到最终通过设计。

注意另外的几个文件夹作用db文件夹存放DC综合生成的项目db 文件,综合网表输出到netlist 文件夹,综合程序运行报告存放在log 文件夹中,而综合结果的数据报告则存放在rpt 文件夹中。

DC脚本的编写(A.scr)DC综合脚本基本上有几大部分组成1】定义综合环境中命名规则(分别对net cell port 命名)define_name_rules verilog –casesensitivedefine_name_rules verilog –type net –allowed “a-z A-Z 0-9 _ ” \\-first_restricted “ _ 0-9 N ”\\-replacement_char “_” \\-prefix “n”define_name_rules verilog –type cell –allowed “a-z A-Z 0-9 _ ” \\-first_restricted “ _ 0-9 ”\\-replacement_char “_” \\-prefix “u”define_name_rules verilog –type port –a llowed “a-z A-Z 0-9 _ ” \\-first_restricted “ _ 0-9 ”\\-replacement_char “_” \\-prefix “p”2】综合环境的建立指明库所在的位置Search_path = { lib_syn/db }指定综合所需目标库一般选用最恶劣情况worst 库作目标库target_library = { slow.db}创建链接库,链接库中包括了一些已经做好的设计和子模块,又包括了当前设计的目标库是设计实例化时所用的库文件li nk_library = { “ * ” , slow.db } + synthetic_library在上述的环境建立所需的各类库中,一般有生产商提供目标库,库中的各类cell用于逻辑映射,链接库则包括了目标库,还包括其他一些以前设计实例基本单元,我们门级网表实例化元件和单元都来自于它。

DC使用全书(Design_Compiler)

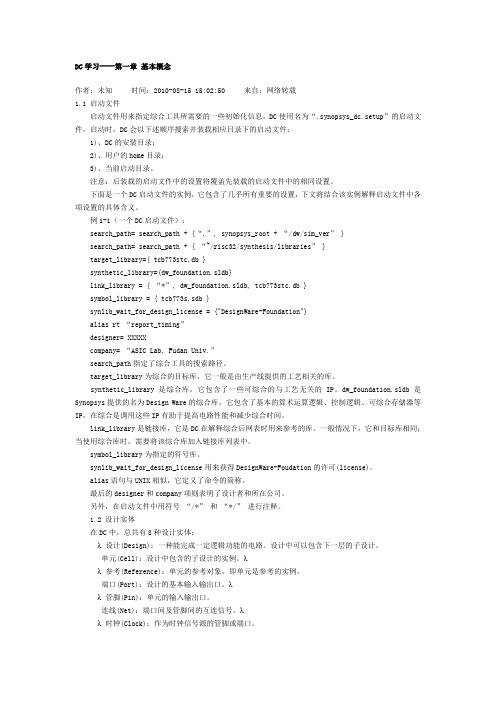

DC学习----第一章基本概念作者:未知时间:2010-08-15 15:02:50 来自:网络转载1.1 启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:1)、DC的安装目录;2)、用户的home目录;3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

下面是一个DC启动文件的实例,它包含了几乎所有重要的设置,下文将结合该实例解释启动文件中各项设置的具体含义。

例1-1(一个DC启动文件):search_path= search_path + {“.”, synopsys_root + “/dw/sim_ver” }search_path= search_path + { “~/risc32/synthesis/libraries” }target_library={ tcb773stc.db }synthetic_library={dw_foundation.sldb}link_library = { “*”, dw_foundation.sldb, tcb773stc.db }symbol_library = { tcb773s.sdb }synlib_wait_for_design_license = {"DesignWare-Foundation"}alias rt “report_timing”designer= XXXXXcompany= “ASIC Lab, Fudan Univ.”search_path指定了综合工具的搜索路径。

target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

逻辑综合工具designCompiler使用教程

逻辑综合工具Design Compiler使用教程编者:适用专业:电子科学与技术沈阳理工大学信息学院2010年6月图形界面design vision操作示例逻辑综合主要是将HDL语言描述的电路转换为工艺库器件构成的网表的过程。

综合工具目前比较主流的是synopsys公司Design Compiler,我们在设计实践过程中采用这一工具。

Design compiler有两种工作模式,一种是tcl模式,另一种为图形模式。

在设计中为增强直观性,采用图形界面design vision。

TCL命令行模式可在设计过程中摸索熟悉,并使之成为习惯。

tcl模式在启动工具之前,准备工作有四项:设计的HDL源文件、采用的工艺库文件、设计的约束文件、工具的启动文件。

图形界面模式最少需要前两项,这里不作多说明。

1. 启动工具登陆Linux之后进入的目录即是用户的家目录,在家目录下建立dcLab作为本次实验dc的操作主目录。

在dcLab目录下,建立设计存放目录如source、约束文件目录如constrn、输出网表文件目录ntlst、报告输出目录rpt、log文件目录log、dc启动目录work,等等。

实验室中的工作站存放有umc公司和tsmc公司的0.18um标准单元库的所有文件,存放在目录:/usr/eda/designKit/下面,设计过程中需要查找的话注意路径与示例中的图片上所示路径稍有不同。

Design compiler工具在工作站中已经安装完毕,且用户的环境变量和license 也已设置完成,登录之后直接启动工具即可。

如果打开终端之后无法启动工具,可能就是license没有启动,需要首先采用命令:start_slic启动license,然后design vision才能正常开启与工作。

建立相关的工程目录之后,进入本次实验的工作目录:~/dcLab/work后,采用启动命令:design_vision&,启动工具后相应的界面如下图1所示。

ubuntu下安装design compiler详细图文教程

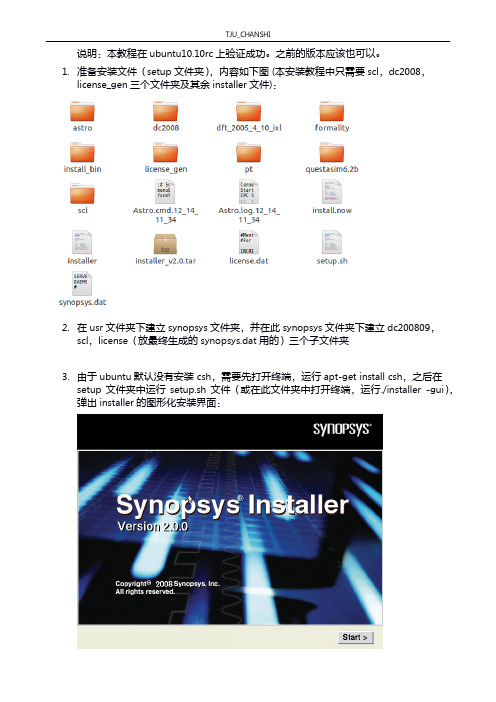

说明:本教程在ubuntu10.10rc上验证成功。

之前的版本应该也可以。

1.准备安装文件(setup文件夹),内容如下图 (本安装教程中只需要scl,dc2008,license_gen三个文件夹及其余installer文件):2.在usr文件夹下建立synopsys文件夹,并在此synopsys文件夹下建立dc200809,scl,license(放最终生成的synopsys.dat用的)三个子文件夹3.由于ubuntu默认没有安装 csh,需要先打开终端,运行apt-get install csh,之后在setup文件夹中运行setup.sh文件(或在此文件夹中打开终端,运行./installer -gui),弹出installer的图形化安装界面:4.先装scl,选择setup文件夹中的scl/temp,如图所示,然后点done,之后一直点next,直到选择安装路径,选择之前创建的usr/synopsys/scl文件夹,安装即可,最后不要关闭,接着装dc2008.5.安装dc2008,选择setup文件夹中的dc2008,安装路径选择之前创建的usr/synopsys/dc200809文件夹,安装完毕,关闭安装界面。

6.之后就是制作license了,其中需要记录linux下的网卡物理地址,打开终端,运行ifconfig,如图:记录下第一行中硬件地址7.切换到windows系统,将计算机名改为ubuntu(因为ubuntu默认的hostname就是ubuntu)重启打开setup/license_gen文件夹, 把eetop[1].cn_dc lic.rar解压,得到EFA LicGen 0.4b和Synopsys SSS Feature Keygen,打开EFA LicGen 0.4b/LicGen.exe,点open,打开EFA LicGen 0.4b/packs下的Synopsys.lpd ,如图:注意勾选use deamon,Select host id要注意:普遍做法是选择Ethernet,但有的电脑可能有好几个网卡(比如无线网卡和有线网卡),此处点Ethernet可能出现的是无线网卡的地址,但我们需要的是有线网卡的地址,此时要选图中的custom,填入第6步Linux系统下记录的硬件地址,之后点generate,弹出下图,此时要注意,其中一定要有“HOSTID=xxxxxx (网卡地址)”字样,网上有的LicGen.exe生成的文件就没有这个字样,导致license生成失败。

Design Compiler ,DC,使用方法

课前说明: 在进行下面的演示之前需要大家拷一个文件夹 dc_example , 里面有本 节课需要用到的文件(包括本讲义) 。这个文件夹在 /home/eda236 目录下,大家 把它们拷贝到自己的帐号目录下,以备使用。

拷贝命令:cp –r ../eda236/dc_example

点 OK ,设置完成。 3. 读入 verilog 文件 选择 File---�Read

在打开文件对话框中选中要打开的文件,在这里我们选中 example1.v 文件。

在 Log 框中出现 successfully 字样表明读入文件成功。相应命令:read_file

点击红色箭头所指的按钮可以查看该电路的 symbol 图。

点击 OK ,相应命令:compile

在 Log 框中出现 Optimization Complete 字样表明优化完成,如下图所示。

6. 查看报告 6.1 查看面积报告

选择 Design-----�Report Area

点击 OK ,相应命令:report_area。

报告总面积为 180.223999,单位是平方微米。

4. 设置约束条件 4.1 设置时钟约束 在 symbol 图上选中 clk 端口

选择 Attributes-----�Specify Clock

出来设置时钟约束的对话框,按下图设置,给时钟取名为 clock,周期 20ns,上升沿 0ns , 下降沿 10ns 。

点击 OK ,时钟约束设置完成。相应命令:creat_clock 4.2 设置复位信号约束 在 symblo 图中选中 rst_n 端口(在本例中它是复位端口) ,选择 Attributes-----�Optimization Directives-----�Input Port

综合与Design_Compiler

综合与Design Compiler综合是前端模块设计中的重要步骤之一,综合的过程是将行为描述的电路、RTL级的电路转换到门级的过程;Design Compiler是Synopsys公司用于做电路综合的核心工具,它可以方便地将HDL语言描述的电路转换到基于工艺库的门级网表。

本章将初步介绍综合的原理以及使用Design Compiler做电路综合的全过程。

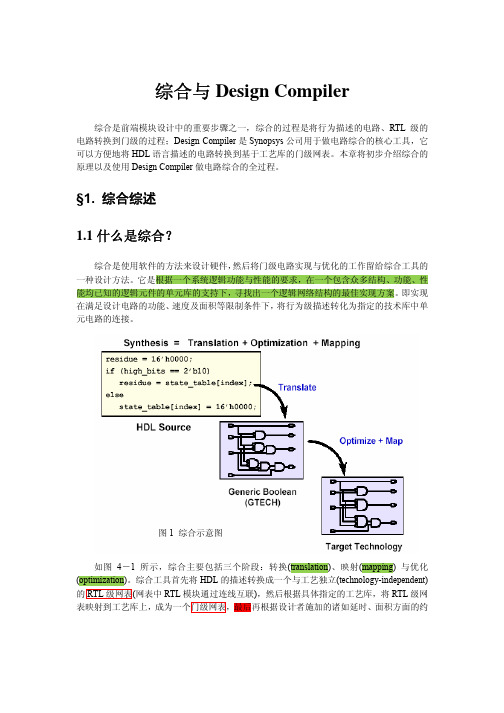

§1. 综合综述1.1什么是综合?综合是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给综合工具的一种设计方法。

它是根据一个系统逻辑功能与性能的要求,在一个包含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑网络结构的最佳实现方案。

即实现在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。

图1 综合示意图如图4-1与优化(optimization)。

综合工具首先将HDL的RTL级网表(网表中RTL模块通过连线互联),然后根据具体指定的工艺库,将RTL级网表映射到工艺库上,成为一个门级网表,最后再根据设计者施加的诸如延时、面积方面的约束条件,对门级网表进行优化。

①1.2 综合的不同层次图2 抽象层次设计的不同的抽象层次如图2所示,随着抽象层次的升高,设计者对于最终硬件(门和触发器)的控制能力越来越小。

设计者可以在上述的三个层次用HDL语言描述他的设计,根据HDL RTL级综合以及行为级综合。

1.2.1 逻辑级综合在逻辑级综合中,设计被描述成布尔等式的形式,触发器、锁存器这样的基本单元采用元件例化(instantiate)的方式表达出来。

下面是一个加法器的逻辑级描述,输出寄存——①有关逻辑综合优化的不同阶段,请参考«VLSI handbook» 的第33章它综合以后的电路网表如下图3所示,对比一下不难看出,逻辑级描述实际上已经暗示了综合以后的网表。

Design Compiler使用笔记_DC中文笔记

DC的手册包括3部分,分别是命令行手册,User Guide,以及参考手册。

其中参考手册有3个,分别是:Constraints & TimingOptimization & Timing AnalysisRegister Retiming本系列笔记为阅读这三个参考手册所做的笔记本文档(约束和时序)包括六章:1. 基本概念2. 约束设计3. 描述设计环境4. 指定时钟和时钟网络5. 描述逻辑功能和信号端口6. 在层次化设计中传播约束Notes for D基本概念篇:利用DC进行综合,主要的过程就是设定适当的约束,从而指导DC综合出较为优化的结果,DC当中进行综合可以分成三大步骤:Transfer、Mapping、Optimization。

总的流程来说为:1.设定各种用于综合的库(.db或者.lib格式)及各种IP核的库。

库中主要描述了库线负载模型、Max_transition、Max_Capacitance 等等;各种单元的时延、面积、逻辑功能、输入输出负载、功耗等等,注意,具有相同footprint的单元是可以互相替换的。

2.读入设计此时可以对设计设定参数(Verilog当中的parameter,VHDL当中的generic)。

设计读入以后将会被转换(Transfer)成网表,该网表是基于一种通用库的,即gtech库(Generic Technology),该库可以较为容易的映射到各种实际的工艺库当中,当然,这个库是没有时延的。

3.设定约束DC的约束总体分成两类:Design Rule Constraints以及Optimization Constraints。

前者是必须要满足的,包括工艺库当中进行的各种限定,而后者是为了优化而设定的。

总的说来,约束包括面积,时序,负载,Porosity,动态/漏功耗(使用Power Compiler )等几大类。

4.约束设定好之后,就可以让DC根据这些约束将通用库的网表映射(Mapping)到实际的库当中去,并进行各种的优化(Optimization),此时就可以得到结果的网表,用于后端的布局布线。

Design Compile (DC) 使用说明

Design Compile (DC) 使用说明一.软件说明Design Compile是synopsys的综合软件,它的功能是把RTL级的代码转化为门级网表。

综合包括转译(Translation),优化(Opitimization),映射(Mapping)三个过程。

在转译的过程中,软件自动将源代码翻译成每条语句所对应的功能模块以及模块之间的拓扑结构,这一过程是在综合器内部生成电路的布尔函数的表达,不做任何的逻辑重组和优化。

优化:基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对转译结果作逻辑优化和重组。

在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库中搜索符合条件的单元来构成实际电路。

RTL design Top-level constraintsPrepare design acs_read_hdlsource src/constraints/to GTECH databaseCompile design acs_compile_design designOptimized designAnalyze resultsConstraints met ? DoneNoRefine design acs_refine_design designRefined designDC有两种界面,图形界面通过敲入design vision&调用出来,另一种命令行界面通过dc_shell-t调用。

建议初学者使用图形界面,因为图形界面比较容易上手;业界的人士比较青睐命令行界面,因为其所耗的资源少,并且将所用的命令写成综合脚本的形式,便于查阅。

因为门级和代码级不同,代码级考虑的是理想情况,但是实际电路不是这样的,它有门级的延时,线的延时,信号的转换时间,甚至时钟信号到达各个触发器的时间不相等。

基于这些考虑,DC通过施加约束,模拟实际环境,根据实际情况得出门级网表。

因此如何适当的施加约束是DC的关键所在。

Synopsys软件安装步骤及说明

DAEMONsnpslmdSCL文件夹路径/linux/bin/snpslmd

例如:我安装SCL的目录为/eda_tools/synopsys/scl10.9,查询计算机信息如图。

故:SERVER和DAEMON行应该为(端口可根据需要填写,我这里只是示例):

SERVERlocalhost.localdomain000c2988ffc628000

7、附录……………………………………………………………..…..13

Synopsys公司的软件都不用破解文件,图形安装流程几乎一样,关键在于license的制作,安装配置都较为简单,在制作license时需要细心。

1

1)、所要安装的软件的软件包

说明:软件包一般包含三个压缩包:common,amd64,linux。可以没有amd64或者linux包,但是必须有common包,amd64是64bit软件包,linux是32bit软件包,安装时可全部安装。

附录:

bashell环境变量.bashell部分配置:

exportSNPSLMD_LICENSE_FILE=27000@localhost.localdomain

################################DC10.03#############################

exportSYNOPSYSDC=/eda_tools/synopsys/DC10.03

2、软件安装….………………………………………………………..3

3、SCL安装….………………………………………………………...5

4、制作license……………………………………………………....6

Design+Compiler中文教程PPT

综合的定义

逻辑综合:决定设计电路逻辑门的相互连接。 逻辑综合的目的:决定电路门级结构、寻求时序和与面积的平 衡、寻求功耗与时序的平衡、增强电路的测试性。 逻辑综合的过程:首先,综合工具分析HDL代码,用一种模型 (GTECH) ,对HDL进行映射,这个模型是与技术库无关的;然后, 在设计者的控制下,对这个模型进行逻辑优化;最后一步,进行 逻辑映射和门级优化,将逻辑根据约束,映射为专门的技术目标 单元库(target cell library)中的cell,形成了综合后的网 表。

ASIC design flow

Constrain scripts(续) /* Apply default drive strengths and typical loads for I/O ports */ set_load 1.5 all_outputs() set_driving_cell -cell IV all_inputs() /* If real clock, set infinite drive strength */ if (find(port, clk) == {"clk"}) { set_drive 0 clk } /* Apply default timing constraints for modules */ set_input_delay 1.2 all_inputs() -clock clk_name set_output_delay 1.5 all_outputs() -clock clk_name set_clock_skew -minus_uncertainty 0.45 clk_name /* Set operating conditions */ set_operating_conditions WCCOM /* Turn on Auto Wireload selection Library must support this feature */ auto_wire_load_selection = true

数字电路系统综合与Design Compiler(1)

综合与Design Compiler综合是前端模块设计中的重要步骤之一,综合的过程是将行为描述的电路、RTL级的电路转换到门级的过程;Design Compiler是Synopsys公司用于做电路综合的核心工具,它可以方便地将HDL语言描述的电路转换到基于工艺库的门级网表。

本章将初步介绍综合的原理以及使用Design Compiler做电路综合的全过程。

§1. 综合综述1.1什么是综合?综合是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给综合工具的一种设计方法。

它是根据一个系统逻辑功能与性能的要求,在一个包含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑网络结构的最佳实现方案。

即实现在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。

图1 综合示意图如图4-1所示,综合主要包括三个阶段:转换(translation)、映射(mapping) 与优化(optimization)。

综合工具首先将HDL的描述转换成一个与工艺独立(technology-independent)的RTL级网表(网表中RTL模块通过连线互联),然后根据具体指定的工艺库,将RTL级网表映射到工艺库上,成为一个门级网表,最后再根据设计者施加的诸如延时、面积方面的约束条件,对门级网表进行优化。

①1.2 综合的不同层次图2 抽象层次设计的不同的抽象层次如图2所示,随着抽象层次的升高,设计者对于最终硬件(门和触发器)的控制能力越来越小。

设计者可以在上述的三个层次用HDL语言描述他的设计,根据HDL语言描述的层次的高低,综合也相应的可以分为逻辑级综合,RTL级综合以及行为级综合。

1.2.1 逻辑级综合在逻辑级综合中,设计被描述成布尔等式的形式,触发器、锁存器这样的基本单元采用元件例化(instantiate)的方式表达出来。

下面是一个加法器的逻辑级描述,输出寄存——①有关逻辑综合优化的不同阶段,请参考«VLSI handbook» 的第33章它综合以后的电路网表如下图3所示,对比一下不难看出,逻辑级描述实际上已经暗示了综合以后的网表。

Synopsys_Design_Compiler使用

Synopsys Design Compiler使用一、介绍:美国Synopsys公司发布的“Design Compiler”软件,简称“DC”,是一种逻辑合成工具。

通过改进电路延迟时间的计算方法,缩小了逻辑合成时的时序与布局完成后的最终时序之间的偏差。

DC得到全球60多个半导体厂商、380多个工艺库的支持。

据最新Dataquest的统计,Synopsys的逻辑综合工具占据91%的市场份额。

DC是十二年来工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

二、要求:由于实训没有硬性要求VHDL文件,本人挑选了已经预先做好的洗衣机时控电路,利用Synopsys Design Compiler工具,进行优化分析,通过这一过程熟悉软件的使用。

三、过程:设置优化运行库,鉴于老师在练习手册上面提供的例子,我们使用库LSI-10K,因此在打开VHDL文件前,需要作以下设置Setup->Defaults,填入以下信息。

在File->read打开要分析优化的VHDL文件,这里我选择一个洗衣机时控电路NewWasher.vhd 如下所示(分别为不同层次的视图:顶层、器件、门级电路)在Tools->Design Optimization中设置好兼顾平衡的约束条件(左图),确定编译后,产生了右边经过优化的门级电路图。

接下来,把优化过的图形转换为VHDL文件和DB文件输出,另存到指定位置File->Save As如右图,生成了新的DB文件和vhd文件。

接下来,是要设定CLK的周期,根据分析、优化、编译出来的Slack Time 松弛数值和Area面积数值,选取最合适的平衡点。

Synopsys

Synopsys Design Compiler的安装问题因为要学习这个软件,因此从安装开始的,但是过程中遇到了很多问题。

备忘如下。

这个软件是⼀个⽼师给的绿⾊版,按理说解压后应该就能⽤的,但是过程相当纠结。

我是安装在centos 6.7的系统中,按照步骤如下:(1)在根⽬录下解压eda.tar.gz(约10GB),得到eda⽂件夹,包含三个⼦⽬录(cadence,synopsys,mentor), synopsys 包含其license⽬录,以及G和H-foundation。

(2) ⽤提供的rc.local替换/etc/rc.d/rc.local 。

(3)⽤提供的.bashrc替换⽤户根⽬录下的.bashrc。

(4)virtuoso64bit_patch⽂件夹中的readme (5) ETS_EDI⽂件夹中的readme. (4)和(5)是对cadence⽂件夹下的操作,看似没有关系,但是如果不执⾏,运⾏dc_shell会有command not found,当然⼀切做完后要重启机器在执⾏dc_shell命令。

⾸先给⼤家看.bashrc⽂件中的内容如下:# .bashrc# Source global definitionsif [ -f /etc/bashrc ]; then. /etc/bashrcfi# User specific aliases and functionsexport CDS_AUTO_64BIT=ALL########################cadence###########################################################CDS_License###############################export OA_HOME=/eda/cadence/MMSIM121/oa_v22.43.006export CDS_LIC_FILE=/eda/cadence/env/cdn_full.dat########################IC615####################################export CDS_HOME=/eda/cadence/IC615export CDS_INST_DIR=/eda/cadence/IC615export PATH=$CDS_INST_DIR/tools/bin:$CDS_INST_DIR/tools/dfII/bin:$PATHexport CDS_Netlisting_Mode=Analog########################EDI101#####################################export EDI_HOME=/eda/cadence/EDI101export EDI_INST_DIR=/eda/cadence/EDI101export PATH=$EDI_INST_DIR/tools/bin:$PATH########################ETS101#####################################export ETS_HOME=/eda/cadence/ETS101export ETS_INST_DIR=/eda/cadence/ETS101export PATH=$ETS_INST_DIR/tools/bin:$ETS_HOME/bin:$PATH########################MMSIM121###################################export MMSIM_HOME=/eda/cadence/MMSIM121export MMSIM_INST_DIR=/eda/cadence/MMSIM121export PATH=$MMSIM_INST_DIR/tools/bin:$MMSIM_INST_DIR/tools/spectre/bin:$PATH########################INCISIV###################################export INCISIV_HOME=/eda/cadence/INCISIV102export INCISIV_INST_DIR=/eda/cadence/INCISIV102export PATH=$INCISIV_INST_DIR/tools/bin:$INCISIV_HOME/bin:$PATH########################mentor###########################################################Calibre2013###############################export MGC_HOME=/eda/mentor/ixl_cal_2013.2_18.13export PATH=$MGC_HOME/bin:$MGC_HOME/lib:$PATHexport MGLS_LICENSE_FILE=/eda/mentor/env/mentor.dat########################synopsys DC################################export LM_LICENSE_FILE=27000@localhost.localdomainexport PATH=/eda/synopsys/H-2013.03-SP1/bin:$PATHexport PATH=/eda/synopsys/G-2012.06-SP3/bin:$PATH########################synopsys ICC################################export ICC_HOME=/eda/synopsys/icc_2013.12export PATH=/eda/synopsys/icc_2013.12/bin:$PATH以上就是.bashrc的内容,主要是环境变量的设置。

第二章 Design Compiler简介

第二章 Design Compiler概述Design Compiler是Synopsys综合软件的核心产品。

它提供约束驱动时序最优化,并支持众多的设计类型,把设计者的HDL描述综合成与工艺相关的门级设计;它能够从速度、面积和功耗等方面来优化组合电路和时序电路设计,并支持平直或层次化设计。

第一节 Design Compiler入门2-1-1 基本的综合流程图2.1中显示了一个简化的综合流程:图2.1 基本综合流程Design Compiler按照所有标准EDA格式读写文件,包括Synopsys内部数据库(.db)和方程式(.eqn)格式。

除此之外,Design Compiler还提供与第三方EDA工具的链接,比如布局布线工具。

这些链接使得Design Compiler和其他工具实现了信息共享。

2-1-2 Design Compiler的功能利用Design Compiler,设计者可以:●利用用户指定的门阵列、FPGA或标准单元库,生成高速、面积优化的ASIC;●能够在不同工艺技术之间转换设计;●探索设计的权衡,包括延时、面积和在不同负载、温度、电压情况的功耗等设计约束条件;●优化有限状态机的综合,包括状态的自动分配和状态的优化;●当第三方环境仍支持延时信息和布局布线约束时,可将输入网表和输出网表或电路图整合在一起输入至第三方环境;●自动生成和分割层次化电路图2-1-3支持的文件格式表2.1列出了Design Compiler所支持的所有的输入输出的设计文件格式:表2.1 支持的文件格式2-1-4 设计类型、输入格式和输出格式设计类型:设计可以是分层的或平直的,时序的或组合的;输入格式:支持VHDL和Verilog作为设计描述的输入格式,也支持开编程逻辑阵列(PLA)和EDIF 200格式;输出格式:除了Synopsys二进制格式(.db),还支持VHDL、Verilog、EDIF 200、方程式、大规模集成(large-scale integration)、Mentor图形、PLA、状态表和Tegas格式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

的,该文件在scl目录下)

的实际路劲

修改主机名

用记事本打开“synopsys.dat”,将第一行修改为:SERVER 主机名 MAC地址 27000。其中主机名是Linux系统下的主机名,可在Linux的终端中用“uname -a”命 令查看,默认一般为“localhost.localdomain”;MAC地址就是网卡地址,后面的 27000是默认需要的。本文中该行信息为“SERVER localhost.localdomain 000c2916d785 27000”

Design_Compiler_2008.09_common.tar

Design_compiler_2008.09_linux.tar 3.安装DC2008需要用到SCL软件包

scl_v10.9.3_common.tar

scl_v10.9.3_linux.tar 4.安装平台 在linux4.6上安装(如果要使用虚拟机,则使用vmware6.5,使用虚拟机有 很多方便,可以在虚拟机中随时读取windows下的文件,资料复制都很方便 (可以直接往linux系统里面拖资料!),而且对于在只有一台电脑的情况下, 可以利用windows平台查看课件,查资料等)

3.利用KeyGen得到得到FEATURE SSS信息 ,运行“KeyGen.exe”,在“SECRET DATA” 栏中填入得到的SECRET DATA码,在“HOST ID”中填入你的MAC地址。

我们刚才得到的SECRET DATA

你的MAC地址

点击Generate后,会在此文件夹中生成一个license.dat的文件。

众多,为了方便,最好分类安放,下面是我文件夹内部的目录结构,仅供参考以 及便于后面的说明。建议安装的时候也参考这样。

2. 安装installer,将installer2.0 解压到installer 文件夹即可; 3. 安装SCL 终端下打开install解压文件夹,运行./installer –gui会出现图形安装界面

用记事本打开

license.dat,将里面

的Feature SSS信息拷贝

到原来生成的

“synopsys.dat”文件内,

替换原有的 Feature SSS

内容。这样,

“synopsys.dat”基本做 好了。

最后,我们要把 SERVER中的主机名和

替 换

下面snpslmd(我们的

license是由此文件启动

SNPSLMD_LICENSE_FILE的意思是指我们要用snpslmd这个license管理器来启动license

安装完成

终端下 输入design_vision可以打开DC图形界面 输入dc_shell即可打开文本界面,在dc_shell模式下, 如果想看图形界面,再输入start_gui即可进入图形界面

在options下我们选 中shared Folders, 选中always enable>add

,就可以添加我们需 要共享的目录了, 完整以后,我们会 在linux,/mnt/hgfs/ 下看到我们所添加 的文件夹,以后就 可以自由地访问 windows中任何文件 了

DC2008的安装

软件安装: 1. 目录结构,本人在linux 的目录下建了/home/wangjun/soft文件夹,IC设计软件

制作license需要机器的MAC地址,查询本机MAC地址可以有一下两 种方法:分别在windows和linux下,但是要注意的是,如果是虚拟机安装 的话,虚拟机的MAC地址也是虚拟的!

(1).windows下查看MAC的办法:

运行cmd,在命令行中输入ipconfig/all

我们可以看到我们的物理地址,

2>在虚拟机中,我们还可以在虚拟机的安 装目录下打开vmware的配置文件,用记事 本打开,里面也可以查看到MAC地址,找 到ethernet0.generatedAddress这一行,也可 以查到MAC数据!

生成license

3.点generate会产生一个 初步的license文件

1.Custom中填入你的MAC地址

安装common包,选好解压目录,点击done

选择好common包的安装目录,安装linux包是 一样安装到这个文件夹!

软件包安装完成, 点击finish,每次都 会出现另外的对话 框,点dismiss就可 以

DC2008—license制作和启动配置文件

注意!!!做这一步之前,请把EFA LicGen 0.4b和Synopsys SSS Feature Keygen两个文件夹放到桌面上!! License 制作是很最关键的,没有license软件肯定没法启动。 首先我们打开EFA LicGen 0.4b文件夹,有一个license产生器 双击后,我们打开packs中的synopsys.lpd这个文件

(这里有一个问题,就是在刚安装完的时候,没重启过linux就在终端输入启 动命令可能会说命令未找到,这时我们只要进入 /home/wangjun/synopsys/dc/bin下,双击dc_shell这个文件,选择在终端中运行, 可以启动DC,然后以后都可以正常启动。)

2.这个勾要选,然后也在 custom下填写MAC地址

这样的话就产生了初步的license,我们save 到Synopsys SSS Feature Keygen文件下,保 存为synopsys.dat

这一步我们就要用到KeyGen产生FEATURE SSS,运行KeyGen之前,我们要利用 “sssverify”得到“secret date”信息。

Vmware tools的安装及共享文件的设置

Linux系统安装完并进行相关设置以后,在vm软件菜单中的vm选项中选中install vmware tools,我们可以看到在linux系统中出现一个光盘图标,点击进入,有两个 压缩包,解压之后发现一个vmware-install.pl 文件,在终端中运行它 ./vmwareinstall.pl,然后一直enter知道安装完成。这时在/mnt下是不是看到了一个hgfs文件 夹这就表明安装成功了,下面就要讲一下怎么来设置共享了,这一部分更简单。 还是在vm菜单中,我们选中setting会出现以下界面

图形安装界面,点start开始 安装

选中scl解压所在文件夹,然后一直next,过程中有些选项都不需要管,也不需 要填,直到选中安装目标路径

我把scl安装在dc目录下

Scl安装完毕! 同样的方法可以安装common包和linux包,安装这两个包的时候最好分开安装, 先安装common包,例如,我的common和linux包分别放在 /home/wangjun/soft/dc/dc200808/common /home/wangjun/soft/dc/dc200808/linux 但是安装目录一定要安装在一起!即都安装在/home/wangjun/synopsys/dc下!

最终的license!!

加入配置文件

在.cshrc中,我们加入以下变量: # .cshrc for the licenses of synopsys dc setenv SNPSLMD_LICENSE_FILE /home/wangjun/synopsys/key/synopsys.dat # .cshrc for synopsys DC 2008.09 setenv SYNOPSYS /home/wangjun/synopsys/dc Setenv PATH "$SYNOPSYS/linux/syn/bin:${PATH}:"

笔记本有2个网卡,所以有两个MAC

但是synopsys软件只认有线的!即上面那 个physical address!

(如果我们是用虚拟机安装linux的话

就只能用虚拟机的MAC了!)

(2).linux下查看MAC的办法:

1>在终端中运行/sbin/ifconfig –a

Hwaddr后面就是虚拟机的MAC!

将“synopsys.dat”第二行改为: DAEMON snpslmd /home/wangjun/synopsys/dc/scl/linux/bin/snpslmd,也就是Linux下 snpslmd的路径(就是我们刚才安装的scl文件夹的子文件夹下),具体根据实际情况 修改,之后保存,也可以保存为txt格式。下图就是我最终的license,将它放到 /home/wangjun/synopsys/key目录下

新建虚拟机

选择自定义安装

选择这项

我们安装的系统是linux4

选择安装目录

处理器个数,选1 选择虚拟内存

连接方式选择桥接模式

选总线模式

创建新的虚拟硬盘,硬盘类型 选IDE

设置虚拟硬盘大小,根 据实际需要进行设定

一个虚拟PC就设置完成了,点击完成, 出现虚拟机界面,就可以开始安装linux 了,制作DC2008的license的时候需要 MAC地址,可以在此时记下来你虚拟机 的MAC地址。这里是(000C29925964) 然后我们可以点击右下方的光盘图标, 加入镜像文件即可安装了。具体安装见 培训课件中linux的安装

逻辑综合

Based on design compile 200809

某 2010.4.21

DC2008的安装

准备工作:

1.installer软件 我们使用 installer_v2.0 Synopsys公司的软件安装需要Installer引导。也即用Installer才可安装 Synopsys公司的软件。因此,我们需要Installer软件。 2.DC的安装软件包

准备工作:

5.此外我们需要自己制作license,因此需要license破解器EFA LicGen

这就是我们安装DC2008所需要的全部资料

安Байду номын сангаас步骤