XilinxFPGA引脚功能详细介绍

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

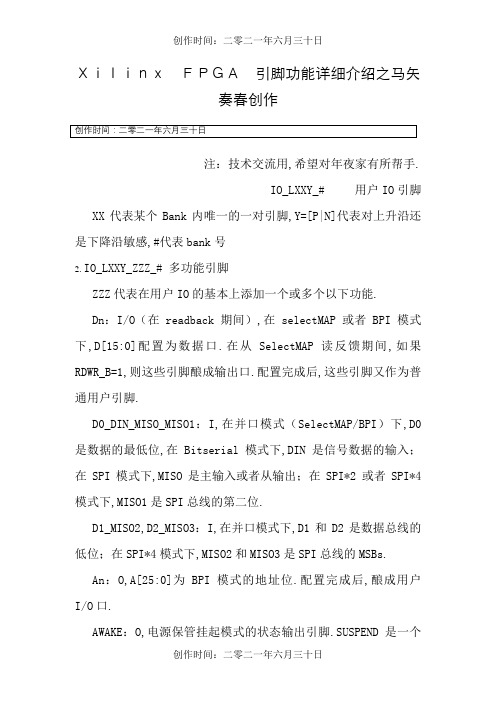

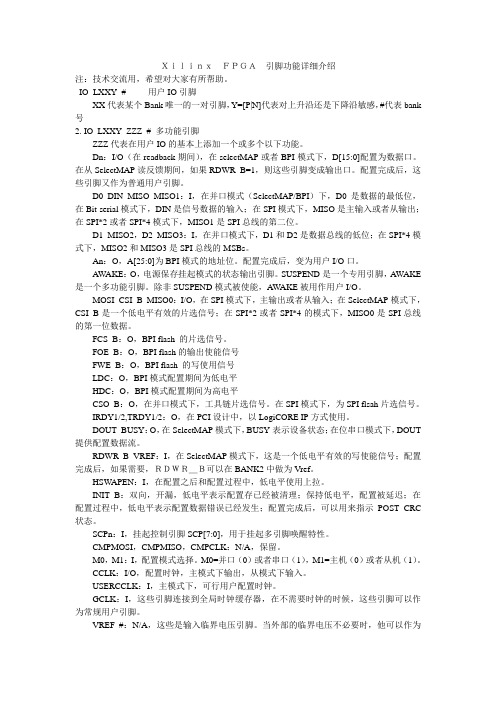

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx-FPGA器件管脚说明doc

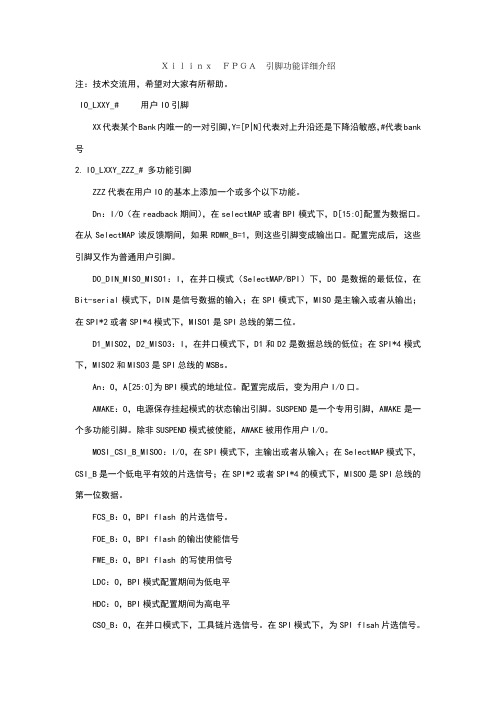

弱上拉

I/O

内部有弱上拉。可以随逻辑需要配置成输入或输出。在配置完成前,这些引脚有内部上拉电阻(25K-100K)至高电平。

在配置模式,这些引脚有弱上拉电阻。对大多数流行的配置模式来而言,在从动串行模式下,模式引脚不需要连接。在有或没有弱上拉或上拉电阻的情况下,三个模式输入引脚可以独自配置。推荐上拉电阻值为4.7K。在特殊定义时,这些引脚只能被作为输入或输出。为应用这些引脚,必须使用库元件MD0、MD1和MD2代替通常的PAD,同时必须使用输入输出缓冲器。

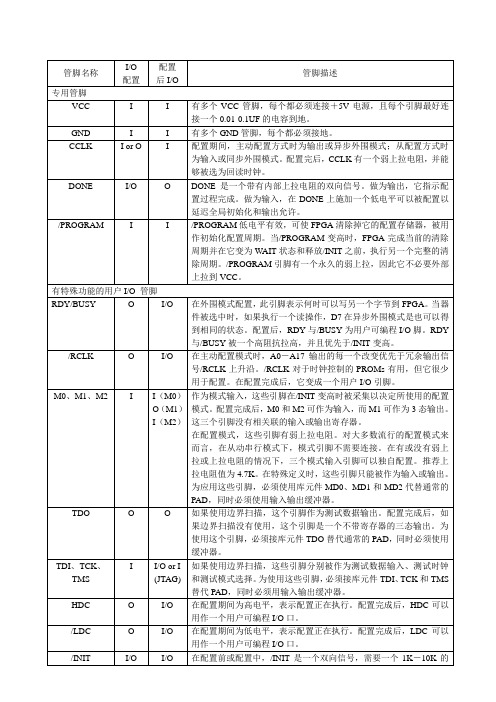

管脚名称

I/O

配置

配置

后I/O

管脚描述

专用管脚

VCC

I

I

有多个VCC管脚,每个都必须连接+5V电源,且每个引脚最好连接一个0.01-0.1UF的电容到地。

GND

I

I

有多个GND管脚,每个都必须接地。

CCLK

I or O

I

配置期间,主动配置方式时为输出或异步外围模式;从配置方式时为输入或同步外围模式。配置完后,CCLK有一个弱上拉电阻,并能够被选为回读时钟。

HDC

O

I/O

在配置期间为高电平,表示配置正在执行。配置完成后,HDC可以用作一个用户可编程I/O口。

/LDC

O

I/O

在配置期间为低电平,表示配置正在执行。配置完成后,LDC可以用作一个用户可编程I/O口。

/INIT

I/O

I/O

在配置前或配置中,/INIT是一个双向信号,需要一个1K-10K的外部上拉电阻。作为一个低电平有效输出,/INIT在电源稳定和清除内部配置内存期间保持低电平。作为一个低电平有效输入,/INIT能在开始配置前保持FPGA在内部WAIT状态。主动模式下,在/INIT变高后,器件将在WAIT状态保持30+300US。在配置期间,输出为低表示配置数据错误。当I/O有效后,/INIT为一个用户可编程I/O引脚。

AlteraFPGA和Xilinx-FPGA-引脚功能详解解读

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

xilinxfpga引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍之马矢奏春创作注:技术交流用,希望对年夜家有所帮手.IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能.Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口.在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚酿成输出口.配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位.D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs.An:O,A[25:0]为BPI模式的地址位.配置完成后,酿成用户I/O口.AWAKE:O,电源保管挂起模式的状态输出引脚.SUSPEND是一个专用引脚,AWAKE是一个多功能引脚.除非SUSPEND模式被使能,AWAKE被用作用户I/O.MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据.FCS_B:O,BPI flash 的片选信号.FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号.在SPI模式下,为SPI flsah片选信号.IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用.DOUT_BUSY:O,在SelectMAP模式下,BUSY暗示设备状态;在位串口模式下,DOUT提供配置数据流.RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref.HSWAPEN:I,在配置之后和配置过程中,低电平使用上拉.INIT_B:双向,开漏,低电平暗示配置内存已经被清理;坚持低电平,配置被延迟;在配置过程中,低电平暗示配置数据毛病已经发生;配置完成后,可以用来指示POST_CRC状态.SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性.CMPMOSI,CMPMISO,CMPCLK:N/A,保管.M0,M1:I,配置模式选择.M0=并口(0)或者串口(1),M1=主机(0)或者从机(1).CCLK:I/O,配置时钟,主模式下输出,从模式下输入.USERCCLK:I,主模式下,可行用户配置时钟.GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为惯例用户引脚.VREF_#:N/A,这些是输入临界电压引脚.当外部的临界电压不需要时,他可以作为普通引脚.当作作bank内参考电压时,所有的VRef都必需被接上.3.多功能内存控制引脚M#DQn:I/O,bank#内存控制数据线D[15:0]M#LDQS:I/O,bank#内存控制器低数据选通脚M#LDQSN:I/O,bank#中内存控制器低数据选通NM#UDQS:I/O,bank#内存控制器高数据选通脚M#UDQSN:I/O,bank#内存控制器高数据选通NM#An:O,bank#内存控制器地址线A[14:0]M#BAn:O,bank#内存控制bank地址BA[2:0]M#LDM:O,bank#内存控制器低位掩码M#UDM:O,bank#内存控制器高位掩码M#CLK:O,bank#内存控制器时钟M#CLKN:O,bank#内存控制器时钟,低电平有效M#CASN:O,bank#内存控制器低电平有效行地址选通M#RASN:O,bank#内存控制器低电平有效列地址选通M#ODT:O,bank#内存控制器外部内存的终端信号控制M#WE:O,bank#内存控制器写使能M#CKE:O,bank#内存控制器时钟使能M#RESET:O,bank#内存控制器复位4.专用引脚DONE_2:I/O,DONE是一个可选的带有内部上拉电阻的双向信号.作为输出,这个引脚说明配置过程已经完成;作为输入,配置为低电平可以延迟启动.PROGRAM_B_2:I,低电平异步复位逻辑.这个引脚有一个默认的弱上拉电阻.SUSPEND:I,电源呵护挂起模式的高电平有效控制输入引脚.SUSPEND是一个专用引脚,而AWAKE是一个复用引用.必需通过配置选项使能.如果挂起模式没有使用,这个引脚接地.TCK:I,JTAG鸿沟扫描时钟.TDI:I,JTAG鸿沟扫描数据输入.TDO:O,JTAG鸿沟扫描数据输出.TMS:I,JTAG鸿沟扫描模式选择5.保管引脚NC:N/A,CMPCS_B_2:I,保管,不接或者连VCCO_26.其它GND:VBATT:RAM内存备份电源.一旦VCCAUX应用了,VBATT可以不接;如果KEY RAM没有使用,推荐把VBATT接到VCCAUX或者GND,也可以不接.VCCAUX:辅助电路电源引脚VCCINT:内部核心逻辑电源引脚VCCO_#:输出驱动电源引脚VFS:I,(LX45不成用)编程时,key EFUSE电源供电引脚.当不编程时,这个引脚的电压应该限制在GND到 3.45V;当不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,悬空也可以.RFUSE:I,(LX45不成用)编程时,key EFUSE接地引脚.当不编程时或者不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,然而,也可以悬空.7.GTP 引脚MGTAVCC:收发器混合信号电路电源引脚MGTAVTTTX,MGTAVTTRX:发送,接收电路电源引脚MGTAVTTRCAL:电阻校正电路电源引脚MGTAVCCPLL0,MGTAVCCPLL1:锁相环电源引脚MGTREFCLK0/1P,MGTREFCLK0/1N:差分时钟正负引脚MGTRREF:内部校准终真个精密参考电阻引脚MGTRXP[1:0],MGTRXN[1:0]:差分接收端口MGTTXP[1:0],MGTTXN[1:0]:差分发送端口• 1. Spartan6系列封装概述Spartan6系列具有低本钱、省空间的封装形式,能使用户引脚密度最年夜化.所有Spartan6 LX器件之间的引脚分配是兼容的,所有Spartan6 LXT器件之间的引脚分配是兼容的,可是Spartan6 LX和Spartan6 LXT器件之间的引脚分配是不兼容的.表格 1Spartan6系列FPGA封装2. Spartan6系列引脚分配及功能详述Spartan6系列有自己的专用引脚,这些引脚是不能作为Select IO使用的,这些专用引脚包括:专用配置引脚,表格2所示 GTP高速串行收发器引脚,表格3所示表格 2Spartan6 FPGA专用配置引脚注意:只有LX75, LX75T, LX100, LX100T, LX150, and LX150T器件才有VFS、VBATT、RFUSE引脚.表格 3Spartan6器件GTP通道数目注意:LX75T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676中封装了8个GTP通道;LX100T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676 和FG(G)900中封装了8个GTP通道.如表4,每一种型号、每一种封装的器件的可用IO引脚数目不尽相同,例如对LX4 TQG144器件,它总共有引脚144个,其中可作为单端IO引脚使用的IO个数为102个,这102个单端引脚可作为51对差分IO使用,另外的32个引脚为电源或特殊功能如配置引脚.表格 4Spartan6系列各型号封装可用的IO资源汇总表格 5引脚功能详述3. Spartan6系列GTP Transceiver引脚如表6所示,对LX25T,LX45T而言,只有一个GTP Transceiver通道,它的位置是X0Y0,所再Bank号为101;其他信号GTP Transceiver的解释类似.表格 6GTP Transceiver所在Bank编号关于XILINX FPGA中VRP/VRN管脚的使用XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚.VRP/VRN管脚是一对多功能管脚,当一个BANK使用到某些DCI(Digitally Controlled Impedance)接口电平标准时,需要通过该BANK的VRP/VRN管脚接入参考电阻.此时,VRN通过一个参考电阻R上拉到Vcco,VRP通过一个参考电阻R下拉到地.VRP/VRN管脚提供一个参考电压供DCI内部电路使用,DCI内部电路依据此参考电压调整IO输出阻抗与外部参考电阻R匹配.当使用到DCI级联时,仅主BANK(master)需要通过VRP/VRN提供参考电压,从BANK(slave)不需要使用VRP/VRN,从BANK的VRP/VRN管脚可当作普通管脚使用.当VRP/VRN不用于DCI功能时,可用于普通管脚.不需要VRP/VRN外接参考电阻的DCI输出接口电平标准有:HSTL_I_DCIHSTL_III_DCIHSTL_I_DCI_18HSTL_III_DCI_18SSTL2_I_DCISSTL18_I_DCISSTL15_DCI不需要VRP/VRN外接参考电阻的DCI输入接口电平标准有:LVDCI_15LVDCI_18LVDCI_25LVDCI_DV2_15LVDCI_DV2_18LVDCI_DV2_25。

Xilinx FPGA 引脚功能详细介绍.pptx

TCK:I,JTAG 边界扫描时钟。 TDI :I,JTAG 边界扫描数据输入。 TDO:O,JTAG 边界扫描数据输出。 TMS:I,JTAG 边界扫描模式选择 5.保留引脚 NC:N/A, CMPCS_B_2:I,保留,不接或者连 VCCO_2 6.其它 GND: VBATT:RAM内存备份电源。一旦 VCCAUX 应用了,VBATT可以不接;如果 KEY RAM 没有使用,推荐把VBATT 接到 VCCAUX 或者 GND,也可以不接。 VCCAUX:辅助电路电源引脚 VCCINT:内部核心逻辑电源引脚 VCCO_#:输出驱动电源引脚 VFS:I,(LX45 不可用)编程时,key EFUSE 电源供电引脚。当不编程时,这个引脚 的电压应该限制在 GND 到 3.45V;当不使用 key EFUSE 时,推荐把该引脚连接到 VCCAUX 或者 GND,悬空也可以。 RFUSE:I,(LX45 不可用)编程时,key EFUSE 接地引脚。当不编程时或者不使用 key

VREF_#:N/A,这些是输入临界电压引脚。当外部涯

普通引脚。当做作bank 内参考电压时,所有的VRef 都必须被接上。 3.多功能内存控制引脚

M#DQn:I/O,bank# 内 存 控 制 数 据 线 D[15:0] M#LDQS:I/O,bank#内存控制器低数据选通脚 M#LDQSN:I/O,bank#中内存控制器低数据选通 N M#UDQS:I/O,bank#内存控制器高数据选通脚 M#UDQSN:I/O,bank#内存控制器高数据选通 N M#An :O,bank# 内 存 控 制 器 地 址 线 A[14:0] M#BAn:O,bank# 内 存 控 制 bank 地 址 BA[2:0] M#LDM:O,bank#内存控制器低位掩码 M#UDM:O, bank#内存控制器高位掩码 M#CLK:O,bank#内存控制 器时钟 M#CLKN:O,bank#内存控制器时钟,低电平 有效 M#CASN:O,bank#内存控制器低电平有效行地址 选通 M#RASN:O,bank#内存控制器低电平有效列地址 选通 M#ODT:O,bank#内存控制器外部内存的终端信 号控制 M#WE:O,bank#内存控制器写使能 M#CKE: O,bank#内存控制器时钟使能 M#RESET:O,bank#内 存控制器复位

XilinxFPGA引脚功能详细介绍

Xilinx FPGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户 IO 引脚XX 代表某个 Bank 内唯一的一对引脚, Y=[P|N] 代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ 代表在用户 IO 的基本上添加一个或多个以下功能。

Dn: I/O (在 readback 期间),在 selectMAP 或者 BPI 模式下, D[15:0] 配置为数据口。

在从 SelectMAP 读反馈期间,如果 RDWR_B=1 ,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1 : I,在并口模式(SelectMAP/BPI )下,DO 是数据的最低位,在 Bit-serial 模式下, DIN 是信号数据的输入;在 SPI 模式下, MISO 是主输入或者从输出;在 SPI*2 或者 SPI*4 模式下, MISO1 是 SPI 总线的第二位。

D1_MISO2,D2_MISO3 : I,在并口模式下, D1和D2是数据总线的低位;在 SPI*4模式下, MISO2 和MISO3 是 SPI 总线的 MSBs。

An: O, A[25:O] 为 BPI 模式的地址位。

配置完成后,变为用户 I/O 口。

AWAKE : O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非 SUSPEND 模式被使能, AWAKE 被用作用户 I/O。

MOSI_CSI_B_MISO0 : I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B 是一个低电平有效的片选信号;在 SPI*2 或者 SPI*4 的模式下, MISOO 是 SPI 总线的第一位数据。

FCS_B:O, BPI flash 的片选信号。

FOE_B:O, BPI flash 的输出使能信号FWE_B : O, BPI flash 的写使用信号LDC :O, BPI 模式配置期间为低电平HDC:O, BPI 模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_#用户IO引脚XX代表某个Bank内唯一得一对引脚,Y=[P|N]代表对上升沿还就是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO得基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0就是数据得最低位,在Bit—serial模式下,DIN就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1就是SPI总线得第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1与D2就是数据总线得低位;在SPI*4模式下,MISO2与MISO3就是SPI总线得MSBs.An:O,A[25:0]为BPI模式得地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式得状态输出引脚。

SUSPEND就是一个专用引脚,AW A KE就是一个多功能引脚。

除非SUSPEND模式被使能,AW AKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B就是一个低电平有效得片选信号;在SPI*2或者SPI*4得模式下,MISO0就是SPI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FOE_B:O,BPI flash得输出使能信号FWE_B:O,BPIflash 得写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍之答禄夫天创作注:技术交流用,希望对大家有所帮忙。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚酿成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变成用户I/O口。

AWAKE:O,电源保管挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍之欧阳与创编

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP 读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

XilinxFPGA引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍【范本模板】

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_#用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit—serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位.D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AW AKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

XilinxFPGA引脚功能详细介绍.docx

XilinX FPGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P∣N]代表对上升沿还是下降沿敏感,#代表bank 号2. IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O (在readback期间),在SeleCtMAP或者BPI模式下,D[15:0]配置为数据口。

在从SeIeCtMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1 : I ,在并口模式(SeIeCtMAP/BPI )下,D0 是数据的最低位,在Bit-SeriaI模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3 : I ,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBS。

An : O, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE : O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0 : I/O ,在SPI模式下,主输出或者从输入;在SeIeCtMAP模式下,CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOo是SPI总线的第一位数据。

FCS_B: O, BPI flash 的片选信号。

FOE_B : O, BPI flash的输出使能信号FWE_B : O, BPI flash的写使用信号LDC : O,BPI模式配置期间为低电平HDC : O,BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍之答禄夫天创作注:技术交流用,希望对大家有所帮忙。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚酿成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变成用户I/O口。

AWAKE:O,电源保管挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

ilin fpga 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

AlteraFPGA和Xilinx-FPGA-引脚功能详解资料

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

在SPI模式下,为SPI flsah片选信号。

IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。

DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT提供配置数据流。

RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。

HSWAPEN:I,在配置之后和配置过程中,低电平使用上拉。

INIT_B:双向,开漏,低电平表示配置存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC状态。

SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。

CMPMOSI,CMPMISO,CMPCLK:N/A,保留。

M0,M1:I,配置模式选择。

M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。

CCLK:I/O,配置时钟,主模式下输出,从模式下输入。

USERCCLK:I,主模式下,可行用户配置时钟。

GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。

VREF_#:N/A,这些是输入临界电压引脚。

当外部的临界电压不必要时,他可以作为普通引脚。

当做作bank参考电压时,所有的VRef都必须被接上。

3.多功能存控制引脚M#DQn:I/O,bank#存控制数据线D[15:0]M#LDQS:I/O,bank#存控制器低数据选通脚M#LDQSN:I/O,bank#中存控制器低数据选通NM#UDQS:I/O,bank#存控制器高数据选通脚M#UDQSN:I/O,bank#存控制器高数据选通NM#An:O,bank#存控制器地址线A[14:0]M#BAn:O,bank#存控制bank地址BA[2:0]M#LDM:O,bank#存控制器低位掩码M#UDM:O,bank#存控制器高位掩码M#CLK:O,bank#存控制器时钟M#CLKN:O,bank#存控制器时钟,低电平有效M#CASN:O,bank#存控制器低电平有效行地址选通M#RASN:O,bank#存控制器低电平有效列地址选通M#ODT:O,bank#存控制器外部存的终端信号控制M#WE:O,bank#存控制器写使能M#CKE:O,bank#存控制器时钟使能M#RESET:O,bank#存控制器复位4.专用引脚DONE_2:I/O,DONE是一个可选的带有部上拉电阻的双向信号。

作为输出,这个引脚说明配置过程已经完成;作为输入,配置为低电平可以延迟启动。

PROGRAM_B_2:I,低电平异步复位逻辑。

这个引脚有一个默认的弱上拉电阻。

SUSPEND:I,电源保护挂起模式的高电平有效控制输入引脚。

SUSPEND是一个专用引脚,而AWAKE是一个复用引用。

必须通过配置选项使能。

如果挂起模式没有使用,这个引脚接地。

TCK:I,JTAG边界扫描时钟。

TDI:I,JTAG边界扫描数据输入。

TDO:O,JTAG边界扫描数据输出。

TMS:I,JTAG边界扫描模式选择5.保留引脚NC:N/A,CMPCS_B_2:I,保留,不接或者连VCCO_26.其它GND:VBATT:RAM存备份电源。

一旦VCCAUX应用了,VBATT可以不接;如果KEY RAM没有使用,推荐把VBATT接到VCCAUX或者GND,也可以不接。

VCCAUX:辅助电路电源引脚VCCINT:部核心逻辑电源引脚VCCO_#:输出驱动电源引脚VFS:I,(LX45不可用)编程时,key EFUSE电源供电引脚。

当不编程时,这个引脚的电压应该限制在GND到3.45V;当不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,悬空也可以。

RFUSE:I,(LX45不可用)编程时,key EFUSE接地引脚。

当不编程时或者不使用key EFUSE 时,推荐把该引脚连接到VCCAUX或者GND,然而,也可以悬空。

7.GTP 引脚MGTAVCC:收发器混合信号电路电源引脚MGTAVTTTX,MGTAVTTRX:发送,接收电路电源引脚MGTAVTTRCAL:电阻校正电路电源引脚MGTAVCCPLL0,MGTAVCCPLL1:锁相环电源引脚MGTREFCLK0/1P,MGTREFCLK0/1N:差分时钟正负引脚MGTRREF:部校准终端的精密参考电阻引脚MGTRXP[1:0],MGTRXN[1:0]:差分接收端口MGTTXP[1:0],MGTTXN[1:0]:差分发送端口• 1. Spartan-6系列封装概述Spartan-6系列具有低成本、省空间的封装形式,能使用户引脚密度最大化。

所有Spartan-6 LX器件之间的引脚分配是兼容的,所有Spartan-6 LXT器件之间的引脚分配是兼容的,但是Spartan-6 LX和Spartan-6 LXT器件之间的引脚分配是不兼容的。

表格 1Spartan-6系列FPGA封装2. Spartan-6系列引脚分配及功能详述Spartan-6系列有自己的专用引脚,这些引脚是不能作为Select IO使用的,这些专用引脚包括:专用配置引脚,表格2所示 GTP高速串行收发器引脚,表格3所示表格 2Spartan-6 FPGA专用配置引脚注意:只有LX75, LX75T, LX100, LX100T, LX150, and LX150T器件才有VFS、VBATT、RFUSE引脚。

表格 3Spartan-6器件GTP通道数目注意:LX75T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676中封装了8个GTP通道;LX100T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676 和 FG(G)900中封装了8个GTP通道。

如表4,每一种型号、每一种封装的器件的可用IO引脚数目不尽相同,例如对于LX4 TQG144器件,它总共有引脚144个,其中可作为单端IO引脚使用的IO个数为102个,这102个单端引脚可作为51对差分IO使用,另外的32个引脚为电源或特殊功能如配置引脚。

表格 4Spartan6系列各型号封装可用的IO资源汇总表格 5引脚功能详述引脚名方向描述User I/O PinsIO_LXXY_# Input/OutputIO表示这是一个具有输入输出功能的引脚,XX表示该引脚在其Bank的惟一标识,Y表示是差分引脚的P还是N引脚Multi-Function PinsIO_LXXY_ZZZ_# Zzz代表该引脚除IO功能之外的其他功能,Dn Input/Output(duringreadback)在SelectMAP/BPI模式中,D0—D15是用于配置操作的数据引脚,在从SelectMAP的回读阶段,当RDWR_B为低电平时,Dn为输出引脚,在配置过程结束后,该引脚可作为通用IO口使用3. Spartan-6系列GTP Transceiver引脚MGTAVTTTX,MGTAVTTRXN/A TX、RX电路供电电源MGTAVTTRCAL N/A 电阻校准电路供电电源MGTAVCCPLL0MGTAVCCPLL1N/A PLL供电电源MGTREFCLK0/1P Input 正极参考时钟MGTREFCLK0/1N Input 负极参考时钟MGTRREF Input 部校准电路的精密参考电阻MGTRXP[0:1] Input 收发器接收端正极MGTRXN[0:1] Input 收发器接收端负极MGTTXP[0:1] Output 收发器发送端正极MGTTXN[0:1] Output 收发器发送端负极如表6所示,对LX25T,LX45T而言,只有一个GTP Transceiver通道,它的位置是X0Y0,所再Bank号为101;其他信号GTP Transceiver的解释类似。

表格 6GTP Transceiver所在Bank编号关于XILINX FPGA中VRP/VRN管脚的使用XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚。

VRP/VRN管脚是一对多功能管脚,当一个BANK使用到某些DCI(Digitally Controlled Impedance)接口电平标准时,需要通过该BANK的VRP/VRN管脚接入参考电阻。

此时,VRN通过一个参考电阻R上拉到Vcco,VRP通过一个参考电阻R下拉到地。

VRP/VRN管脚提供一个参考电压供DCI部电路使用,DCI部电路依据此参考电压调整IO输出阻抗与外部参考电阻R匹配。