BPSK调制原理

BPSK的调制与解调ppt课件

π/4 -0.707

38 00100110

3π/8 -0.924

11 00001010

π/2 -1.000

1

00000001

5π/8 -0.924

11 00001010

3π/4 -0.707

38 00100110

7π/8 -0.383

79 01001111

π

0.0004

BPSK的Simulink仿真结果

没加噪声的仿真结果:

5

BPSK的Simulink仿真结果

调制信号经过加性高斯白噪声信道之后解调的仿真结果 SNR=0dB时,解调正确:

6

BPSK的Simulink仿真结果

调制信号经过加性高斯白噪声信道之后解调的仿真结果 SNR=-3dB时,解调出现了错码:

7

一种基于BPSK的调制的方框图

2

对数字信号“10111001000111110000”进行BPSK 调制之后,输出的波形如下图所示。

3

2. BPSK(Binary Phase Shift Keying)解调

BPSK解调原理框图 根据BPSK的调制特点,我们只需要用一个周期相 等的正弦信号和调制信号相乘,再经过一个低通滤波 器,就可以在一个周期中得到2个正向的半波信号(对 应数据“0”)或2个负向的半波信号(对应数据 “1”),然后用逻辑电路进行解调。

由于接受到的信号,中间电平可能是上下浮动的,上面

的绝对判断方法在信噪比较低时可能有误判现象,则可以通过 相对比较法来判断,即B1>B2时判“0”, B2>B1时判“1”,即 A[0]-A[12 ]+A[1]-A[13] +A[2]-A[14]……+A[11]-A[23]得到C值,根 据C大于零,输出是“0”,反之,输出为“1”。

BPSK调制解调

一、 主要内容1、简要阐述BPSK 调制解调原理2、用MATLAB 进行仿真,附上仿真源程序和仿真结果,对结果进行分析。

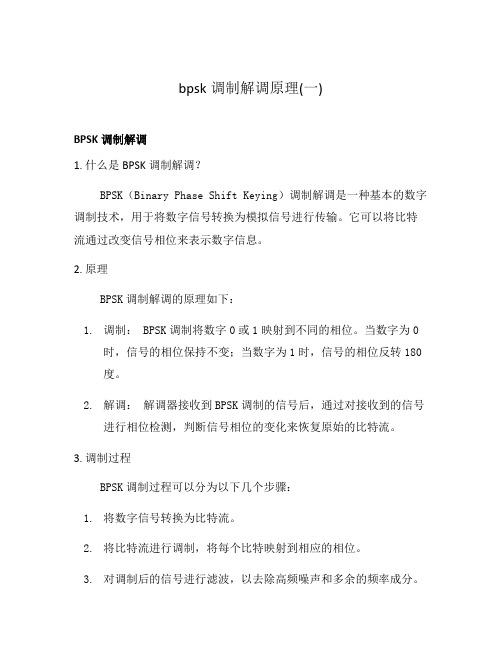

二、 主要原理2.1 BPSK 的调制原理在二进制数字调制中,当正弦载波的相位随二进制数字基带信号离散变化时,则产生二进制移相键控(2PSK )信号。

通常用已调信号载波的0度和180度分别表示二进制数字基带信号的1和0.二进制移相键控信号的时域表达式为t w nT t g a t e c s nn PSK cos )]([)(2-=∑ (式2—1)其中,n a 与2ASK 和2FSK 时的不同,在2PSK 调制中,n a 应选择双极性,即当发送概率为P ,1a =n ,当发送概率为1-P, 1-=n a 。

若g(t)是脉宽为S T 、高度为1的矩形脉冲,则有当发送概率为P 时,)cos()(2t w t e c PSK = (式2—2) 发送概率为1-P 时,)cos(2t w e c PSK -= (式2—3)由(式2—2)和(式2—3)可以看出,当发送二进制符号1时,已调信号)(e 2t PSK 取0度相位,当发送二进制符号为0时,)(e 2t PSK 取180度相位,则有)cos(2n c PSK t w e ϕ+=,其中发送符号1,00=n ϕ,发送符号0,0180=n ϕ。

这种以载波的不同相位直接表示相应二进制数字调制信号的调制方式,称为二进制绝对移向方式。

下面为2PSK 信号调制原理框图2.1所示:图2.1:2PSK 信号的调制原理图(模拟调制方法)利用模拟调制的方法去实现数字式调制,即把数字调制看成是模拟调制的一个特例,把数字基带信号当做模拟信号的特殊情况处理。

图2.2 BPSK 信号时间波形示例2.2 BPSK 解调原理2PSK 信号的解调通常都采用相干解调,解调器原理如图2.3所示,在相干解调过程中需要用到和接收的2PSK 信号同频同相的想干载波。

图2.3:BPSK 相干解调图2.4 BPSK 解调各点时间波形b a d ec在2PSK 相干信号解调过程中,当回复的相干载波产生180度倒相时,解调出的数字基带信号与将发送的数字基带信号正好相反,解调器输出数字基带信号全部错误,这通常称为“倒π”现象。

bpsk 实验报告

bpsk 实验报告BPSK实验报告引言BPSK(Binary Phase Shift Keying)是一种常用的数字调制方式,它将二进制数据转换成相位的变化来进行传输。

在本次实验中,我们将研究BPSK调制的原理、性能以及在通信系统中的应用。

一、BPSK调制原理BPSK调制是一种相位调制方式,它将二进制数据转换成两个相位状态:0对应0°相位,1对应180°相位。

这种相位变化可以通过正弦波进行表示。

在发送端,二进制数据经过调制器转换成相应的相位信号,然后通过信道传输到接收端。

在接收端,接收到的信号经过解调器解调,得到原始的二进制数据。

二、实验步骤1. 准备工作:搭建BPSK调制与解调实验电路。

将信号源与调制器连接,调制器与解调器连接,解调器与示波器连接。

2. 生成二进制数据:通过信号源生成一串二进制数据,作为待调制的信号。

3. BPSK调制:将二进制数据输入到调制器中,调制器将其转换成相应的相位信号。

通过示波器观察调制后的信号波形。

4. 信号传输:将调制后的信号通过信道传输到接收端。

5. BPSK解调:接收端的解调器将接收到的信号解调,得到原始的二进制数据。

通过示波器观察解调后的信号波形。

6. 性能评估:比较解调后的二进制数据与原始数据,计算误码率(Bit Error Rate, BER),并分析BER与信噪比(Signal-to-Noise Ratio, SNR)之间的关系。

三、实验结果与分析通过实验,我们观察到了BPSK调制与解调的波形,得到了解调后的二进制数据。

根据实验结果,我们计算出了不同SNR下的误码率。

通过绘制误码率-SNR曲线,我们可以看到误码率随着SNR的增加而逐渐减小。

这是因为较高的信噪比可以提高信号的质量,减少误码率。

在实际通信系统中,BPSK调制广泛应用于低速率的数字通信系统,特别是在低信噪比环境下。

由于BPSK调制只有两个相位状态,相对于其他调制方式,它的复杂度较低,抗干扰性能较好。

(完整版)BPSKDPSK调制

卫星通信仿真作业BPSK调制/解调系统及性能分析1、实验原理1.1 BPSK调制原理BPSK(binary phase shift keying)二进制移相键控,作为一种数字调制方式,用已调信号载波的0°和180°分别表示二进制数字基带信号的1和0。

BPSK信号的时域表达式为e BPSK=[∑a n g(t−nT s)]cosωc tn其中的a n为双极性码,取值为±1。

这样的话,当发送的码元为+1时,输出波形的初始相位为0;而当发送码元为-1时,输出波形的初始相位为180°。

1.2 BPSK解调原理BPSK解调有两种方式,一种是相干解调,一种是非相干解调,即差分解调。

1.2.1 相干解调相干解调的基本原理是将BPSK调制信号直接与载波进行相乘,然后通过低通滤波器进行滤波,最终进行抽样判决即可。

1.2.2 差分解调差分解调不能直接应用与BPSK,它是对DPSK调制的一种解调方式。

而要进行差分解调,首先对输入信源进行DPSK调制。

要进行DPSK调制,首先要对输入码元进行码形变换,然后对变换后的码元进行BPSK 调制即可。

而对输入码元进行码形变换就是将输入的绝对码变换为相对码。

它们之间的关系可由公式导出ân+1=ân⨁a n其中a n为原信源码元,ân为差分编码后的变换码元。

差分解调的过程是将DPSK调制后的波形与它做一个码元宽度时间延迟后的波形进行相乘,然后通过低通滤波器进行滤波,最终进行抽样判决。

1.3 BPSK调制解调系统整体框图1.4 DPSK调制解调系统整体框图输入码元2、 实验过程2.1 BPSK 系统的调制/解调全过程 2.1.1 参数设定 在对BPSK 系统调制解调全过程的仿真时,设定如下参数: 码元长度:10 采样率:100倍码元速率,也就是一个码元采样100个点 信号比:7dB (也就是噪声的增益为0.1) 波形成型滤波器参数:使用升余弦滤波器,滚降系数0.5。

bpsk调制原理

bpsk调制原理bpsk调制原理与模拟通信系统相比,数字调制和解调同样是通过某种方式,将基带信号的频谱由一个频率位置搬移到另一个频率位置上去。

不同的是,数字调制的基带信号不是模拟信号而是数字信号。

在大多数情况下,数字调制是利用数字信号的离散值去键控载波。

对载波的幅度、频率或相位进行键控,便可获得ASK、FSK、PSK等。

这三种数字调制方式在抗干扰噪声能力和信号频谱利用率等方面,以相干PSK的性能最好,目前已在中、高速传输数据时得到广泛应用。

2PSK系统的调制部分框图如下图所示2PSK/BPSK调制部分框图1、M序列发生器实际的数字基带信号是随机的,为了实验和测试方便,一般都是用M序列发生器产生一个伪随机序列来充当数字基带信号源。

按照本原多项式f(x)=X5+X3+1组成的五级线性移位寄存器,就可得到31位码长的M序列。

码元定时与载波的关系可以是同步的,以便清晰观察码元变化时对应调制载波的相应变化;也可以是异步的,因为实际的系统都是异步的,码元速率约为1Mbt/s。

2、相对移相和绝对移相移相键控分为绝对移相和相对移相两种。

以未调载波的相位作为基准的相位调制叫作绝对移相。

以二进制调相为例,取码元为“1”时,调制后载波与未调载波同相;取码元为“0”时,调制后载波与未调载波反相;“1”和“0”时调制后载波相位差1800。

绝对移相的波形如下图所示。

绝对移相的波形示意图在同步解调的PSK系统中,由于收端载波恢复存在相位含糊的问题,即恢复的载波可能与未调载波同相,也可能反相,以至使解调后的信码出现“0”、“1”倒置,发送为“1”码,解调后得到“0”码;发送为“0”码,解调后得到“1”码。

这是我们所不希望的,为了克服这种现象,人们提出了相对移相方式。

相对移相的调制规律是:每一个码元的载波相位不是以固定的未调载波相位作基准的,而是以相邻的前一个码元的载波相位来确定其相位的取值。

例如,当某一码元取“1”时,它的载波相位与前一码元的载波同相;码元取“0”时,它的载波相位与前一码元的载波反相。

BPSK调制原理

BPSK调制原理原理:2DPSK ⽅式是⽤前后相邻码元的载波相对相位变化来表⽰数字信息。

假设前后相邻码元的载波相位差为??,可定义⼀种数字信息与??之间的关系为则⼀组⼆进制数字信息与其对应的2DPSK 信号的载波相位关系如下表所⽰数字信息与?? 之间的关系也可以定义为2DPSK 信号调制过程波形如图1所⽰。

图1 2DPSK 信号调制过程波形可以看出,2DPSK 信号的实现⽅法可以采⽤:⾸先对⼆进制数字基带信号进⾏差分编码,将绝对码表⽰⼆进制信息变换为⽤相对码表⽰⼆进制信息,然后再进⾏绝对调相,从⽽产⽣⼆进制差分相位键控信号。

2DPSK 信号调制器原理图如图2所⽰。

0,01φπ??=?表⽰数字信息“”,表⽰数字信息“”()()1 1 0 1 0 0 1 102DPSK 0 0 0 0 0 00 0 0 0ππππππππππ⼆进制数字信息:信号相位:或0,10φπ??=?表⽰数字信息“”,表⽰数字信息“”绝对码相对码载波DP SK 信号101100101 0 0 1 0 1 1 0 2开关电路图2 2DPSK 信号调制器原理图其中码变换即差分编码器如图3所⽰。

在差分编码器中:{a n }为⼆进制绝对码序列,{d n }为差分编码序列。

D 触发器⽤于将序列延迟⼀个码元间隔,在SystemView 中此延迟环节⼀般可不采⽤D 触发器,⽽是采⽤操作库中的“延迟图符块”。

⼆进制差分相位键控(2DPSK )的解调1、实验⽬的:(1)了解2DPSK 系统解调的电路组成、⼯作原理和特点;(2)掌握2DPSK 系统解调过程信号波形的特点;(3)熟悉系统中信号功率谱的特点。

2、实验内容:以2DPSK 作为系统输⼊信号,码速率Rb =10kbit/s 。

(1)采⽤相⼲解调法实现2DPSK 的解调,分别观察系统各点波形。

(2)获取主要信号的功率谱密度。

3、实验原理:相⼲解调法:2DPSK 信号可以采⽤相⼲解调⽅式(极性⽐较法),对2DPSK 信号进⾏相⼲解调,恢复出相对码,再通过码反变换器变换为绝对码,从⽽恢复出发送的⼆进制数字图3差分编码器信息。

bpsk调制 升余弦 相关解调

BPSK调制、升余弦和相关解调是数字通信中常见的调制和解调技术。

本文将从理论和实际应用的角度介绍这三个主题,以帮助读者更好地理解和应用这些技术。

一、BPSK调制1. BPSK调制是一种基带调制技术,全称为二进制相移键控调制(Binary Phase Shift Keying)。

它通过改变载波信号的相位来传输数字信息。

具体来说,当数字为0时,载波信号的相位不变;当数字为1时,载波信号的相位反转180度。

这样就可以在相位上进行二进制编码。

2. BPSK调制的优点是简单直观,适用于频谱效率要求不高的情况。

在实际应用中,BPSK调制常用于低速数据传输、卫星通信和短波通信等场景。

3. 在无线传感网中,由于节点之间的距离较近、数据传输速率较低,可以采用BPSK调制来实现简单可靠的通信。

二、升余弦滚降滤波器1. 在数字通信中,为了尽可能减小传输信号的带宽,减小信道间的干扰,常常采用升余弦滚降滤波器(R本人sed Cosine Filter)来进行信号的滤波和调制。

2. 升余弦滚降滤波器的频率响应在频率为0附近有较好的抑制作用,可以有效地控制信号的带宽。

其滚降特性也能够减小信号在频率间隔内的干扰,提高信号的抗干扰能力。

3. 实际应用中,升余弦滚降滤波器常用于QPSK、16QAM等多种调制方式,尤其适用于要求频谱效率高、抗干扰能力强的场景。

三、相关解调1. 相关解调是指在接收端利用发送端已知的信号来解调接收到的信号。

通过计算接收信号和已知信号的相关性,可以还原发送信号。

2. 相关解调在数字通信中有着广泛的应用,特别是在多路径传输、信道干扰较大的高速数据传输场景中效果明显。

相对于其他解调方法,相关解调在抗噪声和多径干扰方面有明显的优势。

3. GPS定位系统中采用的CDMA技术就采用了相关解调的原理,来实现对传输信号的解调和定位。

BPSK调制、升余弦滚降滤波器和相关解调是数字通信领域中重要的技术手段,它们在不同的场景中发挥着重要的作用。

《移动通信--BPSK调制与解调》报告

《移动通信--BPSK调制与解调》报告《移动通信BPSK 调制与解调》报告在当今的信息时代,移动通信技术的发展日新月异,为人们的生活和工作带来了极大的便利。

其中,BPSK(Binary Phase Shift Keying,二进制相移键控)调制与解调技术作为一种重要的数字通信技术,在移动通信中发挥着关键作用。

一、BPSK 调制的基本原理BPSK 是一种最简单的相移键控方式。

在 BPSK 中,通常用二进制数字“0”和“1”来控制载波的相位。

当数字信号为“0”时,载波的相位为0 度;当数字信号为“1”时,载波的相位为 180 度。

从数学角度来看,假设发送的二进制数字序列为{an},其中 an 取值为 0 或 1,载波信号为Acos(2πfct),那么 BPSK 调制后的信号可以表示为:s(t) =Acos(2πfct +πan)通过这种方式,将数字信息加载到载波信号的相位上,实现了信号的调制。

二、BPSK 调制的实现方式在实际应用中,BPSK 调制可以通过多种方式实现。

一种常见的方法是使用乘法器。

将数字信号与一个正弦载波相乘,得到调制后的信号。

另一种实现方式是基于数字电路,通过逻辑门和计数器等组件来生成 BPSK 调制信号。

这种方式在数字通信系统中应用广泛,具有稳定性高、易于集成等优点。

三、BPSK 解调的基本原理解调是从接收到的已调信号中恢复出原始数字信号的过程。

BPSK的解调通常采用相干解调的方法。

相干解调需要在接收端产生一个与发送端载波同频同相的本地载波。

接收到的 BPSK 信号与本地载波相乘,然后通过低通滤波器滤除高频分量,再进行抽样判决,恢复出原始的数字信号。

四、BPSK 解调的实现过程首先,接收到的信号与本地载波相乘,得到:r(t) = s(t) × cos(2πfct +φ)其中,φ 为本地载波与发送端载波的相位差。

经过乘法运算后,得到:r(t) = 05A1 +cos(2πfct +πan +φ 2πfct)= 05A1 +cos(πan +φ)通过低通滤波器后,滤除高频分量,得到:r'(t) = 05A1 +cos(πan +φ)最后,对 r'(t) 进行抽样判决。

bpsk调制及解调原理实验报告

bpsk调制及解调原理实验报告BPSK 调制及解调原理实验报告一、实验目的本实验旨在深入理解二进制相移键控(BPSK)调制及解调的原理,通过实际操作和观测,掌握 BPSK 信号的产生、传输和恢复过程,分析其性能特点,并探讨相关参数对系统性能的影响。

二、实验原理(一)BPSK 调制原理BPSK 是一种最简单的相移键控方式,它使用两个相位(通常为 0和π)来表示二进制数字信息。

在 BPSK 中,当输入的二进制数字为“0”时,调制后的载波相位为 0;当输入的二进制数字为“1”时,调制后的载波相位为π。

假设输入的二进制序列为{an},载波信号为cos(ωct),则 BPSK 调制后的信号可以表示为:s(t) =an cos(ωct +φn)其中,当 an = 0 时,φn = 0;当 an = 1 时,φn =π。

(二)BPSK 解调原理BPSK 的解调通常采用相干解调的方法。

相干解调需要一个与发送端同频同相的本地载波。

接收到的 BPSK 信号与本地载波相乘后,通过低通滤波器滤除高频分量,再进行抽样判决,恢复出原始的二进制数字信息。

具体的解调过程如下:接收信号 r(t) = s(t) + n(t) (其中 n(t) 为加性高斯白噪声)与本地载波cos(ωct) 相乘得到:r(t) cos(ωct) =an cos(ωct +φn) +n(t) cos(ωct)= 1/2 an 1 +cos(2ωct +φn) +n(t) cos(ωct)经过低通滤波器后,滤除2ωc 频率成分,得到:1/2 an +n(t) cos(ωct)对其进行抽样判决,若抽样值大于 0,则判决为“0”;若抽样值小于0,则判决为“1”。

三、实验内容与步骤(一)实验内容1、产生 BPSK 调制信号2、加入高斯白噪声3、进行相干解调4、分析不同信噪比下的误码率性能(二)实验步骤1、利用编程语言(如 MATLAB)生成随机的二进制数字序列作为输入信号。

BPSK调制解调及误码率的计算

BPSK调制解调及误码率的计算BPSK (Binary Phase Shift Keying) 是一种基本的数字调制技术,常用于数字通信系统中。

它通过将数字信号映射为相位上的两个值来进行调制,并使用相干解调器进行解调。

本文将介绍BPSK调制解调的原理以及如何计算误码率。

1.BPSK调制原理:在BPSK调制中,每个二进制位(0或1)被映射为两个可能的相位值:0对应于0度相位,1对应于180度相位。

这种相位差可以通过正弦和余弦函数来实现。

-二进制信息序列被输入到调制器中。

-调制器将二进制位转换为相位值,0对应于0度相位,1对应于180度相位。

-经过调制的信号通过信道传输。

2.BPSK解调原理:BPSK解调器的任务是将传输信号恢复为原始的二进制序列。

当信号通过信道传输后,可能会受到噪声和其他干扰的影响,从而导致误码的产生。

BPSK解调的过程如下:-接收到的信号经过信道传输后,会受到噪声和其他干扰的影响,使信号的相位发生随机的偏移。

-解调器使用相干解调的方法测量接收信号的相位。

-根据测量到的相位值,解调器将信号恢复为原始的二进制序列。

3.误码率的计算方法:误码率是衡量通信系统性能的重要指标,它表示在传输过程中发生误码的概率。

对于BPSK调制,误码率的计算可以通过理论分析或仿真实验进行。

理论分析方法:在BPSK调制中,误码率的理论计算可以使用误码率表达式得到。

对于理想的信道,没有噪声和干扰,误码率的表达式为:P_e = Q(sqrt(2*Eb/N0))其中,Eb/N0表示信噪比,Q(x)为高斯函数。

对于有噪声和干扰的实际信道,可以根据信号接收的信噪比进行实际误码率的计算。

仿真实验方法:使用计算机仿真软件,可以模拟BPSK调制解调系统,并通过对大量的二进制序列进行模拟传输和解调,统计接收到的误码数量来计算误码率。

误码率的计算通过测量接收信号中发生错误的比特数与总传输的比特数之比得到。

它通常以对数的形式表示,即以dB为单位。

bpsk正交iq调制

bpsk正交iq调制

BPSK(二进制相移键控)正交IQ调制是一种数字调制技术,常

用于无线通信系统中。

在BPSK调制中,数字比特流被映射到正弦波

的相位上,而正交IQ调制则是在两个正交的载波上分别进行BPSK

调制。

这种调制技术的原理和应用可以从多个角度来进行解释:

1. 原理,BPSK正交IQ调制使用两个正交的载波信号,通常分

别为正弦信号和余弦信号。

将输入的数字比特流分别映射到这两个

正交载波上,形成两路信号。

这样可以实现在相同频谱上同时传输

两路独立的信息,从而提高频谱利用率。

2. 优点,BPSK正交IQ调制具有频谱利用率高、抗干扰能力强、易于实现等优点。

由于正交的特性,可以在有限的频谱内传输更多

的信息,提高了信道的利用率。

同时,正交调制使得信号在传输过

程中更加稳定,抗干扰能力更强。

3. 应用,BPSK正交IQ调制广泛应用于数字通信系统中,特别

是无线通信系统中。

例如,在Wi-Fi、蓝牙、LTE和5G等无线通信

标准中都采用了BPSK正交IQ调制技术。

它能够有效地提高数据传

输速率和系统的可靠性,适用于各种宽带通信系统。

总的来说,BPSK正交IQ调制是一种重要的数字调制技术,通过将数字比特流映射到正交载波上,实现了高效的数据传输和频谱利用,广泛应用于无线通信系统中。

bpsk调制原理

bpsk调制原理2011-08-18 08:18:59 来源:互联网bpsk调制原理与模拟通信系统相比,数字调制和解调同样是通过某种方式,将基带信号的频谱由一个频率位置搬移到另一个频率位置上去。

不同的是,数字调制的基带信号不是模拟信号而是数字信号。

在大多数情况下,数字调制是利用数字信号的离散值去键控载波。

对载波的幅度、频率或相位进行键控,便可获得ASK、FSK、PSK等。

这三种数字调制方式在抗干扰噪声能力和信号频谱利用率等方面,以相干PSK的性能最好,目前已在中、高速传输数据时得到广泛应用。

2PSK系统的调制部分框图如下图所示2PSK/BPSK调制部分框图1、M序列发生器实际的数字基带信号是随机的,为了实验和测试方便,一般都是用M序列发生器产生一个伪随机序列来充当数字基带信号源。

按照本原多项式f(x)=X5+X3+1组成的五级线性移位寄存器,就可得到31位码长的M序列。

码元定时与载波的关系可以是同步的,以便清晰观察码元变化时对应调制载波的相应变化;也可以是异步的,因为实际的系统都是异步的,码元速率约为1Mbt/s。

2、相对移相和绝对移相移相键控分为绝对移相和相对移相两种。

以未调载波的相位作为基准的相位调制叫作绝对移相。

以二进制调相为例,取码元为“1”时,调制后载波与未调载波同相;取码元为“0”时,调制后载波与未调载波反相;“1”和“0”时调制后载波相位差1800。

绝对移相的波形如下图所示。

绝对移相的波形示意图在同步解调的PSK系统中,由于收端载波恢复存在相位含糊的问题,即恢复的载波可能与未调载波同相,也可能反相,以至使解调后的信码出现“0”、“1”倒置,发送为“1”码,解调后得到“0”码;发送为“0”码,解调后得到“1”码。

这是我们所不希望的,为了克服这种现象,人们提出了相对移相方式。

相对移相的调制规律是:每一个码元的载波相位不是以固定的未调载波相位作基准的,而是以相邻的前一个码元的载波相位来确定其相位的取值。

bpsk调制过程

bpsk调制过程BPSK调制过程BPSK(Binary Phase Shift Keying)是一种基本的数字调制方式,它在通信系统中被广泛应用。

在BPSK调制过程中,数字信号被转换为相位状态,通过改变信号的相位来传输信息。

本文将详细介绍BPSK调制过程的原理及其实现。

一、BPSK调制原理BPSK调制通过改变信号的相位来传输信息。

它使用两个相位状态来表示数字信号的两个不同值(通常为0和1)。

其中,一个相位状态表示数字0,另一个相位状态表示数字1。

具体而言,BPSK调制将数字0映射到相位为0的载波信号,将数字1映射到相位为π的载波信号。

二、BPSK调制过程BPSK调制过程包括信号源、载波发生器、相位调制器和发送天线等组成。

1. 信号源:信号源产生数字信号,通常为二进制序列。

2. 载波发生器:载波发生器产生载波信号,其频率与信号源频率相同。

3. 相位调制器:相位调制器将信号源产生的数字信号转换为相位状态。

当数字信号为0时,相位调制器将载波信号的相位设置为0;当数字信号为1时,相位调制器将载波信号的相位设置为π。

4. 发送天线:发送天线将经过相位调制的载波信号发送出去,进入信道进行传输。

三、BPSK解调原理在接收端,BPSK解调器将接收到的信号与本地产生的相位参考信号进行比较,从而确定信号的相位状态,进而恢复出数字信号。

1. 接收天线:接收天线接收到经过信道传输后的信号。

2. 相位参考信号:接收端使用本地产生的相位参考信号,与接收到的信号进行比较。

3. 相位差检测器:相位差检测器比较接收到的信号与本地产生的相位参考信号之间的相位差,从而确定信号的相位状态。

4. 解调器:解调器将确定的相位状态转换为数字信号,完成信号的解调过程。

四、BPSK调制的特点和应用BPSK调制的特点有以下几点:1. 抗噪声性能好:BPSK调制仅通过改变信号相位来传输信息,相位的改变对信号的幅度没有影响,因此在噪声环境下具有较好的抗干扰性能。

bpsk调制解调原理相关书籍

标题:深入理解BPSK调制解调原理:相关书籍推荐一、BPSK调制解调原理概述在数字通信领域,二进制相移键控(BPSK)调制解调技术是一种常见的调制解调方式。

它通过改变载波的相位来表示数字信号的“0”和“1”,在无线通信、卫星通信以及光通信等领域中得到广泛应用。

深入理解BPSK调制解调原理对于理解数字通信系统以及解决实际工程问题具有重要意义。

二、相关书籍推荐1. 《数字通信原理》(作者:李文光)该书系统地介绍了数字调制技术,包括BPSK调制解调原理在内的多种调制方式。

书中详细阐述了BPSK调制原理、解调原理、误码率性能分析等内容,适合作为数字通信专业的教材使用,也适合工程技术人员参考。

2. 《数字通信系统设计与应用》(作者:杨宗坤)该书介绍了数字通信系统的基本原理、技术规格以及应用场景。

其中对于BPSK调制解调原理进行了深入分析,结合实际案例进行讲解,对于理解BPSK调制解调技术有很好的辅助作用。

3. 《现代数字通信》(作者:周文杰)本书系统介绍了现代数字通信技术,其中有专门章节对BPSK调制解调原理进行了详细介绍。

该书理论与实践并重,适合具有一定数字通信基础的读者阅读,对于BPSK调制解调原理的理解和应用具有很好的指导意义。

三、选择适合自己的书籍阅读以上推荐的书籍时,读者可以根据自身的专业水平和兴趣爱好进行选择。

对于初学者来说,建议先选择针对初学者编写的教材,如《数字通信原理》;对于已经有一定通信基础的人员,可以选择更深入的专业书籍进行学习。

四、其他学习资源推荐除了书籍之外,还可以通过网络课程、学术论文、专业全球信息湾等途径进行学习。

国内外许多知名大学都会开设相关的数字通信课程,通过网络评台可以观看这些课程的录像,并进行学习与交流。

各种学术期刊和专业全球信息湾上也会有大量的相关论文和技术资料可供参考。

五、结语BPSK调制解调技术是数字通信领域的重要内容之一,深入理解其原理对于相关领域的研究和应用至关重要。

bfsk调制解调原理

BPSK调制解调原理BPSK(Binary Phase Shift Keying)是一种数字调制方式,它通过改变载波的相位来传输信息。

在BPSK中,二进制信息(0和1)通过将载波相位改变180度来编码。

解调时,通过检测接收信号的相位,确定二进制信息的值。

以下是BPSK调制解调原理的详细介绍:一、BPSK调制原理BPSK调制是将二进制数据序列通过改变载波的相位来传输。

在BPSK中,二进制数据序列(通常表示为{-1, +1}或{0, 1})通过与一个固定频率的载波信号相乘来调制。

载波信号是一个正弦波,其相位可以在0度和180度之间变化。

根据二进制数据序列的值,载波信号的相位被改变180度。

当数据为1时,载波相位为180度;当数据为-1时,载波相位为0度。

BPSK调制原理可以用以下数学公式表示:S(t) = A * cos(2πfct + πb)如果b=0S(t) = A * sin(2πfct + πb)如果b=1其中,S(t)是已调信号,A是幅度,fc是载波频率,b是二进制数据序列的值。

通过改变载波的相位,我们可以将二进制数据序列传输到接收端。

在传输过程中,信号可能会受到噪声和干扰的影响,但只要信号的幅度足够大,我们就可以在接收端正确地检测到信号的相位变化。

二、BPSK解调原理BPSK解调是将接收到的已调信号还原为原始的二进制数据序列的过程。

在BPSK解调中,我们首先需要从已调信号中提取出载波信号的相位信息,然后根据相位信息确定二进制数据的值。

BPSK解调通常使用相干解调或非相干解调方法。

相干解调需要使用与发送端相同的载波信号进行解调,而非相干解调则不需要。

在实际应用中,非相干解调方法通常更为简单且可靠。

1. 相干解调相干解调需要使用与发送端相同的载波信号进行解调。

首先,接收到的已调信号与本地产生的载波信号相乘,得到一个正弦波信号。

然后,通过低通滤波器滤除高频分量,得到一个直流分量。

最后,根据直流分量的极性判断二进制数据的值。

bpsk调制解调原理(一)

bpsk调制解调原理(一)BPSK调制解调1. 什么是BPSK调制解调?BPSK(Binary Phase Shift Keying)调制解调是一种基本的数字调制技术,用于将数字信号转换为模拟信号进行传输。

它可以将比特流通过改变信号相位来表示数字信息。

2. 原理BPSK调制解调的原理如下:1.调制: BPSK调制将数字0或1映射到不同的相位。

当数字为0时,信号的相位保持不变;当数字为1时,信号的相位反转180度。

2.解调:解调器接收到BPSK调制的信号后,通过对接收到的信号进行相位检测,判断信号相位的变化来恢复原始的比特流。

3. 调制过程BPSK调制过程可以分为以下几个步骤:1.将数字信号转换为比特流。

2.将比特流进行调制,将每个比特映射到相应的相位。

3.对调制后的信号进行滤波,以去除高频噪声和多余的频率成分。

4. 解调过程BPSK解调过程可以分为以下几个步骤:1.接收到调制后的信号。

2.对接收到的信号进行相位检测,判断信号相位的变化。

3.根据相位的变化确定每个比特的数值,恢复原始的比特流。

5. 优点与应用BPSK调制解调具有以下优点:•抗噪声能力强:由于BPSK调制只有两个相位,相位判断更容易,因此在噪声环境下具有较好的性能。

•简单实现:BPSK调制解调电路相对简单,容易实现和部署。

BPSK调制解调广泛应用于以下领域:•无线通信系统:BPSK是许多无线通信标准中的关键调制方式,如802.11系列(Wi-Fi)、蓝牙等。

•传感器网络:BPSK被用于传感器网络中的数据传输,如环境监测、智能建筑等。

•卫星通信:BPSK可以通过卫星传输数据,广泛应用于卫星通信领域。

6. 总结BPSK调制解调是一种基本的数字调制技术,通过改变信号相位来表示数字信息。

它具有抗噪声能力强、简单实现等优点,在无线通信、传感器网络、卫星通信等领域有广泛的应用。

理解BPSK调制解调的原理对于深入研究数字通信系统至关重要。

7. BPSK调制解调的性能分析BPSK调制解调的性能可以通过误码率(Bit Error Rate,BER)来评估。

BPSK原理

BPSK是PSK系列中最简单的一种。

它是使用两个相位差180°且正交的信号表示0及1的资料。

它在坐标图放置的点并无特别设计,两点皆放在实数轴,分别在0°的点及180°的点。

这种系统是在PSK系列中抗噪声能力(SNR)是最佳的,在传送过程中即使严重失真,在解调时仍可尽量避免错误的判断。

调制原理分析相移键控是利用载波的相位变化来传递数字信息,而振幅和频率保持不变。

在BPSK中,通常用初始相位0或π分别表示二进制的‘0’和‘1’。

因此,BPSK信号的时域表达式为::公式包含0和π两个相位。

其中代表0,代表1。

由于表示信号的两种码元的波形相同,极性相反,故BPSK信号一般可以表述为一个双极性全占空(100% duty ratio)矩形脉冲序列于一个正弦载波的相乘,即其中,这里,g(t)脉冲宽度为T s的单个矩形脉冲,而a n得统计特性为:即发送二进制符号位‘0’时(a n取+1),e BPSK (t)取0相位;发送二进制符号为‘1’时(a n取-1),e BPSK (t)取π相位。

这种以载波的不同相位直接去表示响应的二进制数字信号的调制方式,称为二进制绝对相移调制(BPSK)调制原理框图如图1.1所示:1.1调制原理框图(采用2KHz信号cos(2*2000*t)作为载波)典型波形图:图1.2 发送码元为1 0 0 1 1的BPSK波形解调原理分析:BPSK信号的解调方法是相干解调法。

由于PSK信号本身就是用相位传递信息的,所以在接受端必须利用信号的相位信息,故采用相干解调法来解调信号。

BPSK解调原理框图如1.2所示:1.3 BPSK解调原理框图(采用2KHz信号cos(2*2000*t)作为载波)给出了一种BPSK信号想干接受设备原理框图。

图中经过带通滤波的信号在相乘器与本地载波相乘,在相干解调中,如何得到与接收的BPSK信号同频同相的相干载波是关键,然后用低通滤波器去除高频分量,再进行抽样判决,判决器是按极性进行判决,得到最终的二进制信息。

BPSK调制解调

一、主要内容1、简要阐述 BPSK调制解调原理2、用 MATLAB进行仿真,附上仿真源程序和仿真结果,对结果进行分析。

二、主要原理2.1 BPSK 的调制原理在二进制数字调制中,当正弦载波的相位随二进制数字基带信号离散变化时,则产生二进制移相键控( 2PSK)信号。

通常用已调信号载波的0 度和 180度分别表示二进制数字基带信号的 1 和 0. 二进制移相键控信号的时域表达式为e2 PSK (t) [ a n g(t nT s )] cosw c t(式 2—1)n其中, a n与 2ASK和 2FSK时的不同,在 2PSK调制中, a n应选择双极性,即当发送概率为 P, a n1,当发送概率为1-P, a n 1 。

若g(t)是脉宽为 T S、高度为1的矩形脉冲,则有当发送概率为 P 时,e2PSK ( )cos()(式—)t w c t22发送概率为 1-P 时,e2PSK cos()(式2—)w c t3由(式 2—2)和(式 2—3)可以看出,当发送二进制符号 1 时,已调信号 e2PSK (t)取 0度相位,当发送二进制符号为0 时, e2PSK (t) 取180 度相位,则有e2 PSK cos(w c t n ),其中发送符号1,n 00,发送符号0,n 1800。

这种以载波的不同相位直接表示相应二进制数字调制信号的调制方式,称为二进制绝对移向方式。

下面为2PSK信号调制原理框图2.1 所示:e2 PSK (t )S(t)码型变换乘法器cos(w c t)图 2.1:2PSK 信号的调制原理图(模拟调制方法)利用模拟调制的方法去实现数字式调制,即把数字调制看成是模拟调制的一个特例,把数字基带信号当做模拟信号的特殊情况处理。

10011tT S图 2.2 BPSK 信号时间波形示例2.2 BPSK 解调原理2PSK信号的解调通常都采用相干解调,解调器原理如图 2.3 所示,在相干解调过程中需要用到和接收的2PSK信号同频同相的想干载波。

基于FPGA的BPSK调制解调器设计与实现

基于FPGA的BPSK调制解调器设计与实现随着通信技术的不断发展,调制解调器在无线通信系统中扮演着重要角色。

本文将探讨基于FPGA的二进制相移键控(BPSK)调制解调器的设计与实现。

BPSK调制技术是一种数字调制技术,常用于低速率无线通信系统,在诸多应用中被广泛采用。

一、调制解调器设计原理1. BPSK调制原理BPSK调制是一种基于相移调制的调制技术,其原理是将数字比特流与载波信号相位相互关联。

对于二进制输入信号,0表示正相位,1表示负相位。

因此,BPSK调制技术将数字信号转换为载波信号的相位,实现信号的调制。

2. BPSK解调原理BPSK解调过程是调制的逆过程。

通过比较解调器接收到的信号相位与参考相位,可以恢复出原始的数字信号。

解调原理可以通过相位差检测、锁相环等技术实现。

二、FPGA在BPSK调制解调器中的应用FPGA是一种可编程逻辑器件,具有并行处理能力和灵活的硬件资源配置。

在BPSK调制解调器设计中,FPGA可以承担信号处理、调制解调等任务,提高系统性能和灵活性。

1. FPGA的优势FPGA具有高度的并行性和灵活性,可以快速实现信号处理算法。

通过灵活配置硬件资源,可以满足不同调制解调算法的需求。

此外,FPGA还具有低功耗、低延迟和容错性强等优势。

2. FPGA的设计流程FPGA的设计流程包括系统建模、算法设计、逻辑设计、综合与布局布线、仿真验证等步骤。

在BPSK调制解调器设计中,首先需要将系统和算法进行建模,然后通过逻辑设计实现相应硬件电路,最后进行综合布局布线和仿真验证。

三、基于FPGA的BPSK调制解调器设计实现步骤1. 系统建模与算法设计根据BPSK调制解调器的原理,将系统进行建模,并设计相应的算法来实现调制和解调过程。

这一步骤需要考虑信号的采样率、滤波器设计、相位恢复等关键问题。

2. 逻辑设计与实现将系统建模和算法设计转化为相应的硬件电路。

利用FPGA的硬件资源进行逻辑设计,并将信号处理算法转化为硬件描述语言(如VHDL或Verilog)进行实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

原理:

2DPSK 方式是用前后相邻码元的载波相对相位变化来表示数字信息。

假设前后相邻码元的载波相位差为∆ϕ,可定义一种数字信息与∆ϕ之间的关系为

则一组二进制数字信息与其对应的2DPSK 信号的载波相位关系如下表所示

数字信息与∆ϕ 之间的关系也可以定义为

2DPSK 信号调制过程波形如图1所示。

图1 2DPSK 信号调制过程波形

可以看出,2DPSK 信号的实现方法可以采用:首先对二进制数字基带信号进行差分编码,将绝对码表示二进制信息变换为用相对码表示二进制信息,然后再进行绝对调相,从而产生二进制差分相位键控信号。

2DPSK 信号调制器原理图如图2所示。

0,01φπ⎧∆=⎨

⎩表示数字信息“”,表示数字信息“”

()(

)1 1 0 1 0 0 1 10

2DPSK 0 0 0 0 0 00 0 0 0

ππππππ

ππππ二进制数字信息:信号相位:或0,10φπ⎧∆=⎨

⎩表示数字信息“”

,表示数字信息“”

绝对码

相对码

载波

DP SK 信号10

1100101 0 0 1 0 1 1 0 2

开关电路

图2 2DPSK 信号调制器原理图

其中码变换即差分编码器如图3所示。

在差分编码器中:{a n }为二进制绝对码序列,{d n }为差分编码序列。

D 触发器用于将序列延迟一个码元间隔,在SystemView 中此延迟环节一般可不采用D 触发器,而是采用操作库中的“延迟图符块”。

二进制差分相位键控(2DPSK )的解调

1、实验目的:

(1)了解2DPSK 系统解调的电路组成、工作原理和特点; (2)掌握2DPSK 系统解调过程信号波形的特点; (3)熟悉系统中信号功率谱的特点。

2、实验内容:

以2DPSK 作为系统输入信号,码速率Rb =10kbit/s 。

(1)采用相干解调法实现2DPSK 的解调,分别观察系统各点波形。

(2)获取主要信号的功率谱密度。

3、实验原理:

相干解调法:

2DPSK 信号可以采用相干解调方式(极性比较法),对2DPSK 信号进行相干解调,恢复出相对码,再通过码反变换器变换为绝对码,从而恢复出发送的二进制数字

图3差分编码器

信息。

解调器原理图和解调过程各点时间波形如图13(a)、(b)所示:

其中码反变换器即差分译码器组成如图14所示。

在差分译码器中:{ˆn

d }为差分编码序列,{ˆn a

}为差分译码序列。

D 触发器用于将序列延迟一个码元间隔,在SystemView 中此延迟环节一般可不使用D 触发器,而是使用操作库中的“延迟图符块

”。

4、 系统组成、图符块参数设置及仿真结果:

相干解调法:

相干解调法的系统组成如图16 所示。

(a )

a

b

c

d

e f

(b )e 1011

000

a

b

c d

e f

(b )e 2DPSK (t )a c d e f 101100

0图13 2DPSK 信号相干解调器原理图和解调过程各点时间波形

图1 4 差分译码器

图16 相干解调法的系统组成

其中,图符11为带通滤波器,图符13实现相干载波的提取,图符12为乘法器,图符15为低通滤波器,图符16、17、18实现抽样判决,图符19、20实现差分解码。

图符19输出再生的绝对码。

图符的参数设置如表3所示。

编号库/名称参数

11 Operator: Linear Sys

Butterworth Bandpass IIR 3 Poles,Low Fc = 10e+3 Hz,Hi Fc = 30e+3 Hz Quant Bits = None,Init Cndtn = Transient,DSP Mode Disabled,FPGA Aware = True,RTDA Aware = Full

13 Comm: Costas VCO Freq = 20e+3 Hz,VCO Phase = 0 deg

Mod Gain = 1 Hz/v,Loop Fltr = 1 + 1/s + 1/s^2

Output 0 = Baseband InPhase ,

Output 1 = Baseband Quadrature

Output 2 = VCO InPhase ,Output 3 = VCO Quadrature t12

RTDA Aware = Full

15 Operator: Linear Sys

Bessel Lowpass IIR 3 Poles,Fc = 8e+3 Hz,Quant Bits = None,Init Cndtn = Transient DSP Mode Disabled,FPGA Aware = True,RTDA Aware = Full

16 Operator: Sampler Interpolating ,Rate = 10e+3 Hz,Aperture = 0 sec,Aperture Jitter = 0 sec

17 Operator: Hold Last Value ,Gain = 1,Out Rate = 200e+3 Hz

18 Logic: Buffer Gate Delay = 0 sec,Threshold = 0 v,True Output = 1 v

False Output = -1 v,Rise Time = 0 sec,Fall Time = 0 sec

19 Logic: XOR Gate Delay = 0 sec,Threshold = 0 v,True Output = 1 v

False Output = -1 v,Rise Time = 0 sec,Fall Time = 0 sec

20 Operator: Delay Non-Interpolating,Delay = 100.e-6 sec,Output 0 = Delay t19

Output 1 = Delay - dT

调制信号为PN序列,码速率Rb=10kbit/s;正弦载波的频率为20k Hz。

系统定时:起始时间0秒,终止时间1.95e-3秒,采样点数500,采样速率300e+3Hz,

获得的仿真波形如图17所示。

(a)二相相对调相(2DPSK)信号

(b)带通滤波器的输出

(c)提取的相干载波

(d)乘法器的输出

(e)低通滤波器的输出

(f)解调输出的相对码

(g)解调输出的绝对码

图17相干解调过程的仿真波形

2DPSK系统输入的PN序列和输出PN序列的瀑布图如图18所示。

图18 2DPSK系统输入的PN序列和输出PN序列的瀑布图

眼图如图19所示。

图19 眼图

图19的眼图是没有加噪声情况下的仿真结果,眼图张开度较大,扫迹清晰。

信噪比0dB时的眼图

信噪比5dB时的眼图

信噪比20dB时的眼图

信噪比30dB时的眼图可以看出随着信噪比的增加,眼图质量越来越好。

5、主要信号的功率谱密度:

2DPSK的谱如图24所示。

图24 2DPSK的谱

乘法器输出信号的谱如图25所示。

图25 乘法器输出信号的谱输出PN序列的基带谱如图26所示。

图26 输出PN序列的基带谱

通过比较相干解调法和非相干解调法可以看出,相干解调法需要提取相干载波,还要进行码反变换,即将相对码变换为绝对码;而非相干解调法不需要提取相干载波,也不需要进行码反变换。

6、低通滤波器的单位冲击相应及幅频特性曲线:

低通滤波器的单位冲击相应

低通滤波器的幅频特性曲线

7、思考题:

(1)在相干解调法中,采用其它方法提取相干载波,试仿真之。

(2)与相干解调法相比,差分相干解调法有哪些优势?。