AD9850芯片原理及使用方法总结

DDS芯片AD9850

AD9850 的复位(RESET) 信号为高电平有效,且脉冲宽度不小于 5 个参考时钟 周期。AD9850 的参考时钟频率一般远高于单片机的时钟频率(小厮所用为单 片机 89C51,使用 12M 晶振), 因此 AD9850 的复位(RESET) 端可与单片机 的复位端直接相连。

W-CL K 和 FQ-UD 信号都是上升沿有效,用 MOVX @DPTR , A 指令向 AD 9850 传 送控制字时,P2.7 经反相并与反相后的信号相与得到一上升沿送至 AD9850 的 W-CL K 脚,此时已送到总线上的数据将被 AD9850 接收,连续五次将 40 位 的控制字全部发送以后,用 MOVX A , @DPTR 指令产生 FQ-UD 信号,使 A D9850 更改输出频率和相位,此时读入到单片机内的数据实际上无任何意义。 4.程序设计

AD9852 300 3.3

内置 12 位的 D/A 转换器、高速比较器、线形调频 1200

和可编程参考时钟倍频器

AD9853 165 3.3/5

1150 可编程数字 QPSK/16-QAM 调制器

AD9854 300 3.3

内置 12 位两路正交 D/A 转换器、高速比较器和可 1200

编程参考时钟倍频器

再加一点东西

AD 公司的常用 DDS 芯片选用列表:

型号

最大工 作频率 (MHz)

工作电压 (V)

最大 功耗 (mw)

备注

AD9831 25

3.3/5

120 低电压,经济,内置 D/A 转换器

AD9832 25

3.3/5

120 小型封装,转型输入,内置 D/A 转换器

直接数字频率合成器AD9850的幅度调制

SET GNDGND+1.1VOne Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106 • 781/329-4700 • World Wide Web Site: Rev. A | Page 1 of 2AN-423应用笔记R SET 引脚处的电压为(内部)控制放大器反馈环路的一部分,不得以外部方式予以更改。

R SET 调制电路(图2)以Q1为可变电阻,以R2为固定限流电阻,以防Q1过度开启。

当Q1工作于截止频率附近时,C1可以抑制噪声。

R1则可降低输入阻抗,从而进一步抑制噪声。

Q1上为完全调制AD9850输出所必需的输入电压约为1.5 v p-p ,直流失调约为2.3 v ,见图4。

直接数字频率合成器AD9850的幅度调制作者:Richard Cushing ,应用工程师本应用笔记将提供一种对AD9850 DDS 的输出电流进行电压控制或幅度调制的方法,其中以一种增强型MOSFET 取代R SET 固定电阻;并利用一种宽频RF 变压器将DDS DAC 输出结合起来,以产生一种对称的AM 调制包络。

速率超过50 kHz 时实现合理线性度的调制是可能的。

AD9850 DDS 的输出电流(最大20mA)一般通过从RSET(引脚12)输入到接地的一个固定电阻设定。

DAC 输出为单极性且互补(180度相位差)。

采用增强型MOSFET 符合单电源理念。

这种设计较为简单,并可尽量减少器件数量。

将I OUT 和I OUTB DAC 输出结合于一个中心抽头型宽频RF 变压器之中可产生一个对称的调制包络,如图1(A)所示。

图1(B)所示为不结合两个输出而仅仅采用一个输出的效应——非对称幅度调制。

两种配置均采用同一信号进行调制。

图2. R SET 改变图1. 对称(A)和非对称(B)幅度调制包络To I OUT OUTB PIN 20*MINI-CIRCUITS BROADBAND RF TRANSFORMERGNDGNDGNDGNDGND GNDAN-423Rev. A | Page 2 of 2©2011 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. 下面的图4展示了10 kHz 调制包络及其至Q1栅极的相关输入信号。

AD9850模块使用说明

3、与单片机的硬件连接及程序(串行送控制字方式)

-2-

DDS 模块使用说明书 2009-07

无忧电子工作室资料

-3-

串行读写程序:该程序实现的是固定频点的输出 1KHZ

#include<regx51.h>

#include <intrins.h>

sbit FQ_QD_AD9850 = P1^0;

-3-

DDS 模块使用说明书 2009-07

无忧电子工作室资料

-4-

FQ_QD_AD9850 = 0; } void Set_Freq(unsigned long int Freqency) {

freq= (unsigned long int)(34.36*Freqency); // SYSCLK = 125 MHz 2^32/125000000=34.36

W3=(unsigned char)freq&0xff; freq=freq>>8;

W2=(unsigned char)freq&0xff;

-5-

DDS 模块使用说明书 2009-07

freq=freq>>8;

W1=(unsigned char)freq&0xff;

Parallel2Serial_AD9850(); } void main(void) {RST_AD9850=1;//复位模块电路 RST_AD9850=1; RST_AD9850=0;

-7-

DDS 模块使用说明书 2009-07

无忧电子工作室资料

-8-

6、输出波形及频率特性(频谱仪测量) 10HZ 波形输出

AD9850中文资料

VC C4

2

U2

VCC CLK GND

16MHz

VCC

36 81

U21

DDS_D0 DDS_D1

4 3

D0

R

DDS_D2 DDS_D3

2 1

D A D1

D2

DA

DDS_D4 28 DDS_D5 27 DDS_D6 26 DDS_D7 25

W_CLK 7

FQ_UP

8

D3

IOUT

D4

D5

dds 芯片复位

A,@R1;

写入 5 个频率字

@DPTR,A

R1;

R0,PROC_9850;

A,#00H

DPTR,#FQ_UP ;装载频率字并启动转换

@DPTR,A ;

J1,J4 为总线插槽,具体管脚定义如下表:

符号

定义

引脚

功能说明

D0~D7

数据总线

4~11 D0~D7 /A0~A7 总线分时复用,非扩展

方式下可作为位控

A0~A7

低 8 位地址线 12~19

CS0~CS7

输 入 输 出 地 址 23~30 由处理器板中的 CPLD 对数据存储地址空间

段选择信号

中的高位地址线译码产生,占据最高的

图 0341-6 模块器件分布图

U2 为有源晶振;

J2 为电源,从上往下依次为:VCC,GND;

U21 为 AD9850;

J6 为电源插座;

J5 为 CPLD 下载编程接口;从左向右依次为:VCC,GND,TCK,TDO,TDI,TMS;

J3 信号输出端。从上到下依次为: SIN_OUT,GND,BUS_CLK,GND;

9850-DDS电路说明书

AD9850/9851DDS电路使用说明书江苏省无线电运动协会2007年4月9850/9851DDS电路简介AD9850/9851DDS电路是专为业余无线电电台设计的,它提供本机振荡信号和波段控制信号,特别适合做自制电台的本振源及老电台改造。

本电路使用有背光1602型通用液晶显示器,显示接收频率及工作模式。

电路大部分元器件为贴片封装,体积小,便于安装(PCB尺寸:36*93mm)。

在满足基本应用的条件下尽量简化设计,以提高性价比。

本电路可以使用AD9850(时钟100MHz)或AD9851(时钟20MHz)芯片,由用户设置。

中频频率可以由用户任意设置。

波段控制输出可以选择4波段或9波段,由用户设置。

所有设置均由软件实现并保存在芯片内。

关机前的工作频率将被保存,下次开机将工作在这个频率。

为简化电路,10MHz以下设计为高本振、10MHz以上为低本振,这样只要一个插入载频即可以完成对10MHz以下的LSB解调和10MHz以上的USB解调。

也可以选择本振减中频的模式(本振总是减中频、DDS输出减中频=接收频率)。

主要功能如下:1.频率范围:0.1-40MHz2.频率分辨率:10Hz3.频率步进:10Hz、100Hz、1KHz、10KHz、100KHz、1MHz4.存储频点:20个存储频点可由用户任意设置。

5.显示模式:USB、LSB、CW、AM、FM6.接收频率微调:具有加减80KHz的接收频率微调功能。

7.收发转换:两种发信方式:普通方式和CW方式。

8.电源:电压8-12V DC,电流约180mA(背光打开),110mA(背光关闭)。

其他功能:1.频率校正:对DDS芯片的基准频率误差可通过软件设置校正。

2.边带切换:当选择了+-IF的模式时上下边带自动切换,10MHz以下为LSB、10MHz以上为USB,。

CW发信方式是利用了DDS的特点而特别设计的,如果选择这种方式,则发信时DDS将直接输出所需的频率而不需要任何频率变换,简化了发信电路。

AD9850125MHzDDS频率合成器的原理及应用_郭荣祥

●模拟器件天地 AD9850 125MHz DDS 频率合成器的原理及应用北京航空航天大学1-12信箱(100083) 郭荣祥 郭吉祥摘 要:介绍了美国ADI 公司采用先进的DDS 技术新推出的高集成度频率合成器AD 9850的主要特性、工作原理、应用电路和应用考虑。

关键词:直接数字频率合成(DDS ) 频率合成器 时钟发生器 锁相环(PLL )1 概述频率合成器是从一个或多个参考频率中产生多种频率的器件。

这种器件已经用了几十年,尤其是在通信系统中已得到广泛应用。

传统的频率合成器,通常从一排晶体振荡器产生的各种频率通过开关进行频率混合。

也有的采用众所周知的锁相环(PL L )技术实现频率合成。

随着数字技术在仪器仪表和通信系统的广泛应用,用数字控制方法从一个参考频率源产生多种频率,即直接数字合成技术(DD S)异军突起。

本文试图介绍世界流行的美国AD I 公司生产的A D 9850频率合成器正是应用这种D DS 技术的典型热门产品之一,其基本结构框图见图1。

·图1DDS 基本结构框图OUT输出f DACLPFN 位正弦查询表地址计数器c时钟f 在图1中,正弦查询表是一个可编程只读存储器(P RO M ),存有一个或多个完整周期的正弦波数据,在时钟f C 驱动下,地址计数器逐步经过PRO M 存储器的地址,地址中相应的数字信号输出到N 位数模转换器(D AC)的输入端,D AC 输出的模拟信号,经过低通滤波器(L PF),可得到一个频谱纯净的正弦波。

在图1系统中,输出频率无法进行编程控制,实际中常用的可编程DD S 系统如图2所示。

该DDS 系统的核心是相位累加器,它由一个加法器和一个N 位相位寄存器组成,N 一般为24~32位。

每来一个时钟f C ,输出频率图2可编程控制DDS 系统时钟fc相位截断13~15位幅度截断相位累加器N 位OUT f DACLPFN 位正弦查询表N位相位寄存器N 位频率控制字M相位控制字微控制器相位寄存器以步长M 增加。

AD9850数据手册

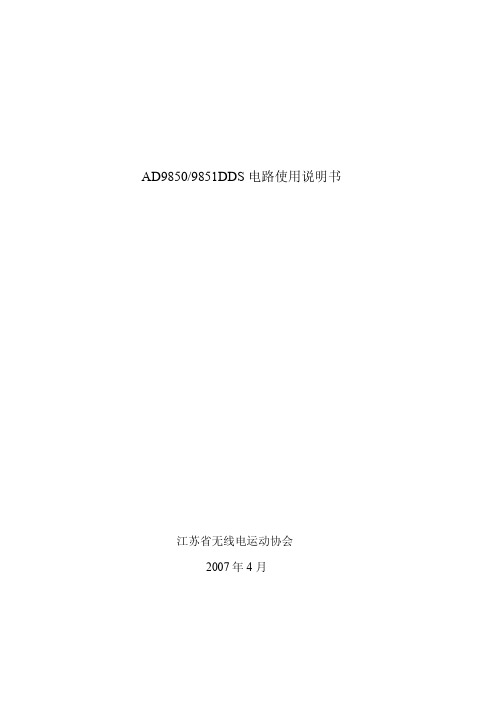

模拟器件 COMS 工艺,125MHZ 完整的DDS 频率合成器特点125M 时钟频率片内高性能DAC 转换器和高速比较器 DAC SFDR > 50 dB @ 40 MHz AOUT 32位频率控制字简单的控制接口:串行或并行装载模式可进行相位调节3.3V 或5V 单电源供电低功耗:380 mW @ 125 MHz (5 V)155 mW @ 110 MHz (3.3 V)省电模式超小型28引脚SSOP 封装 应用频率/相位——方便的正弦波合成 针对数字通信的时钟恢复和锁存电路 数控ADC 编码发生器 灵活的本机振荡器应用概述AD9850是一款高度集成的设备,采用先进的DDS 技术,结合内部高速,高性能的D / A 转换器和比较器,以构成一个完整的,数字可编程频率合成器和时钟发生器。

当连接到一个准确的时钟源时,AD9850产生一个频谱纯净,频率/相位可编程的模拟输出正弦波。

这个正弦波可以直接使用作为频率源,或者它可以被转变为方波作为精准时钟发生器使用。

AD9850先进的高速DDS 内核提供了一个32位的频率调谐字,这使得其在外部125MHZ 参考时钟的输入下,分辨率可达0.0291HZ 。

AD9850的电路架构使得其产生的最高输出频率为其参考的基准时钟频率的一半(或62.5兆MHZ ),而且其输出频率是数控可变的,速率高达72.310 次每秒。

该器件还提供了5位的相位控制字,从而使其输出信号的相位该变量可以为180°,90°,45°,22.5°,11.25°,以及它们的任意组合。

AD9850还包含一个高速比较器,该比较器可以输入经过滤波(外部)的片内DAC 产生的信号以生成一个低抖动方波输出。

这使得该芯片可以作为精准的时钟信号源。

AD9850的频率调谐,控制和相位调制字是通过一个并行字节或方式载入到芯片内部的。

并行载入格式由五个8位的控制字组成。

多个基于DDS芯片AD9850 AD9851的合成器的同步方法

多个基于DDS芯片AD9850/AD9851的合成器的同步方法一.概述在许多应用中,要求产生两个或者更多明确的相位相关的正弦信号,例如相位正交,美国ADI( Analog Devices Inc)公司推出的AD9850和AD9851 DDS集成芯片就可以提供这样的正弦信号。

本文详细地介绍了DDS芯片AD9850/AD9851的基本原理以及多个基于DDS芯片AD9850/AD9851的合成器的同步方法,提供了实现的步骤和指令,并且讨论了产生相位错误的可能原因。

二.基本原理1、AD9850/AD9851的基本特点和工作原理AD9850/AD9851是AD公司生产的最高时钟为125MHz、采用先进的CMOS技术的直接频率合成器。

它结合一个片内高速、高性能DAC和比较器构成一个完整的数字控制可编程频率合成器,是具有时钟产生功能的高集成度芯片。

由于采用了CMOS技术,其功耗较小,在+5V 电源供电,125MHz时钟时,能以380mW的功率工作。

AD9850/AD9851具有以下特点:a)125MHz的时钟频率;b)集成在一块集成电路芯片上的高性能DAC以及高速比较器;c)5bits相位调制;d)32bits频率控制字;e)40MHz模拟输出时,DAC输出的抑制寄生动态范围SFDR>50dB;f) +5V电源供电,125MHz时钟时,功率为380mW;g)简化的控制接口,并行或串行输入形式;h)极小的28管脚表面封装形式。

图1为AD9850/AD9851的功能模块图。

由此可以看出,这两种芯片只有微小的区别,那就是AD9851有一个6x时钟乘法器和MUX,而AD9850没有。

在DDS (Direct Digital Synthesis,直接数字式频率合成)内核前有两个寄存器,第一个是移位寄存器,它接收5字节的并行数据或者40位的串行数据,由字输入时钟信号W_CLK将数据锁存到该寄存器中。

当第二个寄存器由FQ_UD信号触发后,它就会将移位寄存器中的内容送到DDS内核,此过程在系统时钟信号的下一个上升沿完成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD9850芯片原理及使用方法总结DDS专用芯片电路广泛的应用于各个领域,其中以AD公司的产品比较有代表性。

如AD7008、AD9850、AD9851、AD9852、AD9854、AD9858等。

其系统时钟频率从30MHz到300MHz不等,其中的AD9858系统时钟更是达到了1GHz。

这些芯片还具有调制功能,如AD7008可以产生正交调制信号,AD9852可以产生FSK(频移键控)、PSK(相移键控)、线性调频以及幅度调制的信号。

这些芯片集成度高,内部都集成了D/A转换器,精度最高可达12bit,同时都采用了一些优化设计来提高性能。

如这些芯片中大多采用了流水技术,通过流水技术的使用,提高了相位累加器的工作频率,从而使得DDS芯片的输出频率可以进一步提高。

一、AD9850简介AD9850是美国AD公司采用先进的DDS技术,1996年推出的高集成度DDS频率合成器,采用CMOS工艺,其功耗在3. 3V供电时仅为155mW,扩展工业级温度范围为- 40~80℃,采用28脚SSOP表面封装形式。

它内部包括可编程DDS系统、高性能DAC及高速比较器,能实现全数字编程控制的频率合成器和时钟发生器。

接上精密时钟源,AD9850可产生一个频谱纯净、频率和相位都可编程控制的模拟正弦波输出。

此正弦波可以直接作为信号源输出或者送入AD9850的高速比较器从而得到方波输出。

AD9850接口控制简单,可以用8位并行口或串行口直接输入频率、相位等控制数据。

32位频率控制字,在125MHz时钟下,输出频率分辨率为0.029Hz,频率范围为0.1Hz~40MHz,幅值范围为0.2~1V。

其引脚排列如图1所示,各引脚定义如下:D0~D7(4-1,28-25):控制字并行输入,给内部寄存器装入 40 位控制数据,其中D7可做串行输入DGND(5、24):数字地DVDD(6、23):为内部数字电路提供电源(3.3V或5V)W-CLK(7):控制字装入时钟,用于加载并行/串行的频率/相位控制字,上升沿有效FQ-UD(8):频率更新控制信号,时钟上升沿确认输入数据有效FREFCLOCK(9):外部参考时钟(有源晶振)输入,最高125MHzAGND(10、19):模拟地AVDD(11、18):为内部模拟电路提供电源(5V),可与数字电源共用Rset(12):外接电阻,决定器件输出电流大小,典型值为3.9KQOUT(13):内部比较器正向输出端(方波)QOUT(14):内部比较器反向输出端(方波)VINN(15):内部比较器的负向输入端VINP(16):内部比较器的正向输入端DACBL(17):内部DAC外接参考电压端,可悬空IOUTB(20):“互补”DAC 输出IOUT(21):内部 DAC 输出,争先电流输出端,一般用电阻接地以转换为正弦电压RESET(22):复位端可编程DDS系统的核心是相位累加器,它由一个加法器和一个N位相位寄存器组成,N一般位24~32。

每来一个外部参考时钟,相位寄存器便以步长M递加。

相位寄存器的输出与相位控制字相加后可输入到正弦查询表地址上。

正弦查询表包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0°~ 360°范围的一个相位点。

查询表把输入地址的相位信息映射成正弦波幅度信号,然后驱动数模转换器(DAC)以输出模拟量,如图2所示。

其内部原理结构如图3所示。

图2AD9850组成框图图 3 AD9850结构可见,AD9850主要组成有三部分:一是高度DDS内核,是AD9850的核心,包括相位寄存器、频率寄存器、相位累加器、波形ROM;二是接口电路,即输入寄存器,用于接收单片机送来的40bit数据;三是模拟电路部分,即DA转换器及比较器。

二、芯片工作方式介绍1、控制字的加载表1 AD9850的40位控制字/数据字AD9850有40位控制字,32位用于频率控制,5位用于相位控制,1位用于电源休眠,2位用于选择工作方式,详见表1。

这40位控制字可通过并行或串行方式输入到AD9850,图4是控制字并行输入的时序图。

在并行装入方式中,通过8位总线D0-D7可将数据输入到寄存器。

在W-CLK的上升沿装入8位数据,并把指针指向下一个输入寄存器,在重复5次之后,再在FQ-UD上升沿把40位数据从输入寄存器装入到频率/相位数据寄存器(更新DDS输出频率和相位),同时把地址指针复位到第一个输入寄存器。

连续5个W-CLK上升沿后, W-CLK的边沿就不再起作用,直到复位信号或FQ-UD上升沿把地址指针复位到第一个寄存器。

图4 控制字并行输入的时序图图5 控制字串行输入时序图在串行输入方式,W-CLK上升沿把25(D7)引脚的一位数据串行移入,当移动40位后,用一个FQ_UD脉冲即可更新输出频率和相位。

图5是相应的控制字串行输入的控制时序图。

AD9850的复位(RESET)信号为高电平有效,且脉冲宽度不小于5个参考时钟周期。

AD9850的参考时钟频率一般远高于单片机的时钟频率, 因此复位端(22)可与单片机的复位端直接相连。

2、相位控制字的计算AD9850中有5bit用于相位控制,相位控制的精度为360°/25=11.25°,用二进制表示为00001,根据实际需要,设置不同的相位控制字就可以实现精确的相位控制。

表2给出了相移与相位控制字之间的对应关系,允许相位按增量11.25°、22.5°、45°、90°、180°移动或者这些值进行组合。

表2 相移与相位控制字之间的关系3、频率控制字的计算输出信号的频率由频率控制字内的相位增加量来决定。

设相位累加器的位数为N,频率控制字内的相位增量为K,参考时钟频率为CLKIN,AD9850的频率控制字为△Freq,则DDS系统输出信号的频率f OUT为:f OUT=(CLKIN×K)/2N,输出信号的频率分辨率为△f OUT=CLKIN/2N,对于一个相位累加器的位数N=32,参考时钟频率为CLKIN=125MHz,当相位增量K=1时,输出信号频率,f OUT最低,其值约为0.03Hz,这个值也是输出信号的频率分辨率△f OUT;K的值不能太大,否则会出现失真波形。

f OUT的最大值理论上至少应少于CLKIN/2,当相位增量K=231时,输出信号频率f OUT 最高,其值可达62.5MHz。

所以要向提高输出频率的最大值,就得靠提高系统的外部时钟CLKIN。

当给定DDS系统输出信号的频率为f OUT,AD9850的频率控制字为:△Freq=K=(f OUT×2N)/CLKIN。

AD9850的频率控制字位数N为32位,当参考时钟频率CLKIN=20MHz,输出信号频率位1kHz,则向AD9850写入的频率控制字为:△Freq=K=(1×103×232)/(20×106)≈214748=0X000346DC。

三、硬件电路设计1、DDS模块与单片机接口电路AD9850默认复位为并行置入方式,所以要采用串行配置必须先进行切换。

即在并行方式下写入一个字节的控制字W0后,利用FQ_UD脉冲更新使其生效即可。

AD9850并串配置切换硬件连接方法是:使D2=0,D1=D0=1,这样在AD9850每次上电或系统复位时的配置方式皆为串行方式。

注意:串行连接时,先送频率字最低字节,再送频率最高字节,最后送相位控制字(每个字节中先低位后高位);并行连接时,先送相位控制字,再送频率最高字节,最后送频率最低字节。

I OUTB引脚是I OUT引脚的互补输出端,它可输出与I OUT引脚相同的电流,在电路设计是,应在I OUT引脚外接电阻,一边输出正弦波电压。

该电压可作为AD9850内部告诉比较器同相端的输入信号,并通过其外围电路的设计,将比较器的阈值电压取为信号幅度的一半,从而使得AD9850输出占空比为50%的方波信号。

图6 串行连接方式接口电路AD9850采用32位的相位累加器将信号截断成14位输入到正弦查询表,查询表的输出再被截断成10位后输入到DAC,DAC再输出两个互补的电流。

DAC满量程输出电流通过一个外接电阻RSET调节,调节关系为ISET =32 ×(1. 148V /RSET),RSET的典型值是3. 9kΩ。

将DAC的输出经低通滤波后接到AD9850内部的高速比较器上即可直接输出一个抖动很小的方波。

AD9850对输入的标准正弦波,进行直接数字合成。

输入信号频率最高为fclk = 125MHz,可生成0 - fclk /2范围内的任意频率正弦波和方波。

AD9850在接上精密时钟源和写入频率相位控制字之间后就可产生一个频率和相位都可编程控制的模拟正弦波输出,此正弦波可直接用作频率信号源或经内部的高速比较器转换为方波输出。

在125MHz 的时钟下,32 位的频率控制字可使AD9850的输出频率分辨率达0. 0291Hz;并具有5位相位控制位,而且允许相位按增量180°、90°、45°、22. 5°、11.25°或这些值的组合进行调整。

使用中注意:RESET决定了器件输出端的电流大小,推荐连3. 9K电阻到地;V INP、V INN 分别是片内比较器的正向输入端和反相输入端,V INP接IOUT输出的正弦信号,可用于将输出的正弦波转换为方波;IOUT通常接200欧电阻到地以转换为正弦电压输出,IOUTB为互补输出;QOUT为方波输出,QOUTB为方波反相输出,悬空。

图7 并行连接方式接口电路2、滤波模块(1)DDS的全数字型导致其存在一定缺陷,即杂波分布广泛。

当杂波落入输入频带内时,则无法滤除。

杂波主要是由数字器件的非理想特性而产生的幅度量化误差和相位截断误差等因素造成的。

其主要撒播分量遵循Nyquist采样订立,杂波分量出现在参考频率与输出频率的组合出,即12(n0,1,2,)nf f+=±±处。

图8 3阶椭圆滤波器电路图为了使输出的频率不受外界和一些杂波的干扰,需用一个低通滤波器(LPF)滤除高次谐波。

常用的滤波器的频率响应有三种:巴特沃斯型(Butterworth),切比雪夫型 (Chebyshev)和椭圆型(Cauer)。

其中巴特沃斯滤波器通带最平坦,它的通带内没有纹波,在靠近零频处,有最平坦通带,趋向阻带时衰减单调增大,缺点是从通带到阻带的过渡带最宽,对于带外干扰信号的衰减作用最弱,过渡带不够陡峭,因此它适用于对通带要求较高,而去除的频率离通带较远的情况;切比雪夫滤波器在通带内衰减在零值和一个上限值之间做等起伏变化,阻带内衰减单调增大,带内有起伏,但过渡带比较陡峭;椭圆滤波器不仅通带内有起伏,阻带内也有起伏,而且过渡带陡峭。