26针信号线接口定义

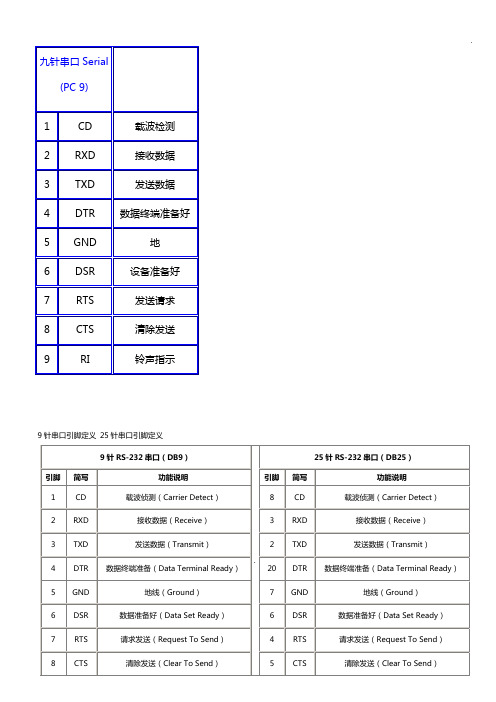

针串口引脚定义25针串口引脚定义

9针串口引脚定义25针串口引脚定义RS-232-C 串口通讯详解串行通信接口标准经过使用和发展,目前已经有几种。

但都是在RS-232标准的基础上经过改进而形成的。

所以,以RS-232C为主来讨论。

RS- 323C标准是美国EIA(电子工业联合会)与BELL等公司一起开发的1969年公布的通信协议。

它适合于数据传输速率在0~20000b/s范围内的通信。

这个标准对串行通信接口的有关问题,如信号线功能、电器特性都作了明确规定。

由于通行设备厂商都生产与RS-232C制式兼容的通信设备,因此,它作为一种标准,目前已在微机通信接口中广泛采用。

在讨论RS-232C接口标准的内容之前,先说明两点:首先,RS-232-C标准最初是远程通信连接数据终端设备DTE(Data Terminal Equipment)与数据通信设备DCE(Data Communication Equipment)而制定的。

因此这个标准的制定,并未考虑计算机系统的应用要求。

但目前它又广泛地被借来用于计算机(更准确的说,是计算机接口)与终端或外设之间的近端连接标准。

显然,这个标准的有些规定及和计算机系统是不一致的,甚至是相矛盾的。

有了对这种背景的了解,我们对RS-232C标准与计算机不兼容的地方就不难理解了其次,RS-232C标准中所提到的“发送”和“接收”,都是站在DTE立场上,而不是站在DCE的立场来定义的。

由于在计算机系统中,往往是CPU和I/O设备之间传送信息,两者都是DTE,因此双方都能发送和接收。

一、RS-232-CRS-232C标准(协议)的全称是EIA-RS-232C标准,其中EIA(Electronic Industry Association)代表美国电子工业协会,RS(ecommeded standard)代表推荐标准,232是标识号,C代表RS232的最新一次修改(1969),在这之前,有RS232B、RS232A。

电脑各类接口引脚定义

电脑各类接口引脚定义PS/2接口:分别为AT键盘(即常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多,而AT键盘已经要沦为昨日黄花。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1.DATA 数据信号2.空3.GND 地端4.+5V5.CLOCK 时钟6.空(仅限PS2键盘)USB接口:接线方式:红线:+5V 黑线:GND 白线:D- 绿线:D+USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB 才真正开始普及,到今天已经发展到USB2.0标准。

USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接头)。

RJ45网线顺序:568B:568A:RS232串口:串口是计算机主要的外部接口之一,通过九针串口连接的设备有很多,像串口鼠标、MODEM、手写板等等,九针串口的示意图如上,其各脚的定义如下:1.DCD 载波检测2.RXD 接收数据3.TXD 发送数据4.DTR 数据终端准备好5.SG 信号地线6.DSR 数据准备好7.RTS 请求发送8.CTS 清除发送9.RI 振铃指示并口:并口是计算机一个相当重要的外部设备接口,最常用来连接的设备那就要算是打印机了,另外,有许多型号的扫描仪也是通过并口来与计算机连接的。

并口也是25针的,与25针串口不同的是,并口是25个孔,所以常称为“母头”,而像串口就常称为“公头”。

安川SGMJV,SGMGV编码器与CDHD接线定义

测试安川电机样机:

1、电机型号:SGMJV-02A3(带20位编码器)。

2、编码器接线:

电机侧自带的连接器,它直接插入驱动器的反馈输入接口。

它是公头,针脚定义如下图截图所示:

电机侧编码器针脚定义如下图所示:“伺服单元侧”即上述公头,

母头的针脚定义及其延长线接线如下图示:

最终接线表:

功能 CDHD C4(26针) 线色 上述母头(6针) Data+ 1 棕 5 Data- 14 黑 6 5 VDC 11 紫 1 0 VDC

24

蓝

2

3、 电机规格:规格书上未提供电感、电阻、极数等信息。

实测电阻约为7.7 Ohm 。

通

过ZERO 1模式,读取极数为6。

2014-10-11补记:安川电机编码器与SERVOTRONIX CDHD 驱动器的连接

SERVOTRONIX CDHD 驱动器 安川电机编码器

信号名 C4接口(26针) 信号名 6针molex 连接器 Data+ 1 PS 5 Data- 14 /PS 6 5 VDC 11 PG 5V 1 0 VDC 24

PG 0V 2 电池正极 无(编码器直接接到电池)

BAT(+)

3

电池负极 无(编码器直接接到电池) BAT(-)

4

屏蔽

26

FG

壳体

20141029

1、安川SGMGV 马达编码器与CDHD 驱动器接线定义

最终接线表:

功能 CDHD C4(26针) 安川SGMGV 马达编码器(10针) Data+ 1 1 Data- 14 2 5 VDC 11 4 0 VDC

24

9

1

2 4 6

3 5

紫 红 棕

黑

黑 蓝。

接口针脚定义培训

TS头:信号热端,Sleeve套管:信号 地

专业设备上至少也是不平衡连接 TS大两芯接口。最好的联结方式 肯定是平衡卡侬接口,十分牢固 !可惜体积大成本高。

平衡接法、非平衡接法

所谓平衡接法就是用两条信号线传送一对平衡的信号的连接方法,由于两 条信号线受的干扰大小相同,相位相反,最后将使干扰被抵消。由于音频的频率 范围较低,在长距离的传输情况下,容易受到干扰,因此,平衡接法作为一种抗 干扰的连接方法,在专业设备的音频 连接中最为常见。在家用电器的连接线中也 有用两芯屏蔽线作音频连接线的,但是,它传输 的是左右声道,是两个信号,不 属于平衡接法。 而非平衡接法就是仅用一条信号线传送信号的连接方法,由于这种接法容 易受到干扰,所以只一般在家用电器上或一些要求较低的情况下使用。 具体的接法以 XLR 接头为例: 1、平衡接法:1 脚接屏蔽,2 脚接+端(又称热端),3 脚接–端(又称冷端) 2、非平衡接法:1 脚和 3 脚相连接屏蔽,2 脚接+端(信号端)。 选择什么接法:根据设备对接口的具体要求而定,能使用平衡接法的尽量 使用平衡接法,进行连接时务必先看清面板上的说明,最好先阅读使用说明书上 的有关说明和要求。在 一些场合还可能遇到一端的设备接口是平衡接口,另一端 的设备是非平衡接口的情况,在要 求不很严格的情况,只需在平衡端使用平衡接 法,非平衡使用非平衡接法,注意各脚对应就 可以了。在要求严格的情况,就必 须使用转换电路将平衡转为非平衡,或将非平衡转为平衡。

接口针脚定义培训

2009/0203

S端子针脚定义

英文简介:Plug——插头;connector——端子; S端子S-connector 端子S 1脚——亮度信号地 (Y-GND信号) 2 脚——色度信号地 (C-GND信号) ——亮度信号地 ——色度信号地 3脚——亮度信号输入输出 (Y信号) 4 脚——色度信号输入输出 (C信号) ——亮度信号输入输出 ——色度信号输入输出

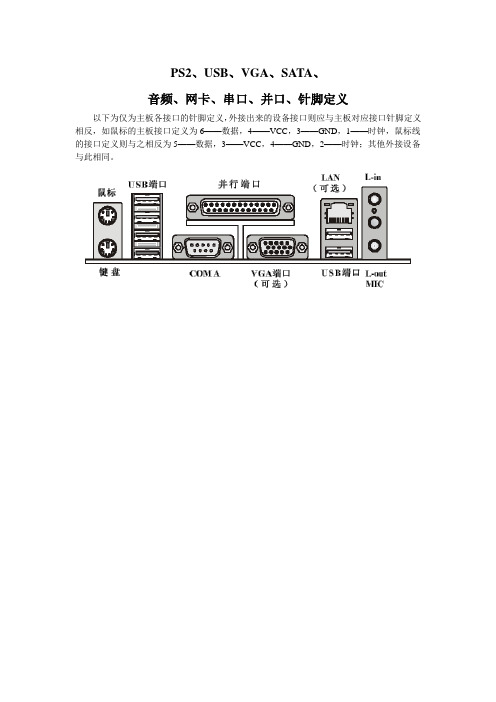

PS2、USB、VGA、SATA、音频、网卡、串口、并口、针脚定义

PS2、USB、VGA、SATA、音频、网卡、串口、并口、针脚定义以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

首先是ATX20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU 的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1 DATA 数据信号2 空3 GND 地端4 +5V5 CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接头)。

USB接口针脚定义及详细说明(附图文说明)

USB接口针脚界说及详细说明(附图文说明)之邯郸勺丸创作鉴于近期常有客户向我司咨询关于USB接口针脚界说及图文解释, 将USB针脚资料进行整理上传, 供客户参阅, 详情如下:一、USB接口界说:众所周知, USB接口金属触点为4根金属线, 两根电源线和两根数据信号线, 故信号是串行传输的.因此也被称为串行口, 标准的USB2.0接口其数据传输速度可达480Mbps.可以很好的满足工业和民用的需要.USB接口的输出电压和电流是:+5V 500mA 实际运用中存有正负0.2v的误差, 也就是4.8-5.2V .usb接口的4根线一般是红白绿黑从左到右这样分配的, 具体针脚界说如下所示, 特提醒切勿将正负极弄反了, 否则会损坏USB设备或者计算机南桥芯片, 从而影响设备正常使用.二、USB引脚界说:针脚名称说明接线颜色 1 VCC + 5V电压红色 2 D- 数据线负极白色 3 D+ 数据线正极绿色 4 GND 接地黑色三、MiniUSB接口界说:一般的排列方式是:红白绿黑从左到右界说:红色-USB电源:标有-VCC、Power、5V、5VSB字样绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+白色-USB数据线:(负)-DATA-、USBD-、PD-、 USBDT+黑色-地线:GND、Ground四、MiniUSB引脚界说:针脚名称说明接线颜色 1 VCC+ 5V电压红色 2 D- 数据线负极白色3 D+ 数据线正极绿色 4 ID permits distinctionof Micro-A- and Micro-B-Plug noneType A:connected to Ground Type B:notconnected 5 GND 接地黑色插针管脚界说(图纸):其中ID脚通常为空, 只有在OTG功能中才使用.由于Mini-USB接口分Mini-A、B和AB接口.如果你的系统仅仅是用做Slave, 那么就使用B接口.系统控制器会判断ID脚的电平判断是什么样的设备拔出, 如果是高电平, 则是B接头拔出, 此时系统就做主模式(master mode) ;如果ID为低, 则是A接口拔出, 然后系统就会使用HNP对话协议来决定哪个做Master, 哪个做Slave.我们手机/移动电源等设备上一般用的都是B型MiniUSB口/Micro USB接口, 目前市面上最为通用的也是USB B型接口、MiniUSB B 型口以及Micro USB B型接口.。

针脚定义及接口定义图解

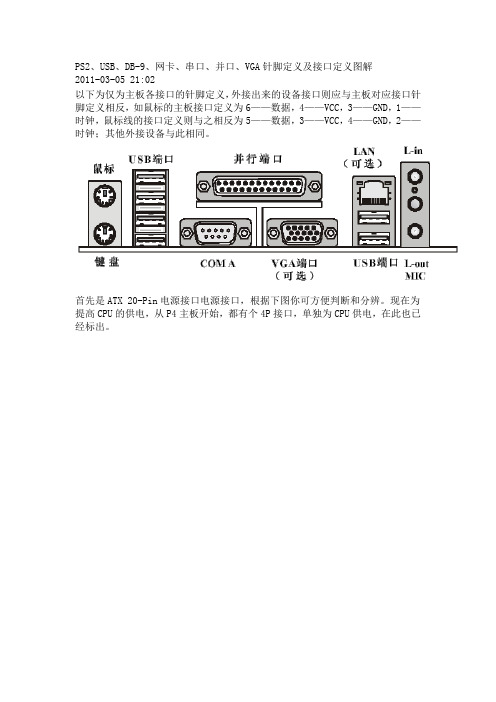

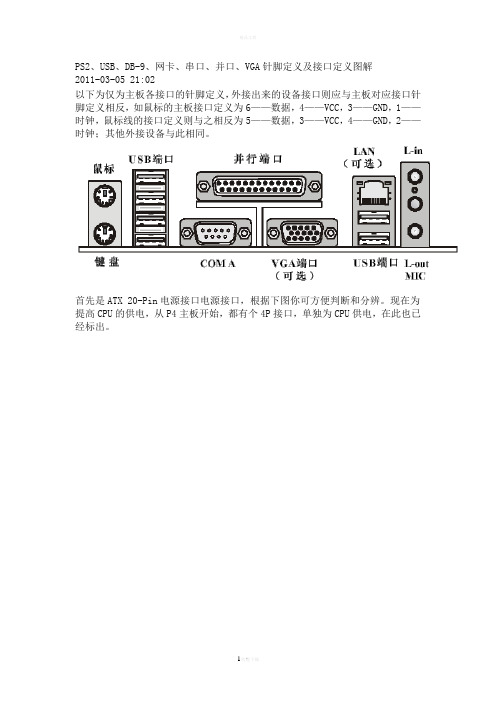

PS2、USB、DB-9、网卡、串口、并口、VGA针脚定义及接口定义图解2011-03-05 21:02以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1、DATA 数据信号2、空3、GND 地端4、+5V5、CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft 等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB 数据线而仅仅包含与电脑相连的“A”连接----USB接口提供5V和200ma电流Imax=500 mApc=500ma,笔记本100ma头)。

常用各种接口针脚定义

各种接口针脚定义RJ45接口信号定义,以及网线连接头信号安排以太网 10/100Base-T 接口:Pin Name Description1 TX+ Tranceive Data+ (发信号+)2 TX- Tranceive Data- (发信号-)3 RX+ Receive Data+ (收信号+)4 n/c Not connected (空脚)5 n/c Not connected (空脚)6 RX- Receive Data- (收信号-)7 n/c Not connected (空脚)8 n/c Not connected (空脚)以太网 100Base-T4 接口:Pin Name Description1 TX_D1+ Tranceive Data+2 TX_D1- Tranceive Data-3 RX_D2+ Receive Data+4 BI_D3+ Bi-directional Data+5 BI_D3- Bi-directional Data-6 RX_D2- Receive Data-7 BI_D4+ Bi-directional Data+8 BI_D4- Bi-directional Data-1 white/orange2 orange/white3 white/green4 blue/white5 white/blue6 green/white7 white/brown8 brown/white注:RJ45接口采用差分传输方式,tx+、tx-是一对双绞线,拧在一起可以减少干扰。

RS-232接口引脚定义RS-232接口又称之为RS-232口、串口、异步口或一个COM(通信)口,严格地讲RS-232接口是DTE(数据终端设备)和DCE(数据通信设备)之间的一个接口,DTE包括计算机、终端、串口打印机等设备。

DCE通常只有调制解调器(MODEM)和某些交换机COM口是DCE。

针脚定义及接口定义图解资料讲解

针脚定义及接口定义图解PS2、USB、DB-9、网卡、串口、并口、VGA针脚定义及接口定义图解2011-03-05 21:02以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU 的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1、DATA 数据信号2、空3、GND 地端4、+5V5、CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接----USB接口提供5V和200ma电流Imax=500 mApc=500ma,笔记本100ma头)。

RNS510(RCD510)针脚定义

RNS510(RCD510)针脚定义第1插座, 8针.扬声器输出1 – Rear r ig ht loudspeaker, positive后右扬声器,正极 RR+2 – Front r ig ht loudspeaker, positive前右扬声器,正极 RF-3 – Front left loudspeaker, positive前左扬声器,正极 LF+4 – Rear left loudspeaker, positive后左扬声器,正极 LR+5 – Rear r ig ht loudspeaker, negative后右扬声器,负极6 – Front r ig ht loudspeaker, negative前右扬声器,负极7 – Front left loudspeaker, negative前左扬声器,负极8 – Rear left loudspeaker, negative后左扬声器,负极第2个插座, 8针,电源电压和CAN线9 – CAN bus, high CAN线高10 – CAN bus, low CAN低11 – Display voltage supply, positive, optional for radio module low version only12 – Voltage supply, negative, terminal 31电源负极13 – Display HV CAN bus low, optional for radio module low version only, not for midline14 – Display HV CAN bus high, optional for radio module low version only, not for midline15 – Voltage supply, positive, terminal 30电源正极16 – Anti-theft coding control signal, SAFE, positive电源正极(防盗码控制)第3插座, 12针,电话和话筒1 – Microphone input, negative话筒输入负极2 – AUX output, audio, right AUX输出,音频,右3 – AUX output, common signal earth AUX输出,公用地4 – Microphone output, negative 话筒输出,负极5 – Telephone audio input signal left, negative电话音频输入,左,负极6 – Telephone audio input signal right, negative电话音频输入,右,负极7 – Microphone input, positive 话筒输入,正极8 – AUX output, audio, left AUX输出,音频,左9 – Microphone output, positive话筒输出,正极10 – Telephone mute (mute switch for radio)电话静音11 – Telephone audio input signal left, positive电话音频输入,左,正极12 – Telephone audio input signal right, positive电话音频输入,右,正极第4插座,12针, CD转换器和CD音频输入1 – AUX signal input, left AUX信号输入,左2 – AUX signal earth AUX 信号,地3 – CD changer, audio signal earth CD变换器,音频信号地4 – CD changer, voltage supply, positive, terminal 30, contact continuous load greater than 1 A, temporary peak load5 A 电源正极5 – Not assigned6 – CD changer, DATA OUT (data exchange for CD changer control from radio navigation system to CD changer)数据输出7 – AUX signal input, right AUX信号输入,右8 – CD changer, left audio channel, CD/L 左声道9 – CD changer, right audio channel, CD/R右声道10 – CD changer, control line, switched positive控制线11 – CD changer, DATA IN (data exchange for CD changer control from CD changer to radio navigation system)数据出12 – CD changer, CLOCK (internal check protocol for data flow monitoring) 时钟信号第5插座,26针,视频输入输出1 – Reserved for Debug RX protocol 保留,调试用2 – Reserved for Debug TX protocol 保留,调试用3 – Not assigned 未分配4 – Video signal input, RGBS, negative (ground) 视频输入,RGBS,负极(地)5 – Video signal output LF, Right (Audio use 17 for ground) 音频输出,右(17为地)6 – Ground Sync input(Internal universal preparation for mobile telephone, mobile telephone detection)7 – Video signal output, vertical and horizontal synchronisation 视频输出,水平垂直同步(Internal universal preparation for mobile telephone, cradle and button evaluation)8 – Video signal ouput, green 视频输出,绿色(Internal universal preparation for mobile telephone, cradle, aerial diagnosis)9 – Video signal input, RGBS, negative (ground)10 – Video signal input LF, right (Audio use 24 for ground) 音频输入,右(24为地)11 – Video signal input, screening earth 视频输入,屏蔽地12 – Video signal input, vertical and horizontal synchronisation 视频输入,水平垂直同步13 – Video signal input, green 视频输入,绿色14 – Not assigned 未分配15 – Not assigned 未分配16 – Not assigned 未分配17 - Video signal output, LF, negative (ground) 音频输出,负极(地)18 – Video signal output LF, Left (Audio use 17 for ground) 音频输出,左(音频17为地)19 – Video signal output, RGBS, negative (ground)(Internal universal preparation for mobile telephone, cradle, negative) 20 – Video signal output, Blue 视频输出,蓝色(Internal universal preparation for mobile telephone, switched terminal 30)21 – Video signal output, Red 视频输出,红色22 – Video signal input, LF, negative23 – Video signal input, LF, left (Audio use 24 for ground) 音频输入,左(音频24为地)24 – Video signal input, RGBS, negative (ground)25 – Video signal input, blue 视频输入,蓝色26 – Video signal input, red 视频输入,红色第 6 插座,天线连接1 – AM and FM2 radio reception aerial connector, double Fakra, no coding, impedance 50 ohms, colour cream-white (奶白插头无代码)2 – FM1 radio reception aerial connector, double Fakra, coding B, impedance 50 ohms, colour cream-white(奶白插头代码B)3 – Navigation aerial connector, double Fakra, coding C, impedance 50 ohms, colour signal blue GPS插座。

针脚定义及接口定义图解

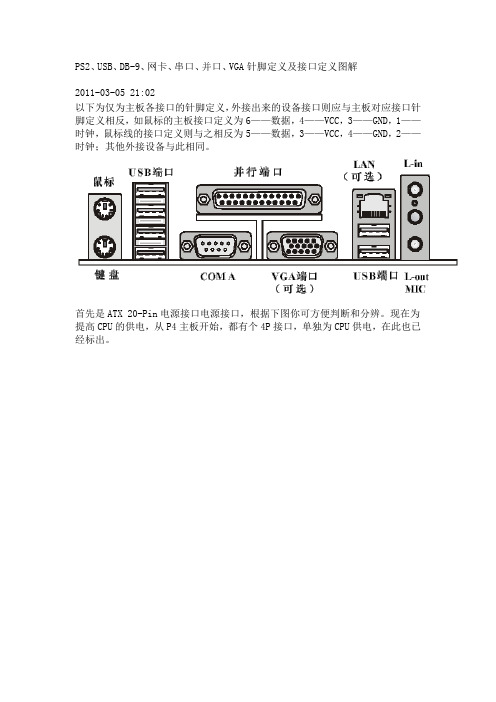

PS2、USB、DB-9、网卡、串口、并口、VGA针脚定义及接口定义图解2011-03-05 21:02以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1、DATA 数据信号2、空3、GND 地端4、+5V5、CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft 等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB 数据线而仅仅包含与电脑相连的“A”连接----USB接口提供5V和200ma电流Imax=500 mApc=500ma,笔记本100ma头)。

针脚定义及接口定义图解

PS2、USB、DB-9、网卡、串口、并口、VGA针脚定义及接口定义图解2011-03-05 21:02以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1、DATA 数据信号2、空3、GND 地端4、+5V5、CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft 等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB 数据线而仅仅包含与电脑相连的“A”连接----USB接口提供5V和200ma电流Imax=500 mApc=500ma,笔记本100ma头)。

USB接口针脚定义及详细说明(附图文说明)

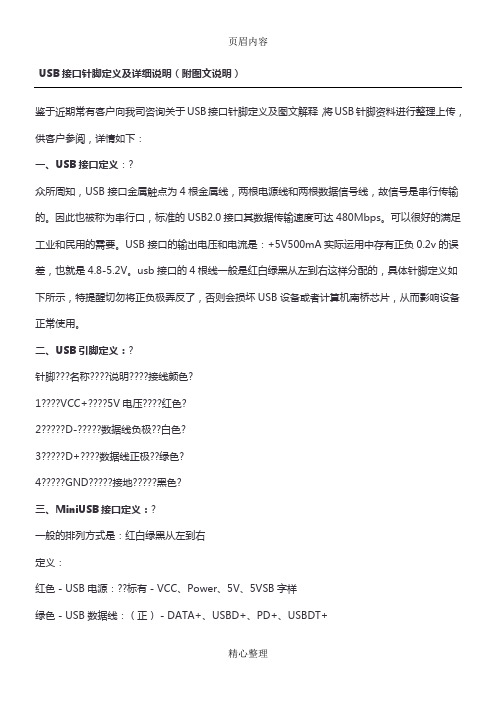

USB接口针脚定义及详细说明(附图文说明)鉴于近期常有客户向我司咨询关于USB接口针脚定义及图文解释,将USB针脚资料进行整理上传,供客户参阅,详情如下:一、USB接口定义:?众所周知,USB接口金属触点为4根金属线,两根电源线和两根数据信号线,故信号是串行传输的。

因此也被称为串行口,标准的USB2.0接口其数据传输速度可达480Mbps。

可以很好的满足工业和民用的需要。

USB接口的输出电压和电流是:+5V500mA实际运用中存有正负0.2v的误差,也就是4.8-5.2V。

usb接口的4根线一般是红白绿黑从左到右这样分配的,具体针脚定义如下所示,特提醒切勿将正负极弄反了,否则会损坏USB设备或者计算机南桥芯片,从而影响设备正常使用。

二、USB引脚定义:?针脚???名称????说明????接线颜色?1????VCC+????5V电压????红色?2?????D-?????数据线负极??白色?3?????D+????数据线正极??绿色?4?????GND?????接地?????黑色?三、MiniUSB接口定义:?一般的排列方式是:红白绿黑从左到右定义:红色-USB电源:??标有-VCC、Power、5V、5VSB字样绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+白色-USB数据线:(负)-DATA-、USBD-、PD-、USBDT+ 黑色-地线:??????GND、Ground四、MiniUSB引脚定义:?针脚????名称??????说明???????????接线颜色?1?????VCC+??????5V电压????????????红色?2?????D-??????数据线负极?????????白色3?????D+??????数据线正极?????????绿色?4?????ID????permitsdistinctionof?Micro-A-andMicro-B-Plug???noneTypeA:connectedtoGround?TypeB:notconnected?5?????GND???????接地????????????黑色插针管脚定义(图纸):其中ID脚通常为空,只有在OTG功能中才使用。

各种接口针脚含义

针脚 6 7 8 9

功能 数据准备好(DSR) 请求发送(RTS) 清除发送(CTS) 振铃指示(RI)

9针串行口的针脚功能

卡侬头、莲花头、插笔头

音频连接线,简称音频线,由音频电缆和连接头两部分组成,其中:音频电缆 一般为双 芯屏蔽电缆,连接头常见的有XLR(俗称卡侬头)、 RCA(俗称莲 花头)、TRS JACKS(俗 称插笔头)。

卡侬头、莲花头、插笔头

这些卡侬接口上都有标记1、2、3,按照上 图1、信号地,2、信号热端,3、信号冷端

RCA莲花接口我们最常见,因为 他被用于“民用设备”,一般的 卡式录音机都使用RCA接口。

卡侬头、莲花头、插笔头

Tip头:信号热端,Ring环: 信号冷端,Sleeve套管:信 号地

有些人总喜欢把TRS接口说 成所谓立体声插头,这恐怕 是因为我们常见的耳机使用 它。但是在这里它是用于声 音信号的平衡连接。

而非平衡接法就是仅用一条信号线传送信号的连接方法,由于这种接法容易 受到干扰,所以只一般在家用电器上或一些要求较低的情况下使用。

具体的接法以 XLR 接头为例: 1、平衡接法:1 脚接屏蔽,2 脚接+端(又称热端),3 脚接–端(又称冷端) 2、非平衡接法:1 脚和 3 脚相连接屏蔽,2 脚接+端(信号端)。 选择什么接法:根据设备对接口的具体要求而定,能使用平衡接法的尽量使 用平衡接法,进行连接时务必先看清面板上的说明,最好先阅读使用说明书上的 有关说明和要求。在 一些场合还可能遇到一端的设备接口是平衡接口,另一端的 设备是非平衡接口的情况,在要 求不很严格的情况,只需在平衡端使用平衡接法, 非平衡使用非平衡接法,注意各脚对应就 可以了。在要求严格的情况,就必须使 用转换电路将平衡转为非平衡,或将非平衡转为平衡。

USB接口针脚定义及详细说明(附图文说明)【范本模板】

USB接口针脚定义及详细说明(附图文说明)鉴于近期常有客户向我司咨询关于USB接口针脚定义及图文解释,将USB针脚资料进行整理上传,供客户参阅,详情如下:一、USB接口定义:众所周知,USB接口金属触点为4根金属线,两根电源线和两根数据信号线,故信号是串行传输的.因此也被称为串行口,标准的USB2.0接口其数据传输速度可达480Mbps。

可以很好的满足工业和民用的需要。

USB接口的输出电压和电流是:+5V 500mA 实际运用中存有正负0。

2v的误差,也就是4.8—5.2V 。

usb接口的4根线一般是红白绿黑从左到右这样分配的,具体针脚定义如下所示,特提醒切勿将正负极弄反了,否则会损坏USB设备或者计算机南桥芯片,从而影响设备正常使用。

二、USB引脚定义:针脚名称说明接线颜色1 VCC + 5V电压红色2 D- 数据线负极白色3 D+ 数据线正极绿色4 GND 接地黑色三、MiniUSB接口定义:一般的排列方式是:红白绿黑从左到右定义:红色-USB电源:标有-VCC、Power、5V、5VSB字样绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+白色-USB数据线:(负)-DATA—、USBD-、PD—、USBDT+黑色-地线: GND、Ground四、MiniUSB引脚定义:针脚名称说明接线颜色1 VCC + 5V电压红色2 D—数据线负极白色3 D+ 数据线正极绿色4 ID permits distinction ofMicro-A- and Micro—B—Plug noneType A:connected to GroundType B:not connected5 GND 接地黑色插针管脚定义(图纸):其中ID脚通常为空,只有在OTG功能中才使用。

由于Mini—USB接口分Mini—A、B和AB接口。

如果你的系统仅仅是用做Slave,那么就使用B接口。

系统控制器会判断ID脚的电平判断是什么样的设备插入,如果是高电平,则是B接头插入,此时系统就做主模式(master mode);如果ID为低,则是A接口插入,然后系统就会使用HNP对话协议来决定哪个做Master,哪个做Slave。

主板常用接口的针脚定义

主板常用接口的针脚定义注意:以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

刚接触电脑的朋友面对着计算机后背那密密麻麻的各种接口和一大把连接线往往会不知所措;接触电脑久的朋友有的时候想搞一些小点子,但常常会找不到各种接口的针脚定义;如果你有以上的经历,那么这一篇文章想必会给您带来一点帮助,那就是外部接口大集合。

首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1、DATA 数据信号2、空3、GND 地端4、+5V5、CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

主板各接口的针脚定义

注意: 注意: 以下为仅为主板各接口的针脚定义, 外接出来的设备接口则应与主板对 以下为仅为主板各接口的针脚定义, 应接口针脚定义相反, 如鼠标的主板接口定义为 6——数据,——VCC, ——数据 4——VCC 数据, VCC, 应接口针脚定义相反, ——数据 数据, 3——GND,1——时钟,鼠标线的接口定义则与之相反为 5——数据, ——GND, ——时钟, GND 时钟 3——VCC,4——GND,2——时钟;其他外接设备与此相同。

——VCC, ——GND, ——时钟;其他外接设备与此相同。

VCC GND 时钟刚接触电脑的朋友面对着计算机后背那密密麻麻的各种接口和一大把连接线往往会不知所措; 接触电脑久的朋友有的时候想搞一些小点子,但常常会找不到各种接口的针脚定义; 如果你有以上的经历,那么这一篇文章想必会给您带来一点帮助,那就是外部接口大集合。

首先是 ATX 20-Pin 电源接口电源接口, 根据下图你可方便判断和分辨。

现在为提 高 CPU 的供电,从 P4 主板开始,都有个 4P 接口,单独为 CPU 供电,在此也已经 标出。

鼠标和键盘绝大多数采用 PS/2 接口, 鼠标和键盘的 PS/2 接口的物理外观完全相 同,初学者往往容易插错,以至于业界不得不在 PC'99 规范中用两种不同的颜色 来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的 PS/2 接口 针脚定义我们就可以看出来。

上图的分别为 AT 键盘(既常说的大口键盘),和 PS2 键盘(即小口键盘),如 今市场上 PS2 键盘的数量越来越多了,而 AT 键盘已经要沦为昨日黄花了。

因为 键盘的定义相似,所以两者有共同的地方,各针脚定义如下: 1、DATA 数据信号 2、空 3、GND 地端 4、+5V 5、CLOCK 时钟 6 空(仅限 PS2 键盘) USB(Universal Serial Bus,通用串行总线)接口是由 Compaq、IBM、Microsoft 等多家公司于 1994 年底联合提出的接口标准,其目的是用于取代逐渐不适应外 设需求的传统串、并口。