06 认识Verilog HDL语言中的运算符和赋值语句

verilog 语法符号

verilog 语法符号Verilog是一种硬件描述语言,用于描述数字电路。

它包含了许多语法符号,下面我将从不同方面介绍Verilog的语法符号。

1. 模块定义符号。

在Verilog中,模块由module和endmodule关键字定义,例如: verilog.module my_module (。

input wire a,。

output reg b.);// 模块内部逻辑。

endmodule.2. 信号声明符号。

在Verilog中,信号可以是输入、输出或者内部信号,声明时使用不同的关键字,如:input,输入信号。

output,输出信号。

reg,寄存器类型的信号。

wire,连线类型的信号。

parameter,参数类型的信号。

3. 运算符号。

Verilog支持多种运算符,包括算术运算符(+、-、、/)、逻辑运算符(&&、||、!)、位运算符(&、|、^)、移位运算符(<<、>>)等。

4. 控制结构符号。

Verilog中的控制结构包括if-else、case、for循环等,它们使用特定的关键字和符号来实现逻辑控制。

5. 时序控制符号。

Verilog中用于描述时序逻辑的符号包括非阻塞赋值(<=)、时钟边沿敏感的触发器(posedge、negedge)等。

6. 注释符号。

在Verilog中,可以使用`//`进行单行注释,也可以使用`/ /`进行多行注释。

7. 实例化符号。

在Verilog中,可以通过实例化模块来创建层次结构,使用实例化符号`inst_name module_name()`来实例化一个模块。

以上是关于Verilog语法符号的一些介绍,希望对你有所帮助。

如果你还有其他关于Verilog语法符号的问题,欢迎继续提问。

verilog 运算符号

verilog 运算符号Verilog 是一种硬件描述语言(HDL),常用于数字电路的设计与验证。

在 Verilog 中,运算符是用于执行各种操作的特殊符号。

本文将介绍常用的 Verilog 运算符,包括算术运算符、位运算符、关系运算符、逻辑运算符、条件运算符和位选择运算符。

1. 算术运算符:- 加法:用 "+" 表示,例如 A + B- 减法:用 "-" 表示,例如 A - B- 乘法:用 "*" 表示,例如 A * B- 除法:用 "/" 表示,例如 A / B- 求余:用 "%" 表示,例如 A % B2. 位运算符:- 位与:用 "&" 表示,例如 A & B- 位或:用 "|" 表示,例如 A | B- 位异或:用 "^" 表示,例如 A ^ B- 位取反:用 "~" 表示,例如 ~A- 左移:用 "<<" 表示,例如 A << 1- 右移:用 ">>" 表示,例如 A >> 13. 关系运算符:- 等于:用 "==" 表示,例如 A == B- 不等于:用 "!=" 表示,例如 A != B- 大于:用 ">" 表示,例如 A > B- 大于等于:用 ">=" 表示,例如 A >= B- 小于:用 "<" 表示,例如 A < B- 小于等于:用 "<=" 表示,例如 A <= B4. 逻辑运算符:- 逻辑与:用 "&&" 表示,例如 A && B- 逻辑或:用 "||" 表示,例如 A || B- 逻辑非:用 "!" 表示,例如 !A5. 条件运算符:- 三目运算符:用 "?" 和 ":" 表示,例如 (A > B) ? A : B6. 位选择运算符:- 指定位置运算符:用 "[]" 表示,例如 A[3:0] 表示提取 A 中的3-0 位- 拼接运算符:用 "{}" 表示,例如 {A, B} 表示将 A 和 B 拼接在一起以上是 Verilog 中常用的运算符。

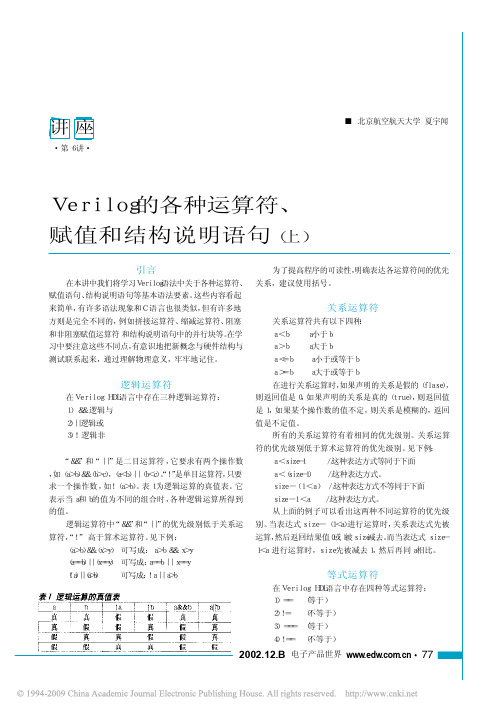

Verilog的各种运算符_赋值和结构说明语句_上_

设计技术782002.12.B 电子产品世界这四个运算符都是二目运算符,它要求有两个操作数。

“==”和“!=”又称为逻辑等式运算符。

其结果由两个操作数的值决定。

由于操作数中某些位可能是不定值x和高阻值z,结果可能为不定值x。

而“===”和“!==”运算符则不同,它在对操作数进行比较时对某些位的不定值x和高阻值z也进行比较,两个操作数必需完全一致,其结果才是1,否则为0。

“===”和“!==”运算符常用于case表达式的判别,所以又称为“case等式运算符”。

这四个等式运算符的优先级别是相同的。

表1列出==与===的真值,帮助理解两者间的区别。

下面举一个例子说明“==”和“===”的区别。

例:if(A==1’bx) ¥display(“AisX”); (当A等于X时,这个语句不执行)if(A===1’bx) ¥display(“AisX”); (当A等于X时,这个语句执行)移位运算符在Verilog HDL中有两种移位运算符:<< (左移位运算符) 和 >>(右移位运算符)。

其使用方法如下: a >> n 或 a << na代表要进行移位的操作数,n代表要移几位。

这两种移位运算都用0来填补移出的空位。

下面举例说明:module shift;reg [3:0] start, result;initialbeginstart = 1;//start在初始时刻设为值0001result = (start<<2); //移位后,start的值0100,然后赋给result。

endendmodule从上面的例子可以看出,start在移过两位以后,用0来填补空出的位。

进行移位运算时应注意移位前后变量的位数,下面给出一例。

例:4’b1001<<1 = 5’b10010; 4’b1001<<2 = 6’b100100;1<<6 = 32’b 1000000; 4’b 1001>>1 = 4’b 0100;4’b 1001>>4 = 4’b 0000;位拼接运算符(Concatation)在Verilog HDL语言有一个特殊的运算符:位拼接运算符{}。

了解VerilogHDL语法规则吗,看完这篇就知道了

了解VerilogHDL语法规则吗,看完这篇就知道了本节介绍Verilog HDL语法规则,包括文字规则、数据对象及运算符的使用等。

Verilog HDL文字规则1.关键词与标识符关键词是Verilog HDL中预先定义的单词,它们在程序中有特别的使用目的。

已经被用作关键词的单词不可以在程序中另作他用,见表3-1。

不同版本的Verilog HDL硬件描述语言中定义的关键词数目略有变化,Verilog 1995的关键词有97个,Verilog 2001共102个。

标识符是用户编程时给对象定义的名称,对象包括:常量、变量、模块、寄存器、端口、连线、示例和beginend块等元素。

定义标识符时应遵循如下规则:只能由26个大小写英文字母、数字和下划线组成。

标识符的第一个字符必须是英文字母或下划线。

字符中的英文字母区分大小写。

【例3-7】判断下面标识符是否合法。

2.注释与C语言一样,硬件描述语言中的注释也不会被编译。

在Verilog HDL中有两种形式的注释方式:采用/* */,多用于多行注释。

采用//,用于单行注释。

【例3-8】注释举例。

在实际使用中,很多公司的编程规范明确表明,注释行中不提倡采用第一种/**/的注释方式,不允许使用中文注释。

3.常数的表示在Verilog HDL中,常数用来表示在程序中不随意变化的量,常数分为整数、实数及字符串三大类型。

(1)整数型常数是数字电路中最常用到的类型,在Verilog HDL中有两种表示方法:简单的十进制格式,例如-50、6等。

基数格式,其表达方式一般如下:〈位宽〉是十进制数值表示的常数化成二进制时对应的宽度,〈进制符号〉用进制符号b或B(二进制)、o或O(八进制)、d或D(十进制)、h或H(十六进制)表示常数的进制格式,即二进制、八进制、十进制、十六进制这4种进制表示。

数字的位宽可以默认,如果没有定义长度,数的长度由具体机器系统决定(至少是32位)。

【例3-9】常数表示方法举例。

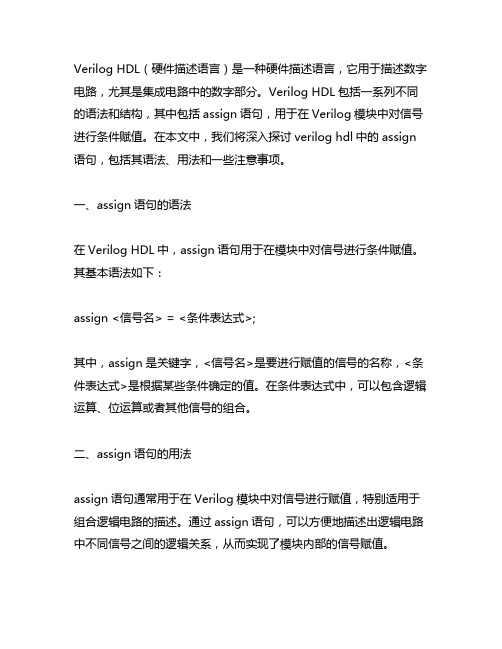

verilog hdl assign 条件赋值

Verilog HDL(硬件描述语言)是一种硬件描述语言,它用于描述数字电路,尤其是集成电路中的数字部分。

Verilog HDL包括一系列不同的语法和结构,其中包括assign语句,用于在Verilog模块中对信号进行条件赋值。

在本文中,我们将深入探讨verilog hdl中的assign 语句,包括其语法、用法和一些注意事项。

一、assign语句的语法在Verilog HDL中,assign语句用于在模块中对信号进行条件赋值。

其基本语法如下:assign <信号名> = <条件表达式>;其中,assign是关键字,<信号名>是要进行赋值的信号的名称,<条件表达式>是根据某些条件确定的值。

在条件表达式中,可以包含逻辑运算、位运算或者其他信号的组合。

二、assign语句的用法assign语句通常用于在Verilog模块中对信号进行赋值,特别适用于组合逻辑电路的描述。

通过assign语句,可以方便地描述出逻辑电路中不同信号之间的逻辑关系,从而实现了模块内部的信号赋值。

假设要实现一个2输入AND门的功能,可以使用assign语句如下所示:module and_gate(input wire a,input wire b,output wire y);assign y = a b;endmodule在这个例子中,使用了assign语句将信号y赋值为a与b的逻辑与操作的结果,从而实现了一个2输入AND门的功能。

另外,assign语句还可以用于实现信号的多路复用和分路功能。

通过在条件表达式中使用三元运算符,可以根据条件的不同选择不同的信号进行赋值,从而实现了信号的多路复用和分路。

三、assign语句的注意事项在使用assign语句时,需要注意以下几个问题:1. assign语句中不能出现时序逻辑。

因为assign语句是在模块实例化时就立即执行的,所以其中不能包含任何时序逻辑,例如时钟边沿敏感的触发器。

Verilog-HDL中的基本语法

一个完整的源程序都应当加上需要的注释, 以加强程序的可读性。

2.2 Verilog HDL的语法

2.2.1 空白符和注释

Verilog HDL的空白符包括空格、tab符号、换行 和换页。

空白符如果不是出现在字符串中,编译源程序 时将被忽略。

8. 条件操作符(Conditional operators)

条件操作符为:?:

条件操作符的操作数有3个,其使用格式为

操作数 = 条件 ? 表达式1:表达式2;

即当条件为真(条件结果值为1)时,操作数 = 表达式1;为假(条件结果值为0)时,操作数 = 表达 式2。

9. 位并接操作符(Concatenation operators) 并接操作符为:{} 并接操作符的使用格式: {操作数1的某些位,操作数2的某些位,…,操作数n 的某些位};

位运算操作符包括:~(按位取反)、&(按位与)、 |(按位或)、^(按位异或)、^~或~^(按位同或)。

在进行位运算时,当两个操作数的位宽不同时, 计算机会自动将两个操作数按右端对齐,位数少的操 作数会在高位用0补齐。

4. 关系操作符(Pelational operators)

关系操作符有:

<(小于)、<=(小于等于)、>(大于)、>=(大 于等于)。

② 每个模块首先要进行端口定义,并说明输入 (input)、输出(output)或双向(inouts),然 后对模块的功能进行逻辑描述。

③ Verilog HDL程序的书写格式自由,一行可以一 条或多条语句,一条语句也可以分为多行写。

④ 除了endmodule语句外,每条语句后必须要有 分号“;”。

VerilogHDL语言(PDF)

Verilog 讲义(二)1)续Verilog 基础2)Verilog 形为描述3.4 运算符九类运算符分类包含运算符算术运算符+ - * / %位运算符~ & | ^ ^~or~^缩位运算符& ~& | ~| ^ ^~or~^逻辑运算符! && ||关系运算符> < <= >=相等与全等运算符== != === !==逻辑移位运算符 <<>> 连接运算符 {}: 条件运算符 ?根据操作数的不同,又可分为三类:1)单目运算符只有一个操作数,且运算符位于操作数的左边如:~clk &a ~& 缩位运算符wire [7:0] aparity=^a (奇校验)2)双目运算符a+b a%b {a,b,c}3)三目运算符out=(sel)?a:b;运算符的优先级参:P443.4.1 算术运算符1)减法亦可用作单目运算符,取补运算2)除法运算符:整型类数据小数部分被截去: integer a=7/2=33)% 取余运算 7%2=13.4.2 位运算符1)~a 按位取反2)a&b 按位相与若a,b 位数不同,短的高位补0,(x者补x)3)^ ^~ 双目3.4.3 缩位运算符单目运算符,按位进行逻辑运算,结果产生一位的逻辑值。

A=4’b1001&a ~&a |a ~|a ^a ~^a0 1 1 0 1 0 3.4.3 逻辑运算符a&&b结果为一位的逻辑值若操作数为多位,只要有一位为1,整个操作数看作逻辑1;若有不定态,结果亦为不定态。

3.4.5关系运算符结果为一位的逻辑值。

3.4.6 相等与全等运算符结果为一位逻辑值相等:比较每一位,所有相等,关系满足,若有不定态或高阻态,不定态结果。

全等:与相等比较过程相同,亦将不定态及高阻态作为逻辑状态比较。

3.4.7 逻辑移位运算符<< >> 以0补位。

数字系统设计与verilog HDL 第6章

4.关系运算符(Relational operators) < 小于 <= 小于或等于 > 大于 >= 大于或等于

5.等式运算符(Equality Operators) == 等于 != 不等于 === 全等 !== 不全等

例:对于A=2'b1x和 B=2'b1x,则 A==B结果为x, A===B结果为1

关键字(Keywords)

Verilog语言内部已经使用的词称为关键字或

保留字,这些保留字用户不能作为变量或节点

名字使用。

关键字都是小写的。

6.2 常量

程序运行中,值不能被改变的量称为 常量(constants),Verilog中的常量主 要有如下3种类型:

◆ 整数 ◆ 实数

◆ 字符串

整数(integer)

字符串(Strings)

字符串是双引号内的字符序列。 字符串不能分成多行书写。例如:

"INTERNAL ERROR"

字符串的作用主要是用于仿真时,显示一些 相关的信息,或者指定显示的格式。

6.3 数据类型

数据类型(Data Type)是用来表示数字电路中的 物理连线、数据存储和传输单元等物理量的。

空白符和注释

空白符(White space) 空白符包括:空格、tab、换行和换页。空白符使 代码错落有致,阅读起来更方便。在综合时空白符 被忽略。 注释(Comment) ◆ 单行注释:以“//”开始到本行结束,不允许续 行 ◆ 多行注释:多行注释以“/*”开始,到“*/”结 束

标识符(Identifiers)

第6章 Verilog HDL语法与要素

主要内容

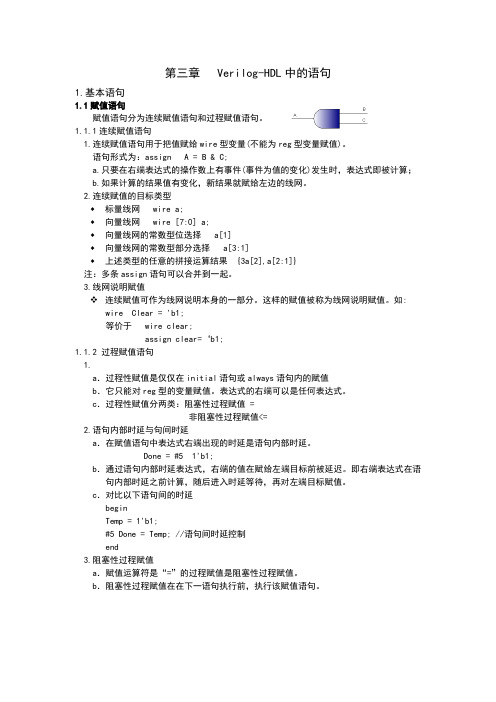

Verilog-HDL中的语句

第三章 Verilog-HDL中的语句1.基本语句1.1赋值语句赋值语句分为连续赋值语句和过程赋值语句。

1.1.1连续赋值语句1.连续赋值语句用于把值赋给wire型变量(不能为reg型变量赋值)。

语句形式为:assign A = B & C;a.只要在右端表达式的操作数上有事件(事件为值的变化)发生时,表达式即被计算;b.如果计算的结果值有变化,新结果就赋给左边的线网。

2.连续赋值的目标类型♦标量线网 wire a;♦向量线网 wire [7:0] a;♦向量线网的常数型位选择 a[1]♦向量线网的常数型部分选择 a[3:1]♦上述类型的任意的拼接运算结果 {3a[2],a[2:1]}注:多条assign语句可以合并到一起。

3.线网说明赋值连续赋值可作为线网说明本身的一部分。

这样的赋值被称为线网说明赋值。

如: wire Clear = 'b1;等价于 wire clear;assign clear=‘b1;1.1.2 过程赋值语句1.a.过程性赋值是仅仅在initial语句或always语句内的赋值b.它只能对reg型的变量赋值。

表达式的右端可以是任何表达式。

c.过程性赋值分两类:阻塞性过程赋值 =非阻塞性过程赋值<=2.语句内部时延与句间时延a.在赋值语句中表达式右端出现的时延是语句内部时延。

Done = #5 1'b1;b.通过语句内部时延表达式,右端的值在赋给左端目标前被延迟。

即右端表达式在语句内部时延之前计算,随后进入时延等待,再对左端目标赋值。

c.对比以下语句间的时延beginTemp = 1'b1;#5 Done = Temp; //语句间时延控制end3.阻塞性过程赋值a.赋值运算符是“=”的过程赋值是阻塞性过程赋值。

b.阻塞性过程赋值在在下一语句执行前,执行该赋值语句。

例:initialbeginClr = #5 0;Clr = #4 1;Clr = #10 0;end4.非阻塞性过程赋值a .在非阻塞性过程赋值中,使用赋值符号“ <=”。

verilog语法 运算符及表达式

verilog语法运算符及表达式运算符及表达式是Verilog语言中非常重要的概念,通过运算符和表达式,可以实现各种计算和逻辑操作。

本文将详细介绍Verilog 语言中常用的运算符及其使用方法,以及如何构建有效的表达式。

一、算术运算符算术运算符用于执行基本的数学运算,包括加法、减法、乘法和除法。

Verilog语言中的算术运算符与普通的数学运算符类似,包括加号(+)、减号(-)、乘号(*)和除号(/)。

例如,可以使用加法运算符计算两个变量的和:sum = a + b;其中,sum、a和b是变量,表示两个操作数和结果。

二、关系运算符关系运算符用于比较两个值之间的关系,包括等于(==)、不等于(!=)、大于(>)、小于(<)、大于等于(>=)和小于等于(<=)。

关系运算符通常用于条件语句或循环语句中,用于判断条件是否满足。

例如,可以使用等于运算符判断两个变量是否相等:if(a == b) begin// 代码块end三、逻辑运算符逻辑运算符用于执行逻辑操作,包括与(&&)、或(||)和非(!)。

逻辑运算符通常用于布尔表达式中,用于判断多个条件是否同时满足或者满足其中一个条件。

例如,可以使用与运算符判断两个条件是否同时满足:if(a && b) begin// 代码块end四、位运算符位运算符用于对二进制位进行操作,包括与(&)、或(|)、异或(^)和取反(~)。

位运算符通常用于处理数字的各个二进制位。

例如,可以使用与运算符将两个变量的对应二进制位进行与操作:result = a & b;其中,result、a和b是变量,表示两个操作数和结果。

五、赋值运算符赋值运算符用于将一个值赋给一个变量,包括等号(=)、加等(+=)、减等(-=)、乘等(*=)、除等(/=)等。

赋值运算符通常用于将计算结果保存到一个变量中。

例如,可以使用等号将一个变量的值赋给另一个变量:b = a;六、条件运算符条件运算符是一种特殊的运算符,用于根据条件选择不同的值。

system verilog 运算符

system verilog 运算符在system verilog中,运算符是用来进行各种数学和逻辑运算的符号。

运算符可以用于操作不同类型的数据,如整数、浮点数、数组等。

本文将介绍一些常见的system verilog运算符,并解释它们的用法和示例。

一、算术运算符1. 加法运算符(+):用于执行两个数的加法运算。

例如,a + b 表示a和b的和。

2. 减法运算符(-):用于执行两个数的减法运算。

例如,a - b 表示a和b的差。

3. 乘法运算符(*):用于执行两个数的乘法运算。

例如,a * b 表示a和b的乘积。

4. 除法运算符(/):用于执行两个数的除法运算。

例如,a / b 表示a除以b的结果。

5. 取余运算符(%):用于计算两个数相除后的余数。

例如,a % b 表示a除以b的余数。

二、关系运算符1. 相等运算符(==):用于判断两个数是否相等。

例如,a == b 表示a是否等于b。

2. 不等运算符(!=):用于判断两个数是否不相等。

例如,a != b 表示a是否不等于b。

3. 大于运算符(>):用于判断一个数是否大于另一个数。

例如,a >b 表示a是否大于b。

4. 小于运算符(<):用于判断一个数是否小于另一个数。

例如,a < b 表示a是否小于b。

5. 大于等于运算符(>=):用于判断一个数是否大于或等于另一个数。

例如,a >= b 表示a是否大于或等于b。

6. 小于等于运算符(<=):用于判断一个数是否小于或等于另一个数。

例如,a <= b 表示a是否小于或等于b。

三、逻辑运算符1. 与运算符(&&):用于对两个条件进行逻辑与运算。

例如,a &&b 表示a和b同时为真时,结果为真。

2. 或运算符(||):用于对两个条件进行逻辑或运算。

例如,a ||b 表示a和b中任意一个为真时,结果为真。

3. 非运算符(!):用于对一个条件进行逻辑非运算。

verilog 运算操作符号

Verilog运算操作符号一、概述在数字电路设计和硬件描述语言(HDL)中,运算操作符号是非常重要的,它们用来表示数字电路中的逻辑操作和数据处理。

Verilog是一种常用的硬件描述语言,其中也包含了丰富的运算操作符号,本文将对Verilog中常见的运算操作符号进行详细介绍。

二、赋值操作符号1. 阻塞赋值(=)阻塞赋值用“=”表示,在Verilog中用于将右侧表达式的值赋给左侧的变量。

阻塞赋值会在当前时间点立即执行,并且会导致模拟的并行行为。

2. 非阻塞赋值(<=)非阻塞赋值用“<=”表示,在Verilog中用于将右侧表达式的值赋给左侧的变量。

非阻塞赋值会延迟一个时间段后才执行,而且多个非阻塞赋值会按顺序执行,模拟的是时序逻辑。

三、逻辑运算操作符号1. 与操作()与操作符号“”用于执行逻辑与操作,对两个操作数的每一位执行与操作,只有两个操作数对应位都为1时结果才为1。

2. 或操作(|)或操作符号“|”用于执行逻辑或操作,对两个操作数的每一位执行或操作,只要两个操作数对应位中有一位为1,结果就为1。

3. 异或操作(^)异或操作符号“^”用于执行逻辑异或操作,对两个操作数的每一位执行异或操作,当两个操作数对应位相同时结果为0,不同时结果为1。

四、算术运算操作符号1. 加法操作(+)加法操作符号“+”用于执行加法操作,对两个操作数进行加法运算。

2. 减法操作(-)减法操作符号“-”用于执行减法操作,对两个操作数进行减法运算。

3. 乘法操作(*)乘法操作符号“*”用于执行乘法操作,对两个操作数进行乘法运算。

4. 除法操作(/)除法操作符号“/”用于执行除法操作,对两个操作数进行除法运算。

五、移位运算操作符号1. 左移操作(<<)左移操作符号“<<”用于将操作数向左移动指定的位数。

2. 右移操作(>>)右移操作符号“>>”用于将操作数向右移动指定的位数。

virilog语法总结

1、verilog特点:★区分大小写,所有关键字都要求小写★不是强类型语言,不同类型数据之间可以赋值和运算★ //是单行注释可以跨行注释★描述风格有系统级描述、行为级描述、RTL级描述、门级描述,其中RTL级和门级别与具体电路结构有关,行为级描述要遵守可综合原★门级描述使用门级模型或者用户自定义模型UDP来代替具体基本元件,在IDE中针对不同FPGA器件已经有对应的基本元件原语verlog语法要点2、语句组成:★ module endmodule之间由两部分构成:接口描述和逻辑功能描述★ IO端口种类: input output inout★相同位宽的输入输出信号可以一起声明, input[3:0] a,b; 不同位宽的必须分开写★内部信号为reg类型,内部信号信号的状态: 0 1 x z, 3‘bx1=3’bxx1 x/z会往左扩展 3‘b1=3’b001 数字不往左扩展★逻辑功能描述中常用assign描述组合逻辑电路,always既可以描述组合逻辑电路又可以描述时序逻辑电路,还可以用元件调用方法描述逻辑功能★ always之间、assign之间、实例引用之间以及它们之间都是并行执行,always内部是顺序执行3、常量格式: <二进制位宽><‘><进制><该进制的数值>:默认进制为10进制默认位宽为32位位宽是从二进制宽度角度而言的由位宽决定从低位截取二进制数2’hFF=2‘b11,通常由被赋值的reg变量位宽决定parameter常用于定义延迟和变量位宽,可用常量或常量表达式定义4、变量种类: wire reg memory① IO信号默认为wire类型,除非指定为reg类型(reg和wire 的区别)wire可以用作任何输入输出端口wire包括input output inoutwire不带寄存功能assign赋值语句中,被赋值的信号都是wire类型assign之所以称为连续赋值,是因为不断检测表达式的变化reg类型可以被赋值后再使用,而不是向wire一样只能输出reg类型变量初始值为xalways模块里被赋值的信号都必须定义为reg类型,因为always 可以反复执行,而reg表示信号的寄存,可以保留上次执行的值reg类型变量与integer变量不同,即使赋负值,实质上也是按二进制无符号数存储的,integer是有符号数verilog中所有内部信号都是静态变量,因为它们的值都在reg中存储起来② memory型只有一维数组,由reg型变量组成memory初始化只能按地址赋值,不能一次性赋值1*256的memory写法: reg mema[255:0] mema[3]=0; 不同位宽的变量之间赋值,处理之前都以被赋值的变量位宽为准扩展或截取A[a:b] 无论a b谁大,a总是实际电路的信号高位,b总是实际电路的信号低位算术运算中如果有X值则结果为Xfor循环中的变量另外定义成integer,因为它不是实际信号,有正负;reg则以无符号数存在5、运算符(其他简单的书上有自己看)== 和!=只比较0、1,遇到z或x时结果都为x (x在if中算做假条件),结果可能是1、0、x===和!==比较更加苛刻,包括x和z的精确比较,结果可能是0、1 &&的结果只有1‘b1或1’b0两种, A&A的结果位宽则是与A相同的{1,0}为 64‘h100000000,所以拼接运算中各信号一定要指定位宽移位运算左移将保留 4'b1000<<1等于5'b10000,右移则舍弃 4'b0011等于4'b0001数字电路里位运算应用普遍,包括按位逻辑运算、移位运算、拼接运算、缩减运算6、非阻塞式赋值<=与阻塞式赋值=(比较)阻塞:在同一个always过程中,后面的赋值语句要等待前一个赋值语句执行完,后面的语句被该赋值语句阻塞非阻塞:在同一个always过程中,非阻塞赋值语句是同时进行的,排在后面的语句不会被该赋值语句阻塞<=:块结束后才能完成赋值块内所有<=语句在always块结束时刻同时赋值<=右边各变量的值是上一次时钟边沿时,这些变量当时的值用于描述可综合的时序电路=:=语句结束之后过程always才可能结束在always过程中,begin end块内按先后顺序立即赋值,在fork join内同时赋值(可能造成冲突)与assign连用描述组合电路begin end中阻塞的含义:begin ...@(A) B=C...; end 如果A事件不发生则永远不能执行下去,被阻塞了由于时钟的延时(往往在ps级),多个always(posedge)之间究竟谁先执行是个未知数使用八原则:(1)时序电路建模时,采用非阻塞赋值(2)锁存器电路建模时,采用非阻塞赋值。

有关Verilog 中的一些语法

有关Verilog 中的一些语法位运算符1) ~ //取反2) & //按位与3) | //按位或4) ^ //按位异或5) ^~ //按位同或(异或非)逻辑运算符在Verilog HDL语言中存在三种逻辑运算符:1) &&逻辑与2) || 逻辑或3) !逻辑非等式运算符在Verilog HDL语言中存在四种等式运算符:1) == (等于)2) != (不等于)3) === (等于)4) !== (不等于)"=="和"!="又称为逻辑等式运算符。

其结果由两个操作数的值决定。

由于操作数中某些位可能是不定值x和高阻值z,结果可能为不定值x。

而"==="和"!=="运算符则不同,它在对操作数进行比较时对某些位的不定值x和高阻值z也进行比较,两个操作数必需完全一致,其结果才是1,否则为0。

"==="和"!=="运算符常用于case表达式的判别,所以又称为"case等式运算符"。

位移运算符左移:右边的添0右移:左边的添0,移除的位舍去举例:4’b1001<<1 = 5’b10010; 4’b1001<<2 = 6’b100100;1<<6 = 32’b1000000; 4’b1001>>1 = 4’b0100; 4’b1001>>4 = 4’b0000;位拼接运算符1.{a,b[3:0],w,3’b101}也可以写成为{a,b[3],b[2],b[1],b[0],w,1’b1,1’b0,1’b1}2.{4{w}} //这等同于{w,w,w,w}3.{b,{3{a,b}}} //这等同于{b,a,b,a,b,a,b}负数:一个数字可以被定义为负数,只需在位宽表达式前加一个减号,减号必须写在数字定义表达式的最前面。

硬件描述语言VerilogHDL基础

入zz x x x

CSLG

4、设计举例

试用Verilog语言的门级 元件描述2线-4线译码器.

E1

& Y0

//Gate-level description of a 2-to-4-

line decoder

module _2to4decoder (A1,A0,E,Y);

input A,B,E;

output [3:0] Y;

常量

格式为:<+/-><位宽>’<基数符号><数 例值如>:3’b101、5’o37、8’he3,8’b1001_0011

实数型常量 十进制记数法 如: 0.1、2.0、5.67

科学记数法 如: 23_5.1e2、5E-4

23510.0、 0.0005

CSLG

❖Verilog允许用参数定义语句定义一个标识 符来代表一个常量,称为符号常量。

CSLG

CSLG

用Verilog HDL描述组合逻辑电路

用VerilogHDL描述组合逻辑电路

❖用VerilogHDL描述组合逻辑电路有三种不 同抽象级别:

▪ 门级描述 ▪ 数据流描述 ▪ 行为级描述

❖VerilogHDL描述的电路就是该电路的 VerilogHDL模型。

CSLG

•门级描述:

一般使用Primitive(内部元件)、自定义的下层模块对电 路描述。主要用于层次化设计中。

多输入端的或非门

多输入端的异或非门

多输出端的反相器

控制信号高电平有效的 三态反相器

控制信号低电平有效的 三态反相器

CSLG

Verilog 基本门级元件

and n-input AND gate

verilog课件 赋值语句课件例程

• • • • • • • • • • • •

module fbosc1 (y1, y2, clk, rst); output y1, y2; input clk, rst; reg y1, y2; always @(posedge clk or posedge rst) if (rst) y1 = 0; // reset else y1 = y2; always @(posedge clk or posedge rst) if (rst) y2 = 1; // preset else y2 = y1; endmodule 依据IEEE Verilog标准,这两个always块可以以任意的次 序执 • 行。如果在reset后第一个块先被执行,结果将是y1和y2 都获 • 得赋值1;如果在reset后第二个块先被执行,结果将是y1 和y2 • 都被赋值0。这个例子清楚地展示了一个Verilog竞争条件

【例6-15】连续赋值语句的例子。 例 module or_by_cont_assignment(c,a,b); input a,b; output c; assign c=a|b; endmodule

【例6-16】与例6-15等价的描述。 例 module or_by_proc_assignment(c,a,b); input a,b; output c; reg c; initial begin c=x; end always @(a or b) c=a|b; endmodule //always过程块用于更新c的取值 //initial过程块用于对c赋初值

连续赋值的目标类型

• 在在实际使用中,连续赋值语句的赋值目标 可 • 以是如下几种: • (1) 标量连线型变量。如

• wire a,b; • assign a = b;

veriloga语法规则

Verilog是一种硬件描述语言,用于描述数字电路和系统。

以下是Verilog语法规则的一些要点:

标识符:Verilog中的标识符由字母、数字和下划线组成,且第一个字符必须是字母或下划线。

标识符区分大小写。

数据类型:Verilog中有多种数据类型,包括wire、reg、int、parameter等。

wire类型用于表示线网,reg类型用于表示寄存器。

赋值语句:Verilog中的赋值语句使用“=”操作符,例如“a = b”。

运算符:Verilog中有多种运算符,包括算术运算符、逻辑运算符、关系运算符等。

控制结构:Verilog中有条件语句、循环语句等控制结构。

模块:Verilog中的模块是自顶向下的设计方法的核心,用于描述数字电路和系统。

模块的语法包括模块声明、端口声明、内部信号声明、过程块和实例化等部分。

时序控制:Verilog中的时序控制使用非阻塞赋值和延迟表达式。

参数:Verilog中的参数用于在模块之间传递值。

任务和函数:Verilog中的任务和函数用于执行特定的操作。

注释:Verilog中的注释使用“//”或“/* */”进行注释。

这些是Verilog语法规则的一些要点,如果您想了解更多细节,建议参考Verilog的相关书籍或文档。

Verilog硬件描述语言(二)三目运算符

要点 :

不使用初始化语句,不使用任务和函数 不使用带有延时的描述 不使用for循环 在always里面慎用乘法和除法

~ | ^~,~^

按位取反 按位或 按位同或

& ^

按位与 按位异或

& 0 1 x

0 0 0 0

1 0 1 x

x 0 x x

| 0 1 x

0 0 1 x

1 1 1 1

x x 1 x

^ 0 1 x

0 0 1 x

1 1 0 x

x x x x

按位与真值表

按位或真值表

按位异或真值表

关系运算符 (Relational operator)

移位运算符

>> << 用法:

(Shift operator)

右移 左移

移位操作符只有两个:左移和右移 A>>n或A<<n; 表示把操作数右移或左移n位;移出的位用0添补

条件运算符

(Conditional operator)

?

这是一个三目运算符,对3个操作数进行运算。 用法: signal=condition?true_expression:flase_expression;

举例 :七段数码管显示译码器

module decode4_7(decodeout,indec); output[6:0] decodeout; input[3:0] indec; reg[6:0] decodeout; always @(indec) begin

end endmodule

case(indec) 4'd0: decodeout=7'b1111110; 4'd1: decodeout=7'b0110000; 4'd2: decodeout=7'b1101101; 4'd3: decodeout=7'b1111001; 4'd4: decodeout=7'b0110011; 4'd5: decodeout=7'b1011011; 4'd6: decodeout=7'b1011111; 4'd7: decodeout=7'b1110000; 4'd8: decodeout=7'b1111111; 4'd9: decodeout=7'b1111011; default: decodeout=7'b1111111; endcase

verilog常用逻辑运算符

请您及时更换请请请您正在使用的模版将于2周后被下线请您及时更换

verilog常 用 逻 辑 运 算 符

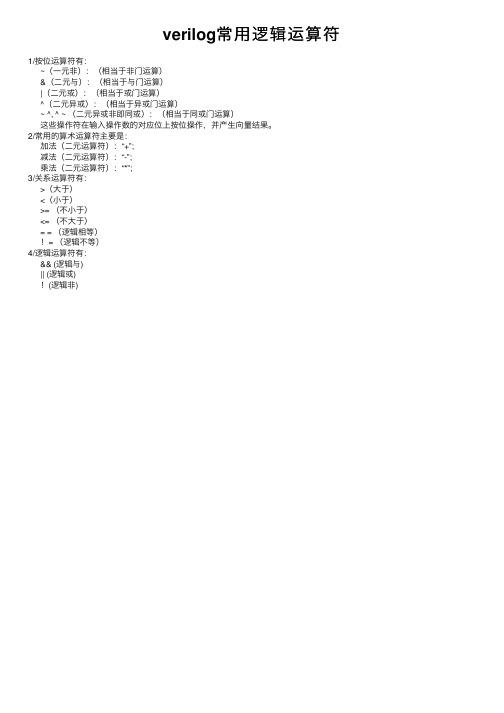

1/按位运算符有: ~(一元非):(相当于非门运算) &(二元与):(相当于与门运算) |(二元或):(相当于或门运算) ^(二元异或):(相当于异或门运算) ~ ^, ^ ~ (二元异或非即同或):(相当于同或门运算) 这些操作符在输入操作数的对应位上按位操作,并产生向量结果。

2/常用的算术运算符主要是: 加法(二元运算符):“+”; 减法(二元运算符):“-”; 乘法(二元运算符):“*”;

3/关系运算符有: >(大于) <(小于) >= (不小于) <= (不大于) = = (逻 (逻辑与) || (逻辑或) !(逻辑非)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

位运算符

1) "取反"运算符~ ~是一个单目运算符,用来对一个操作数

进行按位取反运算。 其运算规则见下表:

位运算符

2) "按位与"运算符& 按位与运算就是将两个操作数的相应位进行

与运算, 其运算规则见下表:

位运算符

3) "按位或"运算符| 按位或运算就是将两个操作数的相应位进行

或运算。 其运算规则见下表:

移位运算符

在Verilog HDL中有两种移位运算符: << (左移位运算符) 和 >>(右移位运算符)。 其使用方法如下: a >> n 或 a << n

位拼接运算符

• 在Verilog HDL语言有一个特殊的运算符:位 拼接运算符{}。用这个运算符可以把两个或 多个信号的某些位拼接起来进行运算操作。 其使用方法如下:

逻辑运算的真值

关系运算符

关系运算符共有以下四种: a < b a小于b a > b a大于b a <= b a小于或等于b a >= b a大于或等于b

等式运算符

在Verilog HDL语言中存在四种等式运算符: 1) == (等于) 2) != (不等于) 3) === (等于) 4) !== (不等于)

位运算符

4) "按位异或"运算符^(也称之为XOR运算符) 按位异或运算就是将两个操作数的相应位进

行异或运算。 其运算规则见下表:

位运算符

5) "按位同或"运算符^~ 按位同或运算就是将两个操作数的相应位先进行异或

运算再进行非运算. 其运算规则见下表:

逻辑运算符

在Verilog HDL语言中存在三种逻辑运算符: 1) && 逻辑与 2) || 逻辑或 3) ! 逻辑非

• {信号1的某几位,信号2的某几位,..,..,信号 n的某几位}

缩减运算符

缩减运算符是单目运算符 。缩减运算的 具体运算过程是这样的:第一步先将操作数 的第一位与第二位进行或与非运算,第二步 将运算结果与第三位进行或与非运算,依次 类推,直至最后一位。

缩减运算符

例如:reg [3:0] B; reg C; C = &B; 相当于: C =( (B[0]&B[1]) & B[2] ) & B[3];

(b)图中,当执行“x<=next_x;”时,并不会阻断语句“y<=x;”的 执行。因此,语句“y<=x;”中的x的值与语句“x<=next_x;”中的x 的值不同:语句“y<=x;”中的x是第一个D触发器的初值(Q0)。而 语句“x<=next_x;”中的x的值是D触发器经过一个同步脉冲后的输出 值(Q1)。基于此这个进程产生了与阻塞赋值进程截然不同的结果, 即:产生了移位寄存器的效果。

基本的算术运算符

算术运算符又称为二进制运算符,共有下面几种: 1) + (加法运算符,或正值运算符,如 rega+regb,

+3) 2) - (减法运算符,或负值运算符,如 rega-3,

-3) 3) × (乘法运算符,如rega*3) 4) / (除法运算符,如5/3) 5) % (模运算符,或称为求余运算符,要求%两

优先级别

关键词

在Verilog HDL中,所有的关键词是事先 定义好的确认符,用来组织语言结构。关键 词是用小写字母定义的,因此在编写原程序 时要注意关键词的书写,以避免出错。

关键词

always, and, assign,begin,buf,bufif0,bufif1,case, casex,casez,cmos,deassign,default,defparam,disable, edge,else,end,endcase,endmodule,endfunction, endprimitive, endspecify, endtable, endtask, event, for, force, forever, fork, function,highz0, highz1, if,initial, inout, input,integer,join,large,macromodule,medium, module,nand,negedge,nmos,nor,not,notif0,notifl, or, output, parameter, pmos, posedge, primitive, pull0, pull1, pullup, pulldown, rcmos, reg, releses, repeat, mmos, rpmos, rtran, rtranif0,rtranif1,scalared,small,specify,specparam,strength, strong0, strong1, supply0, supply1, table, task, time, tran, tranif0, tranif1, tri, tri0, tri1, triand, trior, trireg,vectored,wait,wand, weak0,weak1,while, wire,wor, xnor, xor

1) 赋值语句执行完后,块才结束。 2) b的值在赋值语句执行完后立刻就改变的。 3) 可能会产生意想不到的结果。

两种赋值语句的对比

(a)阻塞赋值 值

(b)非阻塞赋

(a)图中,当执行“x=next_x;”时,x会立即得到next_x的值。而下 一句“y=x;”必须等到“x=next_x;”执行完毕才能被执行。由于这 两条语句都没有延迟(相当于导线),导致他们的等价语句为 “y=next_x;”。赋值是实时的,计算完右面的马上赋值给左边的,然 后再执行下一句,操作是串行的,且在一个alway内完成。

赋值语句

赋值语句 在Verilog HDL语言中,信号有两种赋值方式: (1).非阻塞(Non_Blocking)赋值方式( 如 b <= a; ) 1) 块结束后才完成赋值操作。 2) b的值并不是立刻就改变的。 3) 这是一种比较常用的赋值方法。(特别在

编写可综合模块时)

赋值语句

(2).阻塞(Blocking)赋值方式( 如 b = a; )

运算符及表达式

运算符类型

按其功能可分为以下几类:

• 1) 算术运算符(+,-,×,/,%) • 2) 赋值运算符(=,<=) • 3) 关系运算符(>,<,>=,<=) • 4) 逻辑运算符(&&,||,!) • 5) 条件运算符(?:) • 6) 位运算符(~,|,^,&,^~) • 7) 移位运算符(<<,>>) • 8) 拼接运算符({ }) • 9) 其它

侧均为整型数据。如7%3的值为1)

位运算符

Verilog HDL作为一种硬件描述语言,是针对硬件 电路而言的。在硬件电路中信号有四种状态值 1,0,x,z.在电路中信号进行与或非时,反映在 Verilog HDL中则是相应的操作数的位运算。 Verilog HDL提供了以下五种位运算符: 1) ~ //取反 2) & //按位与 3) | //按位或 4) ^ //按位异或 5) ^~ //按位同或(异或非)

运算符类型

按其所带操作数的个数运算符可分为三种:

1) 单目运算符(unary operator):可以带一个操作数, 操作数放在运算符的右边。

2) 二目运算符(binary operator):可以带二个操作 数,操作数放在运算符的两边。

3) 三三目运算符分隔开。