MOS芯片的ESD保护电路设计

芯片IO缓冲及ESD设计

芯片I/O缓冲及ESD电路设计摘要:文章详细介绍了基于C MOS的芯片I/O缓冲电路分类,功能,电路及版图设计的一些考虑以及芯片引脚的静电保护问题。

广告插播信息维库最新热卖芯片:ST10043QC IRFR024N SMBJ5.0CA XC17S10PD8C ICL7612BCPA TC35302P2 4LC128T-I/SN TC551001BFL-85L PQ30RV21UPD485505G-35关键词:I/O;缓冲电路;静电保护;CMOS针对引脚的输入输出缓冲(I/O buffer)电路设计,也可以称为输入输出接口(I/O interface)电路设计,是一颗完整芯片设计中不可或缺的组成部分,但是详细论述其设计规则的文章或者著作在国内却比较鲜见,这对初学者或者没有这方面经验的工程师无疑会造成困惑。

本文以CMOS工艺为例,较全面的论述I/O缓冲电路设计中各种考虑,可以作为芯片引脚输入输出电路设计的一个参考。

根据I/O缓冲电路应用目标的不同,可将其分为输入、输出等几类,详见表1。

表1 I/O缓冲电路的分类输出缓冲(是个大驱动器,他将信号输出芯片)输出缓冲电路的功能要求能够驱动大的片外负载,通常为2~50pF,并且提供适当的上升/下降时间。

一组连续的大尺寸的缓冲器(buffer)对驱动能力的提高是有益的。

大尺寸的管子容易受闩锁效应(latch-up)的影响,在版图设计时建议采用保护环(Guardrings)保护以避免闩锁效应,如图1-1所示。

在图中,用P+作为内保护环,而N+作为外保护环(In n-well)。

图1-1缓冲器一种常见的输出电路如图1-2所示,En是输出电路的使能信号,Dout是输出数据,MOS管组合的功能如图中所示。

当En为低而Dout有效时,A、B均为高电平,输出Y为低,且由外向里看为高阻抗状态,如果Dout未定,则Y为高阻。

需要注意的是,最后输出级的管子尺寸要大到能够提供足够的电流源或电流沉并且减少延迟时间。

CMOS片上电源总线ESD保护结构设计_王怡飞

CMOS 片上电源总线ESD 保护结构设计王怡飞,胡新伟,郭立(中国科学技术大学电子科学与技术系,合肥230027)摘要:随着集成电路制造技术的高速发展,特征尺寸越来越小,静电放电对器件可靠性的危害也日益增大,E SD 保护电路设计已经成为IC 设计中的一个重要部分。

讨论了三种常见的CMOS 集成电路电源总线E SD 保护结构,分析了其电路结构、工作原理和存在的问题,进而提出了一种改进的ESD 保护电源总线拓扑结构。

运用HSPICE 仿真验证了该结构的正确性,并在一款自主芯片中实际使用,ESD 测试通过±3000V 。

关键词:静电放电;电源总线;保护电路中图分类号:TN402;TN403 文献标识码:A 文章编号:1003-353X (2008)06-0524-03Power Bus ESD Protection Structure Design in CMOS ICWang Yifei ,Hu Xinwei ,Guo Li(Dept .o f Electronic Science and Technolo gy ,USTC ,Hefei 23007,China )A bstract :With the development of VLSI process ,the character dimension is getting smaller and smaller while the damage of electrostatic discharge is markedly incr easing in the MOS device reliability ,ESD pr otection circuit becomes an important part of IC design .Three common power bus ESD protection structures in C MOS IC were discussed ,the circuit structure and working theories wer e analyzed ,an improved power bus ESD protection structure was put for ward .The simulation result with HSPI CE proves its correction and the structure is used in an independence chip ,which has passed ±3000V E SD tests .Key words :E SD ;power bus ;protection circuit EEAC C :2570D ;0170N图1 IC 失效原因统计Fig .1 Distribution of failure modes in ICs0 引言随着IC 特征尺寸的日益缩小和集成规模的飞速提高,静电放电(E SD ,electrostatic discharge )保护电路的设计已经成为集成电路可靠性设计中的一个重要环节。

esd保护电路

CMOS电路中ESD保护结构的设计上海交通大学微电子工程系王大睿1 引言静电放电(ESD,Electrostatic Discharge)给电子器件环境会带来破坏性的后果。

它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,互补金属氧化物半导体(CMOS,ComplementaryMetal-Oxide Semiconductor)的特征尺寸不断缩小,金属氧化物半导体(MOS,Metal-Oxide Semiconductor)的栅氧厚度越来越薄,MOS管能承受的电流和电压也越来越小,因此要进一步优化电路的抗ESD性能,需要从全芯片ESD保护结构的设计来进行考虑。

2 ESD的测试方法ESD模型常见的有三种,人体模型(HBM,Hu-man Body Model)、充电器件模型(CDM,Charge DeviceModel)和机器模型(MM,Machine Mode),其中以人体模型最为通行。

一般的商用芯片,要求能够通过2kV静电电压的HBM检测。

对于HBM放电,其电流可在几百纳秒内达到几安培,足以损坏芯片内部的电路。

,所以对I/O引脚会进行以下六种测试:1) PS模式:VSS接地,引脚施加正的ESD电压,对VSS放电,其余引脚悬空;2) NS模式:VSS接地,引脚施加负的ESD电压,对VSS放电,其余引脚悬空;3) PD模式:VDD接地,引脚施加正的ESD电压,对VDD放电,其余引脚悬空;4) ND模式:VDD接地,引脚施加负的ESD电压,对VDD放电,其余引脚悬空;5) 引脚对引脚正向模式:引脚施加正的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空;6) 引脚对引脚反向模式:引脚施加负的:ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空。

VDD引脚只需进行(1)(2)项测试3 ESD保护原理ESD保护电路的设计目的就是要避免上作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。

一种ESD保护电路的版图设计

课程名称:集成电路版图设计穿、抗闩锁、寄生小、面积小、工艺兼容等特点[6,7],且在深亚微米互补性氧化金属半导体CMOS工艺中,ESD保护电路由于要承受大电流或大电压的保护,通常把管子做得比较大,以实现I/O输入输出ESD保护、电源钳位ESD 保护和轨到轨ESD保护。

因此ESD保护电路的设计需要结合实际情况与应用需求,再综合考虑以上各个因素,才能设计出具有较好鲁棒性指标的保护电路。

除了要有较好鲁棒性的ESD保护电路外,我们还需注意一些外接引脚所引起的静电效应,做到电路(软件)和硬件的完美结合。

在集成电路的引脚中,除了少数一些自己能抵抗ESD 的引脚外,我们都需要将他们接到衬底或扩散层上去,比如说NPN 管的集电极,这些面积较大的结能在静电荷聚积到足以破坏器件之前吸收掉它们。

而在提供电源或大功率的引脚上,我们可以多接一些扩散层。

又由于那些直接连接到MOS 管栅极的的引脚很容易形成ESD 的介电体,因此必须有一些特别的保护结构设计在这些引脚上,比如我们可以用一些大的电阻(500Ω~5KΩ)或者是使电流不经过没有任何连接的发射极而直接接到外部的衬底上[8]。

3.2传统的静电保护电路和版图设计传统的方法是利用了TVS二极管的特性来保护电路免受ESD的冲击。

TVS全称是瞬态抑制二极管(Transient V oltage Suppressor),是一种二极管形式的高效能保护器件。

当TVS二极管的两极受到反向瞬态高能量冲击时,它能以10的负12次方秒量级的速度,将其两极间的高阻抗变为低阻抗,吸收高达数千瓦的浪涌功率,使两极间的电压箝位于一个预定值,有效地保护电子线路中的精密元器件,免受各种浪涌脉冲的损坏。

图1 电路中的TVS二极管如图2所示,传统的静电保护电路一般设计在芯片的管脚旁边,静电保护源和地,这样保证PMOS 和NMOS 在芯片正常工作时候处于关闭状态,这种类型的静电保护电路存在二个寄生二极管(TVS),当IO 到VCC 放生正静电时候,静电通过上面的寄生二极管正向通道泄放,当IO 到GND发生正静电时候,N+(漏端)-P+(衬底)-N+(源端)形成寄生NPN,静电通过这个寄生三极管泄放,当IO 到GND 发生负静电时候,静电通过下面的寄生二极管正向导通泄放,当IO 到VCC 放生负静电时候,静电没有合适的泄放通路。

大功率mos管驱动保护电路

一、引言随着电子技术的飞速发展,大功率MOS管在工业、军事、民用等领域得到了广泛应用。

然而,由于MOS管的特性,使用不当很容易导致其损坏,甚至危及设备和人员安全。

因此,设计一种可靠的保护电路,对于确保MOS管的正常工作和延长其寿命具有重要意义。

本文将介绍一种基于大功率MOS管的驱动保护电路,主要包括电流保护、过压保护、过温保护和ESD保护四个方面。

二、电流保护电流保护是防止MOS管过电流损坏的主要手段。

一般来说,电流过大会导致MOS管发热严重,从而对其内部结构产生不可逆的损伤。

因此,需要通过设置合理的电流限制值和保护电路来保护MOS 管。

具体实现方式如下:1.1 电流检测在MOS管的源极和负载之间增加一个小电阻,通过检测该电阻两端的电压来实现对MOS管的电流监测。

为了减小误差,可以采用差分放大器、精密电阻等器件进行检测。

1.2 电流限制当检测到MOS管电流超过设定值时,可以通过控制信号,直接将MOS管的驱动电压降低或关闭MOS管,以保护其不受过电流损伤。

三、过压保护过压保护是保护MOS管免受过高电压损害的重要手段。

在实际应用中,由于干扰、电源波动等因素,系统中可能会出现过压情况,如果MOS管无法承受这样的压力,就会导致其损坏。

具体实现方式如下:2.1 过压检测通过设置一个合适的过压检测电路,来监测系统中的电压变化情况。

一旦检测到过压情况,则需要立即采取相应的保护措施。

2.2 过压保护当检测到过压情况时,可以通过控制信号,直接将MOS管的驱动电压降低或关闭MOS管,以避免其受到过高的电压影响。

四、过温保护过温保护是保护MOS管免受高温损害的重要手段。

由于工作环境的限制,MOS管在高温环境下长时间工作会导致其内部结构损坏或退化,影响其寿命和性能。

具体实现方式如下:3.1 温度检测通过设置一个合适的温度检测电路,来监测MOS管周围的温度变化情况。

可以采用热敏电阻、热敏电偶等器件进行检测,并将其转换为电信号。

MOS芯片的ESD保护电路设计

MOS芯片的ESD保护电路设计ESD(Electrostatic Discharge)保护电路是在MOS芯片设计中非常重要的一部分,其主要作用是保护芯片免受静电放电和其他电压干扰引起的损坏。

在设计ESD保护电路时,需要考虑静电放电的强度、放电路径、放电时间以及芯片的特性。

本文将详细介绍MOS芯片的ESD保护电路设计。

首先,设计ESD保护电路需要了解芯片的工作电压范围和工作环境。

这些参数将决定所需的ESD保护等级和保护电路的设计方案。

通常,ESD保护电路需要满足以下几个基本要求:1.渠道长度匹配:ESD保护电路通常需要使用多个MOS管来承受ESD电流。

为了提高保护效果,这些MOS管的渠道长度应该尽量相等,以保证它们可以均匀分担ESD电流。

在设计过程中,可以采用各种技术来实现渠道长度匹配,例如采用仿射布局或者通过电路设计巧妙应用。

2.延迟时间:ESD保护电路需要尽快响应ESD事件,并将电压降低到安全的范围内。

因此,保护电路的响应时间应该尽量短,以确保芯片能够在ESD事件发生时快速响应,避免损坏。

延迟时间通常可以通过选择合适的电阻和电容参数来调整。

3.低电压降:在ESD事件中,保护电路需要将电压降低到芯片所能接受的安全范围内,以避免芯片受损。

为了实现低电压降,通常会采用多级级联的保护结构,通过分级响应来降低电压。

此外,选择合适的电阻和电容参数也可以帮助减小电压降。

4.高可靠性:ESD保护电路需要能够经受多次击打,无损耗或自愈。

因此,在设计中需要使用具有较高可靠性的器件和元件。

例如,可以采用具有低漏电流和高耐压能力的二极管、MOSFET等元件。

在具体的ESD保护电路设计中,常用的保护结构包括二极管保护、级联保护和母线保护等。

例如,二极管保护方法主要通过将二极管连接在输入和输出之间来分散ESD放电能量,以提供保护。

级联保护方法则通过将多个保护器件级联并设置适当的门控电压来提高保护效果。

除了以上核心的保护电路设计,还可以采取一些其他的措施来增强芯片的ESD保护能力。

ESD保护版图设计

摘要静电放电(简写为ESD)是集成电路(简写为IC)在制造、运输、以及使用过程中经常发生并导致IC芯片损坏或失效的重要原因之一。

工业调查表明大约有40%的IC失效与ESD/EOS(过强的电应力)有关。

因此,为了获得性能更好更可靠的IC芯片,对ESD开展专门研究并找到控制方法是十分必要的。

随着芯片尺寸的持续缩小,ESD问题表现得更加突出,已成为新一代集成电路芯片在制造和应用过程中需要重视并着力解决的一个重要问题。

论文论述了CMOS集成电路ESD 保护的必要性,研究了在CMOS电路中ESD 保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD 保护结构的设计要求。

论文所做的研究工作和取得的结果完全基于GGNMOS的器件物理分析,是在器件物理层次上研究ESD问题的有益尝试;相对于电路层次上的分析结果,这里的结果更加准确和可靠,可望为GGNMOS ESD保护器件的设计和制造提供重要参考。

关键词:静电放电(ESD);接地栅NMOS;保护器件;电源和地AbstractThe electrostatic discharge (ESD) is integrated circuit (IC) in manufacturing, transportation, and use process occurs frequently and cause IC chips damage or failure of one of the important reasons. Industrial survey shows that about 40 percent of IC failure and ESD/EOS (overpowered electrical stress) relevant. Therefore, in order to obtain better performance more reliable IC chips, to carry out special research and find the ESD control method is very necessary. Along with the continuous narrowing, chip size behaved more prominent ESD problems, has become a new generation of integrated circuit chip in the manufacture and application process needed to pay attention to and addressing an important question.This paper discusses the CMOS integrated circuit, the necessity of ESD protection in CMOS circuit was studied in the structure of ESD protection design principle, analyzes the structure on the map the relevant requirements, especially discussed in the I/O circuit ESD protection structure design requirements.Keywords:Electrostatic Discharge, GND gate NMOS, Protected Device, Power and Ground目录摘要 (1)Abstract (2)第1章绪论 (4)1.1 集成电路的发展状况 (4)1.1.1 集成度的提高 (4)1.1.2 摩尔定律 (4)1.2 集成电路中的ESD保护 (5)1.2.1 为何出现ESD (5)1.2.2 ESD保护的必要性 (5)第2章关于版图设计与版图设计环境的介绍 (7)2.1 集成电路版图设计 (7)2.2 版图结构 (7)2.3 版图设计流程与方法 (8)2.4 版图设计环境 (8)2.4.1 Technology file 与Display Resource File 的建立 (9)2.4.2 Virtuoso工具的使用 (9)第3章CMOS电路的ESD保护结构版图设计 (13)3.1 CMOS电路中ESD测试 (13)3.2 ESD保护原理 (14)3.3 CMOS电路ESD保护结构的设计 (14)3.3.1 CMOS电路ESD保护器件 (15)3.4 CMOS电路ESD保护结构的版图设计 (16)3.4.1 版图设计原则 (16)3.4.2 ESD保护结构版图设计 (17)第4章结束语 (18)参考文献 (19)致谢 (20)第1章绪论1.1 集成电路的发展状况1.1.1 集成度的提高真正导致数字集成电路技术发生革命性变化的是半导体存储器和微处理器的引入。

CMOS集成电路ESD保护技术研究

CMOS集成电路ESD保护技术研究董培培;张海涛【摘要】介绍了 ESD 保护原理、测试方法及典型的 ESD 保护电路,针对2000V 的 HBM模型ESD 保护指标要求,采用 CSMC 0.5μm 25V(VGS)/25V (VDS)DPTM工艺模型和 GGMOS 器件进行了全芯片的 ESD 保护电路设计,并对 ESD 保护管的输出驱动级做了探索,在保证输出级 ESD 保护能力的同时,提高了输出端口的带负载能力。

鉴于 ESD 保护结构工艺移植性较差,保护性能与工艺密切相关的特点,结合具体版图设计实践,总结了 ESD 保护结构版图设计的通用原则。

这些原则旨在提高 ESD 保护结构的抗静电能力或提高 ESD 保护器件的工作可靠性,与具体的实现工艺无关。

流片后的 ESD 实验表明,设计的 ESD 保护结构可以承受2000V HBMESD 攻击。

%The principles,measurement methods and typical circuits of ESD Protection are introduced in this ing CSMC 0.5μm 25V(VGS)/25V(VDS)DPTMProcess and GGMOS devices,the ESD protection circuits of the whole chip are designed to achieve 2000V HBMESD protection ability,and output driver designed with ESD protection FETs is explored to raise the driving ability of output pin while keeping the ESD protection ability.Because technology portability of ESD protection circuits is bad and ESD protection ability is highly related with technology,combined with layout design practice,the general principles of ESD layout design are presented.The principles,regardless of technology,aim at raising the protection ability or reliability of ESD protection structure.The ESD experiment of the fabricated chip shows that the designed ESD protection structure can endure 2000V HBMESD attack.【期刊名称】《微处理机》【年(卷),期】2016(037)005【总页数】4页(P9-12)【关键词】ESD保护;GGMOS 器件;电路设计;版图设计;通用原则;工作可靠性【作者】董培培;张海涛【作者单位】中国电子科技集团公司第四十七研究所,沈阳 110032;中国人民解放军 95979 部队,辽宁,沈阳 110045【正文语种】中文【中图分类】TN4随着电路设计和制造工艺水平的发展,CMOS集成电路工艺尺寸不断缩小,单芯片集成度不断变大,且电路结构越来越复杂,极大提高了集成电路的性价比。

CMOS芯片的ESD保护电路设计

随着CMOS集成电路产业的高速发展,越来越多的CMOS芯片应用在各种电子产品中,但在电子产品系统的设计过程中,随着CMOS工艺尺寸越求越小,单位面积上集成的晶体管越来越多,极大地降低了芯片的成本,提高了芯片的运算速度。

但是,随着工艺的进步和尺寸的减小,静电释放(ESD),Elecyro Static Discharge)问题变得日益严峻。

据统计,在集成电路设计中大约40%的失效电路是ESD问题造成的。

MOS晶体管是绝缘栅器件,栅极通过薄氧化层和其他电极之间绝缘。

如果栅氧化层有较大的电压,会造成氧化层击穿,使器件永久破坏。

随着器件尺寸减少,栅氧化层不断减薄,氧化层能承受的电压也不断下降,引起氧化层本征击穿的电场强度约为1 X 107V/cm。

如栅氧化层厚度是50 nm 则可承受的最大电压约50 V,当栅氧化层厚度减少到5 nm,则所能承受的最大电压约为5 V。

因此外界的噪声电压容易引起栅击穿。

特别是外界各种杂散电荷会在栅极上积累,由于MOS 晶体管的栅电容很小,只要少量的电荷就能形成很大的等效栅压,引起器件和电路失效,这就是ESD 问题。

例如,人体所带的静电荷可产生高达几kV的电压,在80%的湿度情况下,人走过化纤地毯可能产生1.5 kV静电压。

ESD对CMOS集成电路的损伤,不仅会引起MOS器件栅击穿,还可能诱发电路内部发生闩锁效畸应。

另外,静电释放产生的瞬时大电流可能造成芯片局部发热,损害器件和电路。

在一般的条件下,ESD不会导致器件即时失效,它往往潜伏在集成电路器件中,这种存在有潜在缺陷的器件在使用时容易失效。

特别是在深亚微米CMOS工艺中,由于溥栅氧化层的击穿电压较低,必须加入有效的在片ESD保护电路以箝位加到内部电路栅氧化层上的过充电压。

1 ESD放电模式与设计方案电路的输入或输出端与电源和地之间的ESD应力有4种模式在集成电路中和外界相连的输入、输出端子比内部器什更容易受到ESD损伤。

射频esd设计

In RF CMOS, the following ESD elements can be utilized : grounded gate n-channel MOSFET (GGNMOS); shallow trench isolation (STI) defined diodes; polysilicon-defined diodes; silicon controlled rectifiers (SCRs).

Methods: Substitution cancellation distributed loads impedance isolation,

As to RF IC ESD, the following should be cared: Quality Factor of Reactive Elements;Series-Parallel Transformation;SNR;Noise Figure;Impedance Matching; Power Matching;Noise Matching;Transducer Power Gain; Operating Power Gain;Available Power Gain;Intermodulation Distortion

• In RF design, passive elements exist in the peripheral circuits for biasing d.c. or a.c.isolation and matching networks. Inductors and capacitors exist in both parallel and shunt configurations. These passive elements have lowloss and high-quality factors (Q). Passive element can serve a dual role of serving as a RF matching element and an ESD protection

ESD保护结构设计

ESD保护结构设计静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的使用环境并未改变,因此要进一步优化电路的抗ESD性能,如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为IC设计者主要考虑的问题。

ESD保护原理ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。

这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

在电路正常工作时,抗静电结构是不工作的,这使ESD保护电路还需要有很好的工作稳定性,能在ESD发生时快速响应,在保护电路的同时,抗静电结构自身不能被损坏,抗静电结构的负作用(例如输入延迟)必须在可以接受的范围内,并防止抗静电结构发生闩锁。

CMOS电路ESD保护结构的设计大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD 旁,I/O电路内部。

典型的I/O电路由输出驱动和输入接收器两部分组成。

ESD通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。

具体到I/O电路,就是与PAD相连的输出驱动和输入接收器,必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD电流,且能立即有效地箝位保护电路电压。

而在这两部分正常工作时,不影响电路的正常工作。

常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅等。

由于MOS管与CMOS 工艺兼容性好,因此常采用MOS管构造保护电路。

CMOS工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底-漏极)晶体管,这个寄生的晶体管开启时能吸收大量的电流。

ESD保护电路的设计

ESD保护电路的设计静电放电(ESD)会给电子产品带来致命的危害,它不仅降低了产品的可靠性,增加了维修成本,而且不符合欧洲共同体规定的工业标准EN61000-4-2,产品就不能够在欧洲销售。

所以电子设备制造商通常会在电路设计的初期就考虑ES D保护。

本文将讨论ESD保护电路的几种方法。

ESD的危害ESD基本上可以分为三种类型,一是各种机器引起的ESD,二是家俱移动或设备移动引起的ESD,三是人体接触或设备移动引起的ES D。

这三种种ES D对于半导体器件的生产和电子产品的生产都非常重要。

电子产品在使用过程最容易受到第三种ES D的损坏,便携式电子产品尤其容易受到人体接触产生的ESD的损坏。

在一般情况下ES D会损坏与之相连的接口器件,另一种情况是遭受ES D冲击后的器件可能不会立即损坏,而是性能下降导致产品过早出现故障。

当集成电路(IC)经受ESD时,放电回路的电阻通常都很小,无法限制放电电流。

例如将带静电的电缆插到电路接口上时,放电回路的电阻几乎为零,造成高达数十安培的瞬间放电尖峰电流,流入相应的IC管脚。

瞬间大电流会严重损伤IC,局部发热的热量甚至会融化硅片管芯。

ESD对IC的损伤还包括内部金属连接被烧断,钝化层受到破坏,晶体管单元被烧坏。

ESD还会引起IC的死锁(LATCHUP)。

这种效应和CMOS器件内部的类似可控硅的结构单元被激活有关。

高电压可激活这些结构,形成大电流信道,一般是从VCC到地。

串行接口器件的死锁电流可高达1A。

死锁电流会一直保持,直到器件被断电。

不过到那时,IC通常早已因过热而烧毁了。

ESD冲击后可能存在两个不易被发现的问题,一般用户和IEC测试机构使用传统的“环路反馈方法”和“插入方法”进行测试,通常检测不出这两个问题。

一个问题是RS-232接口电路中接收器对发送器产生交叉串扰。

同类产品RS-232接口电路中的ESD保护结构可能对某种波形的ESD或某个ESD冲击电压失效,经过ESD冲击后在接收器输入端和发送器输出端之间形成通路,从而导致接收器对发送器产生交调(图1)。

CMOS 电路中ESD 保护结构的设计

CMOS电路中ESD保护结构的设计作者 王大睿上海交通大学 微电子工程系摘 要:本文研究了在CMOS 工艺中I/O 电路的 ESD保护结构设计以及相关版图的要求,其中重点讨论了PAD到VSS电流通路的建立。

关键词:ESD保护电路,ESD设计窗口,ESD 电流通路Construction Strategy of ESD Protection Circuit Abstract:The principles used to construct ESD protection on circuits and the basic concept ions of ESD protection design are presented.Key words:ESD protection/On circuit, ESD design window, ESD current path1引言静电放电(ESD,Electrostatic Discharge)给电子器件环境会带来破坏性的后果。

它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,互补金属氧化物半导体(CMOS,Complementary Metal-Oxide Semiconductor)的特征尺寸不断缩小,金属氧化物半导体(MOS, Metal-Oxide Semiconductor)的栅氧厚度越来越薄,MOS管能承受的电流和电压也越来越小,因此要进一步优化电路的抗ESD性能,需要从全芯片ESD保护结构的设计来进行考虑。

2ESD的测试方法ESD模型常见的有三种,人体模型(HBM ,Human Body Model)、充电器件模型(CDM,Charge Device Model)和机器模型(MM,Machine Mode),其中以人体模型最为通行。

一般的商用芯片,要求能够通过2kV静电电压的HBM检测。

对于HBM放电,其电流可在几百纳秒内达到几安培,足以损坏芯片内部的电路。

CMOS集成电路中ESD保护技术研究

CMOS集成电路中ESD保护技术研究作者:王翠霞许维胜余有灵吴启迪范学峰来源:《现代电子技术》2008年第08期摘要:分析ESD失效的原因和失效模式,针对亚微米CMOS工艺对器件ESD保护能力的降低,从工艺、器件、电路三个层次对提高ESD保护能力的设计思路进行论述。

工艺层次上通过增加ESD注入层和硅化物阻挡层实现ESD能力的提高;器件方面可针对电路的特点,选择合适的器件(如MOS,SCR,二极管及电阻)达到电路需要的ESD保护能力;电路方面采用栅耦和实现功能较强的ESD保护。

关键词:静电放电;失效模式;ESD保护电路;栅耦合中图分类号:TN433文献标识码:A文章编号:1004-373X(2008)08-001-(1.Institute of Semiconductor and Information Technology,TongjiAbstract:On the basis of failure source and failure mode of ESD,the paper describes the method of improving ESD protection ability from the level of process,device and circuit,according to the decreasing of the ESD protection ability in the advanced micro CMOS technology.In the Process level,ESD ability can be improved by adding ESD implant and silicide blocking mask.In the device level,it can be enhanced by selecting the right device such as MOS,SCR,diode and resistor accordingKeywords:静电在芯片的制造、封装、测试和使用过程中无处不在,积累的静电荷以几安培或几十安培的电流在纳秒到微秒的时间里释放,瞬间功率高达几百千瓦,放电能量可达毫焦耳,对芯片的摧毁强度极大[1]。

芯片IO缓冲及ESD电路设计

芯片I/O缓冲及ESD电路设计摘要:文章详细介绍了基于CMOS的芯片I/O缓冲电路分类,功能,电路及版图设计的一些考虑以及芯片引脚的静电保护问题。

关键词:I/O;缓冲电路;静电保护;CMOS针对引脚的输入输出缓冲(I/O buffer)电路设计,也可以称为输入输出接口(I/O interface)电路设计,是一颗完整芯片设计中不可或缺的组成部分,但是详细论述其设计规则的文章或者著作在国内却比较鲜见,这对初学者或者没有这方面经验的工程师无疑会造成困惑。

本文以CMOS工艺为例,较全面的论述I/O缓冲电路设计中各种考虑,可以作为芯片引脚输入输出电路设计的一个参考。

根据I/O缓冲电路应用目标的不同,可将其分为输入、输出等几类,详见表1。

表1 I/O缓冲电路的分类输出缓冲输出缓冲电路的功能要求能够驱动大的片外负载,通常为2~50pF,并且提供适当的上升/下降时间。

一组连续的大尺寸的缓冲器(buffer)对驱动能力的提高是有益的。

大尺寸的管子容易受闩锁效应(latch-up)的影响,在版图设计时建议采用保护环(Guardrings)保护以避免闩锁效应,如图1-1所示。

在图中,用P+作为内保护环,而N+作为外保护环(In n-well)。

图1-1缓冲器一种常见的输出电路如图1-2所示,En是输出电路的使能信号,Dout是输出数据,MOS管组合的功能如图中所示。

当En为低而Dout有效时,A、B均为高电平,输出Y为低,且由外向里看为高阻抗状态,如果Dout未定,则Y为高阻。

需要注意的是,最后输出级的管子尺寸要大到能够提供足够的电流源或电流沉并且减少延迟时间。

其负面影响是电流变化率(di/dt)变大而使穿过输出点到封装的压焊线上的L(di/dt)噪声增大,从而导致较大的片上噪声。

图1-2常用的输出缓冲电路在高性能的芯片中,如32位的微处理器,如果多个I/O输出驱动电路工作状态相似时,L(di/dt)噪声可能逐步增强,会影响芯片速度。

cmos 电路 esd泄放原理

CMOS电路是当今集成电路中最常见的一种电路类型,而ESD (Electrostatic Discharge,静电放电)则是一个不可忽视的问题。

在CMOS电路中,ESD对电路的损坏可能会导致严重影响甚至可能造成整个系统的失效。

了解CMOS电路中的ESD泄放原理对于电路设计和集成电路的稳定性至关重要。

一、CMOS电路简介1. CMOS电路特点CMOS电路是一种使用互补型金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,简称CMOS)技术制作的集成电路。

CMOS电路具有低功耗、高噪声抑制、集成度高等优点,因此被广泛应用于数字集成电路、微处理器、存储器等领域。

2. CMOS电路结构CMOS电路由P型金属氧化物半导体(P-MOS)和N型金属氧化物半导体(N-MOS)两种类型的MOSFET器件组成。

它利用P-MOS和N-MOS的互补特性,实现高密度和低功耗。

二、ESD泄放原理1. ESD的危害ESD是指人体或物体在静电充电后,与另一对象或地面突然放电的现象。

在现代集成电路中,ESD是造成电路损坏和性能降低的主要原因之一。

当ESD发生时,电流冲击会对CMOS电路中的敏感元件产生破坏性影响。

2. ESD泄放原理ESD泄放是指在CMOS电路中设计专门的保护电路,以接受和限制ESD脉冲,从而保护电路不受损坏。

它通过引入ESD元件并将其连接到电源和地,以吸收来自ESD事件的能量,从而降低ESD对电路的损害。

三、CMOS电路中的ESD保护技术1. ESD保护器件在CMOS电路中,常用的ESD保护器件包括二极管、二极管堆、金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,简称MOSFET)等。

这些保护器件能够有效限制ESD脉冲的能量,保护主要电路不受损坏。

2. ESD保护电路设计原则在设计CMOS电路的ESD保护电路时,需要考虑ESD脉冲的能量、速度以及保护电路的响应时间等因素。

CMOS电路芯片ESD保护电路设计技术分析

CMOS电路芯片ESD保护电路设计技术分析摘要:静电是造成CMOS电路芯片失效机理的主要因素之一,严重时还会引发电路自燃现象。

因此,探讨ESD对于CMOS电路芯片保护而言存在一定的必要性。

基于此,本文简单分析提升ESD保护能力的常用方式及保护原理,并深入探讨CMOS电路芯片ESD保护电路结构设计,以供参考。

关键词:静电放电;CMOS电路芯片;ESD保护引言:静电通常会在电路芯片使用、测试、封装与制造过程中产生,而静电放电现象会为各种电子器件造成不同程度的损伤,静电累积电荷在某种情况下可瞬间达到几百千瓦功率,对电路芯片伤害强度极大。

因此,必须通过合理设计ESD电路芯片保护结构,进而降低静电对电路芯片的破坏。

1.ESD的失效模式通常来讲,导致产生ESD的原因不同对CMOS电路芯片放电方式也会有所不同,最为常见的ESD现象模型为电场感应模型、带电器件模型、机器模型和人体模型。

其中人体模型在整体放电过程时会在上百纳秒内瞬间产生有数安倍电流的释放,其对电路芯片的整体伤害相对较轻。

机械模型放电时间通常较短,只在几十纳秒内便会产生有数安培的电流瞬间释放,可在一定程度上危害机械模型。

而带电体模型则放电时间更短,其对电路芯片整体危害最大,在几纳秒内便会将电流释放量达到十几安培。

引发ESD失效的根本原因为电失效和热失效两种。

其中热失效主要由于电路系统局部电流过于集中而产生热量,使各种器件金属区域芯片产生热斑或将线路熔化,进而造成二次击穿。

电失效则是因为栅氧化物上施加的电压强度超出其介质最高强度,进而导致相关介质被表面击穿或结构击穿。

而ESD的整体失效模式主要包括潜在失效、软失效与硬失效三种模式。

1.提升ESD保护能力的常用方法2.1从制程上改进现阶段,从整体上优化ESD保护能力主要通过两种方式执行:即增设阻挡层金属硅化物掩膜板及ESD保护系统注入工序。

以上两道增设工序可充分提升电路芯片器件本身对ESD的承受能力,但在一定程度上增加了大量改进成本[1]。

LDMOS器件在ESD保护中的应用

LDMOS器件在ESD保护中的应用电子科技大学功率集成技术研究室肖艳 贺江平 张波摘要: 本文针对LDMO S器件在ESD保护应用中的原理进行了分析,重点讨论了设计以及应用过程中如何降低高触发电压和有效提高二次击穿电流,结合实际工艺对器件进行参数优化,得到了承受4KV ESD电压的LDMOS 器件。

1 引言ESD(Electrostatic Discharge)现象对集成电路的可靠性造成了巨大威胁,利用片内半导体器件形成保护电路是提高ESD保护的重要手段[1]。

一般的消费电子产品要求在人体放电模式(HBM,Human-Body Mode)模式下承受的ESD电压大于2KV。

智能功率集成电路通常需要高低压器件兼容集成来实现,横向双扩散绝缘栅场效应晶体管(LDMOS,Lateral Double Diffused MOS Transistor)具有较高耐压,且与双极、CMOS低压工艺兼容,易于集成而被广泛应用于智能功率IC中。

同时,LDMOS被广泛选用对高压通道进行ESD保护。

本文利用双金属层、0.6µm 双极-互补MOS-双扩散MOS(BCD)工艺下的LDMOS来实现一块智能功率IC输出端口的静电保护,并成功通过测试,有效提高了芯片的可靠性。

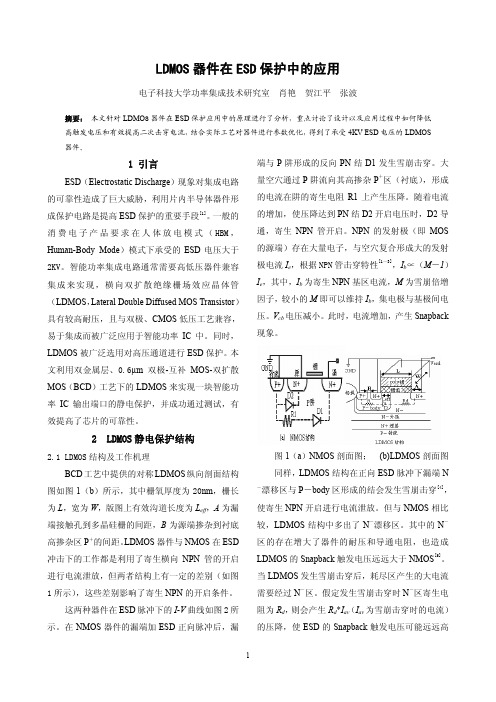

2 LDMOS静电保护结构2.1 LDMOS结构及工作机理BCD工艺中提供的对称LDMOS纵向剖面结构图如图1(b)所示,其中栅氧厚度为20nm,栅长为L,宽为W,版图上有效沟道长度为L eff,A为漏端接触孔到多晶硅栅的间距,B为源端掺杂到衬底高掺杂区P+的间距。

LDMOS器件与NMOS在ESD 冲击下的工作都是利用了寄生横向NPN管的开启进行电流泄放,但两者结构上有一定的差别(如图1所示),这些差别影响了寄生NPN的开启条件。

这两种器件在ESD脉冲下的I-V曲线如图2所示。

在NMOS器件的漏端加ESD正向脉冲后,漏端与P阱形成的反向PN结D1发生雪崩击穿。

CMOS电路ESD保护结构的设计

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。

论述了CMOSESD保护的必要性,研究了在CMOS电路中ESD 保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求。

1 引言静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的使用环境并未改变,因此要进一步优化电路的抗ESD性能,如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为者主要考虑的问题。

2 ESD保护原理ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。

这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

在电路正常工作时,抗静电结构是不工作的,这使ESD保护电路还需要有很好的工作稳定性,能在ESD发生时快速响应,在保护电路的同时,抗静电结构自身不能被损坏,抗静电结构的负作用(例如输入延迟)必须在可以接受的范围内,并防止抗静电结构发生闩锁。

3 CMOS电路ESD保护结构的设计大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。

典型的I/O电路由输出驱动和输入接收器两部分组成。

ESD 通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。

具体到I/O电路,就是与PAD相连的输出驱动和输入接收器,必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD 电流,且能立即有效地箝位保护电路电压。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MOS鑺墖鐨凟SD淇濇姢鐢佃矾璁捐

銆€銆€闅忕潃CMOS闆嗘垚鐢佃矾浜т笟鐨勯珮閫熷彂灞曪紝瓒婃潵瓒婂鐨凜MOS鑺墖搴旂敤鍦ㄥ悇绉嶇數瀛愪骇鍝佷腑锛屼絾鍦ㄧ數瀛愪骇鍝佺郴缁熺殑璁捐杩囩▼涓紝闅忕潃CMOS宸ヨ壓灏哄瓒婃眰瓒婂皬锛屽崟浣嶉潰绉笂闆嗘垚鐨勬櫠浣撶瓒婃潵瓒婂锛屾瀬澶у湴闄嶄綆浜嗚姱鐗囩殑鎴愭湰锛屾彁楂樹簡鑺墖鐨勮繍绠楅€熷害銆?

銆€銆€浣嗘槸锛岄殢鐫€宸ヨ壓鐨勮繘姝ュ拰灏哄鐨勫噺灏忥紝闈欑數閲婃斁(ESD)锛孍lecyro Static Discharge)闂鍙樺緱鏃ョ泭涓ュ郴銆傛嵁缁熻锛屽湪闆嗘垚鐢佃矾璁捐涓ぇ绾?0%鐨勫け鏁堢數璺槸ESD闂閫犳垚鐨勩€?

銆€銆€MOS鏅朵綋绠℃槸缁濈紭鏍呭櫒浠讹紝鏍呮瀬閫氳繃钖勬哀鍖栧眰鍜屽叾浠栫數鏋佷箣闂寸粷缂樸€傚鏋滄爡姘у寲灞傛湁杈冨ぇ鐨勭數鍘嬶紝浼氶€犳垚姘у寲灞傚嚮绌匡紝浣垮櫒浠舵案涔呯牬鍧忋€?

銆€銆€闅忕潃鍣ㄤ欢灏哄鍑忓皯锛屾爡姘у寲灞備笉鏂噺钖勶紝姘у寲灞傝兘鎵垮彈鐨勭數鍘嬩篃涓嶆柇涓嬮檷锛屽紩璧锋哀鍖栧眰鏈緛鍑荤┛鐨勭數鍦哄己搴︾害涓? X 107V/cm銆傚鏍呮哀鍖栧眰鍘氬害鏄?0 nm 鍒欏彲鎵垮彈鐨勬渶澶х數鍘嬬害50 V锛屽綋鏍呮哀鍖栧眰鍘氬害鍑忓皯鍒? nm锛屽垯鎵€鑳芥壙鍙楃殑鏈€澶х數鍘嬬害涓? V銆傚洜姝ゅ鐣岀殑鍣0鐢靛帇瀹规槗寮曡捣鏍呭嚮绌裤€?

銆€銆€鐗瑰埆鏄鐣屽悇绉嶆潅鏁g數鑽蜂細鍦ㄦ爡鏋佷笂绉疮锛岀敱浜嶮OS 鏅朵綋绠$殑鏍呯數瀹瑰緢灏忥紝鍙灏戦噺鐨勭數鑽峰氨鑳藉舰鎴愬緢澶х殑绛夋晥鏍呭帇锛屽紩璧峰櫒浠跺拰鐢佃矾澶辨晥锛岃繖灏辨槸ESD闂銆備緥濡傦紝浜轰綋鎵€甯︾殑闈欑數鑽峰彲浜х敓楂樿揪鍑爇V鐨勭數鍘嬶紝鍦?0%鐨勬箍搴︽儏鍐典笅锛屼汉璧拌繃鍖栫氦鍦版鍙兘浜х敓1.5 kV闈欑數鍘嬨€侲SD瀵笴MOS闆嗘垚鐢佃矾鐨勬崯浼わ紝涓嶄粎浼氬紩璧稭OS鍣ㄤ欢鏍呭嚮绌匡紝杩樺彲鑳借鍙戠數璺唴閮ㄥ彂鐢熼棭閿佹晥鐣稿簲銆?

銆€銆€鍙﹀锛岄潤鐢甸噴鏀句骇鐢熺殑鐬椂澶х數娴佸彲鑳介€犳垚鑺墖灞€閮ㄥ彂鐑紝鎹熷鍣ㄤ欢鍜岀數璺€傚湪涓€鑸殑鏉′欢涓嬶紝ESD涓嶄細瀵艰嚧鍣ㄤ欢鍗虫椂澶辨晥锛屽畠寰€寰€娼滀紡鍦ㄩ泦鎴愮數璺櫒浠朵腑锛岃繖绉嶅瓨鍦ㄦ湁娼滃湪缂洪櫡鐨勫櫒浠跺湪浣跨敤鏃跺鏄撳け鏁堛€?

銆€銆€鐗瑰埆鏄湪娣变簹寰背CMOS宸ヨ壓涓紝鐢变簬婧ユ爡姘у寲灞傜殑鍑荤┛鐢靛帇杈冧綆锛屽繀椤诲姞鍏ユ湁鏁堢殑鍦ㄧ墖ESD淇濇姢鐢佃矾浠ョ疂浣嶅姞鍒板唴閮ㄧ數璺爡姘у寲灞備笂鐨勮繃鍏呯數鍘嬨€?

銆€銆€1 ESD鏀剧數妯″紡涓庤璁℃柟妗?

鐢佃矾鐨勮緭鍏ユ垨杈撳嚭绔笌鐢垫簮鍜屽湴涔嬮棿鐨凟SD搴斿姏鏈?绉嶆ā寮? 銆€銆€鍦ㄩ泦鎴愮數璺腑鍜屽鐣岀浉杩炵殑杈撳叆銆佽緭鍑虹瀛愭瘮鍐呴儴鍣ㄤ粈鏇村鏄撳彈鍒癊SD鎹熶激銆備竴鑸數璺殑杈撳叆鎴栬緭鍑虹涓庣數婧愬拰鍦颁箣闂寸殑ESD搴斿姏鏈?绉嶆ā寮忥細

銆€銆€(1)鏌愪竴杈撳叆(鎴栬緭鍑?绔鍦扮殑姝h剦鍐茬數鍘?PS妯″紡)锛歏SS鎺ュ湴锛孍SD姝g數鍘嬪姞鍒拌杈撳叆杈撳嚭绔紝瀵筕SS鏀剧數锛孷DD涓庡叾浠栫鑴氭偓绌恒€?

銆€銆€(2)鏌愪竴杈撳叆(鎴栬緭鍑?绔鍦扮殑璐熻剦鍐茬數鍘?NS妯″紡)锛歏SS鎺ュ湴锛孍SD璐熺數鍘嬪姞鍒拌杈撳叆杈撳嚭绔紝瀵筕SS鏀剧數锛孷DD涓庡叾浠栫鑴氳剼鎮┖銆?

銆€銆€(3)鏌愪竴涓緭鍏ユ垨杈撳嚭绔浉瀵筕DD绔殑姝h剦鍐茬數鍘?PD妯″紡)锛

歏DD鎺ュ湴锛孍SD姝g數鍘嬪姞鍒拌杈撳叆杈撳嚭绔紝瀵筕DD鏀剧數锛孷SS涓庡叾浠栫鑴氭偓绌恒€?

銆€銆€(4)鏌愪竴涓緭鍏ユ垨杈撳嚭绔浉瀵筕DD绔殑璐熻剦鍐茬數鍘?ND妯″紡)锛歏DD鎺ュ湴锛孍SD璐熺數鍘嬪姞鍦ㄨ杈撳叆杈撳嚭绔紝瀵筕DD鏀剧數锛孷SS涓庡叾浠栫鑴氭偓绌恒€?

銆€銆€闃叉闆嗘垚鐢佃矾鑺墖杈撳叆銆佽緭鍑虹鍙楀埌ESD搴斿姏鎹熶激鐨勬柟娉曟槸鍦ㄨ姱鐗囩殑杈撳叆鍜岃緭鍑虹澧炲姞ESD淇濇姢鐢佃矾銆備繚鎶ょ數璺殑浣滅敤涓昏鏈変袱鏂归潰锛氫竴鏄彁渚汦SD鐢垫祦鐨勯噴鏀鹃€氳矾;浜屾槸鐢靛帇閽充綅锛岄槻姝㈣繃澶х殑鐢靛帇鍔犲埌MOS鍣ㄤ欢涓娿€?

銆€銆€瀵笴MOS闆嗘垚鐢佃矾杩炴帴鍒板帇鐐圭殑杈撳叆绔父閲囩敤鍙屼簩鏋佺淇濇姢鐢甸晙锛屽浘2鎵€绀轰负甯歌鐨凟SD淇濇姢鐢佃矾鐨勭粨鏋勶細鍙屼簩鏋佺淇濇姢鐢佃矾銆?

銆€銆€浜屾瀬绠1鏄拰PMOS婧愩€佹紡鍖哄悓鏃跺舰鎴愮殑锛屾槸p+n-缁撴瀯锛屼簩鏋佺D2鏄拰NMOS婧愩€佹紡鍖哄悓鏃跺舰鎴愮殑锛屾槸n+p-缁撴瀯銆傚綋鍘嬬偣鐩稿鍦板嚭鐜拌礋鑴夊啿搴斿姏锛屽垯浜屾瀬绠2瀵奸€氾紝瀵奸€氱殑浜屾瀬绠″拰鐢甸樆褰㈡垚ESD鐢垫祦鐨勬硠鏀鹃€氳矾銆?

銆€銆€褰撳帇鐐圭浉瀵瑰湴鍑虹幇姝h剦鍐插簲鍔涳紝浣夸簩鏋佺D2鍑荤┛锛屽彧瑕佷簩鏋佺D2鍑荤┛鐢靛帇浣庝簬鏍呮哀鍖栧眰鐨勫嚮绌跨數鍘嬶紝灏卞彲浠ヨ捣鍒颁繚鎶や綔鐢ㄣ€傜被浼肩殑锛屽綋鍘嬬偣鐩稿鐢垫簮鍑虹幇姝h剦鍐叉垨璐熻剦鍐插簲鍔涳紝浜屾瀬绠1璧蜂繚鎶や綔鐢紝鎻愪緵闈欑數鑽风殑娉勬斁閫氳矾銆?

銆€銆€杩欎袱涓簩鏋佺鎶婂姞鍒拌緭鍏ョ骇MOS鏅朵綋绠℃爡鏋佺殑鐢靛帇鑼冨洿濡傚紡(1)鎵€绀猴細-0锛?

銆€銆€鍋囪浜屾瀬绠$殑姝e悜瀵奸€氱數鍘嬫槸0.7 V銆傜數闃荤殑浣滅敤鏄檺鍒舵祦杩囦簩鏋佺鐨勭數娴併€傜敱浜嶦SD搴斿姏鐢靛帇閮芥槸鐭殏鐨勮剦鍐蹭俊鍙凤紝鍙鐢垫祦涓嶆槸闈炲父澶э紝浜屾瀬绠′笉浼氳鐑у潖锛屽彲浠ユ寔缁捣淇濇姢浣滅敤銆傚浘2涓娇鐢ㄤ簩鏋佺浣滀负I/O绔殑ESD淇濇姢鐢佃矾锛屼富瑕佹彁渚汸D鍜孨S妯″紡涓嬬殑鐢垫祦娉勬斁閫氳矾锛屼絾瀵逛簬ND妯″紡鍜孭S妯″紡锛屼簩鏋佺澶勪簬鍙嶅亸鐘舵€侊紝鍙嶅亸绠濅綅鐢靛帇杩囬珮锛岀數娴佹硠鏀捐兘鍔涜緝寮憋紝瀵奸€氱數闃昏緝楂橈紝浣跨疂浣嶈兘鍔涗笉澶燂紝涓斾骇鐢熺殑鐑噺杈冨ぇ銆?

銆€銆€鍥?涓數璺富瑕佺敤浜庡弻鏋佸伐鑹猴紝閲囩敤涓€涓熀鏋佹帴VDD鍦癙NP 涓夋瀬绠″拰涓€涓熀鏋佹帴鍦扮殑NPN涓夋瀬绠″叡鍚屾瀯鎴怑SD淇濇姢鐢佃矾銆傞噰鐢ㄨ繖绉嶄繚鎶ょ數璺紝鐩稿浜庝簩鏋佺锛屽湪ND鍜孭S妯″紡涓嬶紝鍙互宸ヤ綔鍦⊿napback鐘舵€侊紝鍏锋湁杈冨己鐨勭數娴佹硠鏀捐兘鍔涘拰杈冧綆鐨勭淮鎸佺數鍘嬨€?

銆€銆€2 ESD淇濇姢鐢佃矾

銆€銆€瀵规繁浜氬井绫矯MOS闆嗘垚鐢佃矾锛屾爡姘у寲灞傜殑鍑荤┛鐢靛帇寰堝皬锛屽父瑙勪簩鏋佺鐨勫嚮绌跨數鍘嬭緝澶э紝涓嶈兘璧峰埌寰堝ソ鐨勪繚鎶や綔鐢ㄣ€傚洜姝ゅ彲浠ュ鍔犵瀛愭敞鍏ユ彁楂樹簩鏋佺鐨勮‖搴曟祿搴︼紝褰㈡垚p+n+鍜宯+p+缁撴瀯鏉ラ檷浣庝簩鏋佺鐨勫嚮绌跨數鍘嬨€?

銆€銆€鑰冭檻鍒板噯澶囨祦鐗囩殑澶氬姛鑳芥暟瀛楄姱鐗囪閲囩敤CSMC2P2M 0.6μm。