DSP技术及应用 第2章

DSP技术及应用课后部分习题答案

第二章3.简述TI公司C2000/C5000/C6000系列DSP的特点及主要用途?1.C2000系列DSP控制器,具有良好的性能集成Flosh存储器,高速A/D 转换器以及可靠的CAN模块,主要应用于数字化控制.用途:工业驱动,供电、OPS。

2.C5000系列杰出的性能和优良的性能价格比,广泛应用,尤其在通信领域.IP电话机和IP电话网关.3.C6000系列采用指令集以及流水应用,使许多指令得以运行,推出三个系列.用途:数字通信和图像处理.5.TMS320C54X芯片的CPU主要由哪些部分构成?①先进的多总线结构(1条程序总线、3条数据总线、4条地址总线)②40位算术逻辑运算单元(ALU),包括1个40位桶形移位寄存器和2个独立的40位累加器③17x17位并行乘法器,与40位专用加法器相连,用于非流水线式单周期乘法/累加(MAC)运算④比较、选择、存储单元(CSSU),用于加法/比较选择⑤指数编码器,可以在单个周期内计算40位累加器中数值的指数⑥双地址生成器,包括8个辅助寄存器和2个辅助寄存器算术运算单元(ARAU)6.简述TMS320C54X芯片的程序空间7.简述TMS320C54X芯片的中断系统(P42)答:2.中断处理步骤(1) 接受中断请求;(2)应答中断;(3)执行中断服务程序(ISR)9.TMS320C54x 有哪几种基本的数据寻址方式①立即寻址②绝对寻址③累加器寻址④直接寻址⑤间接寻址⑥存储器映像寄存器寻址⑦堆栈寻址10.使用循环寻址时,必须遵循的3个原则是什么?试举例说明循环寻址的用法。

(P60)答:1.把循环缓冲区的首地址放在符合上述算法的N的边界地址上2、使用一个小于或等于缓冲区大小的步长3、在开始寻址前,辅助寄存器必须指向循环缓冲区内的一个元素举例:LD * +AR1(8)a%, ASTL A,*+AR1(8)%;11。

TMS320C54x的指令集包含了哪几种基本类型的操作?答:数据传送指令、算术运算指令、逻辑运算指令、程序控制指令、并行操作指令和重复操作指令12.汇编语句格式包含哪几种部分?编写汇编语句需要注意哪些问题?答: [标号][:]空格[助记符]空格[操作数]空格[;注释]1、所有的语句必须以一个标号、空格、星号或分号开始。

DSP技术原理及应用教程

加强与数学、物理学、生物学等其他学科的交叉融合,以开拓DSP技 术在更多领域的应用。

注重实际应用

在研究过程中,注重与实际应用的结合,以提高DSP技术的实用性和 市场竞争力。

THANKS

感谢观看

应用前景

通信领域

DSP技术将在通信领域发挥重 要作用,如调制解调、信号编

解码等。

音频处理

DSP技术在音频信号处理方面 具有天然优势,如音频编解码 、音频效果处理等。

图像处理

DSP技术也可应用于图像信号 处理,如图像增强、目标检测 等。

工业控制

DSP技术将应用于工业控制领 域,实现智能化、高精度的信

号处理。

06

结论

主要观点总结

DSP技术原理

数字信号处理(DSP)是一门跨学科的综合性技术,涉及数学、电路、计算机等多个领域。其主要原理是将模拟信号转换 为数字信号,然后通过计算机进行运算处理,以达到改善信号质量或提取有用信息的目的。

应用领域

DSP技术在通信、雷达、声呐、图像处理、语音识别、生物医学工程等领域有着广泛的应用。通过DSP技术,可以实 现信号的滤波、频谱分析、参数估计、模式识别等功能。

FFT算法将DFT的计算复杂度从 $O(N^2)$降低到$O(Nlog N)$,大 大提高了计算效率。

03

DSP技术的应用领域

通信领域

调制解调

频谱分析

信道均衡

语音压缩

在数字通信中,调制解调是 将基带信号转换为频带信号 的过程,反之亦然。DSP技 术可以快速实现各种调制解 调算法,如QPSK、QAM等 ,提高通信速率和抗干扰能 力。

DSP芯片采用先进的制程技术,具有低功耗 的特点,延长了设备的待机时间。

DSP芯片技术及应用

DSP总结:以下总结仅针对宁波大学DSP芯片技术及应用(通信类非控制类)这门课,个人根据重点、考点总结的,用于期末复习(请结合课本以及PPT的例子),不足之处请见谅,基本能过就是,如若其中有错请联系QQ:493288964。

还是建议您平时学点,理解为先!!!将该文章用于百度等兑换积分的行为是可耻的!第一章绪论(简介)1、DSP芯片特点:采用哈佛结构;多总线结构;流水线技术;专用的硬件乘法器;特殊的DSP指令;快速的指令周期;硬件配置强;支持多处理器结构1)CPU是冯.诺伊曼结构;DSP是数据和地址空间分开的哈佛结构。

冯.诺依曼结构:单存储空间;统一的程序和数据空间;共享的程序和数据总线;程序指令只能串行执行单指令周期:100ns,现在单指令周期为:10ns哈佛结构:双存储空间;程序存储器和数据存储器分开;程序总线和数据总线分开;独立编址、独立访问改进型哈佛结构:双存储空间、多条总线;多条数据总线;高速缓冲器(重复指令,只需读入一次)2)采用多总线结构:TMS320C54X:4组总线;单机器周期内可完成的操作;3)流水线操作4)专用的硬件乘法器硬件乘法累加器是DSP区别于通用微处理器的一个重要标志MAC(乘累加)单元(独立的乘法器和加法器;单周期内完成一次乘法和一次加法运算;MPY,MAC,MACA, MACSU等指令)分类:工作时钟和指令类型:静态和一致性DSP芯片;用途分:通用和专用型;数据格式分:定点和浮点型2、DSP按数据格式分为定点型和浮点型定点DSP芯片:数据长度16位/24位TMS320C2000/5000/6000价格便宜、功耗较低、但运算精度稍低。

浮点DSP芯片:数据长度32位/40位MS320C3X/4X/VC33/C67X/C8X价格稍贵、功耗较大、但运算精度高。

3、芯片简介TMS320VC5416PGE160 主处理器芯片的性能:频率:160MHz 速度:160MIPS 周期:6.25ns第二章:TMS320C54X的硬件结构1、C54X:为低功耗,高性能而专门设计的16位定点DSP芯片C54基本结构:中央处理器(CPU)、内部总线结构、存储器、片内外设。

dsp2

DSP技术及应用

20

图2.8 乘法器/加法器单元功能框图

DSP技术及应用

21

2.3

中央处理单元(CPU)

(5)比较、选择和存储单元

功能 用途:在数据通信、模式识别等领域,经常要用到 Viterbi(维特比)算法。C54x DSP的CPU的比较、选择和 存储单元 (CSSU) 就是专门为 Viterbi 算法设计的进行加 法/比较/选择(ACS)运算的硬件单元。

DSP技术及应用

30

2.4

存储器和I/O空间

• C54x的总存储空间为192K字

存储器的组成(分为3个可选择的存储空间):

程序存储空间ROM 64K 16位:存放程序(要执行的指令) 单访问SARAM 数据存储空间RAM 64 K16位 保存执行指令所使用的数据( 双访问DARAM I / O存储空间64 K16位:提供与外部存储器映射的接口

DSP技术及应用

3

2.1

TMS320C54x硬件结构框图

TMS320C54x内部结构(3大块) (1)CPU 包 括 算 术 逻 辑 运 算 单 元 (ALU, Arithmetic Logic Unit) 、乘法器、累加器、移位寄存器、各种专门用途 的寄存器、地址生成器及内部总线。 (2)存储器系统 包括片内程序 ROM 、片内单访问的数据 RAM 和双访问 的数据RAM、外接存储器接口。 (3)片内外设与专用硬件电路 包括片内定时器、各种类型的串口、主机接口、片 内锁相环(PLL)、时钟发生器及各种控制电路。

第2章

2.1 2.2 2.3 2.4

DSP应用技术-DSP及其应用概述

① C55xTM DSP内核可以为高达600 MIPS的性能提供300 MHz;

② 目前TMS320C5510 DSP已经开始投产,TMS320C5509 DSP 可提供样片;

③ 在整个C5000TM DSP平台上可实现软件兼容。

(2) 应用:功能丰富的便携产品,2G、2.5G、3G手机与基站, 数字音频播放器,数码相机,电子图书,语音识别,GPS接收器, 指纹/模式识别,无线调制解调器,耳机,生物辨识。

③ 高达7 MB的片上内存;

④ 两个多通道缓冲串行端口(McBSP)(三个用于C6202与 C6203 DSP的McBSP);

⑤ 16位主机端口接口(HPI)(32位用于C6202、C6203与C6204 DSP的扩展总线);

⑥ 两个32位定时器;

⑦ 300 MHz时速率高达2400 MIPS(C6203 DSP)。

(6) 具有软、硬件等待功能,能与各种存取速度的存储器接 口。

(7) 针对滤波、相关和矩阵运算等需要大量乘法累加运算的 特点,DSP芯片大多配有独立的乘法器和加法器,使得在同一 时钟周期内可以完成乘、累加两个运算。

(8) 低功耗,DSP一般为0.5~4 W,而采用低功耗技术的 DSP芯片只有0.1 W,可用电池供电。

(2) 特性:OMAP5910双内核处理器同时包括。 ① 150 MHz的TI增强ARM925微处理器: * 16 KB指令高速缓冲存储器以及8 KB数据缓冲器; * 数据与指令MMU; * 32位与16位指令集。

② 150 MHz TMS320C55xTM DSP内核: * 24 KB指令高速缓冲存储器; * 160 KB SRAM; * 用于视频算法的硬件加速器。

(3) 特性:高级自动电源管理;可配置的空闲域,以延长电 池寿命;缩短调制过程,从而加快产品上市进程。

DSP技术及应用陈金鹰

噪声

干扰影响大

电磁场等

数字系统

只要能判决 就能复原信号

可靠性好 可重复性好

12

第13页/共39页

可靠性和可重复性的典型例子

信号 信号

放大器A 放大器B

计算机A 计算机B

A、B结果 可能不同

A、B结结 果相同

13

第14页/共39页

4.大规模集成

模拟系统: 有一些模拟集成电路 品种较少 集成度不高 价格较高

使FFT、卷积等运算中的寻址、排序及计算速 度大大提高。1024点FFT的时间已小于1ms。

29

第30页/共39页

5. 硬件配置能力强

多通道缓冲串行口(McBSP)

片

主机接口(HPI)

内

DMA控制器

具 有

软件控制等待状态发生器

锁相环时钟发生器

JTAG边界扫描逻辑电路

30

第31页/共39页

6. 耗电省

26

第27页/共39页

2. 多流水线操作技术(Pipeline)

取指 译码 寻址 取数 运算 存储 取指 译码 寻址 取数 运算 存储 取指 译码 寻址 取数 运算 存储

流水线深度可达8级

27

第28页/共39页

3. 独立的硬件乘法器

DSP利用硬件乘法器 通过MAC指令在单周期内完成 A(k)B(n—k) 这类运算的取数、乘法、累加

模拟处理系统升级

修改硬件设计 调整硬件参数

数字处理系统的升滤波器

如

自适应滤波器

10

第11页/共39页

2.更高的精度

模拟处理系统

依赖元器件精度

数字处理系统

取决于A/D的位数 计算机字长 先进的算法

DSP应用技术教程 部分习题答案

《TMS320C54x DSP应用技术教程》部分习题答案注意:未提供的参考答案习题(因考试为开卷形式,部分在课堂讲过,部分需要自行思考归纳总结或编程),请参考PPT和书上示例,自行解答。

第1章绪论1.简述Digital Signal Processing 和Digital Signal Processor 之间的区别与联系。

答:前者指数字信号处理的理论和方法,后者则指用于数字信号处理的可编程微处理器,简称数字信号处理器。

数字信号处理器不仅具有可编程性,而且其数字运算的速度远远超过通用微处理器,是一种适合于数字信号处理的高性能微处理器。

数字信号处理器已成为数字信号处理技术和实际应用之间的桥梁,并进一步促进了数字信号处理技术的发展,也极大地拓展了数字信号处理技术的应用领域。

2.什么是DSP技术?答:DSP技术是指使用通用DSP处理器或基于DSP核的专用器件,来实现数字信号处理的方法和技术,完成有关的任务。

5.数字信号处理的实现方法有哪些?答:参见P3-4 1.1.3节。

6.DSP的结构特点有哪些?答:哈佛结构和改进的哈佛结构、多总线结构、流水线技术、多处理单元、特殊的DSP指令、指令周期短、运算精度高、硬件配置强。

7.什么是哈佛结构和冯洛伊曼结构?它们有什么区别?答:参见P5-6 1.2.2节。

8.什么是哈佛结构和冯.诺依曼结构?它们有什么区别?答:DSP处理器将程序代码和数据的存储空间分开,各空间有自己独立的地址总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,这就是哈佛结构。

以奔腾为代表的通用微处理器,其程序代码和数据共用一个公共的存储空间和单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行的,这样的结构称为冯·诺伊曼结构。

采用哈佛结构,可同时取指令和取操作数,并行地进行指令和数据的处理,从而可以大大地提高运算的速度,非常适合于实时的数字信号处理。

而冯·诺伊曼结构当进行高速运算时,取指令和取操作数是分时操作的,这样很容易造成数据传输通道的瓶颈现象,其工作速度较慢。

多媒体技术及应用 数字音频技术02

00

60

8分音符编号

音符C3编号

2-35

多媒体 音频技术

2.4 MIDI与音乐合成

二、MIDI合成方式 1.调频合成法--FM 原理:MIDI合成器接收到MIDI音乐信息 后,利用傅立叶级数原理将其分解为若干个 不同频率的正弦波,然后生成MIDI音乐信息 中指定乐器的各个正弦波分量,最后将这些 分量合成起来送至扬声器播放。 特点:①系统开销小,声音清脆 ②声音音色少,音质较差

2.3 声卡与音箱

4.声卡的外部接口

2-22

多媒体 音频技术

2.3 声卡与音箱

用来连接外部音频设备以便进行录音,如 录音机、CD唱机和音响等 用来连接话筒,直接输入现场的声音信号 用来连接外部音频设备的输入口,也可连 接大功率有源音响等 用来连接扬声器,从声卡的内置功率放大 器向扬声器输出声音 用来连接游戏杆或MIDI设备。 用来连接CD-ROM驱动器,可以直接播放CD 音乐,而不占用CPU时间

压缩编码技术是指用某种方法使 数字化信息的编码率降低的技术

音频信号能压缩的基本依据: ① 声音信号中存在大量的冗余度; ② 人的听觉具有强音抑制弱音的现象; ③ 低频段敏感、高频段不敏感。

2-14

多媒体 音频技术

2.2 数字音频压缩标准

音频信号压缩编码的分类: ①无损压缩(熵编码) 霍夫曼编码、算术编码、行程编码 ②有损压缩 波形编码--PCM、DPCM、ADPCM 子带编码、矢量量化 参数编码--LPC 混合编码--MPLPC、CELP

多媒体 音频技术

2.3 声卡与音箱

(3)驻极体式传声器,利用驻极体材料 制作的电容传声器。 优点:简单、体积小、耐振动、价格低 (4)无线传声器,声音信号转变为电信 号,形成超高频信号。 无线传声器不是指传声器的结构原理,而 是指信号的传输方法。 优点:可随身携带、无需电缆 缺点:时远时近,影响拾音效果

DSP技术及应用习题答案

《DSP技术及应用》习题答案第1章绪论1.1 DSP的概念是什么?本书说指的DSP是什么?答:DSP有两个概念。

一是数字信号处理(Digital Signal Processing),指以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理;二是数字信号处理器(Digital Signal Processor),指是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。

本书中的DSP主要指后者,讲述数字信号处理器的应用。

1.2 什么是哈佛结构和冯•诺伊曼结构?它们有什么区别?答:(1)冯·诺伊曼(Von Neuman)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行.当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

(2)哈佛(Harvard)结构该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理.1.3 已知一个16进制数3000H,若该数分别用Q0、Q5、Q15表示,试计算该数的大小.答:3000H=12288。

若用Q0表示,则该数就是12288;若用Q5表示,则该数就是12288*2—5=384;若用Q15表示,则该数就是12288*2—15=0。

3751。

4 若某一个变量用Q10表示,试计算该变量所能表示的数值范围和精度。

答:Q10能表示的数值范围是-32~31.9990234,其精度为2-101.5 若x=0.4567,试分别用Q15、Q14、Q5将该数转换为定点数.答:Q15:x*215=int(0。

TigerSHARC处理器技术及其应用(冯小平)-第2章

2.1 TS系列DSP的内核结构概述 2.2 TS处理器的运算模块 2.3 TS处理器的整型算术逻辑单元 2.4 TS101S的程序控制器 2.5 TS20XS的程序控制器

第2章 TS系列DSP的内核结构 2.1 TS系列DSP的内核结构概述

第2章 TS系列DSP的内核结构

2) 非存储器映射寄存器 非存储器映射寄存器是一些特殊寄存器,非存储器映射寄 存器包括: (1) 运算模块的状态寄存器(XSTAT和YSTAT); (2) ALU的并行结果寄存器(XPR1~0和YPR1~0); (3) 乘法器定点乘积寄存器(XMR3~0和YMR3~0); (4) 乘法器定点乘积溢出寄存器(XMR4和YMR4); (5) 移位器的位FIFO溢出暂存寄存器(XBFOTMP和 YBFOTMP)。

第2章 TS系列DSP的内核结构

TS201S的内核结构如图2.1-2所示。 TS201S与TS101S在内核结构方面基本相同,因此本章的 后续各节将以TS101S为主,介绍TS处理器的内核中的各个模 块。

第2章 TS系列DSP的内核结构 图2.1-2 TS201S的内核结构

第2章 TS系列DSP的内核结构 2.2 TS处理器的运算模块

2.1.1 TS101S的内核结构概述 ADSP—TS101的内核结构框图如图2.1-1所示。它主要由

双运算模块、双IALU、程序控制器及其内总线等组成。

第2章 TS系列DSP的内核结构 图2.1-1 ADSP—TS101的内核结构框图

第2章 TS系列DSP的内核结构

其内核具有如下特点: (1) 双运算模块:即X和Y运算模块,各包含一套乘法器、 ALU、移位器和一套32字寄存器组。 (2) 双整型ALU:J和K整型ALU,各拥有一套32位ALU和32 字寄存器组。 (3) 程序控制器:用于控制指令流,它包含一个指令对 齐缓冲(IAB)和一个分支目标缓冲(BTB)。 (4) 内部有三套128位宽的总线,为内部存储器块之间提 供每周期48字节的高带宽连接,同时实现与外部存储器、存储 器映射I/O、主机处理器以及其他TigerSHARC的接口。

《DSP应用实例》课件

Part Three

DSP应用实例展示

语音处理实例

语音识别:将语音信号转换为文字 语音合成:将文字转换为语音信号 语音增强:提高语音信号的清晰度和可懂度 语音编码:对语音信号进行压缩和编码,以减少传输带宽和存储需求

图像处理实例

● 应用领域:图像处理、视频处理、信号处理等 ● 实例一:图像去噪 ● 实例二:图像增强 ● 实例三:图像分割 ● 实例四:图像识别 ● 实例五:图像压缩 ● 实例六:图像融合 ● 实例七:图像重建 ● 实例八:图像水印 ● 实例九:图像加密 ● 实例十:图像检索 ● 实例十一:图像分类 ● 实例十二:图像生成 ● 实例十三:图像修复 ● 实例十四:图像超分辨率 ● 实例十五:图像风格转换 ● 实例十六:图像合成 ● 实例十七:图像质量评估 ● 实例十八:图像处理算法优化 ● 实例十九:图像处理硬件加速 ● 实例二十:图像处理软件实现 ● 实例二十一:图像处理系统设计

DSP应用实例PPT课件 大纲

,

汇报人:

目录

01 添 加 目 录 项 标 题

02 D S P 技 术 概 述

03 D S P 应 用 实 例 展 示

04 D S P 技 术 实 现 方 法

05 D S P 应 用 实 例 解 析

06 D S P 应 用 实 例 总 结 与展望

Part One

单击添加章节标题

Part Four

DSP技术实现方法

DSP算法实现方法

基于DSP的算法实现方法 基于DSP的算法优化方法 基于DSP的算法测试方言:DSP 编程的主要语 言,具有高效、

简洁的特点

汇编语言:用 于优化代码, 提高执行效率

开发工具:如 CCS、IAR等, 提供代码编辑、 编译、调试等

数字信号处理及其应用

数字信号处理及其应用第一章:引言数字信号处理(Digital Signal Processing,DSP)是指利用数字信号处理技术来处理信号的方法,主要就是针对时间上的连续变化的模拟信号进行数字化处理,在数字领域进行算法求解和数字信号输出。

数字信号处理技术主要应用于通信、音频、图像、视频等多种领域。

第二章:数字信号的基本原理数字信号是由一系列离散点所组成的信号,离散点的值可以用数字形式呈现。

数字信号来源于模拟信号,其数字化过程主要包括:采样、量化和编码。

其中,采样是指用固定的时间间隔对模拟信号进行取样,得到离散的信号点;量化是指将采样得到的连续信号点映射成有限个数值,称为量化值,该过程可以理解为数字信号的离散化过程,通常按照等间距离断线方式实现。

量化过程中引入的误差称为量化误差;编码是指将采样和量化得到的数字信号用二进制的形式表示,以便于存储和传输。

第三章:数字信号的处理方法数字信号处理包括时域处理和频域处理两种方法。

1. 时域处理:时域处理是指对信号的时间变化进行处理,如差分、滤波、卷积、变换等。

时域处理方法主要应用于时域相关信号,如音频信号、生物信号等。

2. 频域处理:频域处理是指对信号的频率成分进行处理,如傅里叶变换、小波变换等。

频域处理的主要应用场景是图像处理、视频处理等。

第四章:数字信号处理的应用数字信号处理应用于多个领域,包括通过数字信号处理进行音频信号处理、图像处理等。

1. 音频信号处理:数字信号处理技术可以应用于音频编码、语音识别、语音合成、数字音频播放等多个方面,包括对声音进行去噪、降噪、声音增强等。

2. 图像处理:数字信号处理技术可以应用于图像处理、视频处理等多个方面,包括对图像进行分析、重构、压缩等。

第五章:数字信号处理的未来发展趋势数字信号处理技术的未来发展可以从多个方面展开。

一方面,随着通信技术的发展,数字信号处理技术将更加深入地应用于通信领域,例如通过数字信号处理实现高速网络、信息安全等。

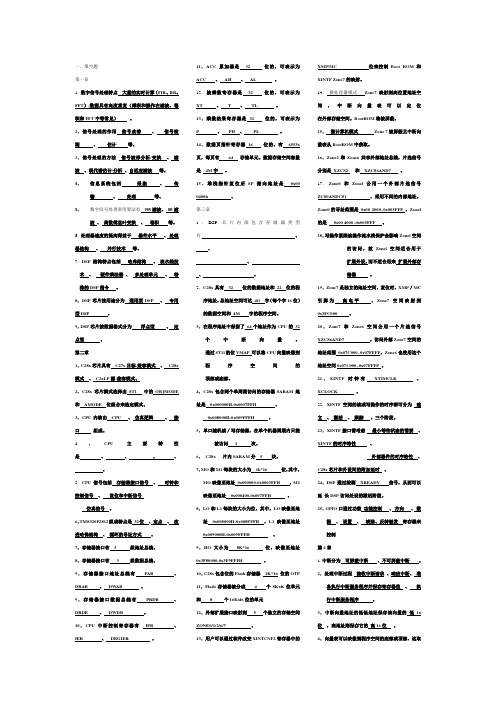

DSP技术与应用习题库 2

一、填空题第一章1.数字信号处理特点大量的实时计算(FIR、IIR、FFT),数据具有高度重复(乘积和操作在滤波、卷积和FFT中等常见)。

2.信号处理的作用信号改善、信号检测、估计等。

3.信号处理的方法信号波形分析/变换、滤波、现代谱估计/分析、自适应滤波等。

4.信息系统包括采集、传输、处理等。

5.数字信号处理常用算法有FIR滤波、IIR滤波、离散傅里叶变换、卷积等。

6.处理器速度的提高得益于器件水平、处理器结构、并行技术等。

7.DSP结构特点包括哈弗结构、流水线技术、硬件乘法器、多处理单元、特殊的DSP指令。

8.DSP芯片按用途分为通用型DSP 、专用型DSP 。

9.DSP芯片按数据格式分为浮点型、定点型。

第二章1.C28x芯片具有C27x目标-兼容模式、C28x 模式、C2xLP源-兼容模式。

2.C28x芯片模式选择由ST1 中的OBJMODE 和AMODE 位组合来选定模式。

3.CPU内核由CPU 、仿真逻辑、接口组成。

4.CPU主要特性是、、、、。

5.CPU信号包括存储器接口信号、时钟和控制信号、复位和中断信号仿真信号。

6.TMS320F2812组成特点是32位、定点、改进哈佛结构、循环的寻址方式。

7.存储器接口有 3 组地址总线。

8.存储器接口有 3 组数据总线。

9.存储器接口地址总线有PAB 、DRAB 、DWAB 。

9.存储器接口数据总线有PRDB 、DRDB 、DWDB 。

10.CPU中断控制寄存器有IFR 、IER 、DBGIER 。

11.ACC累加器是32 位的,可表示为ACC 、AH 、AL 。

12.被乘数寄存器是32 位的,可表示为XT 、T 、TL 。

13.乘数结果寄存器是32 位的,可表示为P 、PH 、PL 。

14.数据页指针寄存器16 位的,有65536页,每页有64 存储单元。

数据存储空间容量是4M字。

15.堆栈指针复位后SP指向地址是0x000400h 。

第三章1.DSP芯片内部包含存储器类型有、、、、。

西华大学 DSP技术及应用实验指导书(李天倩)

《DSP技术及应用》实验指导书适用专业:电子信息、测控、电气课程代码:总学时: 24 总学分: 2编写单位:电气信息学院信息工程系编写人:李天倩审核人:审批人:批准时间:年月日目录实验一DSP的常用指令实验 (2)实验二数字振荡器实验 (4)实验三FIR滤波器的DSP实现 (7)实验四IIR滤波器的DSP实现 (10)注释 (13)主要参考文献 (13)实验一DSP的常用指令实验一、实验目的和任务1、熟悉CCS编程环境及TMS320C54xDSP的基本算术运算指令。

2、了解TMS320C5402的存储空间分配。

3、进行DSP的基本编程调试。

二、实验内容用CCS编程环境进行DSP的基本算术运算指令的编程调试。

三、实验仪器、设备及材料安装有WINDOWS98以上操作系统和CCS2.0(`C5000)的计算机。

四、实验原理借用计算机的资源仿真DSP的内部结构,以学习DSP的基本编程。

五、主要技术重点、难点主要技术重点:CCS编程环境,TMS320C5402的存储空间分配,DSP的基本算术运算指令。

主要技术难点:DSP的基本算术运算指令的运用。

六、实验步骤1、鼠标左键双击桌面“Setup CCS 2 ('C5000)”图标启动CCS Setup,鼠标左键依次单击“C5402Simulator”,“Import”,“Save and Quit”,“是(Y)”启动CCS,在[Project]-[Open]菜单中打开ex1.pjt;2、在左边树状列表框内双击[Project]展开目录树,双击[ex1.asm]打开源程序文件,参考程序中的注释仔细阅读源程序;3、在[Project]-[Build]菜单中编译项目文件,编译成功后在下端的状态窗口中显示Build Complete,0Errors,0 Warnings;4、在[File]-[Load Programm]中加载输出执行代码文件ex1.out,选择[View]-[ [Disassembly ]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. (1) 具有192K字的可寻址空间: 64K字的程序空间, 64K 字的数据空间和64K字的I/O空间, 有的芯片内还具有多达 256K~8M (2) 片内存储器的结构和容量可根据芯片的型号有所不同。

3. (1) (2) (3) 片内的锁相环(PLL)时钟发生器, 可采用内部振荡器

(4) 外部总线关断控制电路可用来断开外部数据总线、 地 址总线和控制信号。

C54x的硬件结构基本上可分为三大块, (1) CPU部分包括算术逻辑单元、 累加器、 乘法器/加法 器、 桶形移位寄存器、 指数编码器、比较选择存储单元及各 种专门用途的寄存器、 地址生成器、 内部总线等。

(2) 存储器部分包括片内程序ROM、 片内单访问数据 RAM(SARAM)、 片内双访问数据RAM(DARAM)及外接存储

在C54x DSP中, 根据存储内容的需要, 可将片内ROM 和RAM存储器安排(也称映射)到程序存储器空间或数据存储器 空间。 一般将ROM映射到程序存储器空间, 也可以将其某段 存储器映射到数据存储器空间。

C54x有一个处理器模式寄存器(Processor Mode Status Register, PMST), 如图2.2所示, 其中有3个状态位(MP/MC 位、 OVLY位和DROM位)可以很方便地“使能”或“禁止” 片内存储器在程序和数据空间之间的映射。

(3) 可控制禁止CLKOUT信号。

8. 具有符合IEEE 1149.1标准的片内仿真接口, 可与主机连 接, 用于系统芯片的开发与应用。

2.2 总 线 结

C54x片内有8条16位总线: 1条程序总线、 3条数据总线 和4条地址总线, 这些总线的功能如下:

(1) 1条程序总线(PB)传送取自程序存储器的指令代码和立 即操作数。

第2章 TMS320C54x数字信号 处理器硬件结构

2.1 TMS320C54x的内部结构及主要特性 2.2 总线结构 2.3 存储系统 2.4 中央处理单元(CPU) 2.5 TMS320VC5416的引脚及说明

2.1 TMS320C54x的内部结构及主要特性

2.1.1 TMS320C54x

TMS320C54x系列DSP芯片产品虽然很多, 但其体系 结构基本上是相同的, 特别是核心CPU部分, 各个型号间 的差别主要是片内存储器和片内外设的配置。 图2.1给出了 TMS320C54x的典型内部结构框图。

(2) 3条数据总线(CB、 DB和EB)将内部各单元(如CPU、 数据地址生成电路、 程序地址生成电路、 芯片外围电路以及 数据存储器)连接在一起。 其中, CB和DB传送来自数据存储 器的数据, EB传送写到存储器的数据。

(3) 4条地址总线(PAB、 CAB、 DAB和EAB)传送执行指 令所需的地址。

图 2.2 PMST结构框图

PMST中3个状态位MP/MC、 OVLY和DROM的功能如下。 (1) MP/MC: 微处理器/ 若MP/MC=0, 则片内ROM映射到程序存储器空间; 若 MP/MC=1, 则片内ROM不能访问, 若访问其对应地址, 则 需访问相应地址的外部程序存储器空间。

2) OVLY: RAM重复占用位。 OVLY=1, 片内RAM既可映射到程序存储器空间, 也 可映射到数据存储器空间, DSP根据映射地址分辨其中存储单 元的内容是程序代码还是数据。 若映射到程序存储器空间, 则看做程序代码, 若映射到数据存储器空间, 则看做数据。 开发人员在安排具体内容时, 两者地址不要重叠。 OVLY=0, 片内RAM只能映射到数据存储器空间而不能 映射到程序存储器空间。

4. 除TMS320C5420外, C54x系列所有的芯片都具有片内引 导功能, 能从片外的存储器或片内的串口将程序引导并装入 指定的存储器。

5. (1) (2) (3) 32 (4) 同时读入2个或3 (5) 并行存储和装入的算术指令。

(6) (7) (8) (9) 指令的执行采用指令预提取、 指令提取、 指令译码、 访问操作数、 读取操作数和执行6级流水线并行结构, 大大提 高了指令的执行速度。

PB能够将存放在程序空间中的操作数(如系数表)传送到乘 法器和加法器, 以便执行乘法/累加操作, 或通过数据传送 指令(MVPD和READA指令)传送到数据空间的目的地。 此种 功能, 连同双操作数的特性, 支持在一个周期内执行3操作数 指令(如FIRS指令)

2.3 存 储 系 统

Байду номын сангаас2.3.1 存储器空间

6. (1) 单指令周期时间分为25/20/15/12.5/10 ns; (2) 每秒指令数为40/50/66/80/100/200 MIPS(MIPS, 每秒 百万级指令数)。

7. (1) 可采用5V、 3.3V、 3V和1.8V(或2.5V)的超低电压 供电; 在型号中分别用C、 LC、 UC和VC指明, 如 TMS320C54x、 TMS320LC54x和TMS320UC54x (2) 可采用功耗下降指令IDLE1、 IDLE2和IDLE3控制芯片

(3) 片内外设部分包括定时器、 各种类型的串口、 主机接 口、 片内的锁相环(PLL)时钟发生器以及各种控制电路等。

此外, 芯片中还包含仿真功能及IEEE 1149.1标准接口,

图 2.1 TMS320C54x的典型内部结构框图

2.1.2 TMS320C54x

1. CPU (1) 先进的多总线结构, 具有1条程序总线、 3条数据总线 和4条地址总线。 (2) 40位算术逻辑单元(ALU), 包括40位的桶形移位寄存 器和2个独立的40位的累加器。

(3) 17位×l7位的并行乘法器与一个40位的专用加法器结 合在一起, 用于非流水线的单周期乘/

(4) 比较、 选择和存储单元(CSSU), 用于Viterbi操作(一 种通信的编码方式)中的求和/

(5) 指数编码器用于单周期内计算40位累加器的指数值。 (6) 2个地址生成器, 包括8个辅助寄存器和2个辅助寄存 器算术单元。

(5) (6) (7) 直接存储器访问(DMA) (8) 有可与主机直接连接的8位并行主机接口(HPI), 有些 产品还包括扩展的8位并行主机接口(HPI8)和16位并行主机接 口(HPI16) (9) 片内的串口根据型号不同可分为全双工的标准串口、 支持8位和16位数据传送的时分多路(TDM)串口、 缓冲串口 (BSP)以及多通道缓冲串口(McBSP)。