dsp实验指导书

DSP实验指导书

实CCS开发环境的使用【实验目的】1.熟悉Code Composer Studio开发环境,了解相关的开发工具。

2.掌握DSP软件开发流程。

通过使用CCS软件,学会创建工程、编译、连接工程3.掌握CCS软件的调试方法。

学习使用CCS的探针和断点调试工程,能够用图形窗口观察数据。

【实验原理】CCS (Code Composer Studio)是TI公司为其TMS320系列DSP提供的一个高度集成的软件开发和调试环境,它将DSP工程项目管理、源代码的编辑、目标代码的生成、调试和分析都打包在一个环境中,使其可以基本涵盖软件开发的每一个环节。

CCS主要包括以下工具:1. C编译器、汇编优化器和连接器(代码生成工具)2.指令集仿真器(Simulator)3.实时的基础软件(DSP/BIOS)4.主机和目标机之间的实时数据交换(RTDX)5.实时分析和数据可视化利用CCS,用户可以方便地建立一个DSP的工程项目,并对相应的源文件进行管理或编辑修改。

所有源文件的编译、汇编和连接只需要一个按钮就可以一次完成,用户不必再通过输入冗长的命令行来完成这些操作。

经过上面的过程产生的目标代码可以在CCS的环境下通过硬件仿真工具,如XDS510等,下载到用户目标系统中进行调试和运行。

如果没有用户目标系统,还可以将目标代码装载到Simulator中运行。

Simulator利用计算机的资源模拟DSP的运行情况,可以帮助用户熟悉DSP的内部结构和指令,在有的情况下还可以对部分的程序功能进行非实时的验证。

在CCS中,用户可以利用其提供的数据可视化工具按照数据的格式来观察数据,如眼图、星座图、FFT瀑布图等,较好的分析数据。

【实验内容与步骤】1.创建一个新项目工程1)从菜单或者快捷方式中打开CCS。

图1CCS界面2)选择Project→New。

在myprojects文件夹中建立一个以自己姓名拼音命名的新的工程文件,如”zhangsan”,如下图所示:图2项目创建对话框3) 在Target中选择器件类型"TMS320C54xx"。

DSP实验指导书_新版_

§5.12 [实验 5.12] FIR 滤波器实时处理实验..................................................115 §5.13 [实验 5.13] 利用信号发生模块的 FFT 实验 ........................................119 §5.14 [实验 5.14] TMS32C5410 的 Bootloader 实验 ...................................... 123 §5.15 [实验 5.15] AIC23 的数字录音机实验 ................................................ 128 §5.16 [实验 5.16] TMS320LF2407A FLASH 烧写实验 .................................. 130 §5.17 [实验 5.17] 数字图像基本处理实验(选做)..................................... 133 第六章 §6.1 §6.2 附录 ................................................................................................ 137 [附录 1] TMS320C5410 DSP 芯片简介 ............................................... 137 [附录 2] TMS320C54X 指令速查表.................................................... 144

百科融创科技有限公司Байду номын сангаас

DSP实验指导书

DSP实验指导书DSP原理与应⽤实验指导书张卫宁王晓东⼆零⼀零年四⽉⽬录第⼀部分软件仿真(Simulator)实验实验⼀集成开发环境CCS应⽤基础实验⼆寻址⽅式实验三定点定标运算实验四浮点运算实验五汇编程序的优化实验六C语⾔编程与优化(乘法—累加运算程序设计)实验七混合编程实验实验⼋FIR滤波器的实现实验九基于DSP的数字图像处理算法的实现第⼆部分硬件(Emulator)实验实验⼗⽚内定时器实验实验⼗⼀数字I/O⼝的应⽤实验⼗⼆同步串⼝与A/D转换实验⼗三基于DSP的数字⾳频处理系统第三部分部分实验程序参考清单实验⼀参考程序实验⼆参考程序实验三参考程序实验四参考程序实验五参考程序第四部分参考资料⼀、C54xCPU的存储器映像寄存器及其地址⼆、C54xCPU的状态和控制寄存器ST0、ST1三、TMS320C5416DSP的存储区映像四、C54xCPU的处理器模式状态寄存器PMST五、C54x的⽚内定时器控制寄存器TCR六、TMS320C5416的中断⽮量表参考⽂献第⼀部分软件仿真(Simulator)实验实验⼀集成开发环境CCS应⽤基础⼀、⽬的1. 通过创建⼀个简单的应⽤⼯程,初步熟悉Code Composer Studio(简称CCS)的集成开发环境(IDE)及其⼯具的使⽤。

2. 掌握汇编语⾔源程序的基本框架和编写⽅法,了解CCS的⼯程结构以及编译、汇编、连接、运⾏和调试的基本过程。

3. 了解ST0、ST1的控制位对计算过程的控制以及计算结果对状态位的影响。

⼆、内容1. 学习使⽤CCS集成开发环境(IDE)的各种⼯具。

包括下列内容:(1)编辑、汇编和连接。

(2)查看和修改存储器映像寄存器的内容。

(3)查看和修改ST0、ST1及PMST的有关位。

(4)查看和修改程序存储器和数据存储器的内容。

(5)断点操作。

(6)运⾏程序(单步运⾏、连续运⾏和断点运⾏)。

2. 观察并理解COFF段结构的划分及存储空间的分配。

DSP实验指导书

实验一常用指令实验一、实验目的1、了解DSP开发系统的组成和结构;2、掌握DSP开发系统连接过程和DSP的开发界面;3,熟悉LF2407系列的寻址系统及常用LF2407系列指令的用法。

二、实验设备计算机,CCS 2.0版软件,DSP仿真器,EXP3实验箱。

三.实验步骤与内容开发TM S 320C2xxx应用系统一般需要以下几个调试工具来完成:(1)软件集成开发环境(CodeComposer):完成系统的软件开发,进行软件和硬件仿真调试。

它也是硬件调试的辅助乎段。

(2)开发系统:实现硬件仿真调试时与硬件系统的通信,控制和读取硬件系统的状态和数据。

(3)评估模块:提供软件运行和调试的平台和用户系统开发的参照。

(4) CodeComposer4.1卞要完成系统的软件开发和调试。

它提供一整套的程序编制、维打…、编译、调试环境,能将汇编语言和C语言程序编译连接生成COFF(公共目标文件)格式的可执行文件,并能将程序下载到目标DSP上运行调试。

(5)用户系统的软件部分可以由CodeComposer建立的工程文件进行管理,工程文件一般包含以下几种文件:源程序文件:C语言或汇编语言文件(*.ASM或*.C)头文件(*H)命令文件(*.CMD)库文件(*.LIB)中断向量交件(*.ASM)★启动CodeComposer双击桌面上“CC C2000 "启动Code Composer 4.1;可以看到显示出的C2XX CodeComposer窗口;★创建工程(1)创建新的工程文件:选择菜单“Project”的“New...”项;输入工程文件名字并保存;这时建立的是一个空的工程文件;.(2)在工程文件中添加程序文件:选择菜单“Project”的“Add Files to Project...”项;在“Add Files to Project”对话框中改变文件类型为“Asm Source Files(.a*;*.s*)",选择文件“*asm";重复上述各步骤,再添加以下文件到工程中;*.cmd, vector.asm.(3)编译连接工程:选择菜单“Project”的“Rebuild All”项;注意编译过程中CCS卞窗日下部的“Build"提示窗中显示编译信息,最后将给出错误和警告的统计数;编辑修改工程中的文件.(4)查看工程文件展开CCS卞窗日左侧工程管理窗中的工程各分支,可以看到“*.mak*工程中包含"*.asm","*.cmd"和"*.h;,其中“*.h”为程序在编译时根据程序中的“include"语句自动加入的;(5).查看源文件双击工程竹理窗中的“`'`as m”文件,可以查看程序内容;双击工程竹理窗中的“`'`.h”文件,打开此文件显示,可以看到其中有卞程序中要用到的一些寄存器等;" *.cmd”文件定义程序所放置的位置,此例中描述了LF2407的片内存储器资源,指定了程序和数据在内存中的位置;(6)基本调试功能:a)执行File-Load Program,在随后打开的对话框中选择刚刚建立的*.out文件;在项日浏览窗日中,双击`'`.rim激活这个文件,移动光标到start 行上,右击鼠标选择Toggle Breakpoint或按F9设置断点;b)使用观察窗口执行View令Watch window打开观察窗日;在`*asm中,选中任意一个变量,右击鼠标,选择”Quickwatch",CCS将打开quickwatch窗口并显示选中的变量;在`*asm中,选中任意一个变量,右击鼠标,选择”Add to watch window",CCS将把变量添加到观察窗日并显示选中的变量值;在观察窗日中双击变量,则弹出修改变量窗日,此时,可以在这个窗日中改变程序变量的值。

DSP实验指导书-图文

DSP实验指导书-图文数字信号处理E某PIV教学实验系统110实验五离散余弦变换(DCT)算法实验一、实验目的学习DCT算法的实现方法。

二、实验设备计算机,CCS2.0版软件,实验箱,DSP仿真器。

三、实验原理离散余弦变换与离散傅立叶变换紧密相关的,属于正弦类正交变换,由于其优良的去冗余性能及高效快速算法的可实现性,被广泛用于语音及图象的有损和无损压缩。

在开始实验之前,应了解以下基本原理。

1.语音或图象的压缩手段;2.DCT变换在数据压缩中的作用与应用。

四、实验步骤1.阅读本实验所提供的样例子程序;2.运行样例程序,分析结果;3.样例程序实验操作说明A.实验前准备1)正确完成计算机、DSP仿真器和实验箱连接后,开关K9拨到右边,即仿真器选择连接右边的CPU:CPU2;系统上电;2)“A/D转换单元”的拨码开关设置:JP3拨码开关:码位123456备注ON:将“模拟信号源”单元的信号输入到AD7822OFF:OFF:OFF:OFF:OFF:SW2拨码开关:SW21ON2ON3ON4备注码位ONAD7822的采样时钟为250KHZ,且中断给CPU2的中断2数字信号处理E某PIV教学实验系统111S23拨码开关:码位1、2B.实验启动CCS2.0,Project/Open打开“Algorithm”目录中“e某p05_cpu2”子目录下“E某p-DCT-AD.pjt”工程文件;双击“E某p-DCT-AD.pjt”及“Source”可查看各源程序;加载“E某p-DCT-AD.out”;在主程序中,在flag=0处设置断点;单击“Run”运备注OFF,不混频行程序,程序将运行至断点处停止;数字信号处理E某PIV教学实验系统112用View/Graph/Time/Frequency打开两个图形观察窗口;采用双踪观察在启始地址分别为某和y,长度为128的单元中数值的变化,数值类型为32位浮点型,这两个数组分别存放的是经A/D转换的输入信号和对该信号进行DCT变换的结果;再打开一个图形观察窗口,设置观察变量为z;变量z为输入信号的DCT变换及逆DCT变换的结果,长度128,32位浮点型,即输入信号的重构信号;调整各图形观察窗口,观察正变换与逆变换结果;单击“Animate”运行程序,调整各图形观察窗口,动态观察变换结果;改变输入信号的波形、频率、幅值,动态观察变换结果;数字信号处理E某PIV教学实验系统113单击“Halt”暂停程序运行,关闭窗口,实验结束;实验结果:在CCS2.0环境,同步观察输入信号及其DCT变换结果。

DSP实验指导书

实验一 CCS基本操作重点:掌握CCS基本操作,工程的建立及调试方法。

难点:源程序调试方法。

(一)实验目的1.掌握Code Composer Studio2.2的安装和配置。

2.了解DSP开发系统和计算机与目标系统的连接方法。

3.了解Code Composer Studio 2.2软件的操作环境和基本功能,了解TMS320C2xxx软件开发过程。

⑴学习创建工程和管理工程的方法。

⑵了解基本的编译和调试功能。

⑶学习使用观察窗口。

⑷了解图形功能的使用。

(二)实验设备计算机、DSP硬件仿真器、SZ-DSP II实验开发平台(三)实验原理让学生了解怎样连接DSP仿真器、对CCS的仿真配置及怎样在CCS内新建工程并生成*.out文件。

(四)实验步骤1.连接实验设备2.启动Code Composer Studio双击桌面上“CCS C2000”,启动Code Composer Studio 2.2;可以看到显示出的C2XX Code Composer Studio窗口;3.创建工程(1)创建工程文件选择菜单“Project”的“New…”项;在Project对话框中输入“yima”作为项目文件名;在“Location”对话框中改变目录到D:\yima,并保存。

(2)往工程中加入文件选择project→Add Files to Project,选择38译码文件夹中的.asm,加入工程中。

重复上述各步骤,再添加.cmd文件到yima工程中4.浏览代码和Windows的资源管理器相似,只要打开+号展现下面的文件,然后双击文件的图标,在主窗口就会显示相应文件的原始代码。

5.编译/执行程序1)选择Project→Rebuild All或工具栏中的相应按钮。

2)编译成功后,选择File→Load Program。

选择你刚编译的可执行程序exp1.out。

3)选择Debug→Run,或工具栏中的相应图标。

6.程序调试的环境应用(1)跟踪/调试程序1)选择Debut→Restart,重新执行程序。

DSP实验指导书_简化版

第一章.实验系统标准配置SZ-DSP II型模块简介:1、TI主控板(2407、5402、5416)其中任意一种2、ALTERA的CPLD系统模板一块3、高速或者高精度A/D、D/A板可选4、CAN总线接口(2407用)5、USB接口6、同步串行口(5416用)7、232、485异步串口电路8、语音芯片TLC320AD50(5416用)9、I/O 扩展电路10、语音电路11、CPLD电路12、单片机管理单元13、拨码功能选择电路14、键盘、液晶屏电路15、数码管、发光二极管显示电路16、机电控制模块(可选)18、视频模块(可选)实验仪的开关、插座定义及初始状态:1、J28是USB接口2、J24为CAN总线接口3、DB9插座是232异步串行接口4、J3是485接口5、M3是耳机插孔,语音输出用6、M1是麦克风插孔,语音输入用7、J31是可外扩的DSP高16位数据和高位地址线接口(位于主板的最左上方),其具体管脚定义如下:1~8脚是DSP的高位地址线A23~A16;9~24脚是DSP的高16位地址线D31~D16;8、J32是可外扩的DSP低16位地址线和数据线接口,其具体管脚定义如下:1~16脚是DSP的低16位地址线A15~A0;17~32脚为DSP的低16位数据线D0~D15;31脚是电源端+5V,32脚是接地端GND。

9、J43为DSP F2407的16位A/D引出端,其具体管脚分布如下:1~16是DSP 2407的16位A/D ADCIN00~ADCIN15;17脚是模拟地AGND,18脚是模拟电压A3.3V。

10、J33是CPLD或FPGA(以下简称CPLD)的I/O脚用来做控制线的输出端,可做二次开发用,其接口如下:1~10脚是DSP小系统上的CPLD的I/O引出端,可作为信号的输出用;11~20脚是DSP小系统上的CPLD的I/O引出端,可作为信号的输入输出用;21、31脚是空脚;22脚是DSP的时钟引出端;23、24、25脚分别可作为FLASH的写控制、读控制、片选;26、28 脚为DSP小系统上CPLD的全局使能引出端,可作为信号输入也可为全局使能信号;27、30脚为DSP小系统上CPLD的时钟引出端,可作为输入信号也可为时钟输入;29脚是DSP小系统上CPLD的引出端,可作为信号输入;32脚是复位信号RESET。

dsp实验指导书

dsp实验指导书实验一I/O实验实验目的:熟悉SZ—DSPII实验平台的使用了解DSP对I/O口的访问方式熟悉简单的程序设计及指令运用实验设备:计算机;DSP硬件仿真器;DSP实验开发平台实验硬件设置:在做实验以前,需要接通该实验的硬件电路,本实验为:先将实验箱右侧的船型开关往“I”方向打开电源,然后将系统主板的开关S33往下拨接通+/-5V电源,然后将CPLD/FPGA模块上的电源开关S9往下(ON)拨,开关S10往下拨来选通主板上发光二极管等输出指示设备;将系统主板中“MCU/DSP选择档”选中MCU(往下拨),将“功能键7”拨上去,电击键盘中的RST键,MCU将对所有发光二极管进行检测,如果所有的发光二极管正常,则将“MCU/DSP选择挡”选中DSP,将功能键1到7都拨下来。

然后开始做实验,注意在做实验时开始按了RST硬件复位后,实验不要再按RST键,以免由于DSP复位而失败。

如果实验中硬件工作不正常,可按RST对整个系统硬件进行复位。

实验原理:本程序主要是实现将数据往一个I/O端口送,从而显示一种状态,来验证DSP对I/O口的访问。

该实验是由DSP直接编程,往发光二极管送数,运用PORTW指令,观察发光二极管的变化,从而完成基本的I/O实验。

D8-D15高八位数据DSPCPLD锁存8个指示灯指示灯的片选1002H硬件框图实验程序框图DSP送出不同的数据DSP初始化开始输出到1002H实验程序FG_ADDR.et1002HDATADELAY.macroec_tenthloop1STM#09h,AR6loop0STM#19999,AR7BANZ$,某AR7-BANZloop0,某AR6-BANZloop1,某AR5-.endm ;延时ec_tenth/10秒STMec_tenth-1,AR5reet:.et60h;doubleramdata.ect\B_c_int00NOPNOP.pace31某4某16.title\.global_c_int00.mmreg.te某tLD#0h,DPSTM#3000h,SPRSB某INTMSTM#07FFFh,SWWSR;工作在20MHz_c_int00:SSB某某F;某F=1ST#1007h,CLKMDRPT#0FFhNOPSTM#0ffffh,IFRORM#000h,IMRRSB某S某MST#8100H,DATA#10WRDENG:PORTWDATA,FG_ADDRDELAYNOPST#4200H,DATADATA,FG_ADDR#10PORTWDELAYST#2400H,DATAPORTWDELAYST#1800H,DATAPORTWDELAY#10ST#1800H,DATAPORTWDELAYDATA,FG_ADDR#10DATA,FG_ADDRDATA,FG_ADDR#10RPT#10NOPST#2400H,DATAPORTWDELAYRPT#10NOPST#4200H,DATAPORTWDELAYRPT#10NOPST#8100H,DATAPORTWDELAYRPT#10NOPSTM#00H,DATA;;;PORTWDELAYNOPST#100H,DATADATA,FG_ADDR#10PORTWDELAYST#200H,DATAPORTWDELAYST#400H,DATAPORTWDELAY#10DATA,FG_ADDRDATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10ST#800H,DATAPORTWDELAYRPT#10NOPST#1000H,DATAPORTWDELAY#10RPT#10NOPST#2000H,DATAPORTWDELAYRPT#10NOPST#4000H,DATAPORTWDELAYRPT#10NOPSTM#8000H,DATAPORTWDELAYRPT#10NOP;;;ST#8000H,DATAPORTWDELAYST#4000H,DATADATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDRDATA,FG_ADDR#10PORTWDELAYDATA,FG_ADDR#10ST#2000H,DATAPORTWDELAY#10ST#1000H,DATAPORTWDELAYRPT#10NOPST#800H,DATAPORTWDELAY#10RPT#10NOPST#400H,DATAPORTWDELAYRPT#10NOPST#200H,DATAPORTWDELAYRPT#10NOPSTM#100H,DATAPORTWDELAYRPT#10NOPST#8100H,DATADATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDRDATA,FG_ADDR#10DATA,FG_ADDRBWRDENGaaanopbaaa.end思考题:有哪三种以上的寻址方式可以完成上述实验?并描述其原理。

DSP实验指导书

实验一 DSP教学实验系统与集成开发环境入门一、实验目的1、熟悉CCS集成开发环境,掌握工程的生成方法;2、熟悉SEED-DTK BPD实验环境;3、掌握CCS集成开发环境的调试方法;4、了解数在计算过程中的定标,掌握数的定点、浮点表示方法,定点、浮点基本运算以及定点、浮点间的相互转换。

二、实验设备(仪器)计算机;DSP仿真器;SEED-DTK BPD型DSP实验箱三、实验内容1、DSP源文件的建立;2、DSP程序工程文件的建立;3、编译与链接的设置,生成可执行的DSP文件;4、进行DSP程序的调试与改错;5、学习使用CCS集成开发工具的调试工具;6、观察实验结果;四、实验步骤1、打开CCS 集成开发环境,进入CCS的Simulator操作环境。

2、新建源文件创建一个未知名的源文件编写源代码并保存保存源程序名为DTK_BPD_MATH.c创建其他源程序(如.cmd)可重复上述步骤3、建立新工程,打开CCS,点击Project-->New,创建一个新工程工程名及路径可任意指定。

这里新建一个名为DTK_BPD_MATH.pjt的工程,路径为C:\tic2000\myprojects\DTK_BPD_MATH。

点击Project,选择add files to project,添加DTK_BPD_MATH.c、math.cmd、rts2800_ml.lib 文件到工程中。

在下面窗口中可以看到DTK_BPD_MATH.c、math.cmd、rts2800_ml.lib文件已经加到工程文件中。

4、设置编译与连接选项设置相应的编译参数,一般情况下,按默认值就可以。

设置连接顺序,注:当使用rts2800_ml.lib 时将其放在最后。

点击Project-->Build all,对工程进行编译,如正确则生成DTK_BPD_MATH.out;若是修改程序,可以使用Project->Build命令,进行编译连接,它只对修改部分做编译连接工作,可节省编译与连接的时间。

DSP技术实验指导书

DSP技术实验指导书陈军波刘海华编电子信息工程学院信号处理教研室2005年10月目 录第一部分DSP实验教学平台功能介绍 (3)☆结构简介: (3)☆数据流程图 (17)第二部分基础实验 (20)实验一CCS操作与DSP综合外设控制实验 (20)实验二DSP存储器及基本指令实验 (33)实验三快速傅里叶变换(FFT)实现 (38)实验四有限冲击响应滤波器(FIR)实现 (43)实验五无限冲击响应滤波器(IIR)实现 (51)实验六实时语音FIR滤波设计实验 (57)第三部分创新性实验 (60)实验一温度测量实验 (60)实验二YUV彩色图像处理之增强对比度 (62)实验三脉冲幅度相干(PAM)解调实验 (66)实验四MP3音频解码实验 (70)提示:请不要带电拔插仿真器和板卡!第一部分DSP实验教学平台功能介绍☆结构简介:一、主要功能模块:1、主CPU(SZ-5416D)模块:采用TI公司TMS320C5416DSP(以下简称5416)芯片,该模块上的资源有:4mbit flash、256k*16bit SRAM、2500 gate CPLD、电平转换芯片,模块上留有JTAG 插口,用户可以通过仿真器和CCS下载程序和进行实验;2、主CPU(SZ-2407E)模块:采用TI公司TMS320LF2407DSP(以下简称2407)芯片,该模块上的资源有:256k*16bit SRAM、2500 gate CPLD、电平转换芯片,模块上留有JTAG插口,用户可以通过仿真器和CCS下载程序和进行实验;以上两个模块可以通过5416的HPI接口实现双DSP的高速并行数据交换。

在实现对其他对象操作时,在平台的主板采用了CPLD(XC95216)来实现两DSP之间的软切换。

3、图象、语音模块(SZ-DSPFVV板):图象采用高速AD(TLC5510)和高速的DA(TLC5602),同时TLC5510和TLC5602又可做普通的AD、DA实验;语音模块采用专用语音处理芯片TLC320AD50C,最高采样率为22.05KHz,16位串行接口。

DSP实验指导书

节 1.01 §1.2 使用方法1. 电源本实验箱内部自带变压器,使用时不需另配低压电源,可直接用普通三相插头接入220V电源。

接上电源后,由电源模块输出±12V,±5V,3.3V,分别送至实验箱的各个模块。

另外为方便单独使用,两个主控板上都设有独立的电源输入端口,可以接入5V的直流电源。

2. 仿真器接口在做实验时,需要一个DSP仿真器,把在计算机上编译并生成的执行代码下载到5509或2812芯片上。

仿真器有两端接口,其中一端与计算机的并行口或USB口相连,这取决于仿真器的类型;另一端与DSP芯片的JTAG 接口相连,这是一个14针的接口,在两块主控板上都可以找到。

仿真器连接好后才能对主控板上的DSP芯片进行读写控制。

4. 计算机的配置DSP实验中的代码编写,下载仿真和程序调试都必须在计算机上完成。

计算机上需要安装DSP集成开发环境软件CCS(使用2.2或3.1版本)。

计算机应具备最少32M内存,100M硬盘空间和奔腾处理器,显示器分辨率不能低于800*600。

另外,部分模块的实验还要求计算机配有标准的USB接口,DB9串行接口以及RJ-45网卡接口。

5. 其它配件包括USB连接线,串行口连接线,网线,排线等。

节 1.02 §2.1 基础实验一、实验目的1. 掌握CCS实验环境的使用;2. 掌握用C语言编写DSP程序的方法。

二、实验设备1. 一台装有CCS软件的计算机;2. DSP实验箱的TMS320F2812主控板;3. DSP硬件仿真器。

三、实验原理浮点数的表达和计算是进行数字信号处理的基本知识;产生正弦信号是数字信号处理中经常用到的运算;C语言是现代数字信号处理表达的基础语言和通用语言。

写实现程序时需要注意两点:(1)浮点数的范围及存储格式;(2)DSP的C语言与ANSI C语言的区别。

四、实验步骤1.打开CCS 并熟悉其界面;2.在CCS环境中打开本实验的工程(Example_base.pjt),编译并重建.out 输出文件,然后通过仿真器把执行代码下载到DSP芯片中;3.把X0 , Y0 和Z0添加到Watch窗口中作为观察对象(选中变量名,单击鼠标右键,在弹出菜单中选择“Add Watch Window”命令);4.选择view->graph->time/frequency…。

DSP实验指导书

实验一 CCS基本操作(一)实验目的熟悉CCS 2.0软件的使用熟悉SZ-DSP II实验平台的使用掌握使用DSP实现16位定点加、减、乘、除运算的编程方法(二)实验设备计算机; DSP硬件仿真器; SZ-DSP II实验开发平台(三)实验原理(1)定点DSP中数据表示方法C54X是16位定点DSP。

一个16位在二进制既可表示一个整数,也可以表示一个小数。

当它表示一个整数据时,其最低位(D0)表示20,D1位表示21,次高位表示(D14)表示214。

如果表示一个有符号时,最高位(D15)为符号位,0表示正数,1表示负数。

例如,07FFFH表示最大的正整数32767(十进制),而0FFFH表示最大负数-1(负数用2的补码方式显示)。

当需要表示小数时,小数点的位置始终在最高位后,而最高位(D15)表示符号。

这样次高位(D14)表示1-1,,然后是2-2,最低位(D0)表示2-15,所以04000H 表示小数0.5,01000H表示小数2-3=0.125,而0001H表示16位定点DSP能表示的最小数(有符号)2-15=0.000030517578125。

在后面的实验中,除非有特别的说明,我们指的是有符号数。

在C54x中,将一个小数用16位定点格式来表示的方法是用2-15乘以该小数,然后取整。

从上面的分析可以看出,在DSP中一个16进制的数可以表示不同的十进制数,或者是整数,或者是小数(如果表示小数,必定小于1)但仅仅是在做整数乘除或小数乘除时,系统对它们的处理才是有所区别的,而在加法运算时,系统都当成整数来处理。

(2)实现16位定点加法C54x中提供了多条用于加法的指令,如ADD,ADDC,ADDM和ADDS。

其中ADDS用于无符号数的加法运算,ADDC用于带进位的加法运算(如32位扩展精度加法),而ADDM专用于立即数的加法。

ADD指令的寻址方式很多,其详细使用说明请参考《TMS320C54X》。

DSP实验及课程设计指导书

第一部分ICETEK–VC5509-A 评估板硬件使用指导第一章ICETEK–VC5509-A 评估板技术指标主处理芯片:TMS320VC5509A;低功耗设计,比上一代C54XX 器件功耗低30%左右;处理速度更快,双核结构,处理速度400MIPS;软件程序兼容C54XX DSP;片内存贮空间128K×16Bit;大容量SDRAM 设计:4M×16Bit;2路10bit 片上A/D 接口;2路的TLC7528 转换,5M/S,8Bit;UART 串行接口,符合RS232 标准;8M bit 扩展FLASH,存储大量固化程序和数据;设计有用户可以自定义的开关和测试指示灯;3U标准的DSP 扩展总线,包括数据、地址、I/O、控制;4组标准扩展连接器,为用户进行二次开发提供条件;具有IEEE1149.1 相兼容的逻辑扫描电路,该电路仅用于测试和仿真;+5V电源输入,内部+3.3V、+1.6V 电源管理;高保真语音接口设计,双路语音采集,每路48K/S;USB 2.0 接口设计;4层板设计工艺,稳定可靠;具有自启动功能设计,可以实现脱机工作;可以选配多种应用接口板,包括图像板,网络板等;第二章 ICETEK–VC5509-A 原理图和实物图1.ICETEK–VC5509-A 评估板接口说明实物图(参见图1-1):图1-1 ICETEK–VC5509-A 接口说明实物图2.ICETEK–VC5509-A 器件布局图(参见图1-2):图1-2 ICETEK–VC5509-A 器件布局图3.ICETEK–VC5509-A 评估板原理框图(参见图1-3):图1-3 ICETEK–VC5509-A 原理框图第三章接插件位置和拨档开关设置U5 四路拨档开关设置:U5-1、U5-2、U5-3 和U5-4 分别按顺序对应连接TMS320VC5509DSP 的GPIO0-GPIO3,当DSP 在复位时读取这四个引脚上的状态确定使用哪一种启动模式。

DSP技术实验指导书

2407DSP 实验指导书实验一 CCS 的使用及输出实验一、 实验目的1、 了解DSP 开发系统的组成和结构;2、 熟悉DSP 开发系统的连接;3、 熟悉DSP 的开发界面;4、 熟悉LF2407系列的寻址系统;5、 熟悉常用LF2407系列指令的用法。

二、 实验设备计算机,CCS 2.0版软件,DSP 仿真器,DSP CPU 挂箱。

三、 实验步骤与内容1、 系统连接进行DSP 实验之前,先必须连接好仿真器、实验箱及计算机,连接方法如下所示:2、 上电复位在硬件安装完成后,确认安装正确、各实验部件及电源连接正常后,接通仿真器电源或启动计算机,此时,仿真盒上的“红色指示灯”应点亮,否则DSP 开发系统与计算机连接有问题。

3、 运行CCS 程序待计算机启动成功后,实验箱220V 电源置“ON ”,实验箱上电,启动CCS ,此时仿真器上的“绿色指示灯”应点亮,并且CCS 正常启动,表明系统连接正常;否则仿真器的连接、JTAG 接口或CCS 相关设置存在问题,掉电,检查仿真器的连接、JTAG 接口连接,或检查CCS 相关设置是否正确。

注:如在此出现问题,可能是系统没有正常复位或连接错误,应重新检查系统硬件并复 位;也可能是软件安装或设置有问题,应尝试调整软件系统设置,具体仿真器和仿真软件CCS 的应用方法参见第三章。

●成功运行CCS 程序后,首先应熟悉CCS 的用户界面●学会CCS 环境下程序编写、调试、编译、装载,学习如何使用观察窗口等。

PCI/USB/EPP 接口 JTAG 接口 计 算 机 仿 真 器 实验箱 CPU 板4、创建工程环境CCS提供工程文件来管理应用程序,所有有关的应用程序的信息保存在工程文件中。

工程文件记录生成一个目标DSP程序和库程序需要的所有文件和运行库。

它也包含了为编译,汇编,链接目标代码而配置的开关参数。

在这部分,你将学习到如何创建工程文件,添加源程序文件和库文件到工程中,以及编辑源程序文件和编译连接生成目标代码。

DSP实验指导书完全版正文_图文(精)

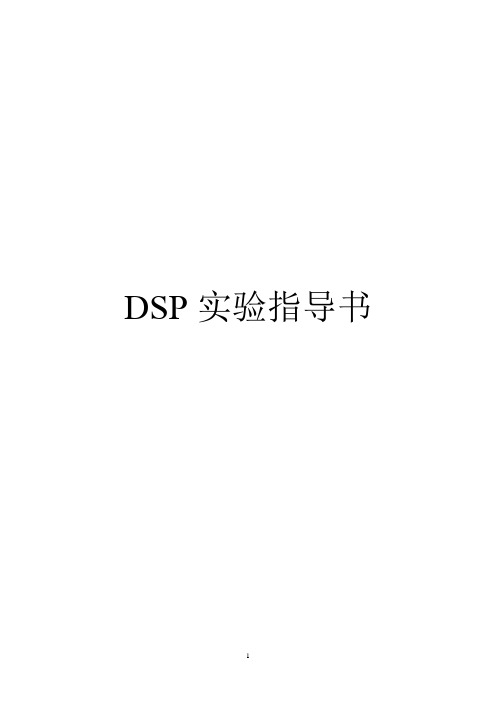

第一章实验系统介绍一、系统概述EL-DSP-EXPII教学实验系统属于一种综合的教学实验系统,该系统采用双CPU 设计,实现了DSP 的多处理器协调工作。

两个DSP 通过HPI 口并行连接,CPU1可以通过HPI 主机接口访问CPU2的存储空间。

该系统采用模块化分离式结构,使用灵活方便用户二次开发。

客户可根据自己的需求选用不同类型的CPU 适配板,我公司所有CPU 适配板是完全兼容的,用户在不需要改变任何配置情况下,更换CPU 适配板即可作TI 公司的不同类型的DSP 的相关试验。

除此之外,在实验板上有丰富的外围扩展资源(数字、模拟信号发生器,数字量IO 扩展,语音CODEC 编解码、控制对象、人机接口等单元),可以完成DSP 基础实验、算法实验、控制对象实验和编解码通信试验。

EL-DSP-EXPII 教学实验系统功能框图二、硬件组成该实验系统其硬件资源主要包括:● CPU 单元● 数字量输入输出单元● 存储器及信号扩展单元● BOOTLOADER 单元● 语音模块● 液晶模块● CPLD 接口● A/D转换单元● D/A转换单元● 信号源单元● 温控单元● 步进电机● 直流电机● 键盘接口●电源模块1、 C PU 单元CPU 单元包括CPU1、CPU2两块可以更换的 CPU板,用户可根据需要选择不同种类的CPU 板。

板上除CPU 之外还包括以下单元: 1) CPU模式选择CPU 通常情况下可以根据用户需求工作在不同的模式下,主要用MP/MC ————的电平来决定。

当MP/MC ————为高电平时,DSP 工作在微处理器模式,当MP/MC —————为低电平时。

DSP 工作在为计算机方式。

在不同模式下存储器映射表有所不同。

详细信息请查阅相应的数据手册。

2)电源模块在CPU 板上由于TMS320VC54X 数字信号处理器内核采用3.3V 和1.8V 供电,因此需要将通用的5V 转换成3.3V 和1.8V 。

DSP实验指导书

DSP实验指导书目录实验一正弦信号发生器 (1)实验二AM系统 (8)实验三DDS (16)实验四FSK调制系统 (25)实验五快速傅里叶变换 (32)实验六16阶FIR滤波器 (51)实验七IIR滤波器 (62)实验一正弦信号发生器一、实验仪器:PC机一台,JQ-SOPC-2C35实验箱一台及辅助软件(DSP Builder、Matlab/Simulink、Quartus II、Modelsim)。

二、实验目的:1. 初步了解JQ-NIOS-2C35实验箱的基本结构;2。

学习和熟悉基于DSP Builder开发数字信号处理实验的流程。

三、实验原理:正弦波是一种基本信号,任何复杂信号都可由许多频率、幅度各不相同的正弦波复合而成。

已知正弦波存在如下的关系:αsinαπ+sin(=2)由以上公式可知,正弦波存在周期性,本实验就是根据正弦波的这一特性进行正弦波发生。

在Altera DSP Builder库中,有一名为Increment Decrement的模块,根据参数设置的不同,Increment Decrement会不断从0计数到设定值,然后清0,接着又从0开始计数。

图3-1显示的是Increment Decrement的参数设置界面,以图中参数为例,number of bits设置为6,即从0开始计数到2^6,然后清0,接着又从0开始计数。

在LUT(Look Up Table)查找表模块中事先存入一个周期的正弦波的抽样值,利用Increment Decrement模块不断计数,根据计数值找到查找表的地址取出里面的值进行输出,因为Increment Decrement模块的输出具有周期性,则从LUT的输出也具有了周期性,这样,就产生了正弦波。

四、实验步骤:本实验的操作步骤如下:1.点击桌面上的Matlab图标,进入Matlab主界面,并将工作目录设为Matlab安装目录下的work文件夹,如图1所示:图1 Matlab启动界面2.点击菜单栏中的File->New->Model,新建一个模型,在Matlab命令窗口中输入simulink命令,调出simulink工具栏,如图2所示:图2 新建模型3.双击simulink工具栏中的Altera DSP Builder中的Arithmetic库,找到Increment Decrement模块,选中它并按住鼠标左键将其拖到新建的模型文件中,如图3所示:图3 添加模块4.双击模型文件中的Increment Decrement模块,打开模块参数对话框,将Bus Type设为Signed Integer,number of bits设为6,保持其他参数不变,点击【OK】按钮确认。

DSP实验指导书wzz

DSP实验指导书第一章软硬件仿真系统的安装与使用1.1硬件仿真器的安装与使用1.1.1 硬件仿真系统的安装第一步、取出实验平台,检查配件是否齐全(见实验平台内的装箱单)A. 关闭PC机电源,将专用25芯并口电缆插入并口中,注意插接要稳固。

B.安装好后,用专用25芯并口电缆的另一头连接仿真器。

C.启动PC机,驱动程序在仿真器随机光盘里。

第二步、不连接电源,将DSP(所配置如LF2407、VC5402、VC33等)板按照主板说明书插入实验箱上的插槽中(出厂时已插好)。

第三步、开启电源。

如安装成功:此时,实验平台上的+12V、-12V、+5V、-5V指示灯亮起。

1.1.2 硬件仿真器的使用硬件仿真器是数字信号处理系统开发的必备工具,它是采用边界扫描技术和DSP芯片通过JTAG口相连接。

实现了主机对DSP芯片的完全检测和控制。

可以通过JTAG和相应的软件的再现调试开发工作。

硬件仿真器的用法比较简单,只要将JTAG连接正确(出厂时已经连接好),DSP芯片能够正常工作并且软件调试环境配置正确即可以应用。

上面给出JTAG的定义;1.2开发系统软件安装配置和应用1.2.1开发系统软件安装1.2.1.1 Code Composer Studio软件安装系统要求要使用Code Composer Studio,你的操作平台必须满足以下的要求:● IBM PC(或兼容机)● Microsft Window98● 32M内存,100M硬盘空间,奔腾处理器,SVGA(800*600)1.2.1.2 Code Composer Studio 的安装完整的安装CCS软件包括以下两个步骤:(1)安装CCS到系统中。

将CCS安装光盘放入到光盘驱动器中,运行CCS安装程序setup.exe,将CCS安装在C盘根目录下。

安装完成后,在桌面会有“CCS C50001.20”和“setup CCS C50001.20”两个快捷方式图标。

分别对应CCS应用程序和CCS配置程序。

DSP实验指导书

PDF 文件使用 "pdfFactory Pro" 试用版本创建

85 bk2:绝对地址寻址方式-数据存储器地址寻址;数据观察窗口地址为实际程序所编。 bk3:绝对地址寻址方式-程序存储器地址寻址;打开内存窗口的程序观察窗口地址 为,实际程序所编写(如程序中定义 PDAT0 为 1F00,地址就为 1F00)。 bk4:累加器寻址方式;打开寄存器和内存的数据观察窗口。 bk5:直接寻址方式(DP 为基准),打内存的数据观察窗口。 bk6:直接寻址方式(SP 为基准),打内存的数据观察窗口。 bk7:间接寻址方式,打开寄存器和内存的数据观察窗口。 bk8:存储器映射寄存器寻址方式,打开寄存器观察窗口。 bk9:堆栈寻址方式,打开寄存器观察窗口。 Bk10: 程序存储器到数据存储器的复制,打开寄存器观察窗口。 具体实验程序请参考:随机光盘里的 hmem 文件夹。 (六)思考题 1、如何将程序存储器其中某一起始地址的 0x100 个字复制到数据存储器的 0x4000 为起 始地址的空间中? 2、如何实现用 C 语言编写一个对可用数据内存清零程序?

DSP实验指导书(10学时)

基于ICETEK-VC5416AE-S60实验指导书电子信息系2011.01实验一、集成开发环境CCS入门实验一.实验目的1.掌握Code Composer Studio 2.21的安装和配置步骤过程。

2.了解DSP开发系统和计算机与目标系统的连接方法。

3.了解Code Composer Studio 2.21软件的操作环境和基本功能,了解TMS320C5xxx软件开发过程。

(1) 学习创建工程和管理工程的方法。

(2) 了解基本的编译和调试功能。

(3) 学习使用观察窗口。

(4) 了解图形功能的使用。

二.实验设备1.PC兼容机一台;操作系统为Windows2000 (或WindowsXP)2.ICETEK-VC5416-AE-EDU实验箱一台。

3.USB连接电缆一条。

三.说明* 开发TMS320C5xxx应用系统一般需要以下几个调试工具来完成:- 软件集成开发环境(Code Composer Studio 2.21):完成系统的软件开发,进行软件和硬件仿真调试。

它也是硬件调试的辅助手段。

- 开发系统(ICETEK 5100 USB或ICETEK 5100 PP):实现硬件仿真调试时与硬件系统的通信,控制和读取硬件系统的状态和数据。

- 评估模块(ICETEK VC5416-A等):提供软件运行和调试的平台和用户系统开发的参照。

* Code Composer Studio 2.21主要完成系统的软件开发和调试。

它提供一整套的程序编制、维护、编译、调试环境,能将汇编语言和C语言程序编译连接生成COFF (公共目标文件)格式的可执行文件,并能将程序下载到目标DSP上运行调试。

* 用户系统的软件部分可以由CCS建立的工程文件进行管理,工程一般包含以下几种文件:- 源程序文件:C语言或汇编语言文件(*.ASM或*.C)- 头文件(*.H)- 命令文件(*.CMD)- 库文件(*.LIB,*.OBJ)四.实验步骤1.启动Code Composer Studio 2.212.创建工程(1) 创建新的工程文件展开主窗口左侧工程管理窗口中“Projects”下新建立的“volume.pjt”,其中各项均为空。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图1-1 正弦发生器模型(model文件)

(3)在Altera DSP Builder中的Arithmetic库,找到Increment Decrement模块加入到新建的model中; 双 击该模块并设置参数,Bus Type:Signed Integer、number of bits:6,确认退出。 (4)在Altera DSP Builder中的Storage库,找到LUT模块加入到新建的model中; 双击该模块并设置参 数 , Data Type : Signed Integer 、 Address Width : 6 、 number of bits : 8 、 MATLAB Array : 127*sin( [0:2*pi/(2^6):2*pi] ),确认退出。 (5)在Altera DSP Builder中的Storage库,找到Delay模块加入到新建的model中。 (6)在Altera DSP Builder中的Arithmetic库,找到Product模块加入到新建的model中,双击该模块并设 置参数,Optional ports and settings中的Use LPM选项前打勾,确认退出。 ( 7)在 Altera DSP Builder中的IO&Bus 库,找到 Input 和Output 模块加入到新建的model中。双击 Input 模块并设置参数,Bus Type:Single Bit,确认退出。双击Output模块并设置参数,Bus Type:Signed Intege、 number of bits:8,确认退出。 ( 8) 在 Simulink 中的 Sinks 库, 找到 Scope 模块加入到新建的 model 中。 双击 Scope 模块并设置参数, 点击菜单栏中的 ,将 number of axes 设为 2,确认退出。

表 2-2 模型名称 AltBus Constant Bus conversion 参数设置 number of Bits:32; Constant Value:88234567;number of Bits:32; Input:32; output:10; Input Bit Connected to Output LSB:22 Data Type:Signed Integer;number of bits:10; MATLAB Array:511*sin([0:2*pi/(2^10):2*pi])

(21) 打开实验箱, 接入电源, 用USB Blaster线将电脑和实验箱连接起来, 选择菜单栏中的

(22)点击Hardware Setup,选择USB-0,点击【Close】确认。选中sinwave.sof文件,点击Start,将文 件下载到实验板上。 ( 23 ) 执 行 Tools SignalTap Ⅱ Logic Analyzer , 选 择 Hardware 右 边 的 Setup , 将 其 设 为 USB-Blaster[USB-0]。 (24)将实验箱上的开关SW[3]和SW[4]拨至高电平,点击工具栏的 采集,一段时间(约10s)后点击 (红色图标)图标,启动数据

LUT

(5)Mux 子系统如图 2-2 所示,添加的模型和设置参数表 2-3 所示。

5

实验二

AM 系统

图 2-2 Mux 子系统连接图 表 2-3 Mux 子系统参数设置 位置 Altera DSP Builder Blockset IO&Bus 名称 Input 参数设置 Bus Type:Unsigned Integer; [number of bits].[]:3; 勾选 Specify Clock; Clock:Clock; Number of Input Data Lines:8; Constant Value:0.89844 Bus Type:Signed Fractional [number of bits].[]:2 [].[number of bits]:8 Constant Value:0.79688 Bus Type:Signed Fractional [number of bits].[]:2 [].[number of bits]:8 Constant Value:0.69922 Bus Type:Signed Fractional [number of bits].[]:2 [].[number of bits]:8 Constant Value:0.59766 Bus Type:Signed Fractional [number of bits].[]:2 [].[number of bits]:8 Constant Value:0.5 Bus Type:Signed Fractional [number of bits].[]:2 [].[number of bits]:8 Constant Value:0.39844 Bus Type:Signed Fractional [number of bits].[]:2 [].[number of bits]:8 重置名称

Altera DSP Builder Blockset Gate&Control Altera DSP Builder Blockset IO&Bus

Multiplexer Constant

Constant5

Altera DSP Builder Blockset IO&Bus

Constant

录下的 work\sinwave_dspbuilder)打开文件 sinwave.qpf

。

(17)工具栏中点击 Assignments,选中 Device,在器件 family 中选择 Cyclone Ⅱ,选择下拉菜单中 的 EP2C35F672C6.,点击 finish。 (18)执行AssignmetsAssignment Editor,将Category设为Pin,并按照下图对Pin进行设置并保存

DSP 实验指导书

(2013 年 06 月 04 日)

实验一 正弦信号发生器

实验一 正弦信号发生器

实验步骤: 本实验的操作步骤如下: (1)打开MATLAB。 (2)从 MATLAB 界面打开点 simulink 文件 。 ,从跳出的 Simulink Library Browser 界面新建一个 model

Constant6

Altera DSP Builder Blockset IO&Bus

Altera DSP Builder Blockset Storage

LUT

Altera DSP Builder Blockset IO&Bus

Constant

(3)将图 2-1 的所有模块选中,单击鼠标右键,点击 Creat Subsystem,点击子系统下文本,将其重命 名为“DDS”。 (4)复制粘贴 DDS,得到“DDS1”。双击 DDS1,并按照表格 2-2 调整参数值。

图标停止数据采集,点击SignalTap中的data窗口,右键点击Output,选

择Bus Display FormatSigned Line Chart,即可看到硬件实现的波形。如图6所示:

图1-3 硬件实现结果

3

实验一 正弦信号发生器

(25)最后打开MATLAB安装目录下的 work文件夹,删除其中的所有文件。

2

实验一 正弦信号发生器

图1-2 管脚设置

(19)执行 ToolsSignalTap Ⅱ Logic Analyzer,选中 Data

,在 Data 窗口中的空

白处双击,在弹出的对话框中将 Fiter 设为 Pins: all®isters:post fittings,点击 List,将 Output 添加至右边 的窗口中,点击【OK】确认。 ( 20)在右边的对话框中将Clock设为 Clock信号,Sample depth设为 1K,点选Trigger in,Source设为 Clock信号,Pattern设为Rising edge。保存,若弹出对话框询问是否将文件添加至工程,选择Yes。点击菜 单栏中的 (紫色三角形),重新对工程进行编译。 图标。

图1-2 Modelsim仿真

(14)随后显示的界面即为Modelsim RTL级仿真的波形图。选中tb_sinwave/dut/output信号,点击鼠标 右键,选中Propertyties选项,选择 Format为analog,将Height设为100,Scale设为0.4,点击【OK】确认。 在信号上点击鼠标右键,选择Zoom Full,即可看到RTL级仿真波形。 (15)点击Signal Compiler模块,打开参数设置页面,器件系列选择cylone II,点击compile,结束后, 关闭该页面。 (16)关闭 MATLAB。在位置“D:\Program Files\MATLAB71\work\sinwave_dspbuilder”(MATLAB 安装目

Hale Waihona Puke 名称参数设置Bus Type:Signed Integer; number of Bits:16 Bus Type:Signed Integer; [number of bits].[]:16; Number of Pipeline Stages:2;

重置名称

Pipelined Adder

Pipelined Adder3

4

实验二

AM 系统

实验二 AM 系统

实验步骤: (1)打开 MATLAB。 (2)新建 model 文件 如图 2-1,添加的模型和设置参数如表 2-1。

图 2-1 DDS 连接图 表 2-1 DDS 参数设置

位置

Altera DSP Builder Blockset IO&Bus Altera DSP Builder Blockset Arithmetic Altera DSP Builder Blockset Storage Altera DSP Builder Blockset IO&Bus Altbus