飞思卡尔s12单片机-动态数码管显示与键盘模块(1)

飞思卡尔S12G系列芯片Demo程序之【按键中断实验】

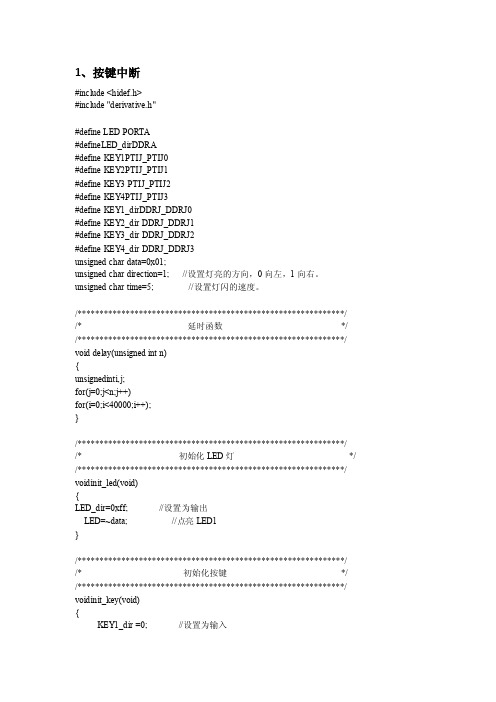

1、按键中断#include <hidef.h>#include "derivative.h"#define LED PORTA#defineLED_dirDDRA#define KEY1PTIJ_PTIJ0#define KEY2PTIJ_PTIJ1#define KEY3 PTIJ_PTIJ2#define KEY4PTIJ_PTIJ3#define KEY1_dirDDRJ_DDRJ0#define KEY2_dir DDRJ_DDRJ1#define KEY3_dir DDRJ_DDRJ2#define KEY4_dir DDRJ_DDRJ3unsigned char data=0x01;unsigned char direction=1; //设置灯亮的方向,0向左,1向右。

unsigned char time=5; //设置灯闪的速度。

/*************************************************************/ /* 延时函数*/ /*************************************************************/ void delay(unsigned int n){unsignedinti,j;for(j=0;j<n;j++)for(i=0;i<40000;i++);}/*************************************************************/ /* 初始化LED灯*/ /*************************************************************/ voidinit_led(void){LED_dir=0xff; //设置为输出LED=~data; //点亮LED1}/*************************************************************/ /* 初始化按键*/ /*************************************************************/ voidinit_key(void){KEY1_dir =0; //设置为输入KEY2_dir=0;KEY3_dir=0;KEY4_dir=0;PPSJ = 0x00; //极性选择寄存器,选择下降沿;PIFJ = 0x0f; //对PIFJ的每一位写1来清除标志位;PIEJ = 0x0f; //中断使能寄存器;}/*************************************************************/ /* 按键中断函数*/ /*************************************************************/ #pragma CODE_SEG __NEAR_SEG NON_BANKEDinterrupt void PTJ_inter(void){if(PIFJ != 0) //判断中断标志{PIFJ = 0xff; //清除中断标志if(KEY1 == 0) //按键1按下{time-=1;if(time==0)time=1;}if(KEY2 == 0){time+=1;if(time>10)time=10;}if(KEY3 == 0)direction=0;if(KEY4 == 0)direction=1;}}#pragma CODE_SEG DEFAULT/*************************************************************/ /* 主函数*/ /*************************************************************/ void main(void){DisableInterrupts;init_led();init_key();EnableInterrupts;for(;;){delay(time);if(direction==1){data=data<<1; //左移一位if(data==0)data=0x01;}else{data=data>>1; //右移一位if(data==0)data=0x80;}LED = ~data;}}2、按键中断#include <hidef.h>#include "derivative.h"#define LEDCPU PORTD_PD3#define LEDCPU_dirDDRD_DDRD3unsigned char single = 0;/*************************************************************/ /* 初始化锁相环*/ /* 使用外部晶振:16MHz */ /* 设置总线频率:16MHz */ /*************************************************************/ void INIT_PLL(void){CPMUPROT=0x26; //解除时钟配置保护CPMUCLKS_PSTP = 0; //禁止PLLCPMUCLKS_PLLSEL = 1; //设置PLLCLK为系统时钟CPMUOSC_OSCE=1; //使能外部晶振CPMUSYNR=0x01; //SYNDIV的值为1,CPMUREFDIV = 0x81; //REFDIV的值为1CPMUPOSTDIV=0x00;CPMUPLL=0x10; //锁相环调频启用,用以减少噪音while(CPMUFLG_LOCK==0); //等待PLLCLK锁定CPMUPROT=0x01; //使能时钟配置保护}/*************************************************************//* 初始化实时中断*//*************************************************************/void INIT_RTI(void){CPMUPROT=0x26; //解除时钟配置保护CPMUCLKS_RTIOSCSEL = 1; //RTI时钟源为晶振时钟CPMUINT = 0x80; //使能实时中断CPMURTI = 0x6f; //设置实时中断的时间间隔为32.768ms,根据机器周期求得CPMUPROT= 0x01; //使能时钟配置保护}/*************************************************************//* 实时中断函数(声明中断函数)*//*************************************************************/#pragma CODE_SEG __NEAR_SEG NON_BANKED/*中断函数置于非分页区内,由于飞思卡尔16位单片机的中断向量是16位所以中断函数只有被置于非分页区内才能被寻址到,这就是第一行的作用*///#pragma主要作用是设定编译器状态,指示编译器完成一些特定动作interrupt void RTI_inter(void){if(CPMUFLG_RTIF == 1)CPMUFLG_RTIF = 1;single +=1;if (single==15){LEDCPU = ~LEDCPU;single = 0;}}#pragma CODE_SEG DEFAULT/*后续代码置于默认区内,由于单片机内部非分页区大小有限,非中断函数一般置于分页区内,最后一行即为此作用*//*************************************************************//* 主函数*//*************************************************************/void main(void){DisableInterrupts;INIT_PLL();INIT_RTI();LEDCPU_dir = 1;LEDCPU = 0;EnableInterrupts;for(;;){}}以上Demo程序已通过本人亲自验证,可实现相关功能,对代码中有疑问的朋友欢迎在主页区留言交流。

飞思卡尔程序调试技巧

一、前言调试程序,是软件开发过程中的一个必不可少的环节。

这篇帖子,匠人试着来整理一下一些调试的技巧。

说到“技巧”,这个词自从被所长批臭之后,匠人就吓得不敢再提,生怕一不小心就暴露了思想的浅薄和眼光的局限,呵呵。

所以咱们不叫“技巧”,干脆低调点,就叫“雕虫小技”吧。

这里所讨论的“调试”技巧,有些是必须结合开发工具本身的功能来实现,而有些可以通过烧录芯片来验证。

各种开发工具,提供的功能多少强弱也不尽相同,这些方法也未必都能套用。

仅供参考吧。

最后说明一下,这是没有草稿的帖子,匠人仍然以不定期连载的方式,边写边发边改。

可能结构会比较混乱。

欢迎大家一起参与讨论。

二、磨刀不误砍柴功在调试之前,需要掌握以下一些基本功:1、熟悉当前的开发(调试)环境,比如:设置断点、单步运行、全速运行、终止运行,查看RAM、查看堆栈、查看IO口状态……总之,要熟练掌握基本操作的方法,并深刻了解其中意义。

2、了解芯片本身的资源和特性。

3、了解一点汇编语言的知识。

(本来匠人是准备写“精通”的,但考虑到现状,还是“放低”这方面的要求罢了)。

4、掌握基本的电路知识和排错能力。

(软件调试有时也会牵涉到硬件原因。

总不能连三极管的好坏都不能识别吧?)5、万用表、示波器、信号发生器……这些工具总该会用吧?6、搜索、鉴别资料的能力。

(内事问百度、外事问古狗、有事没事上21ic网)7、与人沟通,描述问题的能力。

(调试36计的最后一计——就是向他人讨教。

当然,你得把话说明白才行)差不多了,如果上述7把砍柴刀磨好了,就可以开始调试了。

接下来,请调入你的程序……三、优先调试人机界面面对程序中的一大堆模块,无从下手是吗?好吧,匠人告诉你,先调显示模块,然后是键盘。

为什么要先调显示模块?道理很简单,我们说“眼睛是心灵的窗户”,同样,“显示是程序的窗户”。

一旦把显示模块调试好了,就可以通过这个窗口,偷窥(天呐,这两个居然是敏感字!)程序内部的数据和状态了。

然后紧接着,就是调试键盘模块。

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置手把手教你写S12XS128程序--PWM模块介绍该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使能位控制PWM 的输出。

键盘、数码管显示综合实验

实验项目名称:键盘、数码管显示综合实验实验室(中心):电子实验室实验完成时间: 09 年11 月 5 日1一.实验目的与要求通过实验,掌握单片机在输入输出口线不够用时,怎样扩展接口的方法来支持8位LED 显示和16键盘集成实现。

熟悉8155、8279等芯片性能;掌握其编程方法。

掌握键盘子程序调试方法,掌握按一个键并将键值显示出来的编程方法,这是诊断硬件、测试硬件、产品开发、软件编程必须掌握的方法。

二.实验原理及实验线路(1)通过8155芯片的扩展功能,建立描述线与数据线同步功能,如图三.实验内容①编写并调试出一个键盘实验子程序;②用子程序调用方法,分别调用键盘子程序和显示子程序,将按一个键的键值(0-F),在数码管上显示出来。

四.实验器材表2.4.5(1):以8155为扩展方式的器件80C51.BUS CRYSTAL PHYC0402NP022P7404 7SEG-MPX6-CC-BLUE RESPACK-88155 HITEMP10U50VBUTTON MINRES10K五、实验程序流程图六.实验步骤1)仿真实验过程:打开Keil程序,执行菜单命令“Project”→“New Project”创建“键盘数码管显示综合实验”项目,并选择单片机型号为AT89C52.BUS。

执行菜单命令“File”→“New”创建文件,输入源程序,保存为“键盘数码管显示综合实验.A51或键盘数码管显示综合实验.c”。

在“Project”栏的File项目管理窗口中右击文件组,选择“Add Files to Group ‘Source Group1’”将源程序“键盘数码管显示综合实验.A51或键盘数码管显示综合实验.c”添加到项目中。

执行菜单命令“Project”→“Options for Target ‘Target 1’”,在弹出的对话框中选择“Output”选项卡,选中“Greate HEX File”。

执行菜单命令“Project”→“Build Target”,编译源程序。

飞思卡尔11章 S12串行通信模块

1 1 2 3 4 5 6 7 8

11.2 SCI串行通信接口 SCI串行通信---异步通信,最常用;SCI基本概念: 1、异步串行通信的格式(NRZ,8位或9位,异步通信:每一数据块的字符以起

始位“0”表示开始;停止位 “1”表示结束)

开始位 第0位 第1位 第2位 第3位 第4位 第5位 第6位 第7位 停止位

SBR7 SBR6 SBR5 SBR4

SBR3 SBR2 SBR1

波特率计算公式:波特率=总线频率/(16xBR),编程时按16位送数,如: LDX #13 STX SCI0BD ; 2MHz/(16x13)=9600bps

重庆大学通信工程学院 任勇

(2) SCI控制寄存器---SCIxCR1、SCIxCR2

P

P

0

1

2

3

4

5

6

7

L

1

1

1

1

1

3

4

5

6

2

1

1

0

1

2

3

4

5

1

1 6

2

1 5

3

1 4

4

1 3

5

1 2

6

1 1

7

1 0

【实例】SPI输入的开关检测。(74LS165:并入串出)

8

9

1

1

1

1

1

1

1

6

5

4

3

2

1

0

9

1

R

VCC

0

1

SW-DIP8

S K

使用SPI,节省MCU的引脚,但须增加外接移位寄存器。

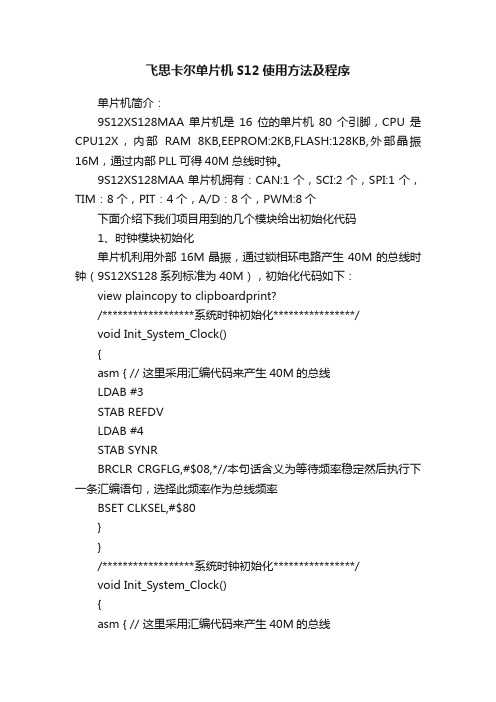

飞思卡尔单片机S12使用方法及程序

飞思卡尔单片机S12使用方法及程序单片机简介:9S12XS128MAA单片机是16位的单片机80个引脚,CPU是CPU12X,内部RAM 8KB,EEPROM:2KB,FLASH:128KB,外部晶振16M,通过内部PLL可得40M总线时钟。

9S12XS128MAA单片机拥有:CAN:1个,SCI:2个,SPI:1个,TIM:8个,PIT:4个,A/D:8个,PWM:8个下面介绍下我们项目用到的几个模块给出初始化代码1、时钟模块初始化单片机利用外部16M晶振,通过锁相环电路产生40M的总线时钟(9S12XS128系列标准为40M),初始化代码如下:view plaincopy to clipboardprint?/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}}/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}上面的代码是汇编写的,这个因为汇编代码量比较少,所以用它写了,具体含义注释已经给出,主函数中调用此函数即可完成时钟初始化,总线时钟为40M.2、SCI模块初始化单片机电路做好了当然少不了和PC之间的通信,通信通过单片机串口SCI链接到PC 端的COM口上去。

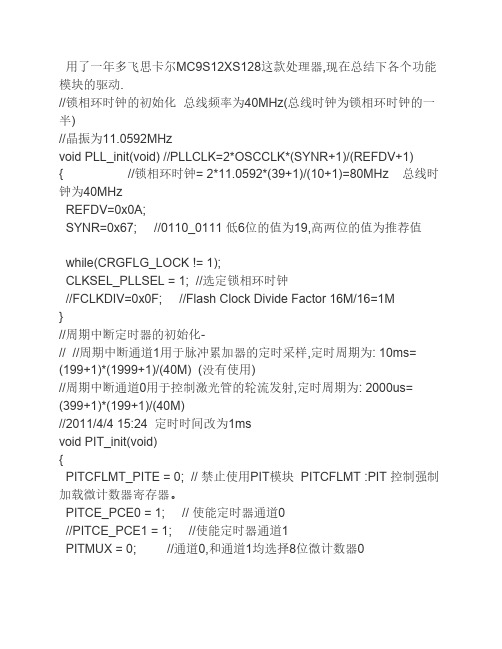

飞思卡尔MC9S12XS128功能模块驱动

用了一年多飞思卡尔MC9S12XS128这款处理器,现在总结下各个功能模块的驱动.//锁相环时钟的初始化总线频率为40MHz(总线时钟为锁相环时钟的一半)//晶振为11.0592MHzvoid PLL_init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1) { //锁相环时钟= 2*11.0592*(39+1)/(10+1)=80MHz 总线时钟为40MHzREFDV=0x0A;SYNR=0x67; //0110_0111 低6位的值为19,高两位的值为推荐值while(CRGFLG_LOCK != 1);CLKSEL_PLLSEL = 1; //选定锁相环时钟//FCLKDIV=0x0F; //Flash Clock Divide Factor 16M/16=1M}//周期中断定时器的初始化-// //周期中断通道1用于脉冲累加器的定时采样,定时周期为: 10ms= (199+1)*(1999+1)/(40M) (没有使用)//周期中断通道0用于控制激光管的轮流发射,定时周期为: 2000us= (399+1)*(199+1)/(40M)//2011/4/4 15:24 定时时间改为1msvoid PIT_init(void){PITCFLMT_PITE = 0; // 禁止使用PIT模块 PITCFLMT :PIT 控制强制加载微计数器寄存器。

PITCE_PCE0 = 1; // 使能定时器通道0//PITCE_PCE1 = 1; //使能定时器通道1PITMUX = 0; //通道0,和通道1均选择8位微计数器0//修改时间只需要改下面四行PITMTLD0 = 199; //向8位微计数器中加载的值PITLD0 = 199; //向16位计数器中加载的值//PITMTLD1 = 39; //向8位微计数器中加载的值 8位,最大值不要超过255//PITLD1 = 1999; //向16位计数器中加载的值PITINTE |= 0x01; //使能定时器通道0的中断PITCFLMT_PITE = 1;//使能PIT模块}//脉冲累加器的初始化, PT7口外接光电编码器//最新修改: 2011/3/25 16:53void PT7_PulAcc_Init(void){DDRT &= 0x77;//设置PT7,PT3口为输入(硬件上PT7,PT3通过跳线联到了一块)PERT |= 0x80; //使能通道7的上拉电阻PPST &= 0x7f; //电阻设为上拉电阻TCTL4 &= 0x3f; //禁止PT3的输入捕捉功能PACTL = 0x50; //启动脉冲累加计数器,上升沿触发,禁止触发中断和溢出中断,主定时器禁止}//通道1用于控制舵机1 PWM 高电平有效,//通道3用于控制电机1 PWM 低电平有效,这与前两代车高电平有效有区别!!!!!//通道7用于给上排激光管提供PWM信号 PWM高电平有效!!!!!//通道6用于给下排激光管提供PWM信号 PWM高电平有效!!!!!// 2011-03-17 7:56 增加了A端口的使用新增通道6//2011-6-9 23:03 //增加了通道4,5的联合使用,用于控制下排方向舵机 void PWM_init(void){PWME = 0x00;//PWM禁止PWMPRCLK = 0x03; // ClockA=40M/8=5M, Clock B = 40M/1=40M PWMSCLB = 10; // Clock SB= 40/2*10= 2MHz(供电机)PWMSCLA = 5; // SA = Clock A/2*5 = 5M/10 = 500K = SA 用于控制舵机PWMPOL = 0xe2; //1110_0010通道7,通道6与通道1、通道5先输出高电平然后输出低电平,POLx=1先输出高电平后输出低电平; PPOLx=0先输出低电平)PWMCAE = 0x00; // 左对齐输出(CAEx=0为左对齐,反之为中心对齐)//PWMCLK = 0010_1010 (0 1 4 5位控制SA_1;或A_0; 2 3 6 7位控制SB_1 或B_0)//为PWM通道1选择时钟 SA(500KHz),//为PWM通道5选择时钟 SA(500KHz),//为通道3选择时钟 SB(10MHz)//为通道7选择时钟B(40MHz)//为通道6选择时钟B(40MHz)PWMCLK = 0x2A; //0010_1010PWMCTL = 0x70; //0111_0000 CON45=1,把通道4,5联合使用。

飞思卡尔MC9S12XS128单片机重点模块讲解

�

这一点和 51 单片机的 I/O 口有区别,在典型的 51 单片中 P0 口内部没有上拉电阻,但作为 I/O 口使用时需要外接排阻。其他 P1-P3 口则可以直接作为双向口使用,51 单片在上电复位 后端口被默认的置 1.在 51 单片中端口的某一位置 0 时端口作为输出口使用,置 1 时作为输 入口使用。例如如果我们想把 P1 作为输出口使用时我们可以在程序开始时写 P1=0x00; 如果 我们想把 P1 口作为输入口使用时我们可以写 P1=0xff; 这一点正好和飞思卡尔的 128 单片机 相反,另外 128 单片有专门的数据方向寄存器 DDRA 或者 DDRB 等来管理各个端口的输入 输出选择,51 单片没有。如果我们想把端口 A 作为输入口使用,我们只需写 DDRA=0x00; 即所有位都置 0,如果我们想把端口 A 作为输出口使用,我们只需要写 DDRA=0xff; 即所有 位都置 1 ,而如 果我们想要 把端口 A 的高四 位做输入口 ,低 4 位做输 出口时我们 就 写 DDRA=0x0f; 当我们需要将该端口的某一位做输出或者输入口使用时只需要将该端口对应的 方向位置 1 或者置 0 即可。例如我们想把 A3 口作输入口, A4 口作输出口使用时我们只需 要写: DDRA_DDRA3=0; DDRA_DDRA4=1; 即可。 � � 对于数据方向寄存器的使用只要记住:置 1——输出 置 0——输入 PORTA 数据寄存器也是由 8 位组成,任何时候都可以对它进行读写操作。

#define uchar unsigned char //数据类型宏替换 #define uint unsigned int /*------------------------延时函数--------------------------------------*/ void delay(uint a) { uint i,j; for(i=0;i<a;i++) for(j=0;j<a;j++) ; } /*--------------------------指示灯闪烁函数-------------------------------*/ void light() { while(INPUT) { PORTB=0x3f; delay(500); PORTB=0x00; delay(500); } } //6 只灯全点亮 //延时一段时间 //6 只灯全熄灭 //延时一段时间 //判断输入电平的高低

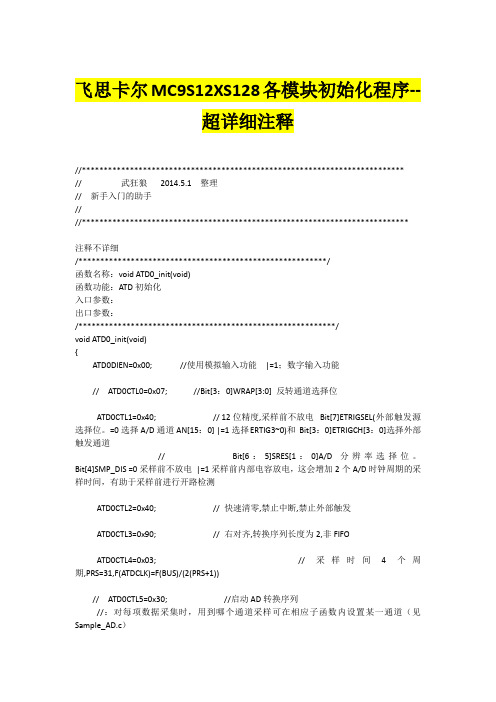

飞思卡尔MC9S12XS128各模块初始化程序--超详细注释

飞思卡尔MC9S12XS128各模块初始化程序--超详细注释//**************************************************************************// 武狂狼2014.5.1 整理// 新手入门的助手////***************************************************************************注释不详细/*********************************************************/函数名称:void ATD0_init(void)函数功能:ATD初始化入口参数:出口参数:/***********************************************************/void ATD0_init(void){ATD0DIEN=0x00; //使用模拟输入功能|=1;数字输入功能// ATD0CTL0=0x07; //Bit[3:0]WRAP[3:0] 反转通道选择位ATD0CTL1=0x40; // 12位精度,采样前不放电 Bit[7]ETRIGSEL(外部触发源选择位。

=0选择A/D通道AN[15:0] |=1选择 ERTIG3~0)和Bit[3:0]ETRIGCH[3:0]选择外部触发通道// Bit[6:5]SRES[1:0]A/D分辨率选择位。

Bit[4]SMP_DIS =0采样前不放电|=1采样前内部电容放电,这会增加2个A/D时钟周期的采样时间,有助于采样前进行开路检测ATD0CTL2=0x40; // 快速清零,禁止中断,禁止外部触发ATD0CTL3=0x90; // 右对齐,转换序列长度为2,非FIFOATD0CTL4=0x03; // 采样时间4个周期,PRS=31,F(ATDCLK)=F(BUS)/(2(PRS+1))// ATD0CTL5=0x30; //启动AD转换序列//:对每项数据采集时,用到哪个通道采样可在相应子函数内设置某一通道(见Sample_AD.c)while(!ATD0STAT2L_CCF0);/*********************************************************/函数名称:void PIT_init(void)函数功能:初始化PIT 设置精确定时时间(1s)入口参数:无出口参数:无说明:无/***********************************************************/void PIT_init(void){PITCFLMT=0x00; //禁止PIT模块Bit[7] PITE:PIT模块使能位,0禁用|1使能// Bit[6] PITSWAI:等待模式下PIT停止位,0等待模式下,PIT模块正常运行| 1等待模式下,PIT模块停止产生时钟信号,冻结PIT模块// Bit[5] PITFRZ: 冻结模式下PIT计数器冻结位。

飞思卡尔S12xs128单片机BDM调试器使用技巧

S12(X)单片机BDM调试器使用技巧第五届全国大学生“飞思卡尔”杯智能气车竞赛限制采用最新的MC9S12XS128(以下简称XS128)单片机作为主控芯片,替代MC9S12DG128。

XS128是Freescale公司推出的S12系列单片机中的一款增强型16位单片机。

片内资源丰富,接口模块有SPI、SCI、IIC、A/D、PWM等常见模块,在汽车电子应用领域具有广泛用途。

XS128和以往大赛使用的S12DG128系列单片机一样,调试接口都是使用Freescale公司传统的BD M(Background Debug Module)接口。

1 MC9S12XS128单片机介绍(1)CPU:增强型16位HCS12 CPU,片内总线时钟最高40 MHz;(2)片内资源:8 KB RAM、128 KB程序闪存、2 KB数据闪存;(3)串行接口模块:SCI、SPI;(4)脉宽调制模块(PWM)可设置成4路8位或者2路16位,逻辑时钟选择频率宽;(5)1个16路12位精度A/D转换器;(6)控制器局域网模块(CAN);(7)增强型捕捉定时器。

MC9S12XS128单片机有112、80和64引脚3种封装形式。

80-pin封装的单片机没有引出用于扩展方式的端口,仅引出了一个8路A/D接口。

竞赛可使用112或80引脚封装器件。

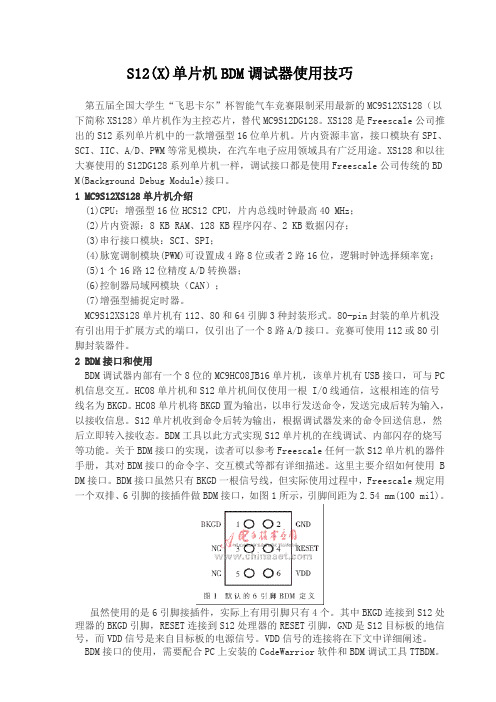

2 BDM接口和使用BDM调试器内部有一个8位的MC9HC08JB16单片机,该单片机有USB接口,可与PC 机信息交互。

HC08单片机和S12单片机间仅使用一根 I/O线通信,这根相连的信号线名为BKGD。

HC08单片机将BKGD置为输出,以串行发送命令,发送完成后转为输入,以接收信息。

S12单片机收到命令后转为输出,根据调试器发来的命令回送信息,然后立即转入接收态。

BDM工具以此方式实现S12单片机的在线调试、内部闪存的烧写等功能。

关于BDM接口的实现,读者可以参考Freescale任何一款S12单片机的器件手册,其对BDM接口的命令字、交互模式等都有详细描述。

飞思卡尔单片机 MC9S12 单片机应用系统开发平台下实时操作

计算机方向嵌入式计算机应用正在计算机领域迅速崛起,虽然该技术还不很成熟,但是它 的应用已经深入到社会各个领域,像办公自动化、民用消费品、计算机外设、机器人和武 器系统等等。

嵌入式系统,属于电子系统,包括微处理器或微控制器,嵌入式系统不是一般的计算 机,是隐藏或嵌入在各种系统中的计算机。主要用于控制领域,兼顾数据处理。而微控制 器即 MCU,MCU 的基本含义,在一片芯片上集成了中央处理单元(cpu)、存储器(RAM/ROM 等)、 定时器/计数器及多种输入\输出(I/O)接口的比较完整的数字处理系统。

单片机系统数码管显示驱动和键盘扫描

单片机系统的数码管显示驱动和键盘扫描以单片机为核心的很多仪器都需要数码管显示驱动和键盘扫描,三种具体方案如下供参考:一、经典方案:使用8279芯片8279是由Intel于80年代首先推出的,参考资料较多,应用比较成熟。

优点:最通用。

缺点:元器件多,面积大,电路复杂,综合成本高。

●8279的驱动电流较小,所以需要加上驱动电路ULN2003,或者使用8个三级管及相应的基极限流电阻。

一般情况下的8279外围电路中,需要16个电阻、一个74LS138芯片、一个ULN2003芯片、8个PNP三极管。

元器件较多,占用较大的PCB面积。

●8279需要外部为其提供上电复位信号和时钟信号,所以电路比较复杂。

●8279在显示驱动方面的功能较少。

二、自由方案:使用辅助单片机也就是在仪器的主控单片机之外,另外使用一个辅助的单片机专门做显示驱动和键盘扫描,最近市面上出现的一些产品就是以PIC系列等单片机实现的,查看其引脚定义尤其是CLK/RTCC/RST引脚都与PIC16C57或PIC16C54相似,另外,这些产品的说明书中都没有标明电流驱动能力。

优点:最灵活。

缺点:元器件多,速度慢,易受干扰,综合成本高。

●由于辅助单片机的驱动电流比较小,按单片机厂商的说明,通常每个引脚不大于20mA,如果长时间驱动大电流则容易损坏。

如果将辅助单片机的引脚直接用作字驱动,则20mA平均到数码管的8个段上,每个段的电流只能分配到3mA,所以只能驱动较小的数码管。

而如果外接驱动电路,例如595芯片或者8个三极管及相应的基级电阻,则电路面积增大,总体成本增加。

●为了节约辅助单片机的端口线,一般使用串行输入输出。

由于辅助单片机一条指令只能处理一位数据,并且在接收到数据后还需要将其移位转换为字节数据或者直接作为命令进行解释,所以速度非常低。

一般要求主控单片机的串行接口的位时钟不能高于200KHz(每个位数据要保持几微秒,才能被辅助单片机检测到并及时处理),所以单片机接口程序需要不断地延时等待。

飞思卡尔学习板简介

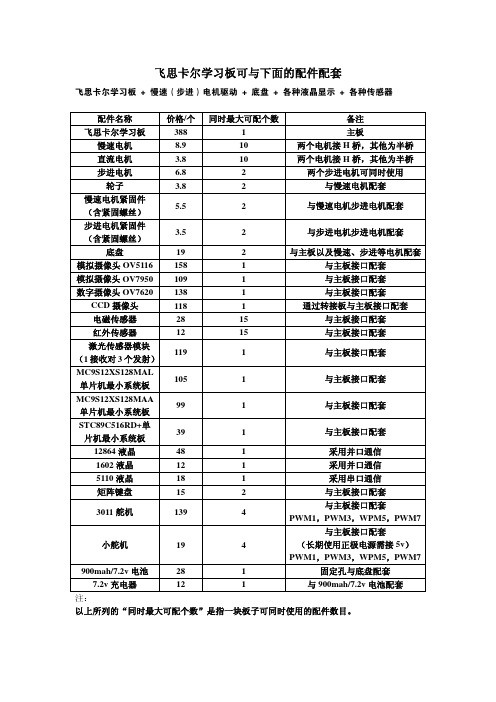

飞思卡尔学习板可与下面的配件配套飞思卡尔学习板 + 慢速(步进)电机驱动 + 底盘 + 各种液晶显示 + 各种传感器配件名称价格/个同时最大可配个数备注飞思卡尔学习板388 1 主板慢速电机8.9 10 两个电机接H桥,其他为半桥直流电机 3.8 10 两个电机接H桥,其他为半桥步进电机 6.8 2 两个步进电机可同时使用轮子 3.8 2 与慢速电机配套慢速电机紧固件(含紧固螺丝)5.5 2 与慢速电机步进电机配套步进电机紧固件(含紧固螺丝)3.5 2 与步进电机步进电机配套底盘19 2与主板以及慢速、步进等电机配套模拟摄像头OV5116158 1 与主板接口配套模拟摄像头OV7950109 1 与主板接口配套数字摄像头OV7620138 1 与主板接口配套CCD摄像头118 1 通过转接板与主板接口配套电磁传感器28 15 与主板接口配套红外传感器12 15 与主板接口配套激光传感器模块(1接收对3个发射)119 1 与主板接口配套MC9S12XS128MAL单片机最小系统板105 1 与主板接口配套MC9S12XS128MAA单片机最小系统板99 1 与主板接口配套STC89C516RD+单片机最小系统板39 1 与主板接口配套12864液晶48 1 采用并口通信1602液晶12 1 采用并口通信5110液晶18 1 采用串口通信矩阵键盘15 2 与主板接口配套3011舵机139 4 与主板接口配套PWM1,PWM3,WPM5,PWM7小舵机19 4 与主板接口配套(长期使用正极电源需接5v)PWM1,PWM3,WPM5,PWM7 900mah/7.2v电池28 1 固定孔与底盘配套7.2v充电器12 1 与900mah/7.2v电池配套注:以上所列的“同时最大可配个数”是指一块板子可同时使用的配件数目。

手创科技研发团队:十月磨一剑,飞思卡尔综合学习板。

飞思卡尔学习板是广州手之创电子科技结合现有产品以及根据客户的反馈建议所设计的,本版适合中高职,本科及研究等学生使用,本版更适合有志于参加智能车比赛的选手。

s12单片机功能模块

---------------------------------------------------------------最新资料推荐------------------------------------------------------1 / 32s12单片机功能模块六 单 接口和功 块 内容 介、 I/O 接口 块 、 数 换 A/D 块 、 冲宽度制 PWM 4、增强型定时器 ECT 5、同 外设接口 SPI 6、串行信接口 SCI 块 块 块 块 、接口MC9S12DG128B 单 I/O 口 接按接发光二 功 中断 入, 有PJ0-PJ5 中断 入, 有 PP6 有 PM6-PM7 有 PS4-PS7 只 入 、 接口口作为 入使 设 方向寄存器(DDRx )为 入(0X00) 时取 I/O 口 数据寄存器(PORTx ) 口作为 出使设 方向寄存器(DDRx )为 出(0XFF ) 设 动 力寄存器( 必页) 拉 逩择( 必页) 时写入 I/O 口数据寄存器(PORTx ) 、 接口 口作为外 中断接收使 开 中断(CLI ) 设 方向寄存器为 入 设 中断有效 (上升 、下 )使 中断 写 关 中断服务 序有效 到杯时,会臧动 入中断服务 序 、 接口 例一 设 一个C 语 序,使教学 上发光二显效显循环效、接口例二使 PORTJ 中断口功例子,例原是:设 A 口为出口,PTA 6 PTJ 6 件,PTB 出,杯控制 8 个 LED , PTJ 开中断,并且设为上升觲发。

馒先 PTA 初始化为 0,PTB 为 0xFF,时。

在大循环冲设PTA 6 位为平,产中断,低 4 个亮, 4 个不亮。

使单行柧效。

、数换块换基念数换定义:将时縣、幅值也縣拟信号换为散、幅值也散数字信号数换精度数换精度是指二制位数。

9S12 AD 块有两精度可逩,分别为 8 位精度(0255)和10 位精度(01023)。

飞思卡尔单片机 S12SPIV2

DOCUMENT NUMBERS12SPIV2/DSPIBlock User GuideV02.07Original Release Date: 21 JAN 2000Revised: 11 Dec 2002Motorola, Inc.Motorola reserves the right to make changes without further notice to any products herein to improve reliability,function or design.Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.Motorola products are not designed,intended, or authorized for use as components in systems intended for surgical implant into the body,or other applications intended to support or sustain life,or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur.Should Buyer purchase or use Motorola products for any such unintended or unauthorized application,Buyer shall indemnify and hold Motorola and its officers,employees,subsidiaries,affiliates,and distributors harmless against all claims,costs,damages,and expenses,and reasonable attorney fees arising out of,directly or indirectly,any claim of personal injury or death associated with such unintended or unauthorized use,even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.SPI Block User Guide — S12SPIV2/D V02.07 Revision HistoryVersion Number RevisionDateEffectiveDate Author Description of Changes0.121 Jan2000This spec is based on the Barracuda, with modifications to changethe module from 16 bit to 8 bit.0.21 Mar2000Template of this document changed as per Version 2.0 SRS.0.314 Jun2000- Signal names are changed as per the SRS2.0- SPE bit remains set in the Mode Fault error case- Slave SPI does not support div2 and div4 cases0.431 Aug2000- Electrical spec added- SPIF flag is cleared by a read access to the status registerfollowed by read access to the data register.0.513 Mar200113 Mar2001- Incorporated feedback regarding format of the document.0.613 Mar200119 Mar2001- Incorporated changes as a result of internal discussions andclarification of SRS20.76 July20016 July2001- Line is added with respect to SPTEF bit to make spec more clear.- Landscape pages have been removed from pdf.- Extra blank pages have been removed.0.819 July200119 July2001- Line is added with respect to SPE bit to make spec more clear.V02.0226 July2001-Added Document Names-variable definitions and Names have been hidden-Changed chapter 3.9 Errata to NoteV02.0328 Sept2001- Corrected the status of SPE when MODF is setV02.0411 Dec2001- Added a note for slave operation for MUCts00531- Updated Block DiagramV02.0513 Feb200213 Feb2002- Cleaned up revision history, summarized three entries withVersion Number V2.04 into one- Section 4.6.2 Cleaned up Figures in Table 4-1- Removed note 4.9, because in slave mode baud rates DIV2 andDIV4 are not supportedV02.0606 Mar200206 Mar2002- Document format updateV02.0711 Dec200211 Dec2002Section 3.3.5 - Added NoteSPI Block User Guide — V02.07 Table of ContentsSection 1 Introduction1.1Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 1.2Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 1.3Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 1.4Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10Section 2 Signal Description2.1Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 2.2Detailed Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 2.2.1MOSI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 2.2.2MISO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 2.2.3SS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 2.2.4SCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11Section 3 Memory Map and Registers3.1Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 3.2Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 3.3Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 3.3.1SPI Control Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 3.3.2SPI Control Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 3.3.3SPI Baud Rate Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 3.3.4SPI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19 3.3.5SPI Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20Section 4 Functional Description4.1General. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 4.2Master Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 4.3Slave Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 4.4Transmission Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 4.4.1Clock Phase and Polarity Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 4.4.2CPHA = 0 Transfer Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 4.4.3CPHA = 1 Transfer Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 4.5SPI Baud Rate Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27SPI Block User Guide — V02.074.6Special Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 4.6.1SS Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 4.6.2Bidirectional Mode (MOMI or SISO). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 4.7Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 4.7.1Mode Fault Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 4.8Low Power Mode Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 4.8.1SPI in Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 4.8.2SPI in Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 4.8.3SPI in Stop Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30Section 5 Reset5.1General. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31Section 6 Interrupts6.1Interrupt Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33 6.1.1MODF. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33 6.1.2SPIF. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33 6.1.3SPTEF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33SPI Block User Guide — V02.07 List of FiguresFigure 1-1SPI Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Figure 3-2SPI Control Register 1 (SPICR1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Figure 3-3SPI Control Register 2 (SPICR2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Figure 3-4SPI Baud Rate Register (SPIBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 Figure 3-5SPI Status Register (SPISR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19 Figure 3-6SPI Data Register (SPIDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20 Figure 4-1Master/Slave Transfer Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Figure 4-2SPI Clock Format 0 (CPHA = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 Figure 4-3SPI Clock Format 1 (CPHA = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 Figure 4-4Baud Rate Divisor Equation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27SPI Block User Guide — V02.07SPI Block User Guide — V02.07 List of TablesTable 3-1Module Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Table 3-2SS Input / Output Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 3-3Bidirectional Pin Configurations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 Table 3-4SPI Baud Rate Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 Table 4-1Normal Mode and Bidirectional Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28SPI Block User Guide — V02.07SPI Block User Guide — V02.07 Section 1 Introduction1.1 OverviewThe SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or the SPI operation can be interrupt driven.1.2 FeaturesThe SPI includes these distinctive features:•Master mode and slave mode•Bi-directional mode•Slave select output•Mode fault error flag with CPU interrupt capability•Double-buffered operation•Serial clock with programmable polarity and phase•Control of SPI operation during wait mode1.3 Modes of OperationThe SPI functions in three modes, run, wait, and stop.•Run ModeThis is the basic mode of operation.•Wait ModeSPI operation in wait mode is a configurable low power mode. Depending on the state of internal bits, the SPI can operate normally when the CPU is in wait mode or the SPI clock generation can be turned off and the SPI module enters a power conservation state during wait mode.During wait mode, any master transmission in progress stops if the SPISWAI bit is set in the SPI controlregister2.Reception and transmission of a byte as slave continues so that the slave is synchronized to the master.•Stop ModeThe SPI is inactive in stop mode for reduced power consumption. The STOP instruction does not affect or depend on SPI register states. Again, reception and transmission of a byte as slavecontinues to stay synchronized with the master.This is a high level description only,detailed descriptions of operating modes are contained in section4.8 Low Power Mode Options.SPI Block User Guide — V02.071.4 Block DiagramFigure 1-1 is a general block diagram of the SPI.Figure 1-1 SPI Block DiagramPIN CONTROL LOGIC8-BIT SHIFT REGISTERCLOCK LOGICSPI CONTROLSPI STATUS REGISTERSPI DATA REGISTERDIVIDERSELECTSPI BAUD RATE REGISTER248163264128256S P I I N T E R R U P T S M M S MSR E Q U E S TSPI CONTROL REGISTER 1BAUD RATE GENERATORMISOMOSISPI CONTROL REGISTER 2SSSCKBUS CLOCKM O D FS P I FS P T E FS P P R 2S P P R 1S P R 1S P R 0S P P R 0S P R 2M S T RC P H AC P O LL S B F EBIDIROESPC0BAUD CLOCK IPBUSMUXED CLOCKSection 2 Signal Description2.1 OverviewThis section lists the name and description of all ports including inputs and outputs that do,or may,connect off chip.The SPI module has a total of 4 external pins.2.2Detailed Signal Descriptions2.2.1MOSIThis pin is used to transmit data out of the SPI module when it is configured as a Master and receive data when it is configured as slave.2.2.2 MISOThis pin is used to transmit data out of the SPI module when it is configured as a Slave and receive data when it is configured as Master.2.2.3SSThis pin is used to output the select signal from the SPI module to another peripheral with which a data transfer is to take place.2.2.4 SCKThis pin is used to output the clock with respect to which the SPI transfers data or receive clock in case of Slave.Section 3 Memory Map and Registers3.1 OverviewThis section provides a detailed description of all memory and registers accessible to the end user.3.2 Module Memory MapThe memory map for the SPI is given below in Table3-1.The address listed for each register is the sum of a base address and an address offset.The base address is defined at the SoC level and the address offset is defined at the module level. Reads from the reserved bits return zeros and writes to the reserved bits have no effect.Table 3-1 Module Memory MapAddress Use Access$___0SPI Control Register 1 (SPICR1)Read / Write$___1SPI Control Register 2 (SPICR2)Read / Write1$___2SPI Baud Rate Register (SPIBR)Read / Write1$___3SPI Status Register (SPISR)Read2$___4Reserved—23$___5SPI Data Register (SPIDR)Read / Write$___6Reserved—23$___7Reserved—23NOTES:1. Certain bits are non-writable.2. Writes to this register are ignored.3. Reading from this register returns all zeros.3.3 Register DescriptionsThis section consists of register descriptions in address order.Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.3.3.1 SPI Control Register 1Figure 3-2 SPI Control Register 1 (SPICR1)Read:anytime Write:anytimeSPIE — SPI Interrupt Enable BitThis bit enables SPI interrupts each time the SPIF or MODF status flag is set.1 = SPI interrupts enabled.0 = SPI interrupts disabled.SPE — SPI System Enable BitThis bit enables the SPI system and dedicates the SPI port pins to SPI system functions.1 = SPI port pins are dedicated to SPI functions.0 = SPI disabled (lower power consumption).SPTIE — SPI Transmit Interrupt EnableThis bit enables SPI interrupt generated each time the SPTEF flag is set.1 = SPTEF interrupt enabled.0 = SPTEF interrupt disabled.MSTR — SPI Master/Slave Mode Select Bit1 = Master mode 0 = Slave modeCPOL — SPI Clock Polarity BitThis bit selects an inverted or non-inverted SPI clock.To transmit data between SPI modules,the SPI modules must have identical CPOL values.1 = Active-low clocks selected; SCK idles high 0 = Active-high clocks selected; SCK idles low CPHA — SPI Clock Phase BitThis bit is used to shift the SCK serial clock.1 = The first SCK edge is issued at the beginning of the 8-cycle transfer operation 0 = The first SCK edge is issued one-half cycle into the 8-cycle transfer operationRegister Address: $___0Bit 7654321Bit 0R SPIE SPE SPTIE MSTR CPOL CPHA SSOE LSBFE W Reset:1SSOE — Slave Select Output EnableThe SS output feature is enabled only in the master mode by asserting the SSOE as shown in Table 3-2.LSBFE — SPI LSB-First EnableThis bit does not affect the position of the msb and lsb in the data register.Reads and writes of the data register always have the msb in bit 7.1 = Data is transferred least significant bit first.0 = Data is transferred most significant bit first.3.3.2 SPI Control Register 2Figure 3-3 SPI Control Register 2 (SPICR2)Read:anytimeWrite:anytime; writes to the reserved bits have no effectMODFEN — Mode Fault Enable BitThis bit when set allows the MODF flag to be set.If the MODF flag is set,clearing the MODFEN does not clear the MODF flag.If the SPI is enabled as master and the MODFEN bit is low,then the SS pin is not used by the SPI.When the SPI is enabled as a slave, the SS is available only as an input regardless of the value of MODFEN.1 = Enable setting the MODF error 0 = Disable the MODF errorTable 3-2SS Input / Output SelectionMOD FENSSOE Master ModeSlave Mode00SS not used by SPI SS input 01SS not used by SPI SS input 10SS input with MODF featureSS input 11SS outputSS inputRegister Address: $___1Bit 7654321Bit 0R 000MODFENBIDIROE0SPISWAISPC0W Reset:00= ReservedBIDIROE — Output enable in the Bidirectional mode of operationThis bit along with the MSTR bit of SPCR1 is used to enable the output buffer when the SPI is configured in bidirectional mode.1 = Output buffer enabled 0 = Output buffer disabled SPISWAI — SPI Stop in Wait Mode BitThis bit is used for power conservation while in wait mode.1 = Stop SPI clock generation when in wait mode 0 = SPI clock operates normally in wait modeSPC0 — Serial Pin Control Bit 0With the MSTR control bit, this bit enables bidirectional pin configurations as shown in Table 3-3.3.3.3 SPI Baud Rate RegisterFigure 3-4 SPI Baud Rate Register (SPIBR)Read:anytimeWrite:anytime; writes to the reserved bits have no effectNOTE:Writing to this register during data transfers may cause spurious results.Table 3-3 Bidirectional Pin ConfigurationsPin ModeSPC0MSTRMISO 1NOTES :1. Slave output is enabled if BIDIROE bit = 1,SS = 0, and MSTR = 0 (C)MOSI 22. Master output is enabled if BIDIROE bit = 1 and MSTR = 1 (D)SCK 33. SCK output is enabled if MSTR = 1 (B, D)SS 44.SS output is enabled if MODFEN bit = 1, SSOE = 1, and MSTR = 1 (B, D).A Normal 00Slave Out Slave In SCK in SS inB 1Master InMaster OutSCK out SS I/O C Bidirectional10Slave I/O—SCK in SS In D1—Master I/OSCK outSS I/ORegister Address: $___2Bit 7654321Bit 0R 0SPPR2SPPR1SPPR00SPR2SPR1SPR0W Reset:00= ReservedSPPR2–SPPR0 — SPI Baud Rate Preselection Bits SPR2–SPR0 — SPI Baud Rate Selection BitsThese bits specify the SPI baud rates as shown in the table below The baud rate divisor equation is as followsBaud Rate = Bus clock / BaudRateDivisorTable 3-4 SPI Baud Rate SelectionSPPR2SPPR1SPPR0SPR2SPR1SPR0SPI Module Clock Divisor00000020000014000010800001116000100320001016400011012800011125600100040010018001010160010113200110064001101128001110256001111512010000601000112010010240100114801010096010101192010110384010111768011000801100116011010320110116401110012801111256BaudRateDivisor SPPR 1+()2•SPR 1+()=NOTE:DIV2 and DIV4 are not supported in slave mode of SPI.0111105120111111024100000101000012010001040100011801001001601001013201001106401001111280101000121010012410101048101011961011001921011013841011107681011111536110000141100012811001056110011112110100224110101448110110896110111179211100016111001321110106411101112811110025611110151211111010241111112048Table 3-4 SPI Baud Rate SelectionSPPR2SPPR1SPPR0SPR2SPR1SPR0SPI Module Clock DivisorFigure 3-5 SPI Status Register (SPISR)Read:anytimeWrite:has no effectSPIF — SPIF Interrupt FlagThis bit is set after the eighth SCK cycle in a data transfer and is cleared by reading the SPISR register (with SPIF set) followed by a read access to the SPI data register.1 = New data Copied to SPIDR 0 = Transfer not yet complete SPTEF — SPI Transmit Empty Interrupt FlagThis bit is set when there is room in the transmit data buffer.It is cleared by reading SPISR with SPTEF set, followed by writing a data value to the transmit buffer at SPIDR.SPISR must be read with SPTEF=1 before writing data to SPIDR or the SPIDR write will be ignored. SPTEF generates an SPTEF CPU interrupt request if the SPTIE bit in the SPICR1 is also set.SPTEF is automatically set when a data byte transfers from the transmit buffer into the transmit shift register.For an idle SPI (no data in the transmit buffer or the shift register and no transfer in progress), data written to SPIDR is transferred to the shifter almost immediately so SPTEF is set within two bus cycles allowing a second 8-bit data value to be queued into the transmit buffer.After completion of the transfer of the value in the shift register,the queued value from the transmit buffer will automatically move to the shifter and SPTEF will be set to indicate there is room for new data in the transmit buffer.If no new data is waiting in the transmit buffer, SPTEF simply remains set and no data moves from the buffer to the shifter.1 = SPI Data register empty 0 = SPI Data register not emptyNOTE:Do not write to the SPI data register unless the SPTEF bit is high. Any such write to the SPI Data Register before reading SPTEF=1 is effectively ignoredMODF — Mode Fault FlagThis bit is set if the SS input becomes low while the SPI is configured as a master.The flag is cleared automatically by a read of the SPI status register (with MODF set) followed by a write to the SPI control register 1. The MODF flag is set only if the MODFEN bit of SPICR2 register is set. Refer to MODFEN bit description in 3.3.2 SPI Control Register 2.1 = Mode fault has occurred.0 = Mode fault has not occurred.Register Address: $___3Bit 7654321Bit 0R SPIF 0SPTEF MODF 0000W Reset:10= ReservedFigure 3-6 SPI Data Register (SPIDR)Read:anytime; normally read only after SPIF is set Write:anytime; see SPTEFThe SPI Data register is both the input and output register for SPI data.A write to this register allows a data byte to be queued and transmitted. For a SPI configured as a master, a queued data byte is transmitted immediately after the previous transmission has completed. The SPI Transmitter empty flag in SPISR indicates when the SPI data register is ready to accept new data.NOTE:Do not write to the SPI data register unless the SPTEF bit is high.Reading the data can occur anytime from after the SPIF is set to before the end of the next transfer.If the SPIF is not serviced by the end of the successive transfers, those data bytes are lost and the data within the SPIDR retains the first byte until SPIF is serviced.NOTE:After reset the content of the SPI Shift Register is undefined until a data byte is stored into SPIDR.Register Address: $___5Bit 7654321Bit 0R Bit 7654322Bit 0W Reset:Section 4 Functional Description4.1 GeneralThe SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or SPI operation can be interrupt driven.The SPI system is enabled by setting the SPI enable(SPE)bit in SPI control register1.While SPE is set, the four associated SPI port pins are dedicated to the SPI function as:•Slave select (SS)•Serial clock (SCK)•Master out/slave in (MOSI)•Master in/slave out (MISO)The main element of the SPI system is the SPI data register. The 8-bit data register in the master and the 8-bit data register in the slave are linked by the MOSI and MISO pins to form a distributed16-bit register. When a data transfer operation is performed,this16-bit register is serially shifted eight bit positions by the SCK clock from the master;data is exchanged between the master and the slave.Data written to the master SPI data register becomes the output data for the slave, and data read from the master SPI data register after a transfer operation is the input data from the slave.A write to the SPI data register puts data into the transmit buffer if the previous transmission was complete. When a transfer is complete, received data is moved into a receive data register. Data may be read from this double-buffered system any time before the next transfer is complete. This 8-bit data register acts as the SPI receive data register for reads and as the SPI transmit data register for writes.A single SPI register address is used for reading data from the read data buffer and for writing data to the shifter.The clock phase control bit(CPHA)and a clock polarity control bit(CPOL)in the SPI control register1 select one of four possible clock formats to be used by the SPI system. The CPOL bit simply selects a non-inverted or inverted clock. The CPHA bit is used to accommodate two fundamentally different protocols by shifting the clock by a half cycle or by not shifting the clock (see4.4 Transmission Formats).The SPI can be configured to operate as a master or as a slave.When MSTR in SPI control register1is set, the master mode is selected; when the MSTR bit is clear, the slave mode is selected.4.2 Master ModeThe SPI operates in master mode when the MSTR bit is set. Only a master SPI module can initiate transmissions. A transmission begins by writing to the master SPI data register. If the shift register is empty, the byte immediately transfers to the shift register. The byte begins shifting out on the MOSI pin under the control of the serial clock.The SPR2, SPR1, and SPR0 baud rate selection bits in conjunction with the SPPR2, SPPR1, and SPPR0 baud rate preselection bits in the SPI baud rate register control the baud rate generator and determine thespeed of the shift register. The SCK pin is the SPI clock output. Through the SCK pin, the baud rate generator of the master controls the shift register of the slave peripheral.In master mode,the function of the serial data output pin(MOSI)and the serial data input pin(MISO)is determined by the SPC0 and MSTR control bits.The SS pin is normally an input which should remain in the inactive high state. However, in the master mode, if both MODFEN bit and SSOE bit are set, then the SS pin is the slave select output.The SS output becomes low during each transmission and is high when the SPI is in the idling state.If the SS input becomes low while the SPI is configured as a master,it indicates a mode fault error where more than one master may be trying to drive the MOSI and SCK lines simultaneously. In this case, the SPI immediately clears the output buffer enables associated with the MISO,MOSI(or MOMI),and SCK pins so that these pins become inputs.This mode fault error also clears the MSTR control bit and sets the mode fault(MODF)flag in the SPI status register.If the SPI interrupt enable bit(SPIE)is set when the MODF bit gets set, then an SPI interrupt sequence is also requestedWhen a write to the SPI data register in the master occurs,there is a half SCK-cycle delay.After the delay, SCK is started within the master.The rest of the transfer operation differs slightly,depending on the clock format specified by the SPI clock phase bit, CPHA, in SPI control register 1 (see4.4 Transmission Formats).4.3 Slave ModeThe SPI operates in slave mode when the MSTR bit in SPI control register1is clear.In slave mode,SCK is the SPI clock input from the master,and SS is the slave select input.Before a data transmission occurs, the SS pin of the slave SPI must be at logic 0.SS must remain low until the transmission is complete.In slave mode, the function of the serial data output pin (MISO) and serial data input pin (MOSI) is determined by the SPC0bit in SPI control register2and the MSTR control bit.While in slave mode,the SS input controls the serial data output pin; if SS is high (not selected), the serial data output pin is high impedance,and,if SS is low the first bit in the SPI data register is driven out of the serial data output pin. Also,if the slave is not selected(SS is high),then the SCK input is ignored and no internal shifting of the SPI shift register takes place.Although the SPI is capable of duplex operation,some SPI peripherals are capable of only receiving SPI data in a slave mode. For these simpler devices, there is no serial data out pin.NOTE:When peripherals with duplex capability are used,take care not to simultaneously enable two receivers whose serial outputs drive the same system slave’s serial dataoutput line.As long as no more than one slave device drives the system slave’s serial data output line,it is possible for several slaves to receive the same transmission from a master, although the master would not receive return information from all of the receiving slaves.If the CPHA bit in SPI control register1is clear,odd numbered edges on the SCK input cause the data at the serial data input pin to be latched. Even numbered edges cause the value previously latched from the serial data input pin to shift into the LSB of the SPI shifter.。