并行IO口的简单扩展

80C51单片机并行IO口的扩展毕业设计资料

摘要近年来随着计算机在社会领域的渗透和大规模集成电路的发展,单片机的应用正在不断的走向深入。

但是在由单片机构成的实际测控系统中,最小应用系统往往不能满足要求,因此在系统设计时首先要解决系统扩展问题。

单片机扩展通常是借助外部器件对系统进行扩展。

本文主要研究了采用可编程多功能扩展芯片intel 8155扩展单片机I/O 口。

把单片机作为一个核心部件,设计单片机与8155的接口,并实现数码管三位数字的显示。

本文的主要内容有:单片机的概述,设计的意义,核心器件intel 8155芯片、80C51单片机、数码管的介绍,单元电路模块,设计原理图及流程图,软件编程设计以及最后的结果和个人在整个设计前后的心得体会。

关键词:单片机,8155,数码管,动态显示。

- I -AbstractWith the development of computer penetration in the social field and LSI in recent years, the application of MCU is constantly deepening. but in the actual measurement and control system constituted by the microcontroller, the smallest applications system often can not meet the requirements, so we have to solve the system expansion. The Microprocessor usually use an external device to relize the expansion of the system.Adopting Intel 8155 which is a kind of programmable multi-function expansion chip,this paper studies the expansion of MCU parallel I/O port. MCU act as a core component,.we have designed the 8155 chip interface to relize three digital display on LED numerical code tube.The main content of this paper are microcontroller overview of the significance of the design, the core of the device intel 8155 ;80C51 microcontroller, the introduction of LED numerical code tube, the unit circuit module,design schematics and flowcharts, software programming design, the final results and individual feelings and experiences throughout the design.Key words:MCU, 8155, LED numerical code tube, dynamic display.目录1.绪论 (1)1.1单片机概述 (1)1.2课题研究背景及意义 (2)1.3设计任务 (3)2.核心器件基本结构与工作原理 (4)2.180C51单片机 (4)2.2带RAM和计数器的可编程并行I/O扩展接口8155 (6)2.2.1 结构和引脚 (6)2.2.2 8155命令和状态字 (8)2.2.3 8155定时器/计数器 (12)2.2.4 MCS-51和8155的接口方法 (13)2.3LED显示器接口 (14)2.3.1 LED显示器的工作原理 (15)2.3.2 LED显示器的显示方式 (16)3.硬件设计 (19)3.1元器件列表 (19)3.2单元电路模块设计 (21)3.2.1 单片机 (21)3.2.2 晶振电路 (22)- 1 -3.2.3 复位电路 (22)3.2.4 Intel 8155与AT89S51接口电路 (23)3.2.5 LED数码管显示电路 (23)3.3总设计原理图 (24)4.软件设计 (25)5.成果展示 (26)总结 (27)致谢 (28)参考文献 (1)附录 (2)80C51单片机并行I/O口的扩展1.绪论1.1 单片机概述单片机是在一片芯片上集成了中央处理器CPU、随机储存器RAM、程序储存器ROM或EPROM、定时器/计数器、中断控制器以及串行和并行I/O口等功能器件的微型计算机。

74.56MCS51并行IO端口的扩展PPT课件

(1) 监视键盘的方法 3) 根据键盘布局构建键值表

1FH 1EH 1DH 1CH 1BH 1AH 19H 18H

L3

17H 16H 15H 14H 13H 12H 11H 10H

L2

0FH 0EH 0DH 0CH 0BH 0AH 09H 08H

L1

07H 06H 05H 04H 03H 02H 01H 00H

ORG 0100H

READKEY: MOV A , #0FFH ; 准备读P1口

MOV P1, A

JNB ACC.0 , RP10 ; 若0#键按下,则转RP10

JNB ACC.1 , RP11 ; 若1#键按下,则转RP11

…

JNB ACC.7 , RP17 ; 若7#键按下,则转RP17

DONE : RET

7.4 MCS-51并行I/O端口的扩展

MCS-51单片机虽然有四个并行端口(P0~P3),但是真正留给 用户使用的只有P1,其它的3个并口都有其它的工作:P0和P2常 用作扩展外存储器,P3经常用到它的各引脚的第二功能。因此, 需要扩展I/O

两种方法: 1) 借用外部RAM的地址来扩展I/O端口(统一编址); 方法简单,但使用受限,尤其在使用无接口能力的外设

设计者按照需要固定好各个按键的位置后,即可以根据 当前的键盘布局,确定某键盘所在的行值和列值。例如按键 “7”的行值为0(L0),列值为0(R0)。

为方便编程,需要将所有按键的键值按照固定的顺序保 存在表格中。因为键值和按键是一一对应的,只要通过查表 查到键值,也就知道用户按下了哪个键。其中各个键值对应 的偏移量是由按键的行值和列值确定的。确切的说,是由列 值和所在行的行首键号(顺序号)确定的。如下图所示:

并行IO口扩展

PA0-PA7 PB0-PB7 PC0-PC5 AD0-AD7 IO/ M TIMER IN TIMER OUT RD、WR ALE CE RESET

端口A的I/O线(8位,接外设) 端口B的I/O线(8位,接外设) 端口C的I/O线(6位,接外设) 三态地址/数据复用线(8位,一般接单片机P0 口,CPU与8155之间的地址、数据、命令、状 态等信号都通过它来传送) 端口/存储器 选择控制 “0”选择片内RAM “1”选择片内I/O口 8155片内定时器/计数器的计数脉冲输入引脚 8155片内定时器/计数器的计满回零输出引脚 分别是对8155片内的RAM或I/O口的的读、写控 制信号 地址锁存引脚 选片 复位引脚

2、8255A内部结构 8255A内部结构由以下四部分组成: 数据端口A、B、C;A组控制和B组控制;读/写控制逻 辑电路;数据总线缓冲器。结构如图所示

端口A:包括一个 8 位的数据输出锁存/缓冲器和一个 8位的数 据输入锁存器,可作为数据输入或输出端口, 并工作于三种 方式中的任何一种。 端口B: 包括一个 8 位的数据输出锁存/缓冲器和一个 8位的 数据输入缓冲器,可作为数据输入或输出端口, 但不能工作 于方式2。 端口C: 包括一个 8 位的数据输出锁存/缓冲器和一个 8位的 数据输入缓冲器, 可在方式字控制下分为两个4位的端口(C 端口上和下),每个4位端口都有4位的锁存器, 用来配合端 口A与端口B锁存输出控制信号和输入状态信号,不能工作于 方式1或2。 A组和B组控制的作用如下: A组控制逻辑控制端口A及端口C的上半部; B组控制逻辑控制端口B及端口C的下半部。

Y2 Y1 Y0

ALE AD0~AD7 RD WE CE PA PB

8155 PC

+5V

并行IO扩展27页PPT文档

• 8255与单片机的接口电路与接口 ① 8255与单片机的接口电路。 在单片机中,外设接口与片外数据存储器RAM统一编 址。所以单片机与8255的连接同片外RAM芯片一样。

由图得到8255各口地址:

P2.7 P2.6 ···P2.0 P0.7···P0.2 P0.1P0.0 选中口

0 × ··· ×

• 方式2—双向输入/输出方式

• 只有A组能工作在方式2。此时,B组可工作于方式0或 方式1。

• 8255的控制字

• 8255的控制字有2种:工作方式控制字和C口置位/复位 控制字。

①工作方式控制字

用于确定8255工作于何种工作方式,以及A口、B口是 输入还是输出等。

• 例1 使8255的A组工作在方式2,B组工作在方式1。 PA=输入,PB=输出,PCL=输出,PCU=输出

(b)控制字为10010000

(c)程序如下:

MOV

A,

MOV

DPTR,

MOVX DPTR,

MOV

DPTR,

MOVX A,

INC

DPTR

MOVX DPTR,

INC

DPTR

MOVX DPTR,

#90H #1003H A #1000H DPTR

A

A

谢谢!

• (b) 控制字节:80H

• (c)

BACK: AGAIN:

MOV MOV MOVX MOV MOV MOV MOV INC DJNZ CPL SJMP

A, DPTR, DPTR, A R4, DPTR, DPTR, DPTR R4, A BACK

#80H #8003H A #55H #3 #8000H A

× ···× 0 0

单片机并行I-O口的扩展方法

单片机并行I/O口的扩展方法摘要:由于在MCS-51单片机开发中P0口经常作为地址/数据复用总线使用,P2口作为高8位地址线使用,P3口用作第二功能(定时计数器、中断等)使用,所以对于51单片机的4个I/O口,其可以作为基本并行输入/输出口使用的只有P1口。

因此在单片机的开发中,对于并行I/O口的扩展十分重要,主要分析3种扩展并行I/O口的方法。

关键词: MCS-51单片机; 并行I/O口; 扩展MCS-51单片机有4个并行的I/O口,分别为P0口、P1口、P2口和P3口,4个并行I/O 口在单片机的使用中非常重要,可以说对单片机的使用就是对这4个口的使用。

这4个并行I/O口除了作为基本的并行I/O口使用,还常作为其他功能使用,如P0口经常作为地址/数据复用总线使用[1], P2口作为高8位地址线使用,P3口用作第二功能(定时计数器、中断等等)使用。

这样,单片机只有P1口作为基本的并行I/O口使用,如果在单片机的使用中对并行I/O口需求较多,对于并行I/O口的扩展就非常重要了。

下面通过具体的实例(8位流水灯设计)来给出几种不同的并行I/O口扩展方法。

为了更好地说明以下几种不同的并行I/O口扩展方法,假设利用单片机实现流水灯的设计。

采用单片机的P1口设计流水灯,电路。

由图1可知,8只LED直接连接在单片机的P1口上,通过对单片机进行编程即可以实现8只发光二极管产生流水灯。

1 使用单片机的串行口扩展并行I/O口单片机有一个全双工的串行口[2],这个口既可以用于网络通信,也可以实现串行异步通信,还可以作为移位寄存器使用。

当单片机的串行口工作在模式0时,若外接一个串入/并出的移位寄存器(74LS164),就可以扩展一个8 bit并行输出口;若外接一个并入/串出的移位寄存器(74LS165),就可以扩展一个8 bit并行输入口。

,单片机外接一个串入/并出的移位寄存器(74LS164),这样就可以扩展8 bit并行输出口。

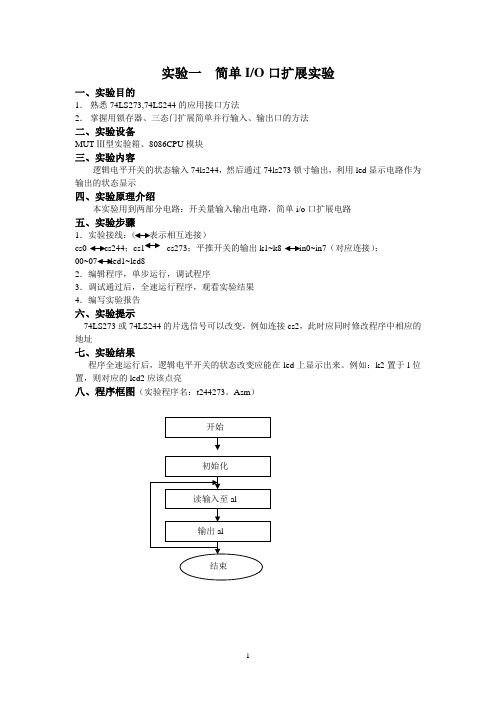

实验一简单IO口扩展实验

8255a是比较常用的一种并行接口芯片,其特点在许多教科书中均有介绍。8255a有三个8位的输入输出端口,通常将a端口作为输入用,b端口作为输出用,c端口作为辅助控制用,本实验也是如此。实验中,8255a工作于基本输入输出方式(方式0)

七、实验结果

程序全速运行后,逻辑电平开关的状态改变应能在led上显示出来。例如:

四、实验原理介绍

本实验用到两部分电路:开关量输入输出电路和8255可编程并口电路

五、实验步骤

1.实验接线

cs0 cs8255;pa0~pa7平推开关的输出k1~k8;pb0~pb7发光二极管的输入led1~led8

2.编程并全速或单步运行

3.全速运行时拨动开关,观察发光二极管的变化。当开关某位置于l时,对应的发光二极管点亮,置于h时熄灭。

四、实验原理介绍

本试验用到两部分电路:脉冲产生电路、8253定时器/计数器电路

五、实验步骤

1.试验连线

CS0<->CS8253OUT0<->8253CLK2OUT2<->LED1CLK3<->8253CLK0,

2.编程调试程序

3.全速运行,观察试验结果

六、实验提示

8253是计算机系统中经常使用的可编程定时器/计数器,其内部有三个相互独立的计数器,分别称为T0,T1,T2。8253有多种工作方式,其中方式3为方波方式。当计数器设好初值后,计数器递减计数,在计数值的前一半输出高电平,后一半输出地电平。试验中,T0、T1的时钟由CLK3提供,其频率为750KHz。程序中,T0的初值设为927CH(37500十进制),则OUT0输出的方波周期为(37500*1/750000=0.05s)。T2采用OUT0的输出为时钟,则在T2中设置初值为n时,则OUT2输出方波周期为n*0.05s。n的最大值为FFFFH,所以OUT2输出方波最大周期为3276.75s(=54.6分钟)。可见,采用计数器叠加使用后,输出周期范围可以大幅度提高,这在实际控制中是非常有用的。

实验 并行IO口8255扩展

}

}

//刷新显示一段时间后递增1,形成滚动效果,最大索引为14

i= (i+1)%15;

}

}

0xff, 0xff, 0xff,0xff, 0xff, 0xff, 0xff, 0xff, 0xff};

//共阳极的7段集成式数码管对应编码

// 0:0xc0

// 1:0xcf

// 2:0xa4

// 3:0xb0

// 4:0x99

// 5:0x92

// 6:0x82

// 7:0xf8

// 8:0x80

#define PC XBYTE[0x0002] //定义8255B地址

#define COM XBYTE[0x0003] //定义8255B控制寄存器地址

//待显示字符队列编码

uchar code DSY_CODE_Queue[ ]=

{0xff, 0xff, 0xff, 0xff, 0xff, 0xff, 0xff,

// 9:0x90

// A:0x88

// B:0x83

// C:0xc6

// D:0xa1

// E:0x86

// F:0x8e

// DOT:0x7f

// -:0xaf

//数码管选通

uchar DSY_Index[]={0x01,0x02,0x04,0x08,0x10,0x20,0x40,0x80};

实验三并行I/O口8255扩展

一、实验目的

1、了解8255A芯片的结构以及编程方法

2、掌握通过8255A并行口读取开关数据的方法

二、实验说明

本次实验用通过8255扩展接口,仅通过P0端口控制8只集成式7段数码管的显示控制。8255A的PA、PB端口分别连接8位数码管的段码和位码,程序控制数码管滚动显示一串数字。

任务八并行IO口扩展

任务分析:采用锁存器扩展并行I/O口

硬件

➢ 采用通用数字电路(74XX或40XX),作为接口电路扩 展并行I/O的方法

软件

➢ 采用锁存器扩展I/O口的编程

编译、下载、调试

➢ 编译软件:keil ➢ 下载软件:STC-ISP

锁存器扩展I/O口的特点

特点:

电路简单、成本低、配置灵活

P0 MCS51

CLK

Q0~Q7

输 出

设

E

备

D0~D7

74LS377

MCS51与74LS377的接口电路

例:将变量Outdata从74LS377输出。 unsigned char xdata *add377 = 0x7fff; unsinged char data Outdata; … *add377 = Outdata;

74LS244扩展并行输入口

74LS244是一种三态输

1G 1A11 2Leabharlann 20VCC19

2G

出8总线收发器/驱动器, 2Y4

无锁存功能。

1A2 2Y3

1A3

3

18

4 74LS 17

5 6

244 16

15

1Y1 2A4 1Y2 2A3

可作为常态数据输入设 2Y2 7

备的输入接口。

1A4

8

2Y1

9

14

1Y3

输出接口:由于大多数外设速度远远低于CPU

速度,输出接口电路必须有锁存功能,锁存CPU 给外设的数据,以便外设慢慢处理。

输入接口:由于大多数外设没有3态缓存功能,

而挂在数据总线的输出端必须有3态缓存功能, 故输入接口电路必须有3态缓存功能。

IO接口电路及其扩展

;写控制字

LD:

;最左边灯亮 ;指向B口 ;取显示数据

;查数据编码 ;写B口 ;延时

39

MB DB DB DB DB DB DB DB MOV MOV DJNZ DJNZ

A, R3

A R3, A LD 3FH 06H 5BH 4FH 66H 6DH 7DH 07H 7FH R7, #02H R6, #FFH R6, LOOP R7, DELAY

6

+5V

P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7

1Y1 1Y2 1Y3 1Y4 1Y5 1Y6 1Y7 1Y8 1G 2G 7 4 L S 2 4 4 1A1 1A2 1A3 1A4 1A5 1A6 1A7 1A8

MCS-51

P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7 RD WR

MOV DPTR, #0FEFFH MOVX A,@DPTR ;确定扩展芯片地址 ;将扩展输入口内容读入累加器A

当与74LS244相连的按键都没有按下时,输入全为 8 1,若按下某键,则所在线输入为0。

典型芯片—74LS245

9

图13-3 74LS244构成的简单输入端口(b)

10

13.1.3 简单的并行口输出

CS:片选信号线,低电平有效。

RD:读信号,控制8255A将数据或状 态信息送给CPU。 WR:写信号,控制CPU将数据或控制 信息到8255A。

A1,A2:地址线,这两个引脚上的信 号组合绝对对8255A内部的哪一个口或 寄存器进行操作。

22

8255的操作表

表13-1 8255的操作

/CS 0 0 0 0 A1 A0 00 01 10 11 WR 0 0 0 0 RD 1 1 1 1 操作 总线=>端口A 总线=>端口B 总线=>端口C 总线=>命令控制字

7并行IO接口电路扩展

CS

0 0 0 0

A1 0 0 1 1

A0 0 1 0 1

RD

0 0 0 0

WR

1 1 1 1

功能 A口→数据总线 B口→数据总线 C口→数据总线 状态寄存器→数据总线

输出

输出 输出

0

0 0

0

0 1

0

1 0

1

1 1

0

0 0

数据总线→ A口

数据总线→ B口 数据总线→ C口

输出

禁止

0

1

1

x

1

x

1

x

0

x

例7-4:8255A作为连接打印机的接口。

下图是通过8255A连接打印机的接口电路,数据传送采用查询方 式。地址译码采用线选法,将A7与8255A的 CS 端相连,其低8位口 地址:A口为0x7C, B口为0x7D,C口为0x7E, 命令口(控制寄存器) 为0x7F。

编制打印50个字符的程序,该数据存于片内RAM从20H开始的50个连续单元 中。程序如下:#include <reg51.h>

P0.7~P0.0 D7~D0 PA7~PA0 PC4 PC5 STBA IBFA PC3 输入设备

D0~D7

INTE A

INT0

8031

EA

& 1

8255A

其中,INTE为中断允许触发器。 INTEA受PC4位置1/置0控制 方式1输入 INTEB受PC2位置1/置0控制

方式1输出

INTEA受PC6位置1/置0控制 INTEB受PC2位置1/置0控制

(1)与外设相连接的有: PA7~PA0:A口I/O线 PB7~PB0:B口I/O线 PC7~PC0:C口I/O线 (2)与单片机相连接的有: D0~D7 数据总线 RESET:复位信号,高有效。当RESET有 效时, 3个端口被设为输入方式。 CS :片选信号,低有效。只有当 CS 有效时, 才选中芯片,允许8255A与CPU交换信息。 RD :读信号,低有效。当 RD 有效时,CPU可 以从8255A中读取输入数据。 WR :写信号,低有效。当 WR 有效时,CPU 可以往8255A中写入控制字或数据

并行IO接口的扩展实验报告

并行IO接口的扩展实验报告一、实验目的1、了解并行IO接口的扩展方法2、掌握可编程接口芯片8255A的工作原理、编程方式和使用方法二、实验条件1、DOS操作系统平台2、8255A接口芯片三、实验原理1、并行IO口的扩展方法:(1)通过通用的IO扩展芯片实现(2)通过TTL、CMOS 锁存器、缓冲器芯片实现。

如74LS377、74LS273、74LS244、74LS245 等。

(3)通过串行通信口扩展并行I/O 口。

2、8255A 扩展I/O 端口:(1)8255A 具有三种基本工作方式,即方式0、方式1、方式2。

各端口的工作方式及输入输出方向都由方式控制字设定(通过写入控制寄存器)。

8255A 的控制字有方式控制字和C 口置位/复位控制字两种。

3、8255A 的工作方式:(1)方式0 是一种基本I/O 方式。

在这种工作方式下,三个端口都可由程序设定为输入或输出,这种方式不使用联络信号,其基本功能为:a. 两个8 位端口(A、B) 和两个4 位端口(C)。

b. 任一个端口可以作为输入或输出。

c. 输出锁存,输入不锁存。

d. 在方式0 时,各端口都可以作为数据端口,CPU 用简单的输入或输出指令来进行读或写。

(2)方式1 是一种选通I/O 方式。

在这种方式下,端口A 和B 可作为数据端口,但C 口的某口的其它位仍可工作于方式0。

方式1 的基本功能为:a. 用作一个或两个选通端口。

b. 每个选通端口包含有:8 位数据瑞口,3 条控制线,提供中断逻辑。

c. 任一端口可输入或输出。

d. 若只有一个端口工作于方式1,余下的13 位可以工作于方式0。

e. 若两个端口工作于方式1,C 口余下2 位可以工作于方式0。

(3)方式2 是一种双向I/O 方式,只有端口 A 具有这种工作方式,其基本功能为:a. 一个8 位双向数据端口(A)和一个5 位控制端口(C)。

b. 输入和输出锁存。

c. 5 位控制端口用作端口A 的状态和控制信息。

并行I-O接口的扩展

MOVDPTR,#OFF7DH;B口地址→DPTR MOVA,#DATA1;要输出的数据#DATA1→A MOVX@DPTR,A;将#DATA1送B口输出 MOVDPTR,#OFF7EH ;C口地址→DPTR MOVA,#DATA2;#DATA2→A MOVX@DPTR,A;将#DATA2送C口输出

8255A的C口8位中的任一位,均可用指令来置位或复位。例 如,如果想把C口的PC5置1,相应的控制字为00001011B=0BH (关于8255A的C口置位/复位的控制字说明参见图5 18),程 序如下:

MOVDPTR,#OFF7FH;控制口地址→DPTR MOVA,#0BH;控制字→A MOVX@DPTR,A;控制字→控制口,PC5=1

(2)方式1:选择输入/输出方式。方式1主要用于中断和查 询数据传送方式,只有A口和B口可以选择这种工作方式。 (3)方式2:双向传送方式。只有A口可以使用方式2,既可以输 入数据,也可以输出数据,此时C口中的PC3~PC7用做A口的控制 和联络信号。

8255A的3种工作 方式由写入控制字寄 存器的方式控制字来 决定。方式控制字的 格式如图所示。3个 端口中C口被分为两 个部分,上半部分随 A口称为A组,下半部 分随B口称为B组。其 中A口可工作于方式0、 1和2,而B口只能工 作在方式0和1。

输入操作: MOV DPTR,#

0FEFFH

MOVX A,

@DPTR

输出操作: MOV A,#DATA

输

入 0FDFFH

信 号

MOV DPTR,# MOVX @DPTR,

A

1.2 可编程并行I/O接口8255A

MCS-51单片机并行IO接口的扩展

第九章MCS-51单片机并行I/O接口的扩展(一)学习要求1、熟悉74LS377、74LS245外围芯片的特性和扩展方法。

2、掌握8255A芯片的结构和工作方式。

3、掌握8155A芯片的结构和工作方式。

4、掌握8155A的RAM和I/O端口寻址方法。

(二)内容提要1、I/O接口的扩展当所需扩展的外部I/O口数量不多时,可以使用常规的逻辑电路、锁存器进行扩展。

这一类的外围芯片一般价格较低而且种类较多,常用的如:74LS377、74LS245、74LS373、74LS244、74LS273、74LS577、74LS573。

1)74LS37774LS377是一种8D触发器,它的E端和CLK端是控制端,当它的E端为低电平时只要在CLK端产生一个正跳变,D0~D7将被锁存到Q0~Q7端输出,在其它情况下Q0~Q7端的输出保持不变。

可以利用74LS377这一特性扩展并行输出口。

如图9-2使用了一片74LS377扩展输出口,如果将未使用到的地址线都置为1则可以得到该片74LS377的地址为7FFFH。

如果单片机要从该片74LS377输出数据的可以执行如下指令:MOV DPTR,#7FFFFHMOVX @DPTR,A2)74LS245。

74LS245是一种三态输出的八总线收发/驱动器,无锁存功能。

它的G端和DIR端是控制端,当它的G端为低电平时,如果DIR为高电平则74LS245将A端数据传送至B端,如果DIR为低电平则74LS245将B端数据传送至A端,在其它情况下不传送数据,并输出高阻态。

可以利用74LS245这一特性扩展并行输入口。

如图9-4使用了一片74LS245扩展输入口,如果将未使用到的地址线都置为1则可以得到该片74LS245的地址为7FFFH。

如果单片机要从该片74LS377输出数据的可以执行如下指令:MOV DPTR,#7FFFFHMOVX A,@DPTR2、8255A可编程I/O接口设计及扩展技术8255A是一种常见的8位可编程并行接口芯片,本接将着重介绍8255A的工作原理、编程方式和应用。

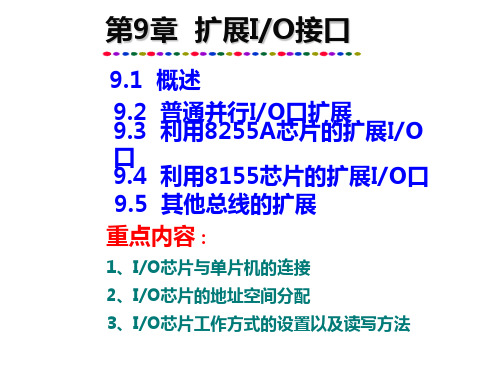

第7章单片机并行IO口的扩展

7.3.4 8255A的控制字 8255A有三种工作方式: (1) 方式0:基本输入输出; (2) 方式1:选通输入输出; (3) 方式2:双向传送(仅A口有)。 1.工作方式选择控制字

三种工作方式由方式控制字来决定。 控制字格式如下。

C口上半部分(PC7~PC4)随A口称为A组, C口下半部分(PC3~PC0)随B口称为B组。 其中A口可工作于方式0、1、和2,而B口只能工作在 方式0和1。

• 分析:由图7-8可知,P2.7=0才选中该片8255,A1 A0(P2.1 P2.0)为00 01对应PA口和PB口、为11时对应控制 口。其余地址写1,A口、B口、控制口地址分别为7CFFH、 7DFFH、7FFFH。设定PA口方式0输出, B口方式0输入,控

7.1.3 I/O端口的编址方式 I/O端口编址是给所有I/O接口中的寄存器编址。

I/O端口编址两种方式:独立编址与统一编址。 1.独立编址方式

I/O寄存器地址空间和存储器地址空间分开编址, 但需专门读写I/O的指令和控制信号。 2.统一编址方式

I/O寄存器与数据存储器单元同等对待,统一编址。 不需要专门的I/O指令,直接使用访问数据存储器。 的指令进行I/O操作,简单、方便且功能强。

(2)任一个端口都可以设定为输入或输出,各端口 的输入、输出可构成16种组合。

(3)数据输出锁存,输入不锁存。

例 假设8255A的控制字寄存器地址为FF7FH,则令A口 和C口的高4位工作在方式0输出, B口和C口的低4位 工作于方式0输入,初始化程序:

MOV DPTR,#0FF7FH ;控制字寄存器地址送DPTR

2.I/O口接口的作用

CPU与I/O设备交换信息情况较为复杂,所以通常 I/O设备并不直接与CPU进行信息交换,而是通过相应 的输入/输出接口(称为I/O接口)来进行的。I/O接 口是CPU和I/O设备之间进行信息交换的中间环节,其 主要功能如下: (1)对输入输出数据进行缓冲、隔离和锁存,实现 速度匹配。 (2)完成信息格式的变换,如串并转换。 (3)实现电气特性的匹配。 (4)选择设备或地址译码等。

IO接口的扩展方法

程序如下: 程序如下: MOV DPTR, #7FFFH MOV A, 60H MOVX @DPTR, A

二、扩展并行输入口 用单向总线缓冲器74LS244扩展并行输入口 用单向总线缓冲器74LS244扩展并行输入口 ,硬件电 74LS244 路如下图所示。74LS244的地址为7FFFH。 的地址为7FFFH 路如下图所示。74LS244的地址为7FFFH。

E

一、8255A的内部结构和引脚 8255A的内部结构和引脚

A组 控制 A组 端口A (8) I/O PA7~PA0

Vcc GND RESET

PA0~PA7

数据 总线 D7~D0 缓冲

A组 端口C 上半部(4)

I/O PC7~PC4

CS RD WR PB0~PB7 8255

B组 端口C 下半部(4)

主要内容: 、利用TTL、CMOS集成电路来扩展 主要内容: 1、利用 、 集成电路来扩展 2、利用可编程并行接口芯片来扩展 、

一、I/O接口的功能 I/O接口的功能

1、速度协调 、 由于CPU与外设速度上的差异,使得数据的 传送只能在 与外设速度上的差异, 由于 与外设速度上的差异 使得数据的I/O传送只能在 确认外设已为数据传送作好准备的前提下才能进行I/O操作 操作。 确认外设已为数据传送作好准备的前提下才能进行 操作。 2、数据锁存 、 单片机的工作速度快,数据在数据总线上保留的时间短, 单片机的工作速度快,数据在数据总线上保留的时间短, 无法满足慢速外设的数据接收。 无法满足慢速外设的数据接收。因此数据锁存就成为接口电路 的一项重要功能。 的一项重要功能。 3、输入数据三态缓冲 、 只允许当前时刻正在进行数据传送的数据源使用数据总线, 只允许当前时刻正在进行数据传送的数据源使用数据总线, 其它数据源都必须与数据总线处于隔离状态。 其它数据源都必须与数据总线处于隔离状态。为此要求接口电 路能为数据输入提供三态缓冲功能。 路能为数据输入提供三态缓冲功能。 4、数据转换 、 需要使用接口电路进行数据信号的转换 其中包括: 信号的转换。 需要使用接口电路进行数据信号的转换 。 其中包括: D/A 转换、 转换、 并转换和并/ 串转换等。 转换、A/D转换、串 / 并转换和并 串转换等。 转换

第九章MCS51并行IO接口扩展

*

8255初始化

对8255的3个端口的工作方式预先设置。设置 方式控制字从控制口写入。 例如:设置8255的A、B、C口全为输出方式,方式控 制字为80H。

初始化程序为: MOV DPTR, #7FFFH ;8255控制口地址送DPTR MOV A, #80H ;控制字送A MOVX @DPTR, A ;控制字写入控制寄存器

B组

RD WR

A

D7——D0 C

A1 A0 B

8255的方式 1

PC口

A

PA0-7 PC4-7 PC0-3 PB0-7 PA0-7

7 6 5 4 3

2 1 0

B

A组

B组

控制线

I/O

PB0-7

A组

B组

8255的方式 0

8255的方式 2

8255的端口选择表:

A1A0 RD WR CS

0 0 0 1 0 1 0 1 1 X 0 0 0 X 1 0 1 0

8255可编程并行接口的扩展

PA4 PA5 PA6 PA7 WR RESET D0 D1 D2 D3 D4 D5 D6 D7 VCC PB7 PB6 PB5 PB4 PB3

8255

8255的基本特性与引脚: PA,PB,PC 三个8位I/O口; 一个8位的数据口D0~D7。 PC口分高4位和低4位。 高4位可与PA口合为一组(A组) 低4位可与PB口合为一组(B组) 内部有4个寄存器,由A1,A0与读,写信号 选择。 片选低有效,复位高有效。 40条引脚,DIP封装

MOV DPTR, #7FFFH MOV A, #82H MOVX @DPTR, A LOOP: MOV DPTR, #7FFDH MOVX A, @DPTR MOV DPTR, #7FFCH CPL A ;把A中的内容逐位取反 MOVX @DPTR, A SJMP LOOP

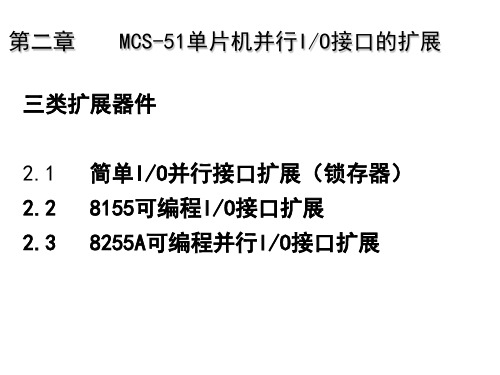

第二章MCS51并行IO接口扩展

简单I/O扩展:(缓冲/驱动器扩展)

P0.0-P0.7

P2.1 WR 单片机 或门 P2.0 RD ≥1 D0 D7 1G* 2G* D0 D7 D0 D7 D0 D7 输出

≥1

或门

CLK

锁存器 74LS273

输入

缓冲器 74LS244

输出: MOV DPTR,#0FD00H MOV A,#DATA MOVX @DPTR, A 输入: MOV DPTR,#0FE00H MOVX A, @DPTR

P2.7……………P2.0 P0.7……………… P0.0 0 X X X X X X 0 X X X X X X 0 0 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1

地址

RAM单元 0号 255号

0000H 00FFH

程序: ;R7作计数器,从0开始共 ;减256次再到0 MOV A,#0FFH ;准备送FFH MOV DPTR,#0000H ;DPTR指向第一个单元 LOOP: MOVX @DPTR,A ;送数 INC DPTR ;调整指针,指向下一个 ;单元 DJNZ R7,LOOP ;循环控制 SJMP $ MOV R7,#00H

第二章

MCS-51单片机并行I/O接口的扩展

三类扩展器件 2.1 2.2 简单I/O并行接口扩展(锁存器) 8155可编程I/O接口扩展

2.3

8255A可编程并行I/O接口扩展

2.1 简单I/O并行接口扩展

在单片机的I/O口线不够用的情况下,可以外接芯片 对I/O口进行扩展。可选用的器件类型很多。 如利用TTL、CMOS的锁存器、三态门等接口芯片把 P0 接口扩展。常选用74LS377、74LS373、74LS374等 通常输出需要锁存,输入需要缓冲