Ncverilog 命令使用详解

Cadence 实验系列10_Verilog设计平台_NC-Verilog

仿真器 (Simulator)

VI编辑器

选中所有 相关文件 后,点击 编译 RISC CPU 所有模块文 件及仿真文 件

编译成功

描述前进行 设定,Tools >elaborator

非所有代码 都加了时间, 为防止报错

Snapshot 文件

描述成功

控制窗口

设计浏览器

不报错,可以仿真

SimVision中你 可以存储个别目 标或者范围的仿 真数据,使得仿 真数据尽量少, 因此需要设定探 测类型。 选择顶层模块 ->Simulation ->Create Probe

优点:

业界第一的性能加快设计验证 64位机器上设计超过1亿门的芯片 用一体化的事务/信号视窗使效率最大化 集成化的代码覆盖保证全面的验证 通过完全兼容的升级到Incisive验证平台获得终极 的验证速度和效率 来自超过30家ASIC供应商的经过认证的库保证精 确性

缺点(个人认为):

NC-Verilog仿真器

NC-Verilog是Verilog-XL的升级版, 它采用NativeCompiled技术, 无论仿真速度, 处理庞大设计能力, 编辑能力, 记忆体容量和侦错环境都以倍数升级。 NC-Verilog是一个编译仿真器,它把Verilog代码 编译成Verilog程序的定制仿真器。也就是它把 Verilog代码转换成一个C程序,然后再把该C程序 编译成仿真器。因此它启动得稍微慢一些,但这 样生成的编译仿真器运行得要比Verilog-XL的解释 仿真器快很多。它也与Verilog-2001标准的大部分 兼容,并且一直被Cadence经常更新,因此包含 了越来越多的高级应用特点。

点击Apply后便可以得到想要的信号显示方式

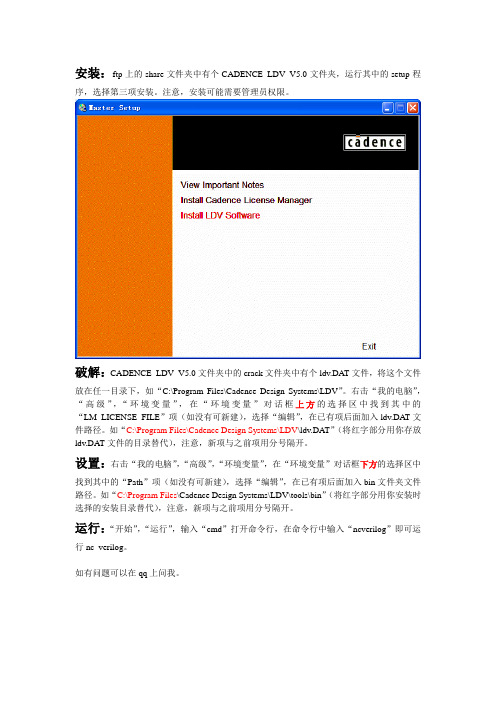

cadence_ldv即ncverilog安装方法

安装:ftp上的share文件夹中有个CADENCE_LDV_V5.0文件夹,运行其中的setup程

序,选择第三项安装。

注意,安装可能需要管理员权限。

破解:CADENCE_LDV_V5.0文件夹中的crack文件夹中有个ldv.DAT文件,将这个文件

放在任一目录下,如“C:\Program Files\Cadence Design Systems\LDV”。

右击“我的电脑”,“高级”,“环境变量”,在“环境变量”对话框上方的选择区中找到其中的“LM_LICENSE_FILE”项(如没有可新建),选择“编辑”,在已有项后面加入ldv.DA T文件路径。

如“C:\Program Files\Cadence Design Systems\LDV\ldv.DAT”(将红字部分用你存放ldv.DAT文件的目录替代),注意,新项与之前项用分号隔开。

设置:右击“我的电脑”,“高级”,“环境变量”,在“环境变量”对话框下方的选择区中

找到其中的“Path”项(如没有可新建),选择“编辑”,在已有项后面加入bin文件夹文件路径。

如“C:\Program Files\Cadence Design Systems\LDV\tools\bin”(将红字部分用你安装时选择的安装目录替代),注意,新项与之前项用分号隔开。

运行:“开始”,“运行”,输入“cmd”打开命令行,在命令行中输入“ncverilog”即可运行nc_verilog。

如有问题可以在qq上问我。

NC-Verilog

SimVision让你控制和查询你的 设计仿真。SimVision中你可以 存储个别目标或者范围的仿真 数据,这可以使得仿真数据尽 量的小。 因此需要设置探测类型: 在设计窗口中,点击 test_drink _machine 图示旁边的加号,展开设计的 层次结构。选择顶层模块--> 选择菜单Simulation--〉 Create Probe

准备工作介绍

本例将演示如何在多步实现(multi-step) 的模式下使用NCLaunch。 文件路径: (ftp模式访问)网上邻居选项 访问服务器账户:stu707 访问密码:stu2016

启动NClaunch

在拷贝了源文件的文件夹下面启动 nclaunch -new & 多步模式(Multiple Step)使用ncvlog和 ncelab命令来编译和描述你的设计;单步模 式(Single Step)使用ncverilog命令。选 择多步模式。

DC综合生成标准延时文件(.Sdf文件)

SDF version 选1.0 文件名后缀为 .sdf

综合过程的操作参考DC 使用说明

谢谢!

按照上图所示进行修改即可,完成后点击表示确认

选择—〉File—〉Close Window关闭选项窗口

如果对源代码进行了修改,则要在重新生成一次snapshot, 然后在Console Window 点击simulationreinvoke simulator 出现图示对话在Console Window 点击simulationrun即可

NC-Verilog概述

在SimVision分析环境下进行对设计中的问 题的调试。 SimVision是一个candence 仿真器统一的 图形化的调试环境。SimVision可以用于调 试用verilog,vhdl,SystemC或者它们混合 写成的数字,仿真,或数模混合电路的设计。

Ncverilog命令使用详解

Ncverilog命令使用详解NCVerilog是一种用于模拟、调试和分析Verilog和SystemVerilog 代码的命令行工具。

以下是对NCVerilog命令使用的详细解释。

1. `ncverilog`命令:启动NCVerilog编译器。

语法如下:```ncverilog [options] <file_list>```- `options`:附加的编译选项,例如`-sv`表示编译SystemVerilog 代码。

- `file_list`:包含要编译的源文件的列表。

2. `+access+r`选项:允许模拟工具读取源代码中的注释。

这对于调试和分析时非常有用。

3. `+define+<macro>`选项:定义一个宏。

这可以用于在模拟期间改变代码的行为。

例如:```+define+DEBUG```4. `+incdir+<dir>`选项:指定包含库文件的目录。

这对于使用外部库或模块时非常有用。

5. `+define+<macro>={value}`选项:为宏指定一个值。

例如:```+define+WIDTH=8```6. `+libext+<ext>`选项:指定库文件的扩展名。

可以用于指定Verilog或SystemVerilog库文件的不同扩展名。

``````8. `+vcs`选项:指定使用VCS编译器的系统Verilog代码。

这对于一些特定的系统Verilog代码可能是必需的。

9. `-y <dir>`选项:指定一个目录,其中包含其他用户定义的Verilog或SystemVerilog库文件。

10. `-v <file>`选项:指定一个要编译的单独的库文件。

11. `-f <file>`选项:指定一个包含文件列表的文件。

这可以用于指定要编译的多个源文件。

12. `-fsmdebug`选项:在编译期间为FSM(有限状态机)创建调试信息。

ncverilog使用

Ncverilog 使用在NC自带的帮助Cadence NC-Verilog Simulator Help中都可以找到。

以下整理自网络,有点乱 :(ncverilog是shell版的,nclaunch是以图形界面为基础的,二者调用相同内核;ncverilog的执行有三步模式和单步模式,在nclaunch中对应multiple step和single step ncverilog的三步模式为:ncvlog(编译) ncelab(建立snapshot文件) ncsim(对snapshot文件进行仿真)基于shell的ncverilog操作(尤其是单步模式)更适合于大批量操作ncverilog的波形查看配套软件是simvision,其中包含原理图、波形、信号流等查看方式三命令模式:>ncvlog -f run.f>ncelab tb -access wrc>ncsim tb -gui第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb文件放在首位,这样可以避免出现提示timescale的错误注意:ncvlog执行以后将产生一个名为INCA_libs的目录和一个名为worklib的目录第二个命令中,access选项是确定读取文件的权限。

其中的tb是你的tb文件内的模块名字。

注意:ncelab要选择tb文件的module,会在snapshot文件夹下生成snapshot的module文件第三个命令中,gui选项是加上图形界面在这种模式下仿真,是用“ - ”的。

而下边要说的ncverilog是采用“ +”的三命令模式下GUI界面较好用,其对应的命令会在console window中显示注意:选择snapshot文件夹下生成的module文件进行仿真单命令模式:>ncverilog +access+wrc rtl +gui在这里,各参数与三命令模式相同。

注意“ + ”通常都使用单命令模式来跑仿真,但要配置好一些文件单命令模式下文件的配置:目录下有源文件、测试台文件、file、run四个文件在linux下执行source run后再执行simvision来查看run文件内容: ncverilog +access+rw -f filefile文件内容: cnt_tb.v(注意把tb文件放在前)cnt.vtb文件中应该包含:initialbegin$shm_open("wave.shm"); //打开波形保存文件wave.shm$shm_probe(cnt_tb,"AS"); //设置探针endA -- signals of the specific scope 为当前层信号设置探针S -- Ports of the specified scope and below, excluding library cellsC -- Ports of the specified scope and below, including library cellsAS -- Signals of the specified scope and below, excluding library cells 为当前层以以下层信号都设置探针,这是最常用的设置方法AC -- Signals of the specified scope and below, including library cells还有一个 M ,表示当前scope的memories, 可以跟上面的结合使用, "AM" "AMS" "AMC"什么都不加表示当前scope的ports;$shm_close //关闭数据库查看结果时可以在source schemic wave register四个窗口同时查看保存波形信号的方法:1.SHM数据库可以记录在设计仿真过程中信号的变化. 它只在probes有效的时间内记录你setprobe on的信号的变化.2.VCD数据库也可以记录在设计仿真过程中信号的变化. 它只记录你选择的信号的变化.$dumpfile("filename"); //打开数据库$dumpvars; //depth = all scope = all$dumpvars(0); //depth = all scope = current$dumpvars(1, top.u1); //depth = 1 scope = top.u1$dumpoff //暂停记录数据改变,信号变化不写入库文件中$dumpon //重新恢复记录3.Debussy fsdb数据库也可以记录信号的变化,它的优势是可以跟debussy结合,方便调试.如果要在ncverilog仿真时,记录信号, 首先要设置debussy:a. setenv LD_LIBRARY_PATH :$LD_LIBRARY_PATH(path for debpli.so file(/share/PLI/nc_xl//nc_loadpli1))b. while invoking ncverilog use the +ncloadpli1 option. ncverilog -f run.f +debug+ncloadpli1=debpli:deb_PLIPtrfsdb数据库文件的记录方法,是使用$fsdbDumpfile和$fsdbDumpvars系统函数,使用方法参见VCD注意: 在用ncverilog的时候,为了正确地记录波形,要使用参数: "+access+rw", 否则没有读写权限产生FSDB波形文件的若干技巧:/bbs/viewthread.php?tid=2539&;extra=page%3D1下载:/bbs/viewthread.php?tid=3357&;extra=page%3D1ncverilog编译的顺序: ncverilog file1 file2 ....有时候这些文件存在依存关系,如在file2中要用到在file1中定义的变量,这时候就要注意其编译的顺序是从后到前,就先编译file2然后才是file2.,信号的强制赋值force:首先, force语句只能在过程语句中出现,即要在initial 或者 always 中间. 去除force 用release 语句.;initial begin force sig1 = 1'b1; ... ; release sig1; end, force可以对wire赋值,这时整个net都被赋值; 也可以对reg赋值.Verilog和Ncverilog命令使用库文件或库目录ex). ncverilog -f run.f -v lib/lib.v -y lib2 +libext+.v //一般编译文件在run.f中, 库文件在lib.v中,lib2目录中的.v文件系统自动搜索,使用库文件或库目录,只编译需要的模块而不必全部编译Q:我的files里面只有一个help文件夹,里面是一个叫ncprotect文件,没有你所说的hdl.var文件啊A:1、NC-VERILOG在创建工程时会生成两个文件:cds.lib和hdl.var。

Verilog中各种语句含义及用法简述

Verilog中各种语句含义及⽤法简述Verilog中各种语句含义及⽤法简述⼀般认为Verilog HDL在系统级抽象⽅⾯⽐VHDL略差⼀些,⽽在门级开关电路描述⽅⾯⽐VHDL要强的多写了第⼀个verilog程序,是⼀个加法器内容如下module adder(count,sum,a,b,cin);input[2:0] a,b;input cin;output count;output [2:0] sum;assign{count,sum}=a+b+cin;endmodule开始编译出现了⼏次错误,后来发现给实体的命名和程序中实体要⼀致⽽且⼤⼩写要⼀样,整个程序是嵌套再module和endmodule当中的⽽其中的注释和C/C++类似,⽤//和来标明module compare(equal,a,b);output equal;input [1:0] a,b;assign equal=(a==b)?1:0;//和C语⾔中的相同endmoduleverilog的基本设计单元是“模块(BLOCK)”。

⼀个模块由两个部分组成,⼀部分描述端⼝,⼀部分描述逻辑功能,即定义输⼊是如何影响输出的。

如下module block(a,b,c,d);input a,b;output c,d;assign c="a|b";assign d="a"&b;endmodule模块中最重要的部分是逻辑功能定义。

有三种⽅法可以再模块中产⽣逻辑。

1、⽤“assign”声明语句如:assign a="b"&c;2、⽤实例元件,如同调⼊库元件⼀样如:and and_inst(q,a,b);3、⽤“always”块如:always @(posedge clk or posedge clr) //always块⽣成了⼀个带有异步清除端的D触发器。

beginif(clr) q<=0;else if(en) q<=d;end采⽤assign语句是最常⽤的⽅法之⼀。

IUS9.2_ncverilog安装

下载ius9.2解压后一共六个文件打开超级终端,进入到此六个文件目录下第一步:./SETUP.SH第二步:设定安装目录(即安装到哪里)第三步:输入y第四步:设定安装源文件的目录(即,一开始解压的六个文件的那个目录)第五步:【与第三步一样】输入y第六步:【与第四步一样】设定安装源文件的目录(即,一开始解压的六个文件的那个目录)第七步:第六步后会弹出窗口,路径就是刚才第四步与第六步设定的路径,不要改,点NEXT>第八步:点NEXT>第九步:路径就是刚才第二步设定的路径,不要改,点NEXT>第十步:全部勾选,点NEXT>第十一步:点install第十二步:等待(直到100%安完),点close第十三步:弹出窗口,点NO第十四步:关掉下面界面,就会回到终端第十五步,进入安装目录,即第二步的目录,在安装目录下给tools.lnx86建一个快捷方式叫tools(使用命令ln -s tools.lnx86 tools)第十六步:复制sfk和patch_cadence(这两个文件是破解文件,到下面网址能下载到,同时也能下载到IUS软件,感谢该网友的无私奉献,/viewthread.php?tid=304428&from=favorites)到IUS安装目录下,执行./patch_cadence第十七步:在windows上面制作license首先打开LicGen.exe软件,点击open,打开Cadence.lpd然后按下图填写,注意Custom后面的那一串是机器的MAC地址,如果是用虚拟机的话,在终端中运行/sbin/ifconfig -a Hwaddr 后面就是虚拟机的MAC!,点击Generate,然后Save成license.dat。

之后用记事本打开license.dat,第一行的SERVER 后面要改成虚拟机的主机名,虚拟机主机名一般默认是localhost.localdomain 。

Verilog语言详解

第三章 Cadence仿真器

学习内容

逻辑仿真算法 如何启动Verilog-XL和NC Verilog仿真器 如何显示波形

仿真算法

主要有三种仿真算法

基于时间的(SPICE仿真器) 基于事件的(Verilog-XL和NC Verilog仿真器) 基于周期的(cycle)

仿真算法

基于时间的算法用于处理连续的时间及变量

课程内容(三)

• 逻辑综合的介绍

– – – – – 简介 设计对象 静态时序分析 (STA) design analyzer环境 可综合的HDL编码风格

• 可综合的Verilog HDL

– Verilog HDL中的一些窍门 – Designware库 – 综合划分

•

实验 (1)

课程内容(四)

• 设计约束( Constraint)

Verilog HDL是在1983年由GDA(GateWay Design Automation)公司的Phil Moorby所创。Phi Moorby 后来成为Verilog-XL的主要设计者和Cadence公司的第一个合伙人。

在1984~1985年间,Moorby设计出了第一个Verilog-XL的仿真器。

Verilog还有一定的晶体管级描述能力及算法级描述能力

行为级和RTL级

MUX的行为可以描述为:只要信号a或b或sel发生变化,如果sel为0则选择a输出;否则选择 b输出。

module muxtwo (out, a, b, sel); input a, b, sel; output out; reg out; always @( sel or a or b) if (! sel) out = a; else out = b; endmodule

NC-verilog 仿真教程和实验实例

Cadence IC设计实验实验六 NC-Verilog Simulator实验实验目的:NC_verilog仿真器的使用,包括编译、运行和仿真。

预备工作:cp /eva01/cdsmgr/ training_IC_data/NCVlog_5_0.tarZ .tar -vxfZ NCVlog_5_0.tarZLab1。

运行一个简单的Verilog设计[1]、设置设计环境1.cd NCVlog_5_0/lab1-mux这个目录包含了用来描述一个多路选择器和其测试平台的verilog 模块。

以下是mux_test.v模块内功能模块的端口框图。

建议:如果有时间,你最好看一看各模块(module)的Verilog代码!2.创建cds.lib文件,vi cds.lib(回车)按小写”i”切换到编辑模式,在其中写入:Define lab1muxlib ./lab1-mux.lib有关vi的编辑命令,请参阅相关资料。

如”Esc”键切换到命令状态,在命令状态下,”x”是删除当前字符,”a”是在当前光标后写入,”:wq”是存盘退出,”:!q”是不保存退出。

存盘退出3.创建(库)文件夹(即目录):mkdir lab1-mux.lib (回车)4.类似步骤1,创建hdl.var文件,在其中写入:Define WORK lab1muxlib存盘退出5.查看verilog源文件。

mux.v是2选1多路选择器MUX2_1 的门级建模源文件,mux_test.v是mux.v的测试台,包含了输入激励信号和监控程序运行的任务语句。

[2]、编译源文件(ncvlog命令):当前目录应为。

/你的学号/NCVlog_5_0/lab1-mux。

1.ncvlog mux.v –messages ,这条指令是编译mux.v。

2.vi hdl.var打开hdl.var文件,在其中添加:Define NCVLOGOPTS –messages 存盘退出注:用NCVLOGOPTS变量定义常用的ncvlog命令行操作,从而避免每次都敲入同样的命令行。

verilog 函数的使用

verilog 函数的使用Verilog函数的使用Verilog是一种硬件描述语言,常用于数字电路的设计和验证。

在Verilog中,函数是一种重要的组织代码的方式,可以将一段具有特定功能的代码封装成函数并在需要的时候进行调用。

本文将介绍Verilog函数的使用方法和一些常见的应用场景。

一、函数的定义和使用在Verilog中,函数的定义使用关键字"function",并指定函数的返回类型和参数列表。

以下是一个简单的函数示例:```function int add(int a, int b);add = a + b;endfunction```以上函数名为"add",返回类型为整数(int),参数列表中有两个整型参数a和b。

函数体中的代码实现了将a和b相加的功能,并将结果赋值给函数的返回值。

函数的调用使用关键字"call",并在括号中传入相应的参数值。

以下是调用上述函数的示例:```int result;result = add(3, 4);```在这个示例中,函数"add"被调用,并将参数3和4传入。

函数执行完毕后,返回值7被赋值给变量"result"。

二、函数的返回值函数在执行完毕后会返回一个值,该值的类型与函数的返回类型相匹配。

在函数体中,可以使用关键字"return"来指定返回的值。

以下是一个返回布尔类型的函数示例:```function bit isEven(int num);if(num % 2 == 0)return 1'b1; // 返回真elsereturn 1'b0; // 返回假endfunction```在这个示例中,函数"isEven"接收一个整数参数"num",并通过判断num是否为偶数来返回一个布尔值。

《NCverilog教程》课件

覆盖率

覆盖率是测试验证中的一个重要概念, 它描述了测试用例覆盖了多少代码。覆 盖率可以分为多种类型,如语句覆盖率 、分支覆盖率、条件覆盖率等。

VS

断言

断言是Verilog中用于描述程序行为的一 种方式。断言可以用于检查程序中的某些 条件是否满足,如果不满足则产生错误。 断言通常用于验证程序的正确性。

详细描述:通过中等难度的实例,帮助学习者深入理解 Verilog的编程原理和技巧,提高编程能力。

详细描述:通过中等难度的实例,让学习者实践编写较 复杂的Verilog代码,掌握高级编程技巧和方法。

复杂实例解析

在此添加您的文本17字

总结词:高级应用

在此添加您的文本16字

详细描述:通过复杂的Verilog代码实例,介绍Verilog在 硬件设计中的应用和实践,包括数字系统设计、硬件测试 等。

05

NCVerilog调试与优化

Chapter

调试工具与技巧

调试工具

使用NCVerilog的调试工具,如仿真 器、调试器等,可以帮助开发者定位 和解决代码中的问题。

调试技巧

在调试过程中,可以采用断点、单步 执行、变量监视等技巧,以便更好地 观察和了解代码的执行情况。

优化策略与技巧

优化策略

优化NCVerilog代码时,可以采用一些常见的优化策 略,如流水线化、并行化、减少计算复杂度等。

它基于Verilog语言,并扩展了其功能 ,支持高性能的数字系统设计。

NCVerilog的特点

支持高性能数字系统设计

NCVerilog提供了高性能的硬件描述语言,支 持大规模数字系统的设计和实现。

高效仿真和综合

NCVerilog具有高效的仿真和综合工具,能够 快速验证和实现设计。

ncverilog使用

Ncverilog 使用在NC自带的帮助Cadence NC-Verilog Simulator Help中都可以找到。

以下整理自网络,有点乱 :(ncverilog是shell版的,nclaunch是以图形界面为基础的,二者调用相同内核;ncverilog的执行有三步模式和单步模式,在nclaunch中对应multiple step和single step ncverilog的三步模式为:ncvlog(编译) ncelab(建立snapshot文件) ncsim(对snapshot文件进行仿真)基于shell的ncverilog操作(尤其是单步模式)更适合于大批量操作ncverilog的波形查看配套软件是simvision,其中包含原理图、波形、信号流等查看方式三命令模式:>ncvlog -f run.f>ncelab tb -access wrc>ncsim tb -gui第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb文件放在首位,这样可以避免出现提示timescale的错误注意:ncvlog执行以后将产生一个名为INCA_libs的目录和一个名为worklib的目录第二个命令中,access选项是确定读取文件的权限。

其中的tb是你的tb文件内的模块名字。

注意:ncelab要选择tb文件的module,会在snapshot文件夹下生成snapshot的module文件第三个命令中,gui选项是加上图形界面在这种模式下仿真,是用“ - ”的。

而下边要说的ncverilog是采用“ +”的三命令模式下GUI界面较好用,其对应的命令会在console window中显示注意:选择snapshot文件夹下生成的module文件进行仿真单命令模式:>ncverilog +access+wrc rtl +gui在这里,各参数与三命令模式相同。

注意“ + ”通常都使用单命令模式来跑仿真,但要配置好一些文件单命令模式下文件的配置:目录下有源文件、测试台文件、file、run四个文件在linux下执行source run后再执行simvision来查看run文件内容: ncverilog +access+rw -f filefile文件内容: cnt_tb.v(注意把tb文件放在前)cnt.vtb文件中应该包含:initialbegin$shm_open("wave.shm"); //打开波形保存文件wave.shm$shm_probe(cnt_tb,"AS"); //设置探针endA -- signals of the specific scope 为当前层信号设置探针S -- Ports of the specified scope and below, excluding library cellsC -- Ports of the specified scope and below, including library cellsAS -- Signals of the specified scope and below, excluding library cells 为当前层以以下层信号都设置探针,这是最常用的设置方法AC -- Signals of the specified scope and below, including library cells还有一个 M ,表示当前scope的memories, 可以跟上面的结合使用, "AM" "AMS" "AMC"什么都不加表示当前scope的ports;$shm_close //关闭数据库查看结果时可以在source schemic wave register四个窗口同时查看保存波形信号的方法:1.SHM数据库可以记录在设计仿真过程中信号的变化. 它只在probes有效的时间内记录你setprobe on的信号的变化.2.VCD数据库也可以记录在设计仿真过程中信号的变化. 它只记录你选择的信号的变化.$dumpfile("filename"); //打开数据库$dumpvars; //depth = all scope = all$dumpvars(0); //depth = all scope = current$dumpvars(1, top.u1); //depth = 1 scope = top.u1$dumpoff //暂停记录数据改变,信号变化不写入库文件中$dumpon //重新恢复记录3.Debussy fsdb数据库也可以记录信号的变化,它的优势是可以跟debussy结合,方便调试.如果要在ncverilog仿真时,记录信号, 首先要设置debussy:a. setenv LD_LIBRARY_PATH :$LD_LIBRARY_PATH(path for debpli.so file(/share/PLI/nc_xl//nc_loadpli1))b. while invoking ncverilog use the +ncloadpli1 option. ncverilog -f run.f +debug+ncloadpli1=debpli:deb_PLIPtrfsdb数据库文件的记录方法,是使用$fsdbDumpfile和$fsdbDumpvars系统函数,使用方法参见VCD注意: 在用ncverilog的时候,为了正确地记录波形,要使用参数: "+access+rw", 否则没有读写权限产生FSDB波形文件的若干技巧:/bbs/viewthread.php?tid=2539&;extra=page%3D1下载:/bbs/viewthread.php?tid=3357&;extra=page%3D1ncverilog编译的顺序: ncverilog file1 file2 ....有时候这些文件存在依存关系,如在file2中要用到在file1中定义的变量,这时候就要注意其编译的顺序是从后到前,就先编译file2然后才是file2.,信号的强制赋值force:首先, force语句只能在过程语句中出现,即要在initial 或者 always 中间. 去除force 用release 语句.;initial begin force sig1 = 1'b1; ... ; release sig1; end, force可以对wire赋值,这时整个net都被赋值; 也可以对reg赋值.Verilog和Ncverilog命令使用库文件或库目录ex). ncverilog -f run.f -v lib/lib.v -y lib2 +libext+.v //一般编译文件在run.f中, 库文件在lib.v中,lib2目录中的.v文件系统自动搜索,使用库文件或库目录,只编译需要的模块而不必全部编译Q:我的files里面只有一个help文件夹,里面是一个叫ncprotect文件,没有你所说的hdl.var文件啊A:1、NC-VERILOG在创建工程时会生成两个文件:cds.lib和hdl.var。

模拟电路提取Verilog模型的方法

模拟电路提取V e r i l o g模型的方法Document number:WTWYT-WYWY-BTGTT-YTTYU-2018GT模块电路提取Verilog模型的方法总结陈锋2018-1-181.在原理图目录,运行icfb。

2.选Tools->LibraryManager…3.在Library找到要提取的库(一般是项目名称),这里选NV3030A1P_GRAM。

在Cell里选要提取的顶层模块,这里选GRAM。

View里选schematic,并右击选open4.在打开的原理图VirtiosoSchematic菜单里,选Tools->Simulation->NC-Verilog5.在设置窗口里,RunDirectory手工填入提取Verilog网表的目录名,比如xxx/GRAM_run66.TopLevelDesign里,点Browser…,选择要提取的顶层,我们这里选择与第3步相同的Library、Cell和View。

如下图,选好后点Close。

7.点左边“跑步的人”来InitialDesign。

会看到“三个勾”(GenerateNetlist)的图标显示出来了。

8.选Setup->Netlist…9.设置提取参数。

我们需要修改“NetlistTheseViews”和“StopNetlistingatViews”,如下图设置。

另外时间和精度也可以在此设置,默认是1ns/1ns,是全局的设置。

我建议不要修改,在生成VerilogNetlist后,手工修改一些特殊模块来提高精度即可。

设置好后,点Apply,OK。

10.点击“三个勾”生成VerilogNetlist。

稍等片刻后,第三个图标“模块图”显示出来,说明网表也生成好。

11.我们进入GRAM_run6目录,并进入子目录ihnl。

会看到很cdsxx开头的文件夹,再看cdsxx目录里面有个netlist文件。

用文本编辑器打开netlist,你就看到了提取出来的Verilog网表了。

linux系统下ncverilog的详细命令

ncverilog: 08.10-p002: (c) Copyright 1995-2008 Cadence Design Systems, Inc. Usage:ncverilog [options] filesFile languages: Verilog, SystemVerilog, VHDL, e, System-C, C, C++In addition to the dash options all ncverilog plus options can be used.Options shown below in lowercase can also be entered in uppercase.For example, both -top and -TOP are valid.If you need more information about an option listed below, use the searchfacility in the online help system. In the "Search for" text box,enter the name of the option, including the dash (-profile, for example).+access<+/-rwc> Turn on read, write and/or connectivity access+allow_unused_properties Allow simulator to enable all properties-allowredefinition Allow mutiple files to define the same object+amsconnrules+<cellname> specify connect rules to use+amsmatlab Dynamically link vpi code for AMS/Matlab-amsmt_enable to enable AMS multithread capability-amsmt_nthreads <arg> number of threads for AMS multithreading.-amsvhdl_ext <ext> Override extensions for VHDL AMS sources+append_key Append keystrokes to existing key file-arr_access Allow tf_nodeinfo access to Verilog arrays-asext <ext> Add extensions to assembly sources+assert Enable PSL language features+assert_count_traces Use trace-based counting for assertions+assert_sc Enable PSL language features+assert_vhdl Enable PSL language features+assert_vlog Enable PSL language features-bb_celldefine Blackbox all verilog modules within `celldefine-bb_nonsynth Blackbox unsynthesizable modules in halsynth-bb_unbound_comp Ignore unbounded component for synthesis checks -bb_vital Blackbox design-units containing VITAL constructs -c Parse and elaborate, do NOT simulate-catcxx Positional option used to combine C++ sources-catcxxsize <size> Sets the CA TCXX partition size for large groups-categories List the categories and their descriptions-ccext <ext> Add extensions to C sources-check <arg> Specify checks and categories of checks+checkargs Check command-line arguments for validity-clean Deletes previous INCA_libs directory if is exists-comb_depth Enable Logic Depth calculation+compile Parse only, do NOT elaborate+controlassert+<arg> Specifies a file containing assertion controls-cpost Compile C files after elaboration+crshell Create shell files for import mode-cxxext <ext> Add extensions to C++ sources-D<macro> Define a macro for the C and C++ compiler-date Print date and time when each engine is invoked -debug Equivalent to -access +rw, Specman debug-debugscript <arg> Specify a debug script file name+define+<macro> Define a macro from command line-defineall <macro> Define macro from command line for all compilers +defparam+<arg> Redefine the value of a Verilog parameter-delay_mode <mode> Delay mode {Zero,PUnit,Unit,Path,Distr,None} +delay_mode_distributed Use distributed delay mode+delay_mode_path Use path delay mode+delay_mode_punit Use precision unit delay mode+delay_mode_unit Use unit delay mode+delay_mode_zero Use zero delay mode-design_facts_file <arg> Generate design facts during structural checks-design_info <arg> Design Information file-distcomp Option used to turn distributed compilation on-distcompargs,<args> Pass user specified argument to distributed comp -distcompjobs <number> Number of parallel distributed compiles to run-distplat <lsf> Specify underlying platform used for distrib comp -dpi Add appropriate build options for dpi designs-dpi_void_task Return value of export/import tasks will be VOID. +dut_prof+<file> Profiler report contains summary for design unit -dynamic Build a shared object for simulation-dynvhpi Enable user to create VHDL drivers at run time -efence Debug ncsim with Electric Fence.-efenceelab Debug ncelab with Electric Fence-end Terminate the list of files-extbind <arg> Bind file for binding SV/VHDL to SV/VHDL-F <filename> Scan file for args relative to file location-f <filename> Scan file for args relative to irun invocation-forceelab Force ncelab to execute-format <on|off> Enables shorter compiling messages from ncsc_run -g Turn on C debugging-gcc_vers <vers> 3.2.3 or 4.1 Linux only-gdb Run ncsim under gdb-gdbelab Run ncelab under gdb-gdbpath <pathToGdb> Use the provided gdb instead of what is shipped +genassert_synth_pragma Enable generating assertions from synth pragma -gnu Choose the GNU C and C++ compiler+gui Invoke the Graphical User Interface-h Print a minimal help message-hal Call hal instead of ncsim-halargs Pass options directly to hal-halsynth_detailcheck Perform detailed check on unsynthesizable modules+helpalias Show the different ways to enter an option+helpall Display all supported option+helpargs Print help for all the options in use+helpfileext Show all the file types and their extensions+helphelp Print out all the options controlling help-helpncverilog Show the ncverilog form of the options-helpshowmin Show the minimum characters required for dash opt +helpshowsubject Show all the subjects for -helpsubject+helpsubject<subject> Display help on the specified subject+helpverbose Show the verbose help text+helpwidth+<width> Set max width for help messages (def 89)-I<include dir> Directory to search for C/C++ include files+ieee1364 Report errors according to IEEE 1364 standards+import Prepare this verilog design for import to VHDL+incdir+<dirs> Specify directories to search for `include files-inst_top <arg> Specify the top-level instance for HAL analysis-iusld Prefix `ncroot`/tools/lib path to LD_LIBRARY_PATH -iusldno Disable the -iusld option-k <filename> Set key file name-L<lib dir> Directory to search for lib files-l <filename> Set logfile name-l<libname> archive or shared library to be linked in-level <arg> Specify levels in HAL analysis+libext+<ext> Specify extensions to be used for the -y search+liborder Library search rule (see documentation)+librescan Library search rule (see documentation)+libverbose Print verbose messages about instance binding-linksysc <dynamic|static> Use libsystemc.so (dynamic) or libsystemc_ar.a-lintpragma Process lint pragma in the design-loadcfc <lib> Dynamically load a CFC application-loadfmi <lib> Dynamically load an FMI library+loadpli1=<arg> Specify the PLI1 library_name:boot_routine(s)+loadsc+<lib> Specify SystemC lib to be dynamically loaded-loadvhpi <lib> Dynamically load a VHPI application+loadvpi=<arg> Specify the VPI library_name:boot_routines(s)-location Print the location of the installation-log_amsspice <logfile> Place amsspice output into the specified logfile-log_hal <logfile> Place the hal output into the specified logfile-logic_depth Enable Logic Depth calculation-loop_unroll_size <arg> Specify the loop unroll limit for halsynth+max_error_count+<arg> Specify the maximum number of errors processed+mixesc Handle escaped identifiers in imported model+multisource_int_delays Make interconnect timing be multisource capable+name+<name> Generate snapshot with specified name-native Use the native C and C++ compiler+nc64bit Invoke 64bit version+nca_ext+<ext> Override extensions for archive files+ncafile+<file> Specify an access file to be used+ncams Force Verilog-AMS and VHDL-AMS compilation +ncamsfastspice Enable Fast SPICE simulator (UltraSim)+ncamslic Check out an AMS license+ncamspartinfo+<file> Mixed-signal partition information+ncamsv_ext+<ext> Override extensions for Verilog-AMS sources+ncanalogcontrol+<arg> Specify analog simulation control file+ncanno_simtime Enable delay annotation at simulation time+ncappend_log Append output log to existing log-ncb_environment <arg> Specify environment file to be loaded by Ncbrowse-ncb_file <arg> File for Ncbrowse to load command line arguments-ncb_filter <arg> Filter for report generation by Ncbrowse-ncb_format <arg> Set the format of messages in the report-ncb_nodefaultenv Prevent Ncbrowse from using default environment-ncb_order <arg> Set the order in which items are shown-ncb_report <arg> Specify the report file to be created by Ncbrowse-ncb_sortby <arg> Specify a sort order to Ncbrowse for report+ncbatch Run simulation in batch mode, this is the default+ncbinding+ Force explicit submodule or unit L.C:v binding+ncc_ext+<ext> Override extensions for C sources+ncccargs Pass arguments to the C compiler+nccd_lexpragma Process preprocessor directive before lex pragmas +nccds_implicit_tmpdir+ Specify location for design data storage+nccds_implicit_tmponly Force tools to read design data only from tmpdir+nccdslib+<arg> Specify a cds.lib file to be used+ncchecktasks Check that all $tasks are built-in system tasks+ncchkdigdisp Perform digital net's discipline compatibility+ncconffile+<file_name> Generate a configuration file with the given name+ncconfflat Requires -CONFFILE, generate a VHDL flat config +ncconfhier Requires -CONFFILE, gen VHDL hierarchical config +ncconfname+<arg> Requires -CONFFILE, specify output config name +nccontrolrelax+<arg> Enable specific relaxed VHDL interpretation+nccovdesign+<string> Select coverage design name+nccovdut+<string> Select DUT for Coverage+nccoverage+<string> Enable coverage instrumentation+nccovfile+<file> Specify coverage instrumentation control file+nccovnomodeldump Disable coverage design database (model) dumping +nccovoverwrite Enable overwrite of coverage output files+nccovtest+<string> Select coverage test name+nccovworkdir+<string> Select coverage workdir+nccpg+<param> Assigns to all generics/params of this name+nccpp_ext+<ext> Override extensions for C++ sources+ncdebug Equivalent to -access +r+ncdefault_ext+<fileType> Override the default extension map+ncdesign_top+<design_top> Specifies top design unit for design-top comp+ncdisable_enht Disable enhanced timing features+ncdiscapf Disable the capital F input file mode+ncdiscipline+<disciplineName> Discipline to use for undisciplined digital wires +ncdisres+<resType> Set discipline resolution+ncdpiheader+<file> Create DPI header file for export functions+ncdresolution Sets discipline resolution to '-disres detailed'+ncdumpports_format+<arg> Specify EVCD format flag for $dumpports+ncdynlib_ext+<ext> Override extensions for dynamic library files+nce_ext+<ext> Override extensions for e sources-ncelab_args,<string> Pass arguments to elaborator (ncsc_run compat)+ncelab_compile requires -CONFILE, compile the configuration file +ncelabargs+<string> Pass arguments to elaborator+ncelabexe+<exe> Specify elaborator with statically linked PLI+ncelabfile File for generated elab options from import+ncendlib Terminate the list of library files+ncendstage Terminate the list of e stage files+ncerror+<arg> Increase the severity of a warning to an error+ncescapedname Print out escaped names in logfile+ncexit Exit simulation instead of issuing a TCL prompt +ncexpand Force expansion of all vector nets+ncextassertmsg Prints Extended Assert message Information+ncextend_tcheck_data_limit/<val> Relax timing check data limit+ncextend_tcheck_reference_limit/<val> Relax timing check reference limit+ncfatal+<arg> Increase the severity of a warn/error to fatal+ncgateloopwarn Enable potential zero-delay gate loop warning+ncgenafile+<file> Generate an access file for PLI and TCL+ncgeneric+<arg> Associate value with top-level generic+ncgnoforce Assigns the value if default value not found+ncgpg+<arg> Assigns to all generics/params of this name+ncgverbose Logs the gpg activity to the ncelab logfile+nchdlvar+<arg> Specify an hdl.var file to be used+nciereport Generate interface element report+ncignore_defexpr Ignore default expressions on variable,signal,...+ncinitbiopz Initialize boundary inout port to 'Z'+ncinitialize+<value> Initialize variables in the design+ncinitzero Enable zero initialization of time and integer+ncinput+<file> Read TCL commands from file+ncinsert+<arg> Specify string to be inserted after matching comp+ncintermod_path Make interconnects be multisource capable+nclexpragma Enable lexical pragma processing+nclib_binding Defaults back to the IUS5.4 binding search order+nclibcell Mark all cells with `celldefine+nclibdirname+<dir> Specify directory name to store created library+nclibdirpath+<path> Relative path where libraries should be created+nclibmap+<arg> Specify the library mapping file+nclibname+<name> Specify the name of a library to search+nclicq Queue simulation till license is available+nclinedebug Enable line debugging capabilities+nclist Produce a VHDL source listing in specified file+nclog_ncelab+<logfile> Place the ncelab output into specified logfile+nclog_ncsc_run+<logfile> Place the ncsc_run output into specified logfile+nclog_ncsim+<logfile> Place the ncsim output into the specified logfile+nclog_ncvhdl+<logfile> Place the ncvhdl output into specified logfile+nclog_ncvlog+<logfile> Place the ncvlog output into specified logfile+nclog_svpp+<logfile> Place the svpp output into specified logfile+nclps_assign_ft_buf Disable continuous assignment as feed through net+nclps_cpf+<file> Specify a CPF file for low power simulation+nclps_iso_off Turn off port isolation+nclps_logfile+<logfile> Specify a log file for low power simulation+nclps_off Turn off low power simulation+nclps_rtn_lock Lock the retained reg value+nclps_rtn_off Turn off state retention+nclps_simctrl_on Enable runtime control over low power simulation+nclps_stime+<time> Specify a time to start low power simulation+nclps_stl_off Turn off state loss+nclps_verbose+<level> Specify a level of information reporting+nclps_verify Enables automatic Low Power verification+nclps_vhdlpwron Brings back VHDL objects to a defined state+ncls_all Run ncls with the -all option+ncls_dep Run ncls with the -dep option+ncls_so Run ncls with the -source option+ncls_ss Run ncls with the -snapshot option+ncmakelib+<libpath[:logical]> Compile HDL files into specified library+ncmatchinst+<instance> Specify name of instance to match for -INSERT+ncmaxdelays Select maximum delays for simulation+ncmindelays Select minimum delays for simulation+ncmodelincdir+<dirlist> Specify a list of directories separated by :+ncmodelpath+<string> For Verilog-AMS, specify list of source files+ncmultview Allows selection of arch/config for binding+ncnamemap_mixgen Do name mapping from VHDL generics to Vlog params +ncno_cross_def_bind Suppress cross-language default binding+ncno_notifier Ignore notifiers in timing checks+ncno_sdfa_header Do not print the SDF annotation header+ncno_tchk_xgen Turn off X-generation in VITAL timing checks+ncno_vpd_msg Turn off VITAL pathdelay warnings+ncno_vpd_xgen Turn off X-generation in VITAL pathdelays+ncnobinding+ Skip instances of unit given as argument+ncnobuiltin Do not use any built-in IEEE operators+ncnocifcheck Disables constraint checking in VDA functions+ncnocopyright Suppress printing of copyright banner+ncnodeadcode Turn off dead code optimization+ncnoesp Disable edge-sensitive iopath delays+ncnoipd Ignore interconnect delays+ncnokey Suppress generation of the default keyfile+ncnolicpromote Do not use a mixed language license+ncnolicsuspend Disable suspending licenses for SIGTSTP+ncnoline Do not locate source line on errors+ncnolog Suppress generation of the default logfile+ncnomempack Do not pack memories+ncnomxindr Do not generate NOMXINDR error; split net instead +ncnontcglitch Suppress delayed net glitch suppression message+ncnoparamerr Do not flag setting undefined parameters as error+ncnopragmawarn Disable pragma related warning messages.+ncnoscynceverydelta Turn Delta cycle accuracy off+ncnosncomp Do not compile Specman input files+ncnosource Do not check source file timestamps in update+ncnospecview Do not invoke the Specview GUI+ncnostdout Turn off output to screen (terminal)+ncnotimezeroasrtmsg Suppress printing of time zero assert messages+ncnovitalaccl Turn off VITAL acceleration+ncnovitalcheck Suppress VITAL compliance checking+ncnowarn+<arg> Disable printing of the specified warning+ncnoxilinxaccl Turn off Xilinx acceleration+ncntc_level+<level> Select NTC algorithm 1 or 2 (default is 2)+ncntc_verbose Display verbose information about NTC process+ncntcnotchks Generate NTC delay while removing timing checks +nco_ext+<ext> Override extensions for object files+ncomicheckinglevel+<level> Specify OMI checking level {Min, Std, Max}+ncoverride_precision Override the timescale precision in Verilog+ncoverride_timescale Override the timescale directives in Verilog+ncpassword Prompt for sim passwd for SimVis walkup connect +ncpli_export Export symbols from loadpli, loadvpi+ncpliverbose Print information for PLI/VPI task registration+ncppdb+<dbase> Invoke the post-processing environment+ncppe Enter post-processing mode+ncpragma Enable pragma processing+ncpreserve Preserves resolution of single-driver sigs+ncprofile Generate a run-time profile of the design+ncprofoutput+<file> Specify an output file for profiling data+ncprofthread Allow threaded processes to profile+ncpromt Prompts to select arch/config/view for entity/mod +ncpropspath+<arg> Specify analog occurrence property database file +ncrandwarn Enable all SV randomize failure warnings+ncredmem Use reduced memory image size+ncreflib+<libpath[:logical]> Add the library to the list of libraries searched+ncrelax Enable relaxed VHDL interpretation+ncrun Begin simulation automatically+ncs_ext+<ext> Override extensions for assembly files+ncsavechoice+<arg> Specify name of file in which to save bindings+ncsaveenv Save the shell environment variables-ncsc_msgs <on|off> Tell ncsc to run ncsc messages on or off+ncscargs+<string> Pass arguments to ncsc_run+ncscope_discipline+<scope> Specify one scope based discipline+ncscparameter+<arg> Associates values with top level SystemC params +ncscprocessorder+<arg> Allow System C process order to vary+ncscscreateviewables Create ncsc_viewable objs inserted by ncsc_wizard +ncscynceverydelta+on|off Turn Delta cycle accuracy on+ncsdf_cmd_file+<file> Specify file of SDF annotation commands+ncsdf_nocheck_celltype Do not check the accuracy of CELLTYPE field+ncsdf_nortis Disable retain input sense+ncsdf_precision+<arg> Specify precision which SDF data will be modified +ncsdf_simtime Allow SDF annotation during simulation+ncsdf_verbose Include detailed information in SDF log file+ncsdf_worstcase_rounding Truncate SDF min delays, round max+ncsdfnowarn Do not report SDF warnings+ncseq_udp_delay+<arg> Specify a constant delay for sequential UDPs+ncsetdiscipline+<scope> Set discipline for a specified scope.+ncshare Reuse any available view with NCUID-ncsim_args,<string> Pass arguments to simulator. (ncsc_run compat)+ncsimargs+<string> Pass arguments to simulator+ncsimcompatible_ams+<arg> Specify compatibility language hspice or spectre +ncsimexe+<exe> Specify simulator with statically linked PLI+ncsimfile File for generated sim options from import+ncsmartlib Specifies multiple library compilation in OIC+ncsmartorder Order-independent compilation (OIC) for VHDL +ncsmartscript+<script> Specifies the OIC compilation script output file+ncsncompargs+<string> Pass arguments to "e" compiler+ncsndefine+<macro> Define an e macro+ncsnini+<ini> Specify Specman initialization file+ncsnload<file> Load e files before HDL access generation+ncsnpath+<path> Append the options value to SPECMAN_PA TH env var +ncsnprerun+<cmds> Execute Specman precommands before simulation+ncsnquit Run Specman compile in quiet mode+ncsnsc Specify SystemC agent for Specman+ncsnseed+<seed> Pass seed value to Specman+ncsnset+<arg> Set command to pass to Specman+ncsnshlib+<libpath> Use the provided precompiled e library+ncsnstage+<stagename> Compile e files as a staged compile+ncsnsv Specify SystemVerilog agent for Specman+ncsntimescale+<arg> Specify the time scale for specman delays+ncsnvhdl Specify VHDL agent for Specman+ncsnvlog Specify Verilog agent for Specman+ncsparsearray+<arg> Make 1-D array with more than <N> elements sparse+ncspectre_argfile_spp+<arg> Run Spectre parser with '-spp' option (spp on)+ncspectre_args+<arg> introduce options to be used by spectre+ncspectre_e Run Spectre parser with '-E' option+ncspectre_spp Run Spectre parser with '-spp' option+ncspecview Invoke the Specview Graphical User Interface+ncsprofile Generate a VHDL source profile+ncstacksize+<arg> Maximum size for the PLI stack+ncstatus Print out the runtime statistics after step+ncsvseed+<seed> Set SystemVerilog default RNG seed+nctfile+<file> Specify a timing file+nctimescale+<arg> Set default timescale on Verilog modules+nctop+<lib.cell:view> Specify the top-level unit+nctypdelays Select typical delays for simulation+ncuid+<arg> Specify a unique ID for this invocation+ncunbuffered Do not buffer output+ncupdate update SystemC design units used in the design+ncuptodate_messages Print module name for up-to-date modules+ncusearch+<arg> Specify the priority list of VHDL architectures+ncusechoice+<arg> Specify name of file from which to read bindings.+ncuseconf+<arg> Specify the priority list of VHDL configurations+ncuselicense+<arg> Colon delimited mnemonics to select license+ncuseview+<arg> Specify the priority list of Verilog views+ncv200x Enable VHDL200X and VHDL93 features+ncv93 Enable VHDL93 features+ncvcdextend Left-extend all vectors in VCD files+ncversion Print the version and exit-ncvhdl_args,<string> Pass arguments to VHDL parser (ncsc_run compat)+ncvhdl_ext+<ext> Override extensions for VHDL sources+ncvhdl_time_precision+<prec> Set default time precision for VHDL+ncvhdlargs+<string> Pass arguments to VHDL parser+ncview+<view> Set the view type for ncvlog compilation+ncvipdmax Select max delay value for VitalInterconnectDelay-ncvlog_args,<string> Pass arguments to Verilog parser(ncsc_run compat)+ncvlogargs+<string> Pass arguments to Verilog parser+ncvpicompat+<1364v1995|1364v2001|1364v2005|1800v2005> Specify the IEEE VPIcompatibility mode default+ncvpidmin Select Min delay value for VitalInterconnectDelay+ncvtimescale+<arg> Define initial timescale for command line files+ncxlifnone Emulate XL's ifnone SDF annotation implementation+ncxlstyle_units Display time values in XL style+nczparse+ Enable zparsing-no_design_facts Do not generate design facts during structural+no_pulse_msg Suppress e-pulse error message+no_show_canceled_e Do not filter negative pulses to E+no_tchk_msg Turn off timing check warnings+noassert Disable PSL and SystemVerilog assertions+noassert_synth_pragma Disable generating assertions from synth pragma+noautosdf Suppress automatic SDF annotation-nocheck <arg> checks and categories not to be performed-nodep Do not create dependencies-nodistcomp Option used to turn distributed compilation off-noedg Turn off the EDG front-end for NC-SC-noelab Disable the invocation of ncelab-nohalcheck Do not run lint checks (disable halcheck engine)-nohalstruct Do not run structural checks-nohalsynth Do not run synthesizability checks+nolibcell Disable tagging library modules as cells+noneg_tchk Ignore negative numbers for SETUPHOLD & RECREM +nontc_warn Suppress NTC non-convergence warnings-nopragmas Ignore HDL pragmas such as translate_off-noremovescratch Do not remove the sub scratch directory for sim-norundbg When attaching gdb to the exec do not execute run-noscv Turn off linking of the CVE and SCV libraries+nospecify Suppress timing information from specify blocks+notimingchecks Do not execute timing checks+noupdate Disable the default update mode-novic Turn on linking of the VIC libraries+ntc_neglim Move negative limit of invalid NTC windows+ntc_poslim Move positive limit of invalid NTC window+ntc_tolerance+<arg> Specify tolerance value for NTC timing window+O0 Optimize to level 0+O1 Optimize to level 1+O2 Optimize to level 2+O3 Optimize to level 3-objext <ext> Add extensions to object files+overwrite Overwrite existing config file of same name-ovm Turn on support for the OVM library-ovmhome <dir> Location to look for the OVM install+partialdesign Allow elaboration of partially-defined design+pathpulse Set pulse limits according to PATHPULSE$-pathtran Kill pathdelays touching multiple tran gates+plimapfile=<arg> Specify VPI and/or PLI mapping file(s)+plinooptwarn Suppress PLI messages caused by limited access+plinowarn Do not print PLI warning and error messages-precompiled_headers <on|off> Use precompiled headers. Only with gcc 4.1-printspecs Have ncsc_run print out the spec file+profile_sc+<file> File containing PSL/Covergroup verification code+profile_vhdl+<file> File containing PSL/Covergroup verification code+propdir+<dir> Specify directory to consider when searching+propext+<ext> Specify extensions to consider when searching+propfile+<file> File containing PSL/Covergroup verification code-propfile <file> Unsupported use -propfile_vlog|vhdl|sc+propssc_ext+<ext> Specify extensions to consider when searching+propvhdl_ext+<ext> Specify extensions to consider when searching+pulse_e/<arg> Set percentage of delay for pulse error limit+pulse_e_style_ondetect Use on-detect filtering of error pulses+pulse_e_style_onevent Use on-event filtering of error pulses+pulse_int_e/<arg> Set percent delay for pulse error limit+pulse_int_r/<arg> Set percent delay for pulse reject limit+pulse_r/<arg> Set percentage of delay for pulse error limit-purecov Instrument ncsim code with purecov-purecovelab Instrument ncelab with purecov-purify Instrument ncsim code with purify-purifyelab Instrument ncelab with purify-Q Quiet mode, with banner and command line-q Suppress informational messages(i.e., Quiet mode) -quantify Instrument ncsim code with quantify-quantifyelab Instrument ncelab with quantify-R Simulate using last snapshot generated-r <snapshot name> Force simulation using snapshot-races Run zero-delay race condition checks-read_lib <arg> Enable DFT, scanchain check using *.lib synthesis-read_tlf <arg> Enable DFT, scanchain check using *.tlf synthesis+rmkeyword+<keyword> Specify list of keywords to be removed-rulefile <arg> file for loading definitions of categories checks-rulelib <arg> A shared library containing user-defined checks-rules_checked Print details of the checks-rules_list Print all the rules present in HAL-s Load snapshot and go to the interactive prompt。

提高NCverilog仿真效率技巧

提高NC-Verilog仿真效率的技巧(转)上一篇/ 下一篇 2010-04-25 22:43:50查看( 1374 ) / 评论( 2 ) / 评分( 0 / 0 )本文回顾了一些NC-Verilog的命令行选项,并说明这些选项如何影响仿真效率。

同时,我们也展示了一些技巧,以帮助用户的NC- Verilog在最大效率下仿真一个设计和测试平台。

文中的命令行选项语法采用单步启动的方式(ncverilog +<options>),这些选项也适合多步启动模式(ncvlog, ncelab, 或ncsim)。

安装最新发布的软件首先确认你是否安装了最新的Cadence LDV版本。

自动1996年发布第一版NC-Verilog以来,我们的研发队伍一直把仿真器的仿真效率作为重点来研究。

在后来推出的新版本里,不断按各种设计风格优化仿真器,因此使用最新版本是最有利的。

直到2002年2月,最新版本是LDV 3.4(s1)。

使用NC-Verilog内置的profilerNC-Verilog在仿真引擎内开发了一个profiler工具。

该工具每秒中断仿真器100次,并将终端时的结构记录下来,生成一个日志文件。

日志文件里列出了被中断次数最多的模块、代码行和结构类型。

这些信息可以帮助你诊断是哪些代码或模块在仿真时耗费了最多的时间。

通过修改这些模块,就能提升仿真效率。

Profiler功能很容易启动,并对仿真只产生非常小的影响。

% ncverilog +ncprofile <other_options> or% ncsim –profile snapshot_name <other_options>在仿真结束时,profiler会创建一个日志文件(ncprof.out),文件里列出了profile运行的细节。

关于如何利用profiler日志文件,可参考Cadence在线文档(Cadence NC-Verilog Simulator Help, Version 3.4, Chapter 14)。

Ncverilog 命令使用详解

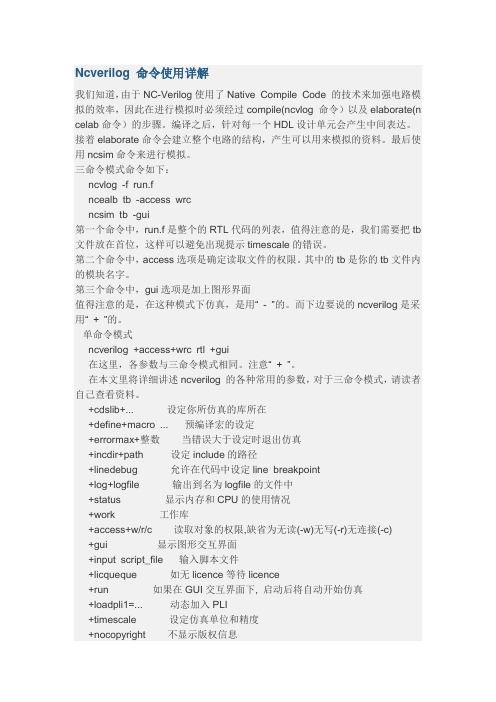

Ncverilog 命令使用详解我们知道,由于NC-Verilog使用了Native Compile Code 的技术来加强电路模拟的效率,因此在进行模拟时必须经过compile(ncvlog 命令)以及elaborate(n celab命令)的步骤。

编译之后,针对每一个HDL设计单元会产生中间表达。

接着elaborate命令会建立整个电路的结构,产生可以用来模拟的资料。

最后使用ncsim命令来进行模拟。

三命令模式命令如下:ncvlog -f run.fncealb tb -access wrcncsim tb -gui第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb 文件放在首位,这样可以避免出现提示timescale的错误。

第二个命令中,access选项是确定读取文件的权限。

其中的tb是你的tb文件内的模块名字。

第三个命令中,gui选项是加上图形界面值得注意的是,在这种模式下仿真,是用“ - ”的。

而下边要说的ncverilog是采用“ + ”的。

单命令模式ncverilog +access+wrc rtl +gui在这里,各参数与三命令模式相同。

注意“ + ”。

在本文里将详细讲述ncverilog 的各种常用的参数,对于三命令模式,请读者自己查看资料。

+cdslib+... 设定你所仿真的库所在+define+macro ... 预编译宏的设定+errormax+整数当错误大于设定时退出仿真+incdir+path 设定include的路径+linedebug 允许在代码中设定line breakpoint+log+logfile 输出到名为logfile的文件中+status 显示内存和CPU的使用情况+work 工作库+access+w/r/c 读取对象的权限,缺省为无读(-w)无写(-r)无连接(-c)+gui 显示图形交互界面+input script_file 输入脚本文件+licqueque 如无licence等待licence+run 如果在GUI交互界面下, 启动后将自动开始仿真+loadpli1=... 动态加入PLI+timescale 设定仿真单位和精度+nocopyright 不显示版权信息。

verilog语法详解

verilog语法详解Verilog语法是一种硬件描述语言,用于设计数字电路。

它可以实现逻辑功能和控制硬件。

以下是Verilog语法的详细解释:1. 模块(Module):模块是Verilog语言中最基本的单元。

模块定义了模块内部的数据类型和信号。

模块可以实现任何逻辑功能,并且可以同其他模块组合使用。

2. 输入(Input)和输出(Output):Verilog模块通过输入和输出端口与其他模块进行通信。

输入是模块接收的数据,而输出是模块输出的数据。

使用“input”和“output”关键字来定义输入和输出。

3. 线路(Wire):线路是Verilog模块中的一种数据类型。

它可以是单个位或多个位。

用“wire”关键字定义线路。

4. 寄存器(Register):寄存器是一种Verilog模块中的数据类型,用于存储数据。

寄存器可以是单个位或多个位。

使用“reg”关键字定义寄存器。

5. 运算符(Operator):Verilog支持各种运算符,包括算术、逻辑和比较运算符。

它们用于执行各种操作,如加、减、乘、除、与、或、非、异或等。

6. 语句(Statement):Verilog中的语句用于控制程序流程。

语句可以是条件语句、循环语句、分支语句等。

常用的语句包括“if”、“else”、“while”、“for”等。

7. 实例(Instance):实例是一个模块的具体实现。

使用“module name instancename()”语句来实例化一个模块。

8. 多模块组合:Verilog允许多个模块组合在一起实现更复杂的功能。

这些模块可以通过实例化彼此来连接。

以上是Verilog语法的详细解释,掌握这些基本概念是学习Verilog的关键。

西安电子科技大学NCverilog教程

在上述步骤之后,会生成一个你的设计对应的snapshot,仿真 就是针对这个Snapshot进行的。如图示,选中该文件,点击 仿真按钮

之后就启动了simulator,会弹出2个窗口 : 设计浏览器(Design Browser)和 控制窗口(Console window)

设计浏览器(Design Browser)

选择多步模式 Multiple step

选择creat cds.lib file,弹出第二个对 话框,save,在新对话框中点击ok, 之后在最初的对话框中点击Ok。

nclaunch的主窗口: 左边的窗口中显示了 当前目录下的所有文 件,在编译和描述后 会在右边显示设计的 库。

在在仿真你的设计以前,必须用编译器编译源文件,并且 用描述器(elaborator)把设计描述成snapshot的形式。 NCLaunch的主窗口让你可以连接你编译和描述设计所需 要的工具

❖ Simulate模式 在Simulate模式下你可以实时的看到仿真的数据。也就是说, 你可以在仿真的过程中就进行数据的分析。你可以通过对设 计设置断点和分步来达到控制仿真的。

控制台窗口 Console Window 源浏览器 Source Browser 设计浏览器 Design Browser 循环阅读器 Cycle Viewer 原理图追踪 Schematic Tracer 信号流浏览器 Signal Flow

现在要描述你的设计: 要展开库(worklib), 选择顶层单元(也就是 测试中的module), 然后选择描述按钮 (elabrate )

但是在这之前要设置 参数,选中module后 选择toolsElaborator 进行设置。

设置参数时注意将Access Visibility按 钮选中并且它的值是All,这个选项意味 着全部存取(读,写,连接探测)来仿 真目标,这样就可以在仿真的数据库里 面探测目标和范围,调试你的设计。 由于不是所有的代码都加了时间,为防 止报错在此处加上时间。 然后点击ok即可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Ncverilog 命令使用详解

我们知道,由于NC-Verilog使用了Native Compile Code 的技术来加强电路模拟的效率,因此在进行模拟时必须经过compile(ncvlog 命令)以及elaborate(n celab命令)的步骤。

编译之后,针对每一个HDL设计单元会产生中间表达。

接着elaborate命令会建立整个电路的结构,产生可以用来模拟的资料。

最后使用ncsim命令来进行模拟。

三命令模式命令如下:

ncvlog -f run.f

ncealb tb -access wrc

ncsim tb -gui

第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb 文件放在首位,这样可以避免出现提示timescale的错误。

第二个命令中,access选项是确定读取文件的权限。

其中的tb是你的tb文件内的模块名字。

第三个命令中,gui选项是加上图形界面

值得注意的是,在这种模式下仿真,是用“ - ”的。

而下边要说的ncverilog是采用“ + ”的。

单命令模式

ncverilog +access+wrc rtl +gui

在这里,各参数与三命令模式相同。

注意“ + ”。

在本文里将详细讲述ncverilog 的各种常用的参数,对于三命令模式,请读者自己查看资料。

+cdslib+... 设定你所仿真的库所在

+define+macro ... 预编译宏的设定

+errormax+整数当错误大于设定时退出仿真

+incdir+path 设定include的路径

+linedebug 允许在代码中设定line breakpoint

+log+logfile 输出到名为logfile的文件中

+status 显示内存和CPU的使用情况

+work 工作库

+access+w/r/c 读取对象的权限,缺省为无读(-w)无写(-r)无连接(-c)

+gui 显示图形交互界面

+input script_file 输入脚本文件

+licqueque 如无licence等待licence

+run 如果在GUI交互界面下, 启动后将自动开始仿真

+loadpli1=... 动态加入PLI

+timescale 设定仿真单位和精度

+nocopyright 不显示版权信息。