可逆计数器实验报告

VHDL实验报告03137

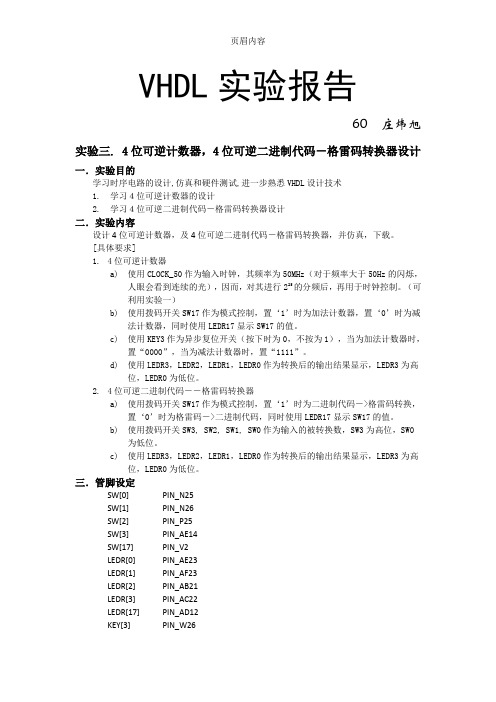

VHDL实验报告60 庄炜旭实验三. 4位可逆计数器,4位可逆二进制代码-格雷码转换器设计一.实验目的学习时序电路的设计,仿真和硬件测试,进一步熟悉VHDL设计技术1. 学习4位可逆计数器的设计2. 学习4位可逆二进制代码-格雷码转换器设计二.实验内容设计4位可逆计数器,及4位可逆二进制代码-格雷码转换器,并仿真,下载。

[具体要求]1.4位可逆计数器a)使用CLOCK_50作为输入时钟,其频率为50MHz(对于频率大于50Hz的闪烁,人眼会看到连续的光),因而,对其进行225的分频后,再用于时钟控制。

(可利用实验一)b)使用拨码开关SW17作为模式控制,置‘1’时为加法计数器,置‘0’时为减法计数器,同时使用LEDR17显示SW17的值。

c)使用KEY3作为异步复位开关(按下时为0,不按为1),当为加法计数器时,置“0000”,当为减法计数器时,置“1111”。

d)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

2.4位可逆二进制代码――格雷码转换器a)使用拨码开关SW17作为模式控制,置‘1’时为二进制代码―>格雷码转换,置‘0’时为格雷码―>二进制代码,同时使用LEDR17显示SW17的值。

b)使用拨码开关SW3, SW2, SW1, SW0作为输入的被转换数,SW3为高位,SW0为低位。

c)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

三.管脚设定SW[0]PIN_N25SW[1]PIN_N26SW[2]PIN_P25SW[3] PIN_AE14SW[17] PIN_V2LEDR[0] PIN_AE23LEDR[1] PIN_AF23LEDR[2] PIN_AB21LEDR[3] PIN_AC22LEDR[17] PIN_AD12KEY[3] PIN_W26CLOCK_50 PIN_N2四.相关知识二进制代码与格雷码相互转换格雷码(Gray Code,简称G码)是典型的循环码,它是由二进制码(Binary,简称 B 码)导出的。

设计一个异步四位二进制计数器实验报告捞金版

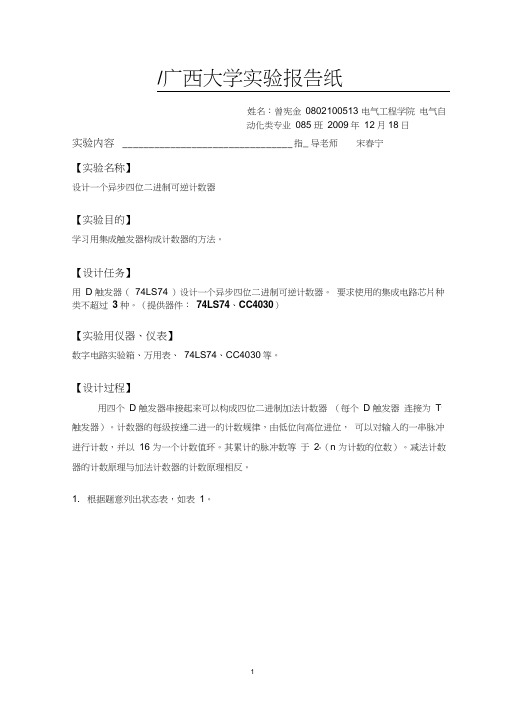

/广西大学实验报告纸姓名:曾宪金0802100513 电气工程学院电气自动化类专业085 班2009年12月18日实验内容________________________________ 指_ 导老师宋春宁【实验名称】设计一个异步四位二进制可逆计数器【实验目的】学习用集成触发器构成计数器的方法。

【设计任务】用D 触发器(74LS74 )设计一个异步四位二进制可逆计数器。

要求使用的集成电路芯片种类不超过3 种。

(提供器件:74LS74、CC4030)【实验用仪器、仪表】数字电路实验箱、万用表、74LS74、CC4030等。

【设计过程】用四个D 触发器串接起来可以构成四位二进制加法计数器(每个D 触发器连接为T'触发器)。

计数器的每级按逢二进一的计数规律,由低位向高位进位,可以对输入的一串脉冲进行计数,并以16 为一个计数值环。

其累计的脉冲数等于2n(n 为计数的位数)。

减法计数器的计数原理与加法计数器的计数原理相反。

1. 根据题意列出状态表,如表1。

令A=0 时,计数器为加法计数器;A=1 时,计数器为减法计数器12. 根据状态表画卡诺图确定各触发器的时钟信号方程:由卡诺图化简可得各触发器的时钟信号方程为:CP3 AQ2n AQ2n A Q2nCP2 AQ1n AQ1n A Q1nCP1 AQ0n AQ0n A Q0nCP0 为输入脉冲信号。

各触发器的输出信号为:各触发器的激励方程为:CP3 Q2n A0101110CP1 Q0n01A001110Q2n 1D2 Q2nQ3、Q2、Q1、Q0Q1n 1D1 Q1n各触发器的状态方程为:Q 3n 1D 3CP 3 Q 3nCP 3 Q 3nCP 3 Q 3nCP 3Q 2n 1D 2CP 2 Q 2nCP 2 Q 2nCP 2 Q 2nCP 2Q 1n 1D 1CP 1 Q 1nCP 1 Q 1nCP 1 Q 1nCP 1Q 0n 1D 0CP 0 Q 0nCP 0 Q 0nCP 0 Q 0nCP 0作状态转换图:Q 3Q 2Q 1Q0000 01 0001 01 0010 10 001111 1110作逻辑电路图:Q3Q Q10 111111 01 1 01010 10 1001 0 10000 0101010111101 1 0 011 011100 0 10110 1 0111运用EWB5.0仿真平台仿真电路:该电路已在EWB5.0平台仿真通过。

加减可逆计数器实训报告

一、实训目的本次加减可逆计数器实训旨在通过实际操作,加深对数字电路原理和计数器设计方法的理解,提高动手能力和实践技能。

通过本次实训,使学生掌握加减可逆计数器的设计原理、电路实现方法,并能够熟练运用相关工具进行电路仿真和测试。

二、实训环境1. 实验设备:数字电路实验箱、示波器、万用表、计算机等。

2. 实验软件:Multisim、Proteus等电路仿真软件。

三、实训原理加减可逆计数器是一种能够实现加法、减法、保持和异步清零的计数器。

它由加法计数器、减法计数器、保持电路和异步清零电路组成。

在加法计数器中,计数器的状态每增加1,输出端的状态也相应增加1;在减法计数器中,计数器的状态每减少1,输出端的状态也相应减少1;保持电路使计数器在需要保持状态时保持原有状态;异步清零电路可以在任意时刻使计数器清零。

四、实训过程1. 设计加减可逆计数器电路原理图。

2. 利用Multisim或Proteus等电路仿真软件搭建加减可逆计数器电路。

3. 设置电路参数,进行仿真测试。

4. 分析仿真结果,验证电路功能。

5. 利用数字电路实验箱搭建实物电路。

6. 测试实物电路,验证电路功能。

五、实训结果与分析1. 仿真结果分析通过仿真测试,验证了加减可逆计数器电路的功能。

在加法计数模式下,计数器能够实现从0到9的计数;在减法计数模式下,计数器能够实现从9到0的计数;在保持模式下,计数器能够保持原有状态;在异步清零模式下,计数器能够快速清零。

2. 实物电路测试结果分析利用数字电路实验箱搭建的实物电路,经过测试,验证了电路的功能。

在加法计数模式下,计数器能够实现从0到9的计数;在减法计数模式下,计数器能够实现从9到0的计数;在保持模式下,计数器能够保持原有状态;在异步清零模式下,计数器能够快速清零。

六、实训总结1. 通过本次实训,加深了对数字电路原理和计数器设计方法的理解。

2. 提高了动手能力和实践技能,学会了使用电路仿真软件进行电路设计和测试。

可逆十进制计数电路功能测试实验报告

可逆十进制计数电路功能测试实验报告可逆十进制计数电路功能测试实验报告一、引言可逆十进制计数电路是一种能够实现在十进制数字范围内进行计数的电路。

它具有多种应用,例如在时钟频率分频器、数据传输和存储器等领域中。

本实验旨在测试可逆十进制计数电路的功能,并验证其在不同输入情况下的正确性。

二、实验目的1. 理解可逆十进制计数电路的工作原理;2. 测试可逆十进制计数电路在不同输入情况下的输出结果;3. 验证可逆十进制计数电路的正确性。

三、实验装置与材料1. 实验装置:可逆十进制计数电路模块、示波器、信号发生器;2. 实验材料:连接线、电源线。

四、实验步骤步骤1:将可逆十进制计数电路模块与示波器和信号发生器连接,确保连接正确稳定。

步骤2:设置信号发生器为方波输出,并调整频率为100Hz。

步骤3:观察示波器上的输出信号,并记录每个周期内的数字变化情况。

步骤4:重复步骤2和步骤3,分别设置不同频率的方波输出,例如200Hz、500Hz等。

步骤5:通过改变信号发生器的输出波形,例如三角波、正弦波等,测试可逆十进制计数电路在不同输入情况下的输出结果。

五、实验结果与分析在本实验中,我们观察了可逆十进制计数电路在不同输入情况下的输出结果,并记录了每个周期内的数字变化情况。

以下是实验结果的总结与分析:1. 方波输入:当信号发生器以100Hz的方波频率输出时,可逆十进制计数电路按照从0到9的顺序进行计数。

每个数字在一个周期内持续显示,并在下一个周期开始时自动切换到下一个数字。

这表明可逆十进制计数电路能够正确地进行十进制计数。

2. 不同频率方波输入:我们通过改变信号发生器的方波频率为200Hz和500Hz进行测试。

结果显示,可逆十进制计数电路仍然能够按照从0到9的顺序进行计数,并且数字切换速度加快。

这表明可逆十进制计数电路对于不同频率的输入具有较好的适应性。

3. 其他波形输入:当信号发生器以三角波、正弦波等非方波形式输出时,可逆十进制计数电路仍然能够正确地进行计数。

实验二异步复位十进制可逆计数器

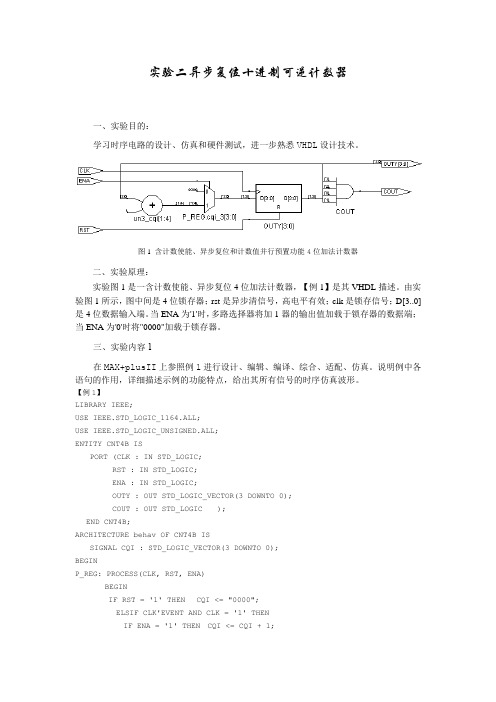

实验二异步复位十进制可逆计数器一、实验目的:学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

图1 含计数使能、异步复位和计数值并行预置功能4位加法计数器二、实验原理:实验图1是一含计数使能、异步复位4位加法计数器,【例1】是其VHDL描述。

由实验图1所示,图中间是4位锁存器;rst是异步清信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端。

当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

三、实验内容1在MAX+plusII上参照例1进行设计、编辑、编译、综合、适配、仿真。

说明例中各语句的作用,详细描述示例的功能特点,给出其所有信号的时序仿真波形。

【例1】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4B ISPORT (CLK : IN STD_LOGIC;RST : IN STD_LOGIC;ENA : IN STD_LOGIC;OUTY : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT : OUT STD_LOGIC );END CNT4B;ARCHITECTURE behav OF CNT4B ISSIGNAL CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINP_REG: PROCESS(CLK, RST, ENA)BEGINIF RST = '1' THEN CQI <= "0000";ELSIF CLK'EVENT AND CLK = '1' THENIF ENA = '1' THEN CQI <= CQI + 1;END IF;END IF;OUTY <= CQI ;END PROCESS P_REG ; --进位输出COUT<=CQI(0) AND CQI(1) AND CQI(2) AND CQI(3);END behav;四、实验内容2:将实验内容1中的计数器改为十进制可逆计数器, 进行设计、编辑、编译、综合、适配、仿真;并进行引脚锁定以及硬件下载测试。

12单片机可预置可逆4位计数器实验-5页精选文档

12.可预置可逆4位计数器1.实验任务利用AT89S51单片机的P1.0-P1.3接四个发光二极管L1-L4,用来指示当前计数的数据;用P1.4-P1.7作为预置数据的输入端,接四个拨动开关K1-K4,用P3.6/WR和P3.7/RD端口接两个轻触开关,用来作加计数和减计数开关。

具体的电路原理图如下图所示2.电路原理图图4.12.13.系统板上硬件连线(1.把“单片机系统”区域中的P1.0-P1.3端口用8芯排线连接到“八路发光二极管指示模块”区域中的L1-L4上;要求:P1.0对应着L1,P1.1对应着L2,P1.2对应着L3,P1.3对应着L4;(2.把“单片机系统”区域中的P3.0/RXD,P3.1/TXD,P3.2/INT0,P3.3/INT1用导线连接到“四路拨动开关”区域中的K1-K4上;(3.把“单片机系统”区域中的P3.6/WR,P3.7/RD用导线连接到“独立式键盘”区域中的SP1和SP2上;4.程序设计内容(1.两个独立式按键识别的处理过程;(2.预置初值读取的问题(3.LED输出指示5.程序框图图4.12.2 6.汇编源程序COUNT EQU 30HORG 00HSTART: MOV A,P3ANL A,#0FHMOV COUNT,AMOV P1,ASK2: JB P3.6,SK1LCALL DELY10MSJB P3.6,SK1INC COUNTMOV A,COUNTCJNE A,#16,NEXT MOV A,P3ANL A,#0FHMOV COUNT,A NEXT: MOV P1,AWAIT: JNB P3.6,WAIT LJMP SK2SK1: JB P3.7,SK2LCALL DELY10MSJB P3.7,SK2DEC COUNTMOV A,COUNTCJNE A,#0FFH,NEX MOV A,P3ANL A,#0FHMOV COUNT,A NEX: MOV P1,AWAIT2: JNB P3.7,WAIT2 LJMP SK2DELY10MS: MOV R6,#20MOV R7,#248D1: DJNZ R7,$DJNZ R6,D1RETEND7.C语言源程序#include <AT89X51.H>unsigned char curcount;void delay10ms(void)unsigned char i,j;for(i=20;i>0;i--)for(j=248;j>0;j--);void main(void)curcount=P3 & 0x0f;P1=~curcount;while(1)if(P3_6==0)delay10ms();if(P3_6==0)if(curcount>=15) curcount=15; elsecurcount++; P1=~curcount;while(P3_6==0); if(P3_7==0)delay10ms();if(P3_7==0)if(curcount<=0) curcount=0; elsecurcount--; P1=~curcount;while(P3_7==0);。

实验二 同步模4可逆计数器

实验二同步模4可逆计数器

实验目的:1.掌握同步时序逻辑电路的设计方法。

2.加深对同步和时序两个概念的理解。

实验条件:

1.操作系统为WINDOWS 2000的计算机一台

2.Multisim 2001电子线路仿真软件一套

实验组件:双D触发器 74LS74 1片,三输入三与非门74LS10 1片,二输入二与非门74LS00 1片,二输入四异或门74LS86 1片

实验内容:

利用D触发器设计一个可逆模4计数器。

附:(选做)

利用JK触发器设计一个可逆模4计数器。

实验要求:

1.看懂光盘中的实验过程,并在Multisim 2001中使用逻辑分析仪验证结果.

2.使用方波发生器5V 1KHZ(器件库—电源—CLOCK SOURCE)提供脉冲,灯泡(器件库—指示器件—LAMP),开关(器件库—BASIC—SWITCH—SPDT)。

3.根据实验内容,列出真值表、逻辑函数式,并在下周三上交实验报告。

附:74LS10引脚图

74LS74的逻辑符号。

实验九可逆计数器的功能测试及应用

实验九可逆计数器的功能测试及应用实验内容:1.测试74LS190和73LS191的逻辑功能,并用数码管显示,验证结果是否正确,分别画出各单元的电路图,写出各自的状态转换图。

74LS190测试电路如下图所示:(图示为加法计数状态)结果:电路能够实现十进制同步加减计数功能,当U’/D=0时,进行加法计数,在跳到0时,RCO出现短暂低电平状态,所接灯泡熄灭,MAX/MIN出现短暂高电平状态,灯发亮。

当U’/D=1时,实现减法计数,在由跳到0时,RCO短暂低电平状态所接灯泡短暂熄灭,MAX/MIN 短暂高电平状态,灯发亮。

其余时候RCO均处于高电平状态,灯亮,MAX/MIN均处于低电平状态,灯灭。

状态转换图:(顺时针方向为加法计数,逆时针方向为减法计数)74LS191测试电路如下:(图示为减法计数状态)结果:电路能够实现二进制同步加减计数功能,当U’/D=0时,进行加法计数,在跳到0时,RCO出现短暂低电平状态所接灯泡短暂熄灭,MAX/MIN出现短暂高电平状态灯短暂发亮。

当U’/D=1时,实现减法计数,在由跳到0时,RCO出现短暂低电平状态所接灯泡短暂熄灭,MAX/MIN出现短暂高电平状态,灯短暂发亮。

状态转换图:(顺时针方向为加法计数,逆时针方向为减法计数)2.测试74LS192和74LS193的逻辑功能,并用数码管显示,验证是否正确。

画出测试电路图。

74LS192测试电路:(图示为加法计数状态)结果:74LS192为双时钟同步十进制可逆计数器。

当UP接脉冲,DOWN 接1时,电路工作在加法计数状态,CO在计数跳到0时出现短暂的低电平状态,灯泡熄灭。

当UP接1,DOWN接脉冲时,电路工作在减法计数状态,BO在计数跳至0时出现短暂的低电平状态灯泡熄灭。

其余时候BO、CO均处于高电平,灯泡亮。

74LS193测试电路:(图示为减法计数状态)结果:74LS193为双时钟同步二进制可逆计数器。

当UP接脉冲,DOWN 接1时,电路工作在加法计数状态,CO在计数跳到0时出现短暂的低电平状态,灯泡熄灭。

实验九-可逆计数器的功能测试及应用电路

实验九可逆计数器的功能测试及应用电路实验目的:(1)掌握可逆计数器74LS191、74LS191、74LS192、74LS193的逻辑功能及使用方法。

(2)熟悉可逆计数器实现任意进制的数码倒计时电路的工作原理。

实验仪器与器件:实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台.74LS191、74LS191、74LS191或74HC48、74LS00和74LS04。

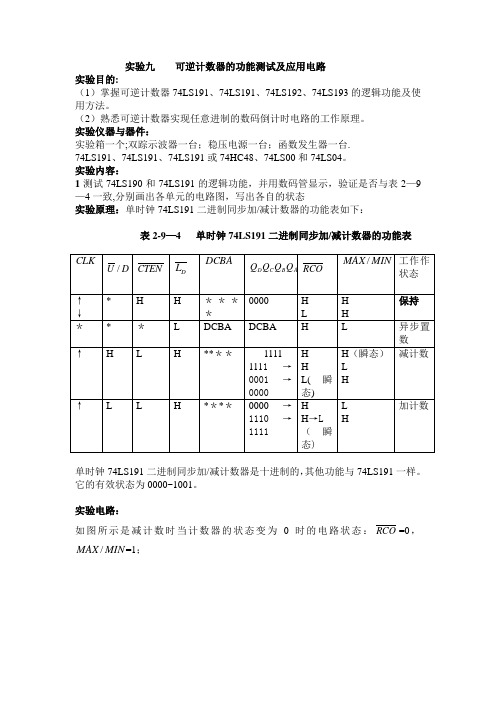

实验内容:1测试74LS190和74LS191的逻辑功能,并用数码管显示,验证是否与表2—9—4一致,分别画出各单元的电路图,写出各自的状态实验原理:单时钟74LS191二进制同步加/减计数器的功能表如下:表2-9—4 单时钟74LS191二进制同步加/减计数器的功能表单时钟74LS191二进制同步加/减计数器是十进制的,其他功能与74LS191一样。

它的有效状态为0000~1001。

实验电路:如图所示是减计数时当计数器的状态变为0时的电路状态:RCO=0,MAX/=1;MIN实验现象与结果:该结果是当CTEN =0,D L =1,D U /=1时,A B C D Q Q Q Q 的 波形图;该结果是当CTEN =0,D L =1,D U /=1时, RCO 与MIN MAX /的波形图需要说明的是:当CTEN=DL=1时,电路保持原来的状态。

2测试74LS192和74LS193的逻辑功能,并用数码管显示,验证是否与表2-9—3及2—9—5一致。

画出测试电路图。

实验原理:双时钟74LS192同步十进制可逆计数器的功能表如下表所示,74LS192是十进制计数器。

表2—9—3双时钟74LS192同步十进制可逆计数器的功能表输入输出工作状态U CP UPDCPDOWNCLRDLDCBAABCDQQQQUTCDTC**H H ****0000 H H 异步清零** L L 1001 1001 H H 异步置数H ↑L H ****1001→0001→0000HHHL减法计数↑H L H **** 0000→1000→1001HLHH加法计数双时钟74LS193二进制同步加/减法计数器的功能表如下表所示,74LS193是一个十六进制的计数器。

可逆计数器实验报告

西南民族大学

学生实验报告

20 17 ------2018学年第 2 学期

课程名称:可编程逻辑器件及应用实验

任课教师:

学院:电气信息工程学院专业:年级:班级:学号:姓名:同组人:

if(Q==0) Q<=4’hf)

else Q<=Q-1;

end

endcase

end

endmodule

4)编辑输入波形数据,选择File—New命令,在New窗口中选择Vector Waveform file选项,单击OK,即出现空白波形编辑器。

5)设置仿真器参数,选择Assignment—Settings命令,在Settings窗口下选择Category—Simulation Settings。

在右侧的Simulation mode下拉列表框中选择Timing,即选择时序仿真,并选择仿真激励文件名fdiv0.vwf。

选择Simulation period 栏,确认选中了“Run simulation until all vector stimuli are used ”

6)启动仿真器,选择Processing—starsimulation,启动仿真,直到出现Simulation was successful,仿真结束。

7)在Simulation report中观察仿真结果。

如图:

4、分析讨论;。

8位可逆循环计数器

一、概述随着科技的日益进步,计数器得到了越来越广泛的应用,发展的也越快。

在数字系统中使用的最多时序逻辑电路要算是计数器了。

计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

本次实验的思路主要是设计一个8位可逆循环计数器,该计数器加计数到最大值(11111111)时输出一个周期的高电平信号(表示计数器达到最大值)并自动变为减计数,减计数到最小值(00000000)是输出一个周期的高电平信号(表示计数器达到最小值)并自动变为加计数。

如此循环往复。

要求设计层次化。

实验中用到的器件主要包括74LS191D、7段显示器、555组成的多谐振荡电路和多个门电路。

二、方案论证为了实现本实验的主要内容,首先要利用555定时器制成一个多谐振荡电路作为时间脉冲为同步十六进制加/减计数器74LS191D提供时间信号,并且要将多谐振荡电路的频率设为HZ,即周期为秒。

因为要实现计数器加到最大值(11111111)(或最小值(00000000))时输出一个周期的高电平信号,故需要加入多个门电路和灯泡,同时要求加数器数器自动变为减数器(或减数器自动变为加数器)故利用T触发器实现该功能,并能够实现循环往复的功能。

其原理框图如图1所示。

图1 电路的原理框图脉冲信号直流稳压电源滤波、整波555时钟信号脉冲电路74LS191D十六进制计数器74LS191D十六进制计数器数码管显示输出一个周期的高电平信号计数器自动的由加数器转换为减数器或相反三、电路设计1.直流稳压电源电路直流稳压电源包括电源电容电阻;其组成电路如图2所示。

图2 直流稳压电源电路2. 时钟信号脉冲电路555定时器是一种多用途的数字—模拟混合电路,利用它能极方便的构成多谐振荡器,且成本低,只需外接几个电阻、电容,就可以实现多谐振荡来产生时钟信号用来计时。

电容C2通过R3和R4开始充电,充到1/3Vcc时,输出上升为高电平,电容继续充电,直到2/3Vcc时,输出又降为低电平,电容向R3放电,放到1/3Vcc时,又开始充电,一直循环,就形成了脉冲。

VHDL实验报告

VHDL实验报告5090309160 庄炜旭实验三. 4位可逆计数器,4位可逆二进制代码-格雷码转换器设计一.实验目的学习时序电路的设计,仿真和硬件测试,进一步熟悉VHDL设计技术1. 学习4位可逆计数器的设计2. 学习4位可逆二进制代码-格雷码转换器设计二.实验内容设计4位可逆计数器,及4位可逆二进制代码-格雷码转换器,并仿真,下载。

[具体要求]1.4位可逆计数器a)使用CLOCK_50作为输入时钟,其频率为50MHz(对于频率大于50Hz的闪烁,人眼会看到连续的光),因而,对其进行225的分频后,再用于时钟控制。

(可利用实验一)b)使用拨码开关SW17作为模式控制,置‘1’时为加法计数器,置‘0’时为减法计数器,同时使用LEDR17显示SW17的值。

c)使用KEY3作为异步复位开关(按下时为0,不按为1),当为加法计数器时,置“0000”,当为减法计数器时,置“1111”。

d)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

2.4位可逆二进制代码――格雷码转换器a)使用拨码开关SW17作为模式控制,置‘1’时为二进制代码―>格雷码转换,置‘0’时为格雷码―>二进制代码,同时使用LEDR17显示SW17的值。

b)使用拨码开关SW3, SW2, SW1, SW0作为输入的被转换数,SW3为高位,SW0为低位。

c)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

三.管脚设定SW[0]PIN_N25SW[1]PIN_N26SW[2]PIN_P25SW[3] PIN_AE14SW[17] PIN_V2LEDR[0] PIN_AE23LEDR[1] PIN_AF23LEDR[2] PIN_AB21LEDR[3] PIN_AC22LEDR[17] PIN_AD12KEY[3] PIN_W26CLOCK_50 PIN_N2四.相关知识二进制代码与格雷码相互转换格雷码(Gray Code,简称G码)是典型的循环码,它是由二进制码(Binary,简称 B 码)导出的。

设计一个四位可逆二进制计数器的实验报告

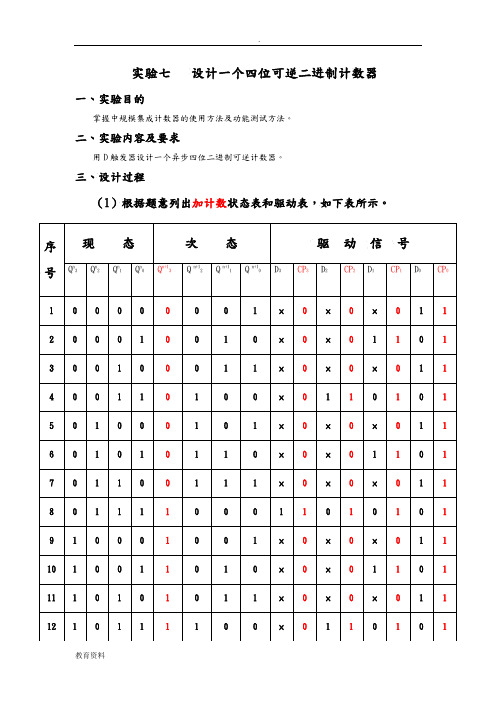

实验七设计一个四位可逆二进制计数器一、实验目的掌握中规模集成计数器的使用方法及功能测试方法。

二、实验内容及要求用D触发器设计一个异步四位二进制可逆计数器。

三、设计过程(1)根据题意列出加计数状态表和驱动表,如下表所示。

(2)用卡诺图化简,如下图所示。

求得各位触器的驱动信号的表达式33Q D =22Q D =11Q D =0Q D =(2)用卡诺图化简,如下图所示。

求得各位触器的时钟方程的表达式23Q CP =12Q CP =01Q CP =CP CP =0(3)根据题意列出减计数状态表和驱动表,如下表所示。

(2)用卡诺图化简,如下图所示。

求得各位触器的驱动信号的表达式33Q D22Q D =11Q D =0Q D =(2)用卡诺图化简,如下图所示。

求得各位触器的时钟方程的表达式23Q CP =12Q CP =01Q CP =CP CP =0由上分析可知:加减计数只在于时钟CP 的不同,若要使一个电路能够可逆计数,增设一控制开关,就可实现。

设K =1时为加计数,设K =0时为减计数,加法:CP n = 1-n Q K 减法:CP n = 1-n Q K则有:CP n =1-⊕n Q K(或如 K=0时为加法: CP n =1-∙n Q KK=1时为 减法: CP n =1-n KQ =1-n Q K 则有:CP n =1-⊕n Q K)四、可逆计数器逻辑图如下:四、实验用仪器、仪表数字电路实验箱、万用表、74LS74、CC4030 五、实验步骤 六、实验数据。

可逆计数器设计报告

一、题目(二)2、加/减可逆计数器二、要求:.设计一个4位二进制加/减可逆计数器。

控制信号为1时,加计数;0时,减计数。

要求写出Verilog代码,给出仿真波形(能反映出所有工作状态)。

三、思路方法:题目要求的计数器是一个带有低电平负载和清零输入端的同步4位二进制计数器。

内部应该像‘163一样采用D触发器而非T触发器,这样便于实现载入和清零功能。

每个D触发器的输入由一个2输入多路复用器驱动,这个复用器由1个或门和2个与门构成。

如果输入信号CLR_L有效,多路复用器的输出就为0。

反之,如果输入信号LD_L有效,上面那个与门就把输入数据传送到输出端。

如果CLR_L和LD_L都无效,下面的与门就把”异-或-非”门(XNOR)的输出传送到多路复用器的输出端。

它的二进制计数顺序既可以按升序进行也可以按降序进行,由输入信号UP/DN的值来控制。

当UP/DN为1时,按升序计数;当UP/DN为0时,按降序计数。

四、仿真结果及分析1、Verilog代码module _counter(CLK,CLR_L,LD_L,ENP_L,ENT_L,UPDN,D,Q,RCO_L);input CLK,CLR_L,LD_L,ENP_L,ENT_L,UPDN;input [3:0]D ;output [3:0]Q;output RCO_L;reg [3:0]Q;reg RCO_L;always @ (posedge CLK) //Creat the counter f-f behaviorif (!CLR_L) Q <= 4'b0;else if(!LD_L) Q <= D;else if(!ENT_L && !ENP_L && UPDN) Q <= Q+1;else if(!ENT_L && !ENP_L && !UPDN) Q <= Q-1;else Q <=Q;always @ (Q or ENT_L or UPDN) //Creat RCO_L combinational outputif (!ENT_L && UPDN && (Q == 4'd15)) RCO_L = 0;else if (!ENT_L && !UPDN && (Q == 4'd0)) RCO_L = 0;else RCO_L = 1;endmodule2、所有功能的仿真结果(1)加计数:计数器工作再自由计数模式且UPDN=1,计数器从0000加计数到1111时,RCO_L输出一个周期的低电平,然后计数器跳回0000重新开始计数。

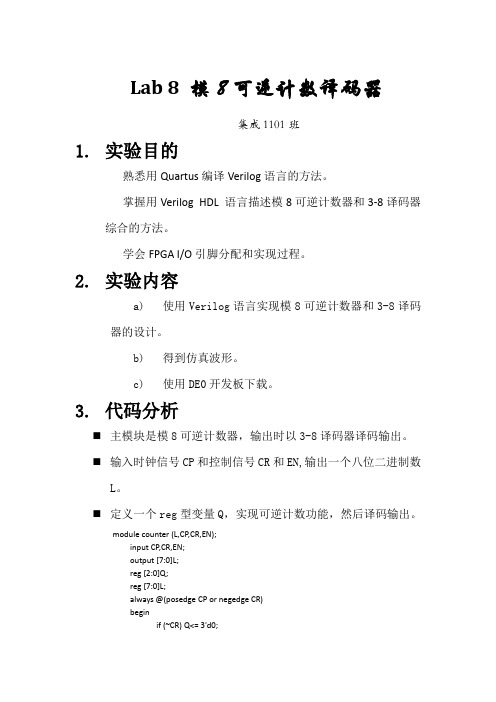

FPGA实验报告8__模8可逆计数器

Lab 8 模8可逆计数译码器集成1101班1.实验目的熟悉用Quartus编译Verilog语言的方法。

掌握用Verilog HDL 语言描述模8可逆计数器和3-8译码器综合的方法。

学会FPGA I/O引脚分配和实现过程。

2.实验内容a)使用Verilog语言实现模8可逆计数器和3-8译码器的设计。

b)得到仿真波形。

c)使用DE0开发板下载。

3.代码分析⏹主模块是模8可逆计数器,输出时以3-8译码器译码输出。

⏹输入时钟信号CP和控制信号CR和EN,输出一个八位二进制数L。

⏹定义一个reg型变量Q,实现可逆计数功能,然后译码输出。

module counter (L,CP,CR,EN);input CP,CR,EN;output [7:0]L;reg [2:0]Q;reg [7:0]L;always @(posedge CP or negedge CR)beginif (~CR) Q<= 3'd0;else if (~EN) //while EN==0,plus countingbeginif (Q>= 3'd7) Q<= 3'd0;elseQ<= Q+3'd1;endelse //while EN==1,decrise countingbeginif (Q<= 3'd0)Q<= 3'd7;elseQ<= Q-3'd1;endcase(Q)3'b000: L=8'b0000_0001;3'b001: L=8'b0000_0010;3'b010: L=8'b0000_0100;3'b011: L=8'b0000_1000;3'b100: L=8'b0001_0000;3'b101: L=8'b0010_0000;3'b110: L=8'b0100_0000;3'b111: L=8'b1000_0000;endcaseendendmodule4.实验步骤(1)打开Quartus9.1软件,选择“File=>New Project Wizard”,在弹出的窗口中输入项目的名称和存储位置。

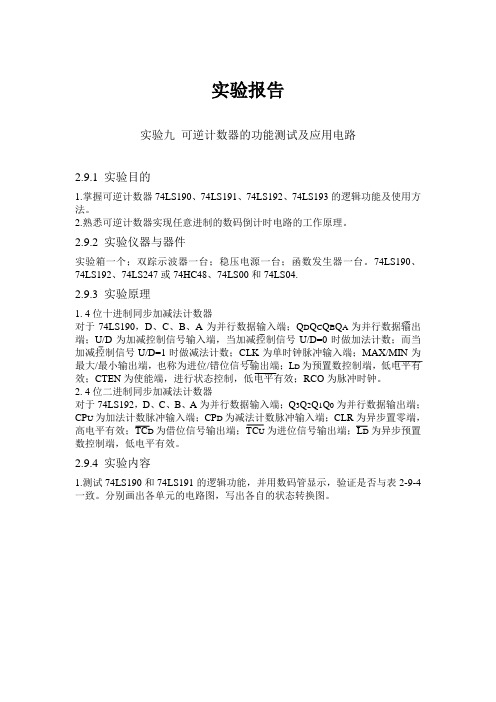

数电实验报告 可逆计数器

实验报告实验九可逆计数器的功能测试及应用电路2.9.1 实验目的1.掌握可逆计数器74LS190、74LS191、74LS192、74LS193的逻辑功能及使用方法。

2.熟悉可逆计数器实现任意进制的数码倒计时电路的工作原理。

2.9.2 实验仪器与器件实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台。

74LS190、74LS192、74LS247或74HC48、74LS00和74LS04.2.9.3 实验原理1. 4位十进制同步加减法计数器对于74LS190,D、C、B、A为并行数据输入端;Q D Q C Q B Q A为并行数据输出端;U/D为加减控制信号输入端,当加减控制信号U/D=0时做加法计数;而当加减控制信号U/D=1时做减法计数;CLK为单时钟脉冲输入端;MAX/MIN为最大/最小输出端,也称为进位/错位信号输出端;L D为预置数控制端,低电平有效;CTEN为使能端,进行状态控制,低电平有效;RCO为脉冲时钟。

2. 4位二进制同步加减法计数器对于74LS192,D、C、B、A为并行数据输入端;Q3Q2Q1Q0为并行数据输出端;CP U为加法计数脉冲输入端;CP D为减法计数脉冲输入端;CLR为异步置零端,高电平有效;TC D为借位信号输出端;TC U为进位信号输出端;L D为异步预置数控制端,低电平有效。

2.9.4 实验内容1.测试74LS190和74LS191的逻辑功能,并用数码管显示,验证是否与表2-9-4一致。

分别画出各单元的电路图,写出各自的状态转换图。

加法计数:0000—0001—0010—0011—0100—0101—0110—0111—1000—1001—0000减法计数:1001—1000—0111—0110—0101—0100—0011—0010—0001—0000加法计数:0000—0001—0010—0011—0100—0101—0110—0111—1000—1001—1010—1011—1100—1101—1110—1111—0000减法计数:1111—1110—1101—1100—1011—1010—1001—1000—0111—0110—0101—0100—0011—0010—0001—00002.测试74LS192和74LS193的逻辑功能,并用数码管显示,验证是否与表2-9-3一致。

数电实验报告可逆计数器设计

2017.12.21

实验地点

一教225

实验设备号

X

一、实验程序源代码

module jishu(

input [0:3] d,

input load,

input mr,

input t reg [0:3] q,

output co

);

always@(posedge clk,negedge mr)

.clk(clk),

.updn(updn),

.q(q),

.co(co)

);

initial begin

clk=1;

forever #10 clk=~clk;

end

initial begin

// Initialize Inputs

updn=1;

mr=1;

d = 1000;

load = 0;//置数

#30;

begin

if(!mr)

q<=0;

else if(!load)

q<=d;

else if(updn)

q<=q+1'b1;

else

q<=q-1'b1;

end

assign co=(updn==1)?(q==1111?1:0):(q=0000?1:0);

endmodule

module test;

// Inputs

reg [0:3] d;

reg load;

reg mr;

reg clk;

reg updn;

// Outputs

wire [0:3] q;

wire co;

// Instantiate the Unit Under Test (UUT)

最新12单片机可预置可逆4位计数器实验汇总

12单片机可预置可逆4位计数器实验12.可预置可逆4位计数器1.实验任务利用AT89S51单片机的P1.0-P1.3接四个发光二极管L1-L4,用来指示当前计数的数据;用P1.4-P1.7作为预置数据的输入端,接四个拨动开关K1-K4,用P3.6/WR和P3.7/RD端口接两个轻触开关,用来作加计数和减计数开关。

具体的电路原理图如下图所示2.电路原理图图4.12.13.系统板上硬件连线(1.把“单片机系统”区域中的P1.0-P1.3端口用8芯排线连接到“八路发光二极管指示模块”区域中的L1-L4上;要求:P1.0对应着L1,P1.1对应着L2,P1.2对应着L3,P1.3对应着L4;(2.把“单片机系统”区域中的P3.0/RXD,P3.1/TXD,P3.2/INT0,P3.3/INT1用导线连接到“四路拨动开关”区域中的K1-K4上;(3.把“单片机系统”区域中的P3.6/WR,P3.7/RD用导线连接到“独立式键盘”区域中的SP1和SP2上;4.程序设计内容(1.两个独立式按键识别的处理过程;(2.预置初值读取的问题(3.LED输出指示5.程序框图图4.12.26.汇编源程序COUNT EQU 30HORG 00HSTART: MOV A,P3ANL A,#0FHMOV COUNT,AMOV P1,ASK2: JB P3.6,SK1LCALL DELY10MSJB P3.6,SK1INC COUNTMOV A,COUNTCJNE A,#16,NEXT MOV A,P3ANL A,#0FHMOV COUNT,A NEXT: MOV P1,AWAIT: JNB P3.6,WAITLJMP SK2SK1: JB P3.7,SK2LCALL DELY10MSJB P3.7,SK2DEC COUNTMOV A,COUNTCJNE A,#0FFH,NEX MOV A,P3ANL A,#0FHMOV COUNT,A NEX: MOV P1,AWAIT2: JNB P3.7,WAIT2 LJMP SK2DELY10MS: MOV R6,#20MOV R7,#248D1: DJNZ R7,$DJNZ R6,D1 RETEND7.C语言源程序#include <AT89X51.H>unsigned char curcount;void delay10ms(void){unsigned char i,j;for(i=20;i>0;i--)for(j=248;j>0;j--);}void main(void){curcount=P3 & 0x0f;P1=~curcount;while(1){if(P3_6==0){delay10ms();if(P3_6==0){if(curcount>=15) {curcount=15; }else{curcount++; }P1=~curcount;while(P3_6==0); }}if(P3_7==0){delay10ms();if(P3_7==0){if(curcount<=0) {curcount=0; }else{curcount--; }P1=~curcount;while(P3_7==0); }}} }。

同步可逆计数器和序列检测器

课程实验报告课程名称:数字电路与逻辑设计专业班级:计实1001班学号:U201014488姓名:王宸敏指导教师:周次:第十周同组人员:熊凯报告日期:2012年5月18日计算机科学与技术学院【内容A】一、实验名称利用所给组件,设计一个同步模4可逆计数器,其框图如图5.9所示。

图中,X为控制变量,当X=0是进行加一计数,X=1时进行减一计数;Y2、Y1为计数状态;Z为进位或借位输出信号。

二、实验目的掌握同步时序电路实验的设计方法,验证所设计的同步时序逻辑电路,加深对“同步”和“时序”这两个名词的理解。

三、实验所用仪器和组件1.双D触发器组件2片,型号为74LS742.负沿双JK触发器2片,型号为74LS733.二输入四“与非”门2片,型号为74LS004.二输入四“或非”门1片,型号为74LS025.三输入三“与非”门1片,型号为74LS106.二输入四“异或”门1片,型号为74LS867.六反相器组件2片,型号为74LS04四、实验设计方案及逻辑图1.首先画出状态图如下:3.由真值表得到D1、D2及Z 的卡诺图如下: D2:121212122y y x y xy y y x y y x D +++=21y y x ⊕⊕= D1:11y D =Z :1212y y x y y x Z +=1212y y x y y x ⋅=4.由D1、D2及Z 的表达式可以设计出电路图如下,采用D 触发器:五、描述实验现象,并运用所学的知识进行分析、处理及讨论1.当输入x=0时,电路实现的是模4加法,即每来一个脉冲计数状态加一,同时逢4进位,即输出z=1。

因为电路图是按照状态图、真值表、状态表、表达式得到的,因此实现的正好是满足功能的电路。

2.当输入x=1时,电路实现的是模4减法,即每来一个脉冲计数状态减一,同时逢4借位,即输出z=1。

因为电路图是按照状态图、真值表、状态表、表达式得到的,因此实现的正好是满足功能的电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西南民族大学

学生实验报告

20 17 ------2018学年第 2 学期

课程名称:可编程逻辑器件及应用实验

任课教师:

学院:电气信息工程学院专业:年级:班级:学号:姓名:同组人:

if(Q==0) Q<=4’hf)

else Q<=Q-1;

end

endcase

end

endmodule

4)编辑输入波形数据,选择File—New命令,在New窗口中选择Vector Waveform file选项,单击OK,即出现空白波形编辑器。

5)设置仿真器参数,选择Assignment—Settings命令,在Settings窗口下选择Category—Simulation Settings。

在右侧的Simulation mode下拉列表框中选择Timing,即选择时序仿真,并选择仿真激励文件名fdiv0.vwf。

选择Simulation period 栏,确认选中了“Run simulation until all vector stimuli are used ”

6)启动仿真器,选择Processing—starsimulation,启动仿真,直到出现Simulation was successful,仿真结束。

7)在Simulation report中观察仿真结果。

如图:

4、分析讨论;。