DSP原理与应用---第5章 dMAX

DSP原理与应用EDMA

EDMA的参数RAM

容量为2KB,总共可以存放85组EDMA传输控制参数, 其内容包括三部分:

➢ 16个EDMA通道入口参数,每组6个字 ➢ 用于重加载/链接的传输参数组,每组6个字 ➢ 空余“草稿区”,8个字节 一旦事件发生器捕捉到某个事件,控制寄存器将从参数

RAM的16组入口参数中读取事件对应的控制参数,送 往地址发生器,发起传输

C672x

dMAX的控制器框图,包括:

➢事件和中断处理寄存器

➢事件编码器

➢高优先级事件参数随机存储 器(PaRAM)

➢低优先级事件参数随机存储 器 PaRAM

➢用于高优先级事件的地址生 成器MAX0(HiMAX)

C671x

EDMA的启动

两种方式启动EDMA: CPU启动EDMA/非同步的EDMA,CPU通过写事件置

位寄存器(ESR),强制触发对应事件,启动1个EDMA 通道 由事件触发的EDMA,事件锁存器一旦捕获到一个触 发事件,并且事件本身已被使能,那么该事件将DMA传输参数的连接

C671x

EDMA中断

所有16个通道共用一个中断信号EDMA_INT, 利用CIPR寄存器来判断发生了哪个事件 通道的传输结束代码TCC值与CIPR位一一对应,

不同的通道可以有相同的TCC,所以不同的通道可 以产生完全相同的中断,处理相同的服务程序。

C671x

快速DMA(QDMA)

几乎支持EDMA的所有传输模式,不支持参数连接

两组寄存器,第二组是第一组的“伪映射”,每组包含5个 寄存器,是C671x搬移数据最有效的手段

一个典型的QDMA操作如下:

QDMA_SRC = SRC_ADDRESS;//设置源地址

QDMA_DST = DST_ADDRESS; //设置目标地址

DSP原理与应用课件

Ⅱ、整数乘整数(数用Q0表示) Q0×Q0=Q0 举例:13×5 = 65 操作数用Q0表示为: 13 = 0000 0000 0000 1101B 5 = 0000 0000 0000 0101B 0000 0000 0000 1101 × 0000 0000 0000 0101 = 0000 0000 0000 0000 0000 0000 0100 0001 = 00000041H 表示的浮点数即为:65处理,如滤波、FFT、卷积等; ● 通信,如调制解调、纠错编码、传真、可 视电话等; ● 语音处理,如语音编码、语音合成、识别、 语音存储等; ●图形/图像处理,如模式识别、图像压缩与 传输、动画、机器人视觉等; ●仪器仪表,如数据采集、函数/波形产生等; ●军事,如保密通信、全球定位、雷达与声 纳信号处理、导航与制导等; ●医疗,如核磁共振、自动治疗仪等。

Ⅲ、混合表示法

在对精度和数据范围要求都比较高的情况下,两个 数可以采用介于Q15与Q0之间的不同的Q表示法。 举例: 设参与运算的两个数x和y的数值范围分别不超过± 1和± 4,两个数的Q值分别为Q15和Q13,为了保证数据 范围,应该采用Q13。例如: x = 0.4 y = 3.2 ,计算x + y 因为 xd = 3276, yd = 26214,则 xd + yd = 3276 + 26214 = 29490 转换为浮点数为:29490 × 2-13 ≈ 3.59985

●举例2:求3/40= ? step1:3 < 40 ,次数=0,余数=3 ; step2:3×10 = 30,30 <40,次数=0,余数=30; step3:30×10=300,300 > 40;300 - 40=260,执行第1次减 法;260 - 40=220,执行第2次减法; 220 - 40=180,执行第3次 减法;180 - 40=140,执行第4次减法;140 - 40=100,执行第5 次减法;100 - 40=60,执行第6次减法;60 - 40=20,执行第7 次减法;次数=7,余数=20; step4: 20×10=200,200 > 40; 200 - 40=160,执行第1次 减法;160 - 40=120,执行第2次减法;120 - 40=80,执行第3 次减法; 80 - 40=40,执行第4次减法; 40 - 40=0,执行第5次 减法;次数=5,余数=0; step5:结果=0 ×100 +0 ×10-1 + 7×10-2 +5 ×10-3 = 0.075

DSP原理与应用-课件

本书的 封面

走信息路 读北邮书

1.2.2 与CPU、MCU、FPGA/CPLD的比较

与CPU、MCU、FPGA/CPLD的比较

尽管微处理器集成度很高,但仍需要较多的外围电路, 使得其性价比、体积、功耗都都比DSP大的多。 但单片机的控制接口种类比DSP多,适用于以控制为主 的模数混合设计,同时在成本上单片机的价格也低的 多。

(4)图形/图像处理:如三维图像变换、模式识别、

图像增强、动画、电子地图等。

(5)自动控制:如机器人控制、自动驾驶、发动机控

制、磁盘控制等。

本书的

封面

走信息路 读北邮书

2.1 TMS320C54x的硬件结构特性

2.1.1 TMS320C54X的硬件结构 2.1.2 TMS320C54X的主要特性

走信息路 读北邮书

1.2.1 DSP芯片的特点 1.2.2 与CPU、MCU、FPGA/CPLD的比较 1.2.3 DSP产品简介

走信息路 读北邮书

本书的 封面

1.1

数字信号处理概述

数字信号处理概述

DSP可以代表数字信号处理技术(Digital Signal Processing),也 可以代表数字信号处理器(Digital Signal Processor

走信息路 读北邮书

本书的 封面

2.1.2 TMS320C54x的主要特性

1

CPU

2

存储器

3 片内外设

4 指令系统

走信息路 读北邮书

本书的 封面

2.1.2

CPU

CPU

(1) 先进的多总线结构(1条程序总线、3条数据总线和4

条地址总线)。

(2) 40位算术逻辑运算单元(ALU)。包括1个40位桶形移

DSP原理与应用2011-第五章TMS320F28335片(精)

DSP 原理与应用The Technology & Applications of DSPs第五章: TMS320F28335片内外设北京交通大学电气工程学院夏明超郝瑞祥万庆祝***************.cn**************.cn**************.cn:TMS320F28335第五讲: TMS320F28335片内外设教学目标:掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、串行外设接口。

外设接重点:TMS320F28335A/DCS308335内部/C 的正确使用,串行通信接口应用。

难点:TMS320F28335的ADC 寄存器操作和串行通信寄存器操作。

教学内容分两部分51§5.1:TMS320F28335内模拟/数字转换§5.2 :TMS320F28335系列串行通信接口SCI 和Modbus 协议介绍DSP 原理与应用2DSP原理与应用3 ADC 有关引脚§5.1 TMS320F28335内模拟/数字转换§5.1 .1Features and functions of ADC module:◆core with built-in dual sample-and-hold◆Simultaneous sampling or sequential sampling modesp g q p g ◆Analog input: ◆Fast conversion time runs at ADC clock orFast conversion time runs at , ADC clock, or 6.25 MSPSmultiplexed inputs◆, multiplexed inputs◆capability provides up to 16 " t i " i i l i E h i "autoconversions" in a single session. Each conversioncan be to select any 1 of 16 input channels.DSP 原理与应用4Sequencer can be operated as two independent 8-state ◆Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencerstwo cascaded 8state sequencers.◆(individually addressable to store conversion values store conversion valuesA/DC digital value:DSP 原理与应用2012年9月3日5◆for the start-of-conversion sequence–S/W -software immediate start–ePWM 1-6–GPIO XINT2◆allows interrupt request on every end-of-sequence (EOS or every other EOSy q ( y◆Sequencer can operate in mode, allowing multiple "time-sequenced triggers" to synchronize p q gg yconversions.Sample-and-hold (S/Hacquisition time window has ◆Sample and hold (S/H acquisition time window has separateA/DC模块框图(Block diagram of A/DC Module)§5.1. 2ADC 有关的寄存器控制寄存器通道顺序选择寄存器结果寄存器ADC有关的寄存器(序)控制寄存器状态寄存器参考电压选择寄存器偏移电压调整寄存器§5.1.3 ADC操作模式1 顺序采样模式(Sequential Sampling Mode)根据采样模式划分,包括顺序采样和同步采样2同步采样模式(Simultaneous Sampling Mode)DSP 原理与应用2012年9月3日11根据转换模式划分,包括:级联模式转换和和双序列模式转换1)级联模式转换DSP 原理与应用2012年9月3日122)双序列模式转换DSP 原理与应用2012年9月3日13 单序列模式和级联模式对比DSP 原理与应用2012年9月3日14§5.1.4 ADC电压参考默为使用内部电压参考也以使用外部电压参考允许值为●默认为使用内部电压参考,也可以使用外部电压参考,允许值为2.048V ,1.5V 和1.024V 。

DSP原理及应用第五章

4 MBytes SDRAM

10

PC

C64x 入门套件: C6416 DSK

X

11

第5章 汇编语言程序开发工具

2. ’C54x的开发工具

(2)代码调试工具:

可扩展的开发系统仿真器(XDS510):可用来 进行系统级的集成调试,是进行DSP芯片软硬件开发 的最佳工具。 评价模块EVM板:是一种低成本的开发板,可 进行DSP芯片评价、性能评估和有限的系统调试。

X

29

第5章 汇编语言程序开发工具

5.4 链接器的使用

链接器的主要任务是根据链接命令文件(.cmd), 将一个或多个COFF目标文件链接起来,生成存储器映 像文件(.map)和可执行的输出文件(.out)。

X

12

C6701 评估板

X

13

第5章 汇编语言程序开发工具

5.2 汇编语言程序的编辑、汇编和链接过程

汇编语言源程序可以在任何一种文本编辑器中进行

。如笔记本、WORD、EDIT、TC等。

当汇编语言源程序编写完成后,还必须经过汇编和

链接后才能运行。

X

14

第5章 汇编语言程序开发工具

5.2 汇编语言程序的编辑、汇编和链接过程

① 将一个或多个COFF目标文件中的各种段作为

链接器的输入段,经链接后在一个执行的COFF输出

模块中建立各个输出段;

② 在程序装入时对其重新定位,为各个输出段

选定存储器地址。

X

23

第5章 汇编语言程序开发工具

5.3.3 链接器对段的处理 链接器有2条伪指令支持上述任务:

● MEMORY伪指令——用来定义目标系统的存储 器配置空间,包括对存储器各部分命名,以及规定 它们的起始地址和长度。 ● SECTIONS伪指令——用来指定链接器将输入 段组合成输出段方式,以及输出段在存储器中的位 置,也可用于指定子段。 若未使用伪指令,则链接器将使用目标处理器 默认的方法将段放入存储空间。

DSP原理及应用——总复习 ppt课件

ppt课件

17

• 21、指数编码器是使用__EXP__指令和_NORM_指 令对累加器的数值进行归一化处理。

• 22、指数编码器可以在单个周期内执行___EXP__指 令,求得累加器中数的___指数__值,并以2的补码 的形式存放到__T暂存器__中。

• 23、C54x提供三个16位寄存器来作为CPU状态和控 制寄存器,它们分别为_ST0_﹑ST1_和_PMST_ 。

置位:SSBX C

ppt课件

15

• 17、桶形移位寄存器的任务是为输入的数据__ 定标___ ,包括在ALU运算前对来自数据存储 器的操作数或累加器的值进行_定标__﹑对累 加器的值进行_移位 ﹑ _归一化处理_等。

• 18、C54X CPU的乘法器/加法器单元包含一个 _17*17__ 位乘法器和_40_位加法器可以,在一 个流水线状态周期内完成一次_乘加____运算。

11典型的dsp系统应包括抗混叠滤波器数据采集ad转换器数字信号处理器dspda转换器低通滤波器12dsp系统的特点是接口方便编程方便具有高速性稳定性好精度高可重复性好集成方便13dsp芯片的特点是在一个指令周期内可完成一次乘法和一次加法程序和数据空间分开可以同时访问指令和数据片内具有快速ram通常可通过独立的数据总线在两块中同时访问具有低开销或无开销循环及跳转的硬件支持快速的中断处理和硬件io支持快速的中断处理和硬件io支持可以并行执行多个操作支持流水线操作使取指译码和执行等操作可以重叠执14dsp系统的设计过程可分为明确设计任务确定设计目标算法模拟确定性能指标选择dsp芯片和外围芯片设计实时的dsp应用系统硬件和软件调试系统集成和测试6个阶段

ppt课件

7

《DSP原理及应用》总复习

第2章 TMS320C54x的硬件结构

dsp技术原理及应用

DSP的字长有16位、24位、32位。为防止运算过程中溢出,累加 器 达 到 40 位 。 此 外 , 一 批 浮 点 DSP , 例 如 TMS320C3x 、 TMS320C4x、 TMS320C67x、 TMS320F283x、 ADSP21020等, 则提供了更大的动态范围。

DSP主要特点续

⑷图形/图像:二位/三维图形处理、图像压缩与传输、图像增强、 动画、机器人视觉等。

⑸军事:保密通信、雷达处理、声纳处理、导航、导弹制导等。

⑹仪器仪表:频谱分析、函数发生、锁相环、地震处理等。

⑺自动控制:引擎控制、声控、自动驾驶、机器人控制、磁盘控制 等。

⑻医疗:助听、超声设备、诊断工具、病人监护等。

⑼家用电器:高保真音响、音乐合成、音调控制、玩具与游戏、数 字电话/电视等。

DSP/多核处理器主要的生产厂家

• TI (德仪):/ • ADI: / • Agere: / • Freescale: / • ST(意法半导体) : • Lucent(朗讯):/ • Analog Device(模拟器件): • Motorola:/ • Samsung:/ • Microchip: / • Intel: / • AMD: /

平滑滤波

Y(t)

抗混叠滤波器将输入信号X(t)中比主要频率高的信号分量滤除, 避免产生信号频谱的混叠现象。

A/D——将输入的模拟信号转换为DSP芯片可接收的数字信号。

DSP芯片——对A/D输出的信号进行某种形式的数字处理。

D/A——经过DSP芯片处理的数字样值经D/A转换为模拟量,然 后进行平滑滤波得到连续的模拟信号。

⑻硬件配置强

新一代DSP的接口功能愈来愈强,片内具有定时器、串行口、主机 接口(HPI)、DMA控制器、软件控制的等待状态产生器、锁相环时 钟产生器、A/D转换以及实现在片仿真符合IEEE 1149.1标准的测试 仿真接口,使系统设计更易于完成。另外,许多DSP芯片都可以工 作在省电方式,大大降低了系统功耗。

DSP原理及应用pdf

1、数字信号处理的实现方法一般有哪几种?答:数字信号处理的实现是用硬件软件或软硬结合的方法来实现各种算法。

(1) 在通用的计算机上用软件实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制;(4) 用通用的可编程 DSP 芯片实现。

与单片机相比,DSP 芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的 DSP 芯片实现。

在一些特殊的场合,要求的信号处理速度极高,用通用 DSP 芯片很难实现(6)用基于通用 dsp 核的 asic 芯片实现。

2、简单的叙述一下 dsp 芯片的发展概况?答:第一阶段,DSP 的雏形阶段(1980 年前后)。

代表产品:S2811。

主要用途:军事或航空航天部门。

第二阶段,DSP 的成熟阶段(1990 年前后)。

代表产品:TI 公司的 TMS320C20 主要用途:通信、计算机领域。

第三阶段,DSP 的完善阶段(2000 年以后)。

代表产品: TI 公司的 TMS320C54 主要用途:各个行业领域。

3、可编程 dsp 芯片有哪些特点?答:1、采用哈佛结构(1)冯。

诺依曼结构,(2)哈佛结构(3)改进型哈佛结构 2、采用多总线结构 3.采用流水线技术4、配有专用的硬件乘法-累加器5、具有特殊的 dsp 指令6、快速的指令周期7、硬件配置强8、支持多处理器结构9、省电管理和低功耗4、4、什么是哈佛结构和冯。

诺依曼结构?它们有什么区别?答:哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯。

诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

DSP原理及应用(精)

4.图形/图像---如二维和三维图形处 理,图像压缩与传输,图像增强,动画, 机器人视觉等;

5.军事---如保密通信,雷达处理,声 纳处理,导航,导弹制导等; 6.仪器仪表---如频谱分析,函数发生, 锁相环,地震处理等; 7.自动控制---如引擎控制,声控,自 动驾驶,机器人控制,磁盘控制等;

可以有两种方式:微处理器,模拟器件。 比较优越性: 模拟滤波器(或者更一般地说,模拟电路)的性能要取决 于温度等环境因素。而数字滤波器则基本上不受环境的响。 数字滤波易于在非常小的宽容度内进行复制,因为其性能 并不取决于性能已偏离正常值的器件的组合。 一个模拟滤波器一旦制造出来,其特性(例如通带频率范 围)是不容易改变的。使用微处理器来实现数字滤波器, 就可以通过对其重新编程来改变滤波的特性。

3、成熟期:87-97年 TI:TMS320C54系列(简写C54X或C5400) AD:ADSP2100系列 Lucent:DSP1600 Motorola:DSP56000 特点:都支持3.3V供电; 片上存储器较大; 都 有JTAG模块支持用户在线调试。

4、突破期(97年以后):

发展非常迅速,从定点——浮点 低端——高端 通用——专用 朝高速、低功耗方向发展。 TI的 DSP系列

第一讲

DSP原理及应用

第一章 绪论 “DSP”

Digital Signals Processing 包括对信号的采集、变换、滤波、估值、 增强、压缩、识别等,是20世纪60年代前后 发展起来的并广泛应用的新兴学科。 Digital Signals Processor 是微型计算机发展的一个重要分支,也 是数字信号处理理论实用化过程的重要技术 工具。

1.信号处理---如数字滤波,快速傅立 叶变换,相关运算,谱分析,卷积,模 式匹配,加窗,波形产生等;

DSP器件原理与应用-05 TMS320C6000系列DSP集成外设

2

1

13

2

1

13

2

1

13

1

1

13

2

1 2 64-bit TCP2 VCP2

2

2

21

3

2

21

3

2

21

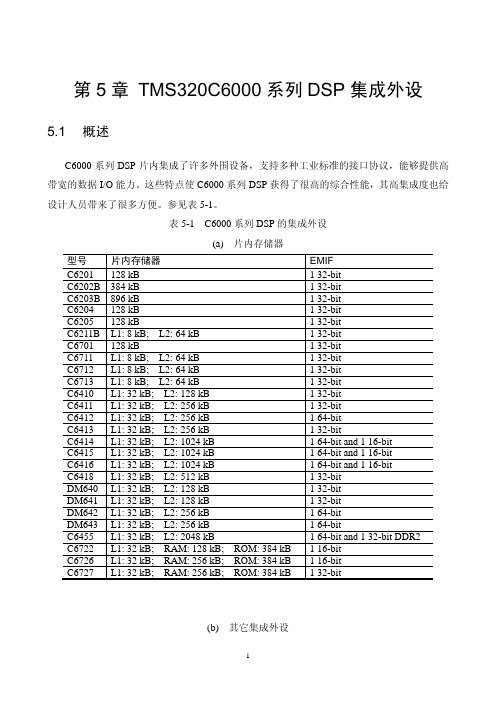

5.2 片内存储器

5.2.1 简介

C6000 系列 DSP 片内集成了大容量存储器,存储器的容量和结构随芯片不同而有所差别。 对于 C620x/C670x,片内存储器分为程序区间和数据区间两部分,其中程序区间可以作为 普通 SRAM 映射到存储空间,也可以作为高速缓存。 对于 C621x/C671x/C64x,片内采用二级存储器结构。第 1 级存储器包括相互独立的程序 缓存(L1P)和数据缓存(L1D),只能作为高速缓存被 CPU 访问。第 2 级存储器(L2)是一 个统一的程序/数据空间,可以整体作为 SRAM 映射到存储空间,也可以整体作为第 2 级缓存, 或者按比例组合。

10/100

10/100

10/100

10/100

10/100/1000

HPI

1 16-bit

1 16-bit 1 16-bit 1 16-bit

1 16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit

Map 0

0140 0000h – 0140 FFFFh 0140 0000h – 0141 FFFFh 0142 0000h – 0143 FFFFh 0140 0000h – 0143 FFFFh 0144 0000h – 0145 FFFFh 0140 0000h – 0140 FFFFh 0140 0000h – 0140 FFFFh 0140 0000h – 0140 FFFFh

DSP原理及应用 (乔瑞萍)(TMS320C54X)

第1章 绪论

TMS 320C8x

Future

多 处 理 器 DSP

TMS 320C3x

TMS 320C4x

TMS

TMS

320C1x 320C2x

TMS 320C2xx

TMS 320C5x

TMS 320C54x

TMS 320C6x

Future Future

浮 点发展示意

[1101 0000B]补 =1011 0000B=- (2-2+2-3)= -(0.25+0.125)= -0.375 小数主要用于数字和各种(ɡè zhǒnɡ)信号处理算法的计算。

共四十二页

第1章 绪论

3.数的定标 显然,定点表示并不意味着就一定是整数表示。 在许多情况下,需要(xūyào)由编程来确定一个数的小数 点的位置,即数的定标。定点数最常用的是Q表示法或 Qm.n表示法。它可将整数和小数表示方法统一起来。 其中,m表示数的2补码的整数部分,n表示数的2补码 的小数部分,1位符号位,数的总字长为m+n+l位。表 示数的整数范围为-2m~2m -1,小数的最小分辨率为 2- n。表1-2给出了16种Q表示法及其所表示的十进制数 范围。

图

共四十二页

第1章 绪论

2.TMS320系列的典型(diǎnxíng)应用 自从20世纪70年代末第一个DSP芯片诞生以来, DSP芯片取得了飞速的发展。在20年里,DSP芯片已经 在信号处理、音/视频、通信、消费、军事等诸多领域 得到了广泛的应用。随着DSP芯片性价比的不断提高, 单位运算量功耗的显著降低,DSP芯片的应用领域将 会不断扩大。表1-1列出了TMS320系列DSP的典型应用。

第1章 绪论

DSP原理与应用课后答案(电子工业出版社)共12页word资料

第一章绪论1、简述DSP系统的构成和工作过程。

答:DSP系统的构成:一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等。

DSP系统的工作过程:①将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠。

②经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。

③数字信号处理器对x(n)进行处理,得数字信号y(n)。

④经D/A转换器,将y(n)转换成模拟信号;⑤经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

9、简述DSP系统的设计步骤。

答:①明确设计任务,确定设计目标。

②算法模拟,确定性能指令。

③选择DSP芯片和外围芯片。

④设计实时的DSP芯片系统。

⑤硬件和软件调试。

⑥系统集成和测试。

第二章 TMS320C54x硬件结构1、 TMS320C54X芯片的基本结构都包括哪些部分?答:①中央处理器②内部总线结构③特殊功能寄存器④数据存储器RAM⑤程序存储器ROM⑥I/O口⑦串行口⑧主机接口HPI⑨定时器⑩中断系统2、TMS320C54X芯片的CPU主要由哪几部分组成?答:①40位的算术运算逻辑单元(ALU)。

②2个40位的累加器(ACCA、ACCB)。

③1 个运行-16至31位的桶形移位寄存器。

④17×17位的乘法器和40位加法器构成的乘法器-加法器单元(MAC)。

⑤比较、选择、存储单元(CSSU)。

⑥指令编码器。

⑦CPU状态和控制寄存器。

3、TMS320VC5402共有多少可屏蔽中断?它们分别是什么?RS和NMI属于哪一类中断源?答:TMS320VC5402有13个可屏蔽中断,RS 和NMI 属于外部硬件中断。

4、试分析下列程序的流水线冲突,画出流水线操作图。

如何解决流水冲突?STLM A ,AR0 STM #10,AR1 LD *AR1,B 解:流水线图如下图:1 2 3 4 5 6 789预取指取指 译码 寻址 读数 执行STLM A,AR0预取指取指 译码 寻址 读数 执行STM#10,AR1 (1st Word)预取指取指 译码寻址 读数 执行STM #10,AR1(2nd Word)预取指取指译码寻址读数执行LD *AR1,B解决流水线冲突:最后一条指令(LD *AR1,B)将会产生流水线冲突,在它前面加入一条NOP 指令可以解决流水线冲突。

ADSP基础入门 第5讲 ADSP处理器的DMA

2

成信院-ADI联合实验室

ADSP-BF533 Block Diagram

L1 Core Timer 64 Instruction Memory

Performance Monitor

Core Processor

LD0 32 L1 Data LD1 32 Memory

JTAG/ Debug SD32 Core D0 bus 32

Descriptor

List (Small Model) Mode (FLOW = 0x6).

In this mode, the Descriptor Block does not include the upper 16 bits of the NEXT_DESC_PTR parameter. The upper 16 bits are taken from the upper 16 bits of the NEXT_DESC_PTR register, thus confining all descriptors to a specific 64K page in memory.

The World Leader in High Performance Signal Processing Solutions

ADSP处理器的DMA

Direct Memory Access (DMA)

电子工程学院 陈子为

成信院-ADI联合实验室

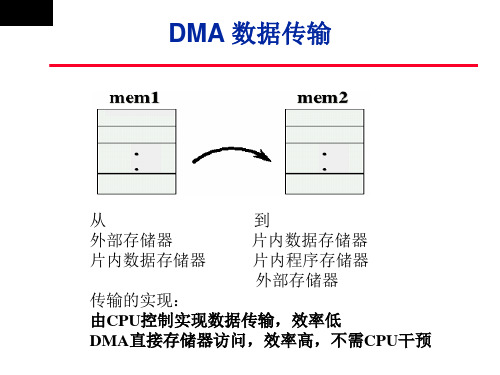

一、DMA概述

在DSP内部,一般采用多总线的哈佛结构,数据总 线和程序总线相互独立,即指令的存取和数据的存 取并行不悖,为了发挥DSP核心运算单元的高速运 算能力,必须先把外部数据传输到片内存储器中。 使用DMA操作可以减少核心处理器的负担,提高 运算速度。 另一方面,DSP系统总要与各种外部信号打交道, 它从外部输入数字信号,经过各种算法处理后,还 要输出给其它外部设备。不仅如此,对于很多应用 系统,数据的输入和输出常常是连续不断的。试想 若用DSP的核心部件完成数据的输入和输出,将无 法发挥DSP的高速运算能力。而AD公司的ADSPBF533内部集成了DMA控制器,从而可用DMA来 完成数据的输入和输出。

dsp技术原理及应用

①在通用的计算机上用软件实现。 ②在通用计算机系统上加上专用的加速处理机实现。 ③用通用的单片机实现。 ④用通用的可编程DSP芯片实现。 ⑤用专用的DSP芯片实现。 ⑥用/CPLD/FPGA实现。

2、数字信号处理系统的一般组成

抗混叠 X(t)

滤波

A/D 转换 X(n) DSP 芯片 Y(n) D/A转换

程序地址总线

控制总线

冯

控制总线 存 储 器 指

诺

CPU

令和数据

曼

共用

CPU

程序存储器

数据存储器

基本哈 佛结构

结

构

数据总线

程序数据总线 数据数据总线

程序/数据

数据

程序/数据

数据

高速缓存

改进哈佛 结构

⑵多总线结构 DSP主要特点续

对DSP来说,总线越多,可以完成的功能就越复杂。

⑶流水线结构

时钟 取指

N N+1 N+2 N+3

⑸特殊的DSP指令 DSP主要特点续

在 DSP 的 指 令 系 统 中 , 设 计 了 一 些 特 殊 的 DSP 指 令 。 例 如 TMS320C54x中的FIRS和LMS指令,则专门用于系数对称的FIR 滤波器和LMS算法。 ⑹指令周期短

DSP广泛采用亚微米CMOS制造工艺,如TMS320C54x,其运行 速度可达200MIPS。 TMS320C55x,其运行速度可达400MIPS。 TMS320C6414T的时钟为1GHz,运行速度达到8000 MIPS。

⑺运算精度高

DSP的字长有16位、24位、32位。为防止运算过程中溢出,累加 器 达 到 40 位 。 此 外 , 一 批 浮 点 DSP , 例 如 TMS320C3x 、 TMS320C4x、 TMS320C67x、 TMS320F283x、 ADSP21020等, 则提供了更大的动态范围。

精品课件-TMS320C54X DSP原理及应用-第5章

第5章 TMS320C54x的引脚功能、流水线结构和外部总线结构

DS 、 PS 、 IS :数据、程序和 I/O 空间选择信号。 MSTRB 、 IOSTRB:外部存储器、I/O 空间选通信号。 READY、R/ W :数据准备好及读/写信号。 HOLD 、 HOLDA :保持输入信号、保持响应信号。 MSC :微状态完成信号。 IAQ :指令获取信号。

19

第5章 TMS320C54x的引脚功能、流水线结构和外部总线结构

在单周期内允许CPU对DARAM访问两次,第一次访问是在 前半周期,再次访问是在后半周期。访问DARAM块的情况如表 5-1所示。

20

第5章 TMS320C54x的引脚功能、流水线结构和外部总线结构

由于两种类型的访问都要按时进行,而每半个周期仅能执 行一次访问,因此有可能会发生时序上的冲突。例如,同时从 同一存储器块中取指和取操作数(都在前半周期),或者同时对 同一存储器块进行写操作和读(第二个数)操作(都在后半周 期),都会造成时序上的冲突。CPU可以通过重新排列访问次 序,或者将写操作延迟一个周期,又或者通过插入一个空周期 的办法,自动地消除这些冲突。

27

第5章 TMS320C54x的引脚功能、流水线结构和外部总线结构

单独的外部空间选择引脚 IS、 DS和 PS用于选择不同存 储空间的外部存储器; MSTR用B于访问外部程序或数据存储器, 用于访问IOIS/OT设R备B ;读/写信号(R/ )则控制数据W传送的方向。

28

第5章 TMS320C54x的引脚功能、流水线结构和外部总线结构

9

第5章 TMS320C54x的引脚功能、流水线结构和外部总线结构

6.串口信号 CLKR0、CLKR1:接收时钟。 CLKX0、CLKX1:发送时钟。 DR0、DR1:串行口数据接收端。 DX0、DX1:串行口数据发送端。 FSR0、FSR1:用于接收输入的帧同步脉冲。 FSX0、FSX1:用于发送的帧同步脉冲。

DSP原理及应用(邹彦)第5章 'C54x的汇编语言程序设计

18

24

LD

2013年11月15日

# bei_hua,A

第5章 TMS320C54x汇编语言程序设计

6. 汇编时间常数

也可以用.set伪指令将符号常数赋给寄存器名。 此时,该符号变成了寄存器的替代名。

例如: AuxRl MVMM .set ARl AuxRl,SP

2013年11月15日

ADD # 99, B

DSP原理及应用 13

操作数# 99是一个立即数。

第5章 TMS320C54x汇编语言程序设计

(1) 指令的操作数前缀 ② 用“*”作前缀

使用“*”符号作为前缀,汇编器将操作数作为 间接地址,即把操作数的内容作为地址。 例如: Label: LD * AR3, B 操作数*AR3指定一个间接地址。该指令将引导 汇编器找到寄存器AR3的内容作为地址,然后将该地 址中的内容装入指定的累加器B中。

2013年11月15日 DSP原理及应用 23

第5章 TMS320C54x汇编语言程序设计

5.1.2 汇编语言中的常数与字符串

6. 汇编时间常数 在程序中使用.set伪指令给一个符号赋值,该符 号就成为一个汇编时间常数,等效于一个常数。

为了使用表达式中的常数,赋给符号的必须是绝 对值。 例如:将常数值18赋给符号bei_hua。 bei_hua .set

立即数方式没有使用,但汇编器认为操作数是 一个数值18(即立即数),用18数值初始化一个字节。

2013年11月15日 DSP原理及应用 16

第5章 TMS320C54x汇编语言程序设计

5.注释 用来说明指令功能的文字,便于用户阅读。 注释可位于句首或句尾,位于句首时,以 “*”或“;”开始,位于句尾时,以分号 “;”开始。 注释可单独一行或数行;

TMS320C55X_dsp原理及应用第5章

之后运行配置函数:

PLL_config(&Config_PLL); 也可以通过函数设置PLL频率: PLL_setFreq (6, 1); 通过PLL_setFreq函数可以复位PLL锁相环,并改变倍频和分频数从而 得到所需的频率

CSL库中PLL_Config锁相环配置结构体声明如下:

CSL库中PLL_Config锁相环配置结构体

使用方法

省电(IDLE)

与省电有关的位是IAI CLKMD引脚为低电平,输出频率等于输入频率; CLKMD引脚为高电平,输出频率等于输入频率的一 半 锁相环对输入时钟跟踪锁定之后,由于其他原因使其 输出时钟发生偏移

DSP复位

失锁

使用方法及实例

利用库函数配置时钟发生器的方法

主机接口

信号采集

采集模拟信号的模/数转换器 提供数字信号输入、输出功能的通用输入/输出 接口 多通道缓冲串口、I2C接口、异步串口、USB接 口以及多媒体卡/SD卡接口 DMA控制器、指令流水线等

通信接口

其他外设

辅助CPU工作,提高DSP的工作效率

片上外设支持库特点:

采用标准协议对外设进行编程

首先要声明PLL配置结构,具体声明如下:

PLL_Config Config_PLL = { 1, /*iai 休眠后重新锁相 */ 1, /*iob 失锁后进入旁路模式并重新锁相 */ 6, /*pllmult CLKIN * pllmult = DSP主时钟*/ 0 /*div CLKOUT= DSP主时钟/(div+1) */ };

DSP原理及应用第五章

STACK

table:

start:

;从程序存储器传送到数据存储器中

;从数据存储器传送到数据存储器中

end:

10

MEMORY { PAGE 0: EPROM : org = 0E000H len = 0100H VECS: org = 0FF80H len = 0004H PAGE 1: SPRAM : org = 0060H len = 0020H DARAM : org = 0080H len = 0100H } SECTIONS { .text :>EPROM PAGE 0 .data :>EPROM PAGE 0 .bss :>SPRAM PAGE 1 STK :>DARAM PAGE 1 .vectors:>VECS PAGE 0 }

16

特 点

对于Xmem和Ymem,只能用以下辅助寄存器及寻址方式:

辅助 寄存器 选择

Xar或Yar 00 01 10 11

操作码语 法 *ARx *ARx*ARx+ *ARx+0%

辅助寄存器 AR2 AR3 AR4 AR5

双数据存储器操作数寻址的类型

Xmod或 Ymod 00 01 10 11 功 能 说 明

第五章 汇编语言编程举例

第一节 汇编语言编程的基本方法

第三节

第四节

DSP在信号发生器上的应用

用DSP实现FIR滤波器

第五节

用DSP实现IIR滤波器

1

第一节 汇编语言编程的基本方法

1.堆栈的使用

要 点

1.压入数据时,堆栈从高地址向低地址 增长。 2.压栈时指针先减,SP-1,再压入数据; 3.出栈时,先弹出数据后,再SP+1。 4.如要用堆栈,必须先设置,后使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.1.2 dMAX术语

EventEntryTable-事件入口表:事件入口表包含所有的事 件入口,占据32个字节,它位于PaRAM的开始。有两个 事件入口表,一个用于高优先级事件,一个用于低优先级 事件。如果一个事件属于高优先级事件组,那么它的事件 入口就位于高优先级事件入口表,如果一个事件属于低优 先级事件组,那么它的事件入口就位于低优先级事件入口 表。 EventPriorityGroup-事件优先级组:dMAX事件可以被 设定为高优先级或低优先级,这样就把事件分进了两个优 先级组:高优先级或低优先级。高优先级事件组由MAX0 模块来处理,低优先级事件组由MAX1模块来处理。

4.1.2 dMAX术语

QuantumTransferSizeLimit(QTSL)-量子传输大小限制 :可在指定通道的事件入口上编程指定量子传输的大小, 可以编程为1个、4个、8个或16个数据单元。量子传输的 实际大小是QTSL中比较小的,而且数据单元的个数也被 传输。减少QTSL可以降低总体的dMAX延迟,增加QTSL 可以提高dMAX的数据吞吐量。 PendingEvent-未处理事件:未处理事件是指在DEFR中 占据了位置但还没有被dMAX控制器处理的事件。 LongDataTransfer-长数据传输:当每个同步事件之后传 输的数据单元的个数大于QTSL时发生长数据传输。

第四章 双通道数据搬移加速器(dMAX)

第四章 双通道数据搬移加速器(dMAX)

4.1 dMAX概述 4.1.1 简介 dMAX 控制器用于处理内部数据存储控制器和C672x DSP 外围设备之间用户编程数据的传输,dMAX也允许任何可 寻址存储空间之间的数据传输,包括内部存储器、外设和 外部存储器。

4.1.2 dMAX术语

One-Dimensional (1D) Transfer-一维传输:一组数据单 元组成一个一维数据块,可以设置数据单元的个数以及数 据单元之间的间隔(space),指定的间隔与源地址和目的 地址无关,范围是-32768到32767个单元。

Two-Dimensional (2D) Transfer-二维传输:一组帧组成 2维数据块,第一维是一个帧中的数据单元数,第二维是 帧的数量,一个二维数据块中帧的数量可以是1到65535 。一次可以传输一帧或整个2维数据块。二维数据块间的 间隔与源地址和目的地址无关,(当前值:-32768到32676 个单元)。

·高优先级事件参数随机存 储器(PaRAM)

·低优先级事件参数随机存 储器 PaRAM ·用于高优先级事件的地址 生成器 MAX0(HiMAX ) ·用于低优先级事件的地址 生成器 MAX1(LoMAX )

dMAX的具 体工作内容

4.1.2 dMAX术语

dMAX-双通道数据搬移加速器:dMAX由两个相同的模块 组成,MAX0和MAX1,两个模块可并行运行。 Element transfer-单元传输:从源地址到目的地址的单个 数据单元(8位,16位,32位)的传输。如果需要的话,每 个单元可以在同步事件的基础上进行传输。单元传输用于 一维传输。 Frame-―帧:一组数据单元组成帧。一个帧可以有交错 的或连接的数据单元。帧可以在有同步事件或无同步事件 的情况下进行传输。帧用于一维传输。

DSP结构框图

dMAX功能框图

dMAX控制器有如下功能

·可以进行高级数据分类的三维数据传输 ·把一部分存储器作为循环缓冲/FIFO存储器,并有基于读 写数据的延迟 ·可以同时处理两个传输请求(假设它们的源地址或目的地 址不同)

dMAX控 制器的结构 框图

·事件和中断处理寄存器。 ·事件编码器

4.1.2 dMAX术语

Three-Dimensional (3D) Transfer-三维传输:一组二维 数据块组成三维数据块,第一维是帧中数据单元的数量, 第二维是帧的数量,第三维是二维数据块的数量。二维数 据块的数量可以是1到32767。一次可以传输一帧或整个3 维数据块。三维数据块间的间隔与源地址和目的地址无关 ,(当前值:-32768到32676个单元)。 One-Dimensional Burst (1DN) Transfer-1维突发传输: 1维突发传输是为搬移存储器里一段连续的数据而进行的 优化,这一传输不支持不连续的源或目的地址。

4.1.2 dMAX术语

Event-事件:由事件标志寄存器(DEFR)触发的事务。例 如,McASP接收的数据可以触发一个事件。

4.1.2 dMAX术语

EventEntry-事件入口:如果一个事件用来触发数据传输,应设定事 件入口以指定传输类型、传输选项,并应该包括指向传输入口的指针 。如果事件是用来触发一个中断,事件入口只需指定使用哪条中断线 路。事件入口仅占用dMAX PaRAM存储空间的一个字节,里面是事 件和事件入口之间一对一的对应关系。在每个PaRAM里一个特定的 事件入口对应一个事件(一个事件在高优先级PaRAM中有一个事件入 口,在低优先级PaRAM中有一个事件入口),事件优先级组决定当一 个事件到达时哪一个事件入口传输给HiMAX/LoMAX。所有的事件被 分进低优先级或高优先级组,事件编码器对所有收到的事件进行优先 级划分,并且找出每个组中具有最高优先级别的事件。两个具有最高 优先级别的事件(每个组一个)可以被同时处理(HiMAX处理来自高优先 级组的最高优先级的请求,LoMAX处理来自低优先级组的最高优先级 的请求)。事件入口是可编程的,定义相应的事件到达时如何进行处 理。

4.1.2 dMAX术语

Transfer Entry-传输入口:传输入口表包括一个11字节 长的入口,定义如源地址、目的地址、计数以及索引等传 输参数。每个PaRAM中有足够的空间来存储8个不同传输 的传输入口(一共16个传输入口)。

Hale Waihona Puke QuantumTransfer-量子传输:为减少系统等待时间,长 数据被分为很多短数据传输,称量子传输。dMAX总是以 量子传输的方式移动数据。如果在dMAX进行量子传输的 时候一个事件到达,那么在量子传输进行完之后再处理这 个事件。