dspDSP芯片结构介绍2

DSP芯片结构和CPU外围电路详解

第二章 DSP芯片结构和CPU外围电路

2.3通用定时器

一、组成和框图 ▪ C5509 DSP片内有两个定时器:Timer0,Timer1; ▪ 具有定时或计数功能。计数器在每个时钟周期减1,当减到0就 产生一个输出信号。该输出信号可用于中断CPU或触发DMA传输 (称为定时器事件)。 ▪ 定时器由时钟、控制寄存器、计数器和定时器事件等部分构成。

第二章 DSP芯片结构和CPU外围电路

四、定时器控制寄存器TCR

▪ IDLE_EN:省电控制使能位,0:禁止省电模式,1:允许省电模式

▪ INT/EXT:时钟源从内部切换到外部的指示标志,当时钟源从内部切换到 外部要检测此位来决定是否准备好使用外部时钟。

0:定时器没准备好使用IM:定时器错误标志,0:正常,1:错误

支持的接口有:

▪ 包括异步 SRAM、ROM、FLASH(闪速存储器) 、EPROM等,EMIF能 够提供可配置的定时参数,提供高度灵活的存储器时序。每个接口都 可以支持

▪ 程序代码访问 ▪ 32bit数据访问、16bit数据访问、8bit数据访问。

第二章 DSP芯片结构和CPU外围电路

2.1.2 TMS320C55x CPU

CPU有4个功能单元:指令缓冲单元(I单元),程序流程单元(P单元) ,地址数 据流程单元(A单元)和数据计算单元(D单元)

CPU结构示意图

第二章 DSP芯片结构和CPU外围电路

▪ A单元16位ALU的功能

能接收I单元数据,又能够和存储器、I/O空间、A单元寄存器、 D单元寄存器和P单元寄存器进行数据交换,完成算术、逻辑、 位操作、移位、测试、旋转等操作。A单元包括的寄存器有下 列4种类型:

1)数据页寄存器(Data Page Register):DPH、DP、(接口数据 页)PDP

DSP第二章DSP芯片的基本结构和特征

允许文本交换的4×12位堆栈 两个间接寻址的辅助寄存器

双通道串行口(TMS32011,TMS320C17/E17) 协处理器接口(TMS320C17/E17) 器件封装:40脚双列直插(DIP)/44脚塑封(PLCC)

h

12

2.3.1.2 TMS320C10 TMS32010采用改进的哈佛结构,即程序和数据

DSP芯片的特征就是有一个专用的硬件乘法器。 在TMS320系列中,由于具有专用的硬件乘法 器,乘法可在一个指令周期内完成。

h

9

2.2.4 特殊的DSP指令

DSP芯片的另一个特征:特殊的指令。 指令DMOV:它完成数据移位功能。在数字信号处理中, 延迟操作非常重要,这个延迟就是由DMOV来实现的。

第二章

DSP芯片的基本 结构和特征

h

1

2.1 引 言

可编程DSP芯片是一种具有特殊结构的微处理器。 DSP芯片一般都具有程序和数据分开的总线结构、 流水线操作功能、单周期完成乘法的硬件乘法器以及 一套适合数字信号处理的指令集。

本章内容:DSP芯片的基本结构,TI公司的各种 DSP芯片的特征及其他公司的DSP芯片的特点。

h

7

CLKOUT1

取指 译码 执行

N N-1 N-2

N+1 N

N-1

N+2 N+1

N

h

8

2.2.3 专用的硬件乘法器

乘法是DSP的重要组成部分。滤波器常常做一 次乘法和一次加法(XY)。乘法速度越快,DSP

处理器的性能就越高。 在通用的微处理器中,乘法指令是由一系列加 法来实现的,故需许多个指令周期来完成。

期使得DSP芯片能够实时实现许多DSP应用。

dspDSP芯片结构介绍2

Digital Signal Processor 数字信号处理器 樊松 讲师

电子与信息工程学院电气工程系

1

第二章 DSP芯片结构介绍

第一节 基本性能 第六节 串行口

第二节 CPU结构

第七节 与外设的接口

第三节 内部总线结构 第八节 复位与省电

第四节 存储器结构 第九节 中断

第五节 在片外围电路 第十节 自举加载

1trn01tcn1m1d1elsen1m2d2d1d2m1尺度1m2尺度22j1n1n2j8d1d216功能exp指数编码器t寄存器如何计算指数171do页存储器18arp1513tc1211ova10ovbbraf15cpl14xf13hm12intm1110ovm19iptr157mpmc如何将40位数据饱和处理成32位数20?程序总线pb?数据总线cbdb和eb?地址总线pabcabdab和eab?在片双向总线2122读写方式地址总线程序总线数据总线pabcabdabeabpbcbdbeb程序读hwlwhwlw单数据写一个周期内如何执行3操作数指令24c54xcpu25cpu26daramsaramrom27存储器型式c541c542c543c545c546c548c549rom28k2k2k48k48k2k16k程序20k2k2k32k32k2k16k程序数据8k16k16kdaram5k10k10k6k6k8k8ksaram24k24k28rom空间交叉的条件mp位ovly位drom位禁止程序数据片内存储器空间29tms320c549存储器空间分配图30?c548和c549页扩展方法?对程序空间扩展31器件rommpmc0daramovly1saramovly1c54128k5kc5422k10kc5432k10kc54548k6kc54648k6kc5482k8k24kc54916k8k24k32片内rom分块的目的333435器件程序数据romdrom1daramsaramc5418k5kc54516k6kc54616k6k8k24kc54916k8k24k363738访问所需周期数39地址cpu寄存器名称地址cpu寄存器名称imr中断屏蔽寄存器12ar2辅助寄存器2ifr中断标志寄存器13ar3辅助寄存器3保留用于测试14ar4辅助寄存器4st0状态寄存器015ar5辅助寄存器5st1状态寄存器116ar6辅助寄存器6al累加器a低字17ar7辅助寄存器7ah累加器a高字18sp堆栈指针ag累加器a保护位19bk循环缓冲长度寄存器bl累加器b低字1abrc块重复计数器bh累加器b高字1brsa块重复起始寄存器bg累加器b保护位1crea块重复结束寄存器t暂存寄存器1dpmst处理器工作方式trn状态转移寄存器1expc程序计数器扩展10ar0辅助寄存器011ar1辅助寄存器11e1f保留4020

第2章 DSP芯片介绍

16 bit instructions defined parallel instructions

C55x C54x Mnemonic Mnemonic

Superset of 54x Mnemonic 8,16,24,32,40,48 bit instructions defined parallel instructions user defined parallel instructions

Low Power

Ch 3

Ch 4 Ch 5

•< 72 mW active power •144-pin LQFP •Ultra-small 144

Small Size

Байду номын сангаас

Addressing Unit 8 Auxiliary Registers 2 Addressing Units Power Management

WD Timer

Peripheral Bus

CAN 2.0B McBSP 2 SCI SPI A/D Converter

Peripheral s optimized for digital control

LF2407 Shown

12-Bits, 16 Channels

C2000系列MCU

Roadmap

Automotive - EPS Battery operated precision for steering

Tire Pressure Low cost pressure sensing based on tire rotation speed measurement

“Segway” Many new cool Application to come

DSP芯片的基本结构和特征ppt课件

• 学习DSP芯片的结构和特征,对于深入理解

DSP芯片的操作过程,掌握DSP芯片的开发 和应用技术具有很重要的意义

二、基本结构

程序 存储器

程序地址 发生单元

数据 存储器

外部存储器 接口

数据总线

程序总线

数据地址 发生单元

指令缓存

DMA 处理器

定时器

时钟单元

等待状态 发生器

DSP芯片的基本结构和特征

1. 引言 2. 基本结构 3. 中央处理单元CPU 4. 总线结构和流水线 5. 片内存储器 6. 片内外设

7. TI定点DSP芯片 8. TI浮点DSP芯片 9. 其他DSP芯片简介 10.小结 11.习题与思考题

一、引 言

• 在DSP芯片操作中,许多特殊功能是与DSP

C20x

(ns) (字) (字) (字) 串口 串口

C203

25/35/50

-

544

-

1

1

C204

25/35/50

4K

544

-

1

1

C205

25/35/50

-

4.5K

-

1

1

F206

25/35/50

-

4.5K

32 K

1

1

F207

25/35/50

-

4.5K

32 K

2

1

C209

35/50

4K

4.5K

-

-

-

七、TI定点DSP芯片

三、CPU

3.4 乘累加单元

CB15-CB0 DB15-DB0 PB15-PB0

40 累加器A

DSP芯片介绍(精)

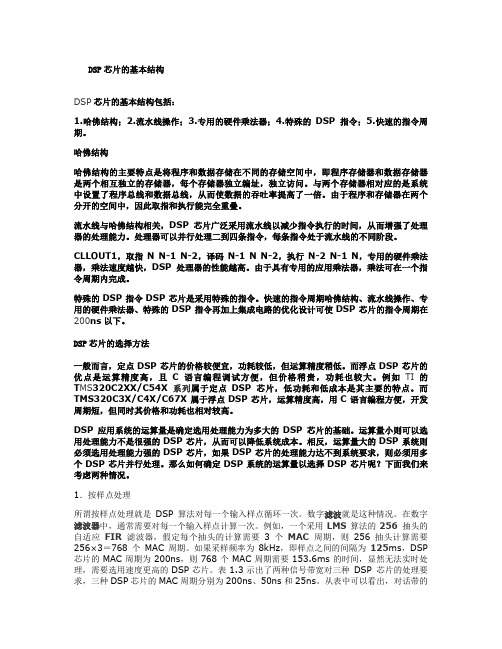

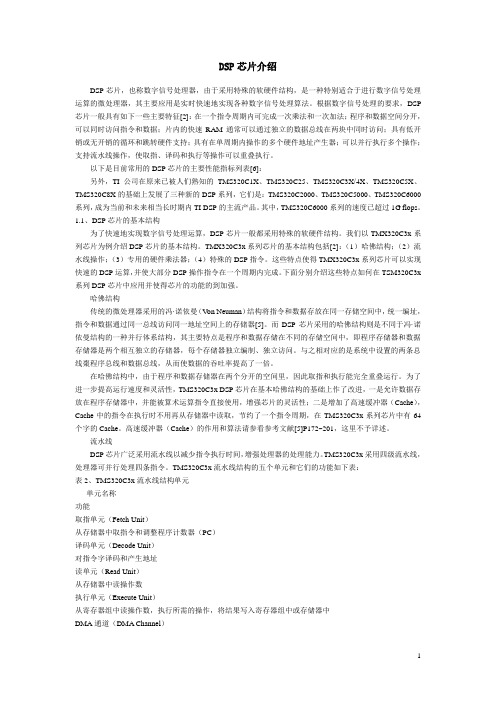

DSP 芯片介绍1 什么是DSP 芯片DSP 芯片,也称数字信号处理器,是一种具有特殊结构的微处理器。

DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP 指令,可以用来快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下的一些主要特点:(1)在一个指令周期内可完成一次乘法和一次加法。

(2)程序和数据空间分开,可以同时访问指令和数据。

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

(4)具有低开销或无开销循环及跳转的硬件支持。

(5)快速的中断处理和硬件I/O支持。

(6)具有在单周期内操作的多个硬件地址产生器。

(7)可以并行执行多个操作。

(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

2 DSP芯片的发展世界上第一个单片DSP 芯片是1978年AMI 公司宣布的S2811,1979年美国Iintel 公司发布的商用可编程期间2920是DSP 芯片的一个主要里程碑。

这两种芯片内部都没有现代DSP 芯片所必须的单周期芯片。

1980年。

日本NEC 公司推出的μPD7720是第一个具有乘法器的商用DSP 芯片。

第一个采用CMOS 工艺生产浮点DSP 芯片的是日本的Hitachi 公司,它于1982年推出了浮点DSP 芯片。

1983年,日本的Fujitsu 公司推出的MB8764,其指令周期为120ns ,且具有双内部总线,从而处理的吞吐量发生了一个大的飞跃。

而第一个高性能的浮点DSP 芯片应是AT&T公司于1984年推出的DSP32。

在这么多的DSP 芯片种类中,最成功的是美国德克萨斯仪器公司(Texas Instruments,简称TI)的一系列产品。

TI公司灾982年成功推出启迪一代DSP 芯片TMS32010及其系列产品TMS32011、TMS32C10/C14/C15/C16/C17等,之后相继推出了第二代DSP 芯片TMS32020、TMS320C25/C26/C28,第三代DSP 芯片TMS32C30/C31/C32,第四代DSP 芯片TMS32C40/C44,第五代DSP 芯片TMS32C50/C51/C52/C53以及集多个DSP 于一体的高性能DSP 芯片TMS32C80/C82等。

TMS320C28x系列芯片的结构及性能

TMS320C28x系列芯片的结构及性能TMS320C28x系列芯片是德州仪器(TI)推出的一系列数字信号处理器(DSP)芯片。

该系列芯片广泛应用于工业控制、汽车电子、通信等领域,具有强大的信号处理能力和低功耗特性。

下面将对TMS320C28x系列芯片的结构和性能进行详细介绍。

一、结构1.中央处理单元(CPU):TMS320C28x芯片采用了一片16位定点RISCCPU,在每个时钟周期可以处理两个16位整数运算,并且支持多达五个数据路径,每个数据路径可以携带两个16位数据。

这种设计方式既提高了运算速度,又降低了功耗。

2.存储器:TMS320C28x芯片内置了多种存储器,包括闪存、RAM和Boot ROM。

其中闪存用于存储程序代码和数据,RAM用于存储临时数据和变量,Boot ROM用于引导和初始化系统。

3.外设接口:TMS320C28x芯片支持多种外设接口,如通用I/O引脚、SPI、I2C、UART等,可以满足不同应用的需求。

此外,芯片还支持多种中断和定时器,并且提供了丰富的时钟控制功能。

4.调试接口:TMS320C28x芯片内置了调试接口,可用于程序的调试和性能分析。

开发者可以通过调试接口连接到芯片,并使用调试工具对程序进行分析和调试。

二、性能1.高性能浮点运算:TMS320C28x芯片支持单精度和双精度浮点运算,具有强大的浮点计算能力。

这使得芯片可以高效地处理各种复杂的信号处理算法,如滤波、变换等。

2.快速数据存取:TMS320C28x芯片具有低延迟的存储器访问和高速数据传输能力。

这使得芯片可以快速读写数据,提高了计算效率和响应速度。

3.高度并行处理:TMS320C28x芯片支持多达五个数据路径,并且每个数据路径可以同时携带两个16位数据。

这意味着芯片可以在一个时钟周期内同时处理多个数据,提高了计算效率。

4.低功耗设计:TMS320C28x芯片采用了低功耗设计,通过优化电路结构和算法,降低了功耗。

DSP各种知识点总结

1 DSP芯片的特点:(1).哈佛结构(程序空间和数据空间分开)(2).多总线结构.(3)流水线结构(取指、译码、译码、寻址、读数、执行)(4)多处理单元. (5)特殊的DSP指令(6).指令周期短. (7)运算精度高.(8)硬件配置强.(9)DSP最重要的特点:特殊的内部结构、强大的信息处理能力及较高的运行速度。

2 三类TMS320:(1)TMS320C2000适用于控制领域(2)TMS320C5000应用于通信领域(3)TMS320C6000应用于图像处理3 DSP总线结构:C54x片内有8条16位主总线:4条程序/数据总线和4条对应的地址总线。

1条程序总线(PB):传送自程序储存器的指令代码和立即操作数。

3条数据总线(CB、DB、EB):CB和EB传送从数据存储器读出的操作数;EB传送写到存储器中的数据。

4条地址总线(PAB、CAB、DAB、EAB)传送相应指令所需要的代码4存储器的分类:64k字的程序存储空间、64K字的数据存储空间和64K字的I/O空间(执行4次存储器操作、1次取指、2次读操作数和一次写操作数。

5存储器空间分配片内存储器的形式有DARAM、SARAM、ROM 。

RAM安排到数据存储空间、ROM构成程序存储空间。

(1)程序空间:MP/MC=1 40000H~FFFFH 片外MP/MC=0 4000H~EDDDH 片外FF00H~FFFFH 片内OVL Y=1 0000H~007FH 保留0080H~007FH 片内OVL Y=0 0000H~3FFFH片外(2)数据空间:DROM=1 F000H~F3FFH 只读空间FF00H~FFFH保留DROM=0 F000H~FEFFH 片外6数据寻址方式(1)立即寻址(2)绝对寻址<两位>(3)累加器寻址(4)直接寻址@<包换数据存储器地址的低7位>优点:每条指令只需一个字(5)间接寻址*按照存放某个辅助寄存器中的16位地址寻址的AR0~AR7(7)储存器映像寄存器寻址(8)堆栈寻址7寻址缩写语Smem:16位单寻址操作数Xmem Ymem 16位双dmad pmad PA16位立即数(0-65535)scr源累加器dst目的累加器lk 16位长立即数8状态寄存器ST0 15~13ARP辅助寄存器指针12TC测试标志位11C进位位10累积起A 的一出标志位OV A 9OVB 8~0DP数据存储器页指针9状态寄存器ST1 CPL:直接寻址编辑方式INTM =0开放全部可屏蔽中断=1关闭C16 双16位算数运算方式10定点DSP 浮点DSP:定点DSP能直接进行浮点运算,一次完成是用硬件完成的,而浮点需要程序辅助。

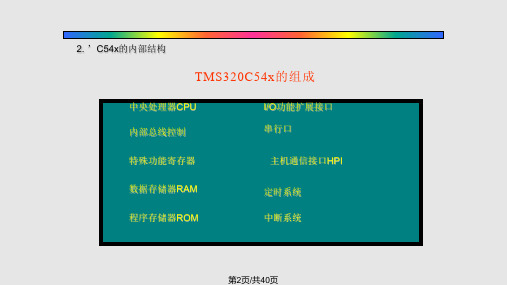

DSP第2章 'C54x的硬件结构2

2013年8月15日

DSP原理及应用

6

3.工作方式状态寄存器PMST

主要设定和控制处理器的工作方式和存储器的配置,反映 处理器的工作状态。

15~7 6 5 4 AVIS 3 2 1 0 SST

IPTR MP/MC OVLY

DROM CLKOFF SMUL

中 断 向 量 指 针

CPU 工 作 方 式 选 择 位

③ 暂存器SPRAM。

2013年8月15日

DSP原理及应用

14

特殊功能寄存器

功能:主要用于程序的运算处理和寻址方式的选

择和设定。地址范围:0000H~001FH。 外设寄存器 ’C5402的CPU寄存器共有27个,CPU访问这 功能:用来控制片内外设电路的状态和存放数据。 些寄存器时,不需要插入等待时间。 地址范围:0020H~005FH。 包括串行口通信控制寄存器组、定时器定时控 暂存器SPRAM 制寄存器组、时钟周期设定寄存器组等。 功能:用来暂存变量。地址范围:0060H~007FH。

中断屏蔽寄存器 10H 中断标志寄存器 11H 保留 ( 用于测试 ) 12H 保留 ( 用于测试 ) 13H 保留 ( 用于测试 ) 14H 保留 ( 用于测试 ) 15H 状态寄存器0 16H 状态寄存器1 17H 累加器A低字(15~0位) 18H 累加器A高字(31~16位) 19H 累加器A保护位(39~32位) 1AH 累加器B低字(15~0位) 1BH 累加器B高字(31~16位) 1CH 累加器B保护位(39~32位) 1DH 暂存寄存器 1EH DSP原理及应用 状态转移寄存器 1FH

2013年8月15日

存储器映像的CPU寄存器, 存储器映像的外设寄存器 特殊功能寄存器

DSP 第二章 DSP芯片的基本结构和特征

1.存储器分配 TMS320C25具有4K字的片内程序ROM和544字的片内RAM。 RAM分为三块:B0、B1、B2。其中,B0块(256字)既可 配置为数据存储器(用CNFD指令),也可配置为程序存储器 (用CNFP指令)。其余288字(B1和B2块)只能是数据存储器。 544字的片内RAM可使C25能处理512字的数据阵列,如可进行 256点复数FFT运算,且尚有32字用作中间结果的暂存。 TMS320C25提供片外可直接寻址的程序和数据空间各64K字。 寄存器组包含8个辅助寄存器(AR0~AR7),它们可用作数据 存储器的间接寻址和暂存,从而增加芯片的灵活性和效率。这 些寄存器既可用指令直接寻址,也可用3比特的辅助寄存器指针 (ARP)间接寻址。辅助寄存器和ARP既可从数据存储器装数, 也可装入立即数。寄存器的内容也可存入数据存储器中。辅助 寄存器组与辅助寄存器算术单元(ARAU)相连接,用ARAU访 问信息表无需CALU参与地址操作,这样可让CALU进行其他操 作。

在哈佛结构中:由于程序和数据存储器 在两个分开的空间中,因此取指和执行能完全 重叠运行。 TMS320系列DSP芯片在基本哈佛结构的基础 上作了改进: 一是允许数据存放在程序存储器中,并被算 术运算指令直接使用,增强了芯片的灵活性; 二是指令存储在高速缓冲器(Cache)中,当 执行此指令时,不需要再从存储器中读取指令, 节约了一个指令周期的时间。如TMS320C30具 有64个字的Cache。进一步提高了运行速度和灵

2.2.4 特殊的DSP指令DSP芯片的另一个特征:特殊的指令。 指令DMOV:它完成数据移位功能。在数字信号处理中, 延迟操作非常重要,这个延迟就是由DMOV来实现的。 指令LTD:它在一个指令周期内完成LT、DMOV和 APAC(将乘法结果加到ACC中 )三条指令。 指令FIRS:

TMS320系列DSP芯片介绍

● 4.程序存储器寻址

● 使用程序计数器(PC)寻址,但是,对于一些指令需要用到绝对寻址。

● 5.中断

● 54X支持软件中断(如INTR,TRAP,RESET)和硬件中断,中断 可分为可屏蔽中断(如TINT,INT0等)和不可屏蔽中断(如 RESET和NMI),其中RESET的优先级最高,不可屏蔽中断的优 先级高于可屏蔽中断的优先级,硬件中断的优先级则高于软件中断 的优先级。

● 9.片上的外设

● 可软件编程的等待状态发生器,使得与速度较慢的设备通讯更加方 便;

● 片上的锁相环时钟发生器可以对外部时钟信号进行倍频或分频,从 而得到自己所需要的时钟频率,当分频时还可节省系统的功耗;

● 可以禁止对外部数据总线,地址总线以及控制信号的控制; ● 可以软件编程的定时器;

● 一些特殊的端口:标准的同步全双工串行口和时分复用(TDM)串 行口,自动缓冲串行口(auto-BSP),多通道缓冲串行口 (MCBSP),直接内存访问(DMA)控制器和与外部处理器通信 的HPI(Host Port Interface)接口。每一个型号的芯49.1标准的边界扫描逻辑 接口,即JTAG扫描逻辑电路,用于仿真和测试,可以实现在线仿真。

TMS320C54X的BOOT设计

● 由于直接将程序写入DSP芯片非常困难,所以TMS320C54X DSP 芯片都在片内设置有BOOT程序,它的主要作用是在开机时将用户 程序从外部装入到程序存储器。

。在一般形式的FIR滤波

器中,乘法是DSP的重要组成部分。在TMS320系列中,由于具有 专用的硬件乘法器,乘法可以在一个指令周期内完成。这样可以大 量降低FIR的计算时间。

特殊的DSP指令 ● 4.

。在TMS320系列中有一些特

DSP原理及应用DSP芯片的硬件结构节讲稿

特殊功能 寄存器

TMS320C54x的硬件结构图

PAB

程序存储器

PB

数据存储器

CAB

串行口

CB

并行口

DAB

定时器

DB

计数器

EAB

中断

EB

外部 存储器 接口

外部 设备 接口

乘法

C累PU加器

算术/逻辑 运算单元

比较器

桶形 移位器

第3页/共40页

2.2 ’C54x的主要特性和外部引 脚2.2.1 ’C54x的主要特性 1、CPU 2、存储器 3、指令系统 其特性还将在后面章节专门介绍

1 9 BIT0 1 8 BIT1 1 7 BIT2 1 6 BIT3 1 5 BIT4 1 4 BIT5 1 3 BIT6 1 2 BIT7

10

GND

GND

15 14 13 12 11 10 9 7

SEG0 1 1 SEG1 7 SEG2 4 SEG3 2 SEG4 1 SEG5 1 0 SEG6 5 SEG7 3

SEG0 1 1 SEG1 7 SEG2 4 SEG3 2 SEG4 1 SEG5 1 0 SEG6 5 SEG7 3

U2 A 2

3

7 4HC0 2 1

U2 B 5

6

7 4HC0 2 4

U2 C 8

9

7 4HC0 2 10

U2 D 11

12

7 4HC0 2 13

a

DS1

b

c

d

e

f

g

dp

a

DS2

b

c

d

第32页/共40页

8. 测试引脚 TCK:测试时钟输入引脚; TDI:测试数据输入引脚; TDO:测试数据输出引脚; TMS:测试方式选择引脚; TRST:测试复位引脚; EMU0:仿真器中断0引脚; EMU1/OFF:仿真器中断1引脚/关断所有 输出引脚。

2DSP芯片(TMS320DM642)概述

第 2 章TMS320C6000 DSP 芯片概述本章介绍了TI公司是DSP芯片和DSP芯片的命名规则,并着重介绍了TMS320DM642的器件特性及总体原理框图。

本章的知识要点为理解TMS320DM6 4的原理框图构成,本章建议安排 2 个课时进行学习。

2.1 DSP 芯片概述随着信息技术的高速发展,数字信号处理器(Digital Signal Processor,DSP)的应用范围越来越广,普及率越来越高。

DSP的应用领域主要包括:图形图像领域(如图形变换、图像压缩、图像传输、图像增强、图像识别等)、自动化控制领域(如导航和定位、振动分析、磁盘驱动、激光打印、机器人控制等)、消费电力领域(如智能玩具、扫描仪、机顶盒、VCD/DVD 可视电话、传真机等)、电子通信领域(如蜂窝电话、IP电话、无线调制解调器、数字语音嵌入等)、语音处理领域(如语音综合、语音增强、语音识别、语音编码等)、工业应用领域(如数字控制、机器人技术、在线监控等)、仪器仪表领域(如数字滤波器、函数发生器、瞬时分析仪、频谱分析仪、数据采集仪器等)、医疗器械领域(如诊断设备、助听器、病情监控器、心电图设备、超声设备等)、军事领域(如导弹制导、导航、雷达、保密通信等)。

因此,DSP 在当今电子通信类产品中起到了不可或缺的作用。

2.1.1 主要类型DSP 芯片主要分为以下两大类:(1)专用DSP芯片。

这类芯片被设计和加工成独立的电路模块,只能完成功能单一的任务,它们的使用场合比较特殊,通常应用于高速信号处理环境中,如执行FFT运算、数值滤波运算、卷积运算等,专用DSP芯片通过硬件逻辑实现信号处理算法,而不是采用内部编程的方法,这种机制保证了专用DSP芯片的执行效率、提高了其运算速度,专用DSP芯片在应用中无须程序设计。

只要根据其功能设计外围电路即可。

(2)通用可编程数字信号处理器(Programmable Digital Signal Processor)。

DSP芯片的基本结构和特征

DSP芯片的基本结构和特征引言DSP芯片(Digital Signal Processor,数字信号处理器)是一种专用于数字信号处理任务的微处理器。

它具有高处理速度和低功耗等特点,广泛应用于音频、视频、通信、雷达、图像处理等领域。

本文将介绍DSP芯片的基本结构和特征,以便读者更好地了解和应用该技术。

1. DSP芯片的基本结构DSP芯片的基本结构通常包括三个主要部分:中央处理单元(CPU)、存储器和数字信号处理模块。

下面将详细介绍这些部分的功能和特点。

1.1 中央处理单元(CPU)中央处理单元是DSP芯片的核心,负责控制和执行指令。

它通常由一个或多个运算单元(ALU)和一个控制单元组成。

ALU负责执行算术和逻辑运算,而控制单元则负责解码和执行指令序列。

中央处理单元是DSP芯片实现高速运算的关键部分。

1.2 存储器存储器是DSP芯片的重要组成部分,用于存储程序代码、数据和中间结果。

它通常包括两种类型的存储器:指令存储器(程序存储器)和数据存储器。

指令存储器用于存储程序代码和指令,而数据存储器用于存储数据和中间结果。

存储器的大小和访问速度对DSP芯片的性能有重要影响。

1.3 数字信号处理模块数字信号处理模块是DSP芯片的核心功能模块,用于执行数字信号处理任务。

它通常包括以下几个功能单元:时钟和定时器单元、数据通路单元、乘法器和累加器(MAC)单元以及控制逻辑单元。

时钟和定时器单元用于提供时序控制和定时功能,数据通路单元用于数据传输和处理,乘法器和累加器单元用于高速乘加运算,控制逻辑单元用于控制和协调各个功能单元的操作。

2. DSP芯片的特征DSP芯片相较于通用微处理器具有一些明显的特征,下面将介绍几个主要特征。

2.1 高速运算能力DSP芯片具有高速运算能力,主要得益于其专门的运算单元和并行处理能力。

相较于通用微处理器,DSP芯片能够更快地执行算术和逻辑运算,满足实时信号处理的需求。

2.2 低功耗设计DSP芯片在设计过程中注重功耗的控制,以满足移动设备和嵌入式系统等低功耗应用的需求。

DSP芯片的基本结构(精)

DSP芯片的基本结构DSP芯片的基本结构包括:1.哈佛结构;2.流水线操作;3.专用的硬件乘法器;4.特殊的DSP指令;5.快速的指令周期。

哈佛结构哈佛结构的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

与两个存储器相对应的是系统中设置了程序总线和数据总线,从而使数据的吞吐率提高了一倍。

由于程序和存储器在两个分开的空间中,因此取指和执行能完全重叠。

流水线与哈佛结构相关,DSP芯片广泛采用流水线以减少指令执行的时间,从而增强了处理器的处理能力。

处理器可以并行处理二到四条指令,每条指令处于流水线的不同阶段。

CLLOUT1,取指 N N-1 N-2,译码 N-1 N N-2,执行 N-2 N-1 N,专用的硬件乘法器,乘法速度越快,DSP处理器的性能越高。

由于具有专用的应用乘法器,乘法可在一个指令周期内完成。

特殊的DSP指令DSP芯片是采用特殊的指令。

快速的指令周期哈佛结构、流水线操作、专用的硬件乘法器、特殊的DSP指令再加上集成电路的优化设计可使DSP芯片的指令周期在200ns以下。

DSP芯片的选择方法一般而言,定点DSP芯片的价格较便宜,功耗较低,但运算精度稍低。

而浮点DSP芯片的优点是运算精度高,且C语言编程调试方便,但价格稍贵,功耗也较大。

例如TI的T MS320C2XX/C54X系列属于定点DSP芯片,低功耗和低成本是其主要的特点。

而TMS320C3X/C4X/C67X属于浮点DSP芯片,运算精度高,用C语言编程方便,开发周期短,但同时其价格和功耗也相对较高。

DSP应用系统的运算量是确定选用处理能力为多大的DSP芯片的基础。

运算量小则可以选用处理能力不是很强的DSP芯片,从而可以降低系统成本。

相反,运算量大的DSP系统则必须选用处理能力强的DSP芯片,如果DSP芯片的处理能力达不到系统要求,则必须用多个DSP芯片并行处理。

DSP原理及结构PPT课件

(8)军事与尖端科技:雷达和声纳信号处理、雷达成像、导弹制导等。 (9)计算机与工作站:计算机加速卡、图形加速卡。 (10)消费电子:数字电视、图形/声音压缩解压装置。

第11页/共87页

4、DSP产品的现状 定点DSP有200多种,浮点DSP有100多种。主要生产:TI 公司、

单3.3V电压输出:TI公司的TPS7133、TPST7233 单电源可调电压输出:TI公司的TPS7101、TPST7201 双电源输出(两路输出的芯片):TPS73H301、TPS73H325、TPS73H318

第44页/共87页

(5)3.3V和5V混合逻辑系统设计 各种电平转换标准

第45页/共87页

第35页/共87页

(3)加电次序 理想情况下,两个电源应同时加电,但在一些场合很难做到。不同型号器件上电顺序不一样。

第36页/共87页

TMS320VC5402与大多数DSP芯片的上电 顺序:

低电压电源CVdd先上电;高电压电源 DVdd后电压;

高电压电源DVdd先断电;低电压电源 CVdd后断电;

列处理器的指令周期已经从第一代的200ns降至20ns以下。快速的指令周 期使DSP芯片能够实时实现许多DSP应用

第30页/共87页

二、TMS320系列DSP的结构 第31页/共87页

1、多总线结构 由哈佛结构决定了具有独立的程序总线和数据总线,以及独立的程序

存储器和数据存储器,这样就可以同时获得指令字和操作数互不干扰,即一 个指令周期内可以同时准备好指令和操作数。

*若不遵照此次序,那么CVdd与DVdd的差 值必须小于2.8V。

TMS320VC549具有静电保护结构,所以上 电 顺 序 与 上 相 反 。第37页/共87页

DSP芯片介绍

DSP芯片介绍DSP芯片,也称数字信号处理器,由于采用特殊的软硬件结构,是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP 芯片一般具有如下一些主要特征[2]:在一个指令周期内可完成一次乘法和一次加法;程序和数据空间分开,可以同时访问指令和数据;片内的快速RAM通常可以通过独立的数据总线在两块中同时访问;具有低开销或无开销的循环和跳转硬件支持;具有在单周期内操作的多个硬件地址产生器;可以并行执行多个操作;支持流水线操作,使取指、译码和执行等操作可以重叠执行。

以下是目前常用的DSP芯片的主要性能指标列表[6]:另外,TI公司在原来已被人们熟知的TMS320C1X、TMS320C25、TMS320C3X/4X、TMS320C5X、TMS320C8X的基础上发展了三种新的DSP系列,它们是:TMS320C2000、TMS320C5000、TMS320C6000系列,成为当前和未来相当长时期内TI DSP的主流产品。

其中,TMS320C6000系列的速度已超过1G flops。

1.1、DSP芯片的基本结构为了快速地实现数字信号处理运算,DSP芯片一般都采用特殊的软硬件结构。

我们以TMX320C3x系列芯片为例介绍DSP芯片的基本结构。

TMX320C3x系列芯片的基本结构包括[2]:(1)哈佛结构;(2)流水线操作;(3)专用的硬件乘法器;(4)特殊的DSP指令。

这些特点使得TMX320C3x系列芯片可以实现快速的DSP运算,并使大部分DSP操作指令在一个周期内完成。

下面分别介绍这些特点如何在TSM320C3x 系列DSP芯片中应用并使得芯片的功能的到加强。

哈佛结构传统的微处理器采用的冯·诺依曼(V on Neuman)结构将指令和数据存放在同一存储空间中,统一编址,指令和数据通过同一总线访问同一地址空间上的存储器[5]。

第2章 DSP芯片结构介绍

32位长操作数指令。 同时读入两个或3个操作数的指令。 并行存储和并行加载的算术指令。(ST//LD) 条件存储指令。(SACCD有条件存储累加器的值) 从中断快速返回指令。(RETF)

例:32位长操作数 12345678h 0100h 0101h 1234 5678 高位 低位

在片外围电路ຫໍສະໝຸດ 2. 程序存储器C54x有64K程序存储空间。C54x的 片内ROM、DARAM、SARAM都 可以映像到程序空间,取决于 PMST的MP/MC位和OVLY位的设 置。 C54x的片内ROM容量大的有28K 字或48K字,小的只有2K字。容量 大的片内ROM可以存放用户程序, 但其高2K字(F800h~FFFFh)中 的内容由TI公司定义。

C54x片内存储器:

1.存储器空间

处理器方式状态寄存器PMST 15~7 6 5 4 3 2 1 0

IPTR

MP/MC OVLY

AVIS

DROM

CLKOFF

SMUL SST

MP/MC位:

若MP/MC=0,则片内ROM安排为程序空间。 若MP/MC=1,则片内ROM不安排为程序空间。 若OVLY=1,则片内RAM安排为程序和数据空间。 若OVLY=0,则片内RAM只安排为数据空间。 若DROM=1,则部分片内ROM安排为数据空间。 若DROM=0,则片内ROM不安排为数据空间。

TMS320C54X的内部硬件组成框图

第一节 TMS320C54x芯片的基本性能

CPU

先进的多总线结构。 40位算术逻辑运算单元(ALU),40位桶形移位器,两个40位累 加器。 17位×17位并行乘法器与40位专用加法器相连。 比较、选择、存储单元(CSSU)。 指数编码器:可以在单个周期内计算40位累加器中数值的指数。 双地址生成器:包括8个辅助寄存器和两个辅助寄存器算术运算单 元(ARAU)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

定时寄存器

25

PRD

定时周期寄存器

26

TCR

定时控制寄存器

27

-

保留

28

SWWSR 软件等待状态寄存器

29

BSCR

块切换控制寄存器

2A~2F

-

保留

30

DRR1

串行端口1数据接收寄存器

31

DXR1

串行端口1数据发送寄存器

32

SPC1

串行端口1数据控制寄存器

40

33~5F

-

保留

第五节 在片外围电路

不同 子系列 器件 差别

BK(循环缓冲长度寄存器)

BRC(块重复计数器)

RSA(块重复起始寄存器)

REA(块重复结束寄存器) PMST(处理器工作方式)

XPC(程序计数器扩展)

39

保留

地址

名称

说明

20

DRR0

串行端口0数据接收寄存器

21

DXR0

串行端口0数据发送寄存器

22

SPC0

串行端口0数据控制寄存器

23

-

保留

24

TIM

32

高端2K字的利用

33

3.数据存储器

RAM(SARAM) 数据存储器类型 RAM(DARAM)

片内ROM(软件映像)

片内/片外数据存储器的识别

34

器件 C541 C542 C543 C545 C546 C548 C549

程序/数据

ROM

DROM=1

8K

-

-

16K

16K

-

16K

DARAM 5K 10K 10K 6K 6K 8K 8K

SARAM -

24K 24K 35

RAM分块目的

36

DARAM前1K数据存储器的配置

37

4.存储器映像寄存器

• 位置 • 作用 • 访问所需周期数

38

地址

0 1 2~5 6 7 8 9 A B C D E F 10 11

CPU寄存器名称

IMR(中断屏蔽寄存器) IFR(中断标志寄存器) 保留(用于测试) ST0(状态寄存器0) ST1(状态寄存器1) AL(累加器A低字) AH(累加器A高字) AG(累加器A保护位) BL(累加器B低字) BH(累加器B高字) BG(累加器B保护位) T(暂存寄存器)

使TDDR初始化 令TSS位为0 TRB位置1

46

开放定时中断 (假定INTM=1)

1)将中断标志寄存器IFR中的TINT位置1, 清除尚未处理完的定时器中断。

2)将中断屏蔽寄存器IMR中的TINT位置1, 开放定时中断。

3)将ST1中的INTM位清0,从整体上开放中 断。

47

编程举例

STM #0000h,SWWSR ;不插等待周期

31~ 16 AH

高阶位

15~ 0 AL

低阶位

O页存储器

11

3.桶形移位器的功能

要

• 什么是定标

点

• 移位处理的作用

• 归一化的作用

• 为何要扩展符号位

12

4.乘法器/加法器

• 结构 • 功能 • 什么是舍入处理 • 饱和处理的优点 • 数据流向

17X17乘法 40位加法

检零 饱和 取整

13

5.比较、选择和存储单元

PLL 工作方式

55

设计举例

• 如 果 要 从 DIV 方 式 转 到 PLL×3 方 式 , 已 知 CLKIN的频率为13MHz,PLLCOUNT=41(十进制 数),只要在程序中加入如下指令即可:

工作频率=外时钟×1.5

工作频率=外时钟/2

选择方案2

工作频率=外时钟 ×5 工作频率=外时钟 × 工4作 频 率 = 内 时 钟 ×5 工作频率=外时钟 4.5 工作频率=外时钟/2

工作频率=内振荡器/2 工作频率=外时钟×1 停止方式

工作频率=内振荡器/2

工作频率=外时钟

×1

停止方式

51

(2)软件可编程PLL

5 4~0

BRAF CPL XF HM INTM 0 OVM SXM C16 FRCT CMPT ASM

18

(3)处理器工作方式状态寄存器(PMST)

15~ 7 IPTR

6

5

4

3

2

1

0

MP/MC OVLY AVIS DROM CLKOFF SMUL SST

如何将40位数据饱和处理成32位数

19

第三节 内部总线结构

ROM MP/MC=0

28K

DARAM OVLY=1

5K

SARAM OVLY=1

-

C542

2K

10K

-

C543

2K

10K

-

C545

48K

6K

-

C546

48K

6K

-

C548

2K

8K

24K

C549

16K

8K

24K

31

• 片内存储器作为程序存储器条件 • 外部存储器作为程序存储器条件 • 片内ROM分块的目的

1

0

0

4000h 工频=内振荡器/2

1

1

0

6000h 工频=外时钟/2

1

1

1

7000h 工频=内振荡器/2

1

0

1

0007h 工频=外时钟×1

0

1

1

-

停止方式 54

锁定定时器

• 工作方式 • 锁定延时时间的设定 • PLLCOUNT的数值设定

DIV 工作方式

锁定定时器工作

时钟发生器 按DIV方式工作

通用I/O引脚XF 定时器 时钟发生器 主机接口 软件可编程等待状态发生器 可编程分区开关 串行口

41

一、通用I/O引脚

特点 XF 发信号

SSBX XF RSBX XF

BIO 收信号

XC 2,BIO

42

功能 结构图

二、定时器

工作过程

43

定时器寄存器(TIM)

主要 部件

定时器周期寄存器(PRD) 定时器控制器寄存器(TCR)

27

1.存储器空间的划分与交叉

片内存储器 类型

• DARAM • SARAM • ROM

空间 MP/位

使能

程序

交叉 OVLY位 的条件 DROM位

禁止

数据 片内存储器空间

28

TMS320C549存储器空间分配图

29

•C548和C549页扩展方法 •对程序空间扩展

30

2.程序存储器

器件 C541

26

存储器型式 C541 C542 C543 C545 C546 C548 C549

ROM

28K 2K

2K 48K 48K 2K 16K

程序

20K 2K

2K 32K 32K 2K 16K

程序/数据

8K

0

0

16K 16K

0

0

DARAM♀ 5K 10K 10K 6K

6K

8K

8K

SARAM♀

0

0

0

0

0

24K 24K

DSP技术及应用

Digital Signal Processor 数字信号处理器 樊松 讲师

电子与信息工程学院电气工程系

1

第二章 DSP芯片结构介绍

第一节 基本性能 第六节 串行口

第二节 CPU结构

第七节 与外设的接口

第三节 内部总线结构 第八节 复位与省电

第四节 存储器结构 第九节 中断

第五节 在片外围电路 第十节 自举加载

时钟工作方式寄存器(CLKMD)

作用

15~ 12 11 10 ~ 3

2

1

0

PLL PLL PLL PLL PLL PLL

MUL DIV COUNT ON/OFF NDIV STATUS

乘数

除数 计数器

通/断位 时钟发生 工作状 器选择位 态位

52

软件编程时钟方式

• 第一:PLL方式 • 第二:DIV方式

A

B

桶形移位器

• 结构 • 功能

MUX

COMP TRN TC CSSU

S MSW/LSW

选择 16

EB15~ EB0

14

2*J M1(尺度1)

2*J+1 M2(尺度2)

D1

N1

J D2

D2

N2

D1

J+8

CMPS A,*AR1

If (M1+D1)>(M2+D2) then N1= M1+D1 Else

N1= M2+D2

;如果A(31~16)>A(15~0)

;则A(31~16)->*AR1,

;TRN左移1位,0->TRN(0),0->TC

;否则A(15~0)->*AR1,TRN左移1位,

;1->TRN(0),1->TC

15

6.指数编码器

• 结构 • 功能

要点

A

B

EXP指数编码器

T寄存器

如何计算指数

一、哈佛结构

特点 与 区别

冯•诺依曼 结构

程序/数据存储器

CPU

24

对存储器空间分配的不同考虑

特点 与 区别

哈佛结构 改善的哈佛结构

程序存储器

CPU

数据存储器

25

二、哈佛结构存储空间分配

空 64K字程序存储空间 DARAM