基于labview的模拟2位7段数码管设计

七段数码管实验源程序及电路仿真图

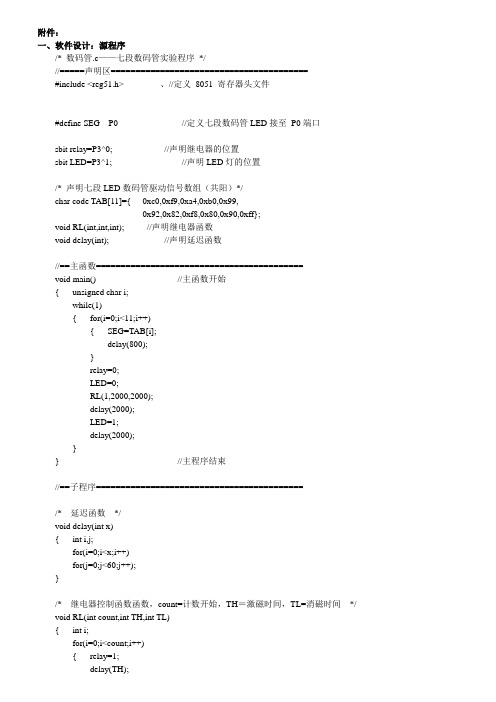

附件:一、软件设计:源程序/* 数码管.c——七段数码管实验程序*///=====声明区========================================#include <reg51.h> 、//定义8051 寄存器头文件#define SEG P0 //定义七段数码管LED接至P0端口sbit relay=P3^0; //声明继电器的位置sbit LED=P3^1; //声明LED灯的位置/* 声明七段LED数码管驱动信号数组(共阳)*/char code TAB[11]={ 0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90,0xff};void RL(int,int,int); //声明继电器函数void delay(int); //声明延迟函数//==主函数==========================================void main() //主函数开始{ unsigned char i;while(1){ for(i=0;i<11;i++){ SEG=TAB[i];delay(800);}relay=0;LED=0;RL(1,2000,2000);delay(2000);LED=1;delay(2000);}} //主程序结束//==子程序==========================================/* 延迟函数*/void delay(int x){ int i,j;for(i=0;i<x;i++)for(j=0;j<60;j++);}/* 继电器控制函数函数,count=计数开始,TH=激磁时间,TL=消磁时间*/ void RL(int count,int TH,int TL){ int i;for(i=0;i<count;i++){ relay=1;delay(TH);relay=0;delay(TL);}}二、硬件设计:程序开始运行时,数码管开始计数从0到9:数码管从0计数到9时,数码管停止计数,随后继电器工作驱动LED灯亮:。

基于labview的数字钟

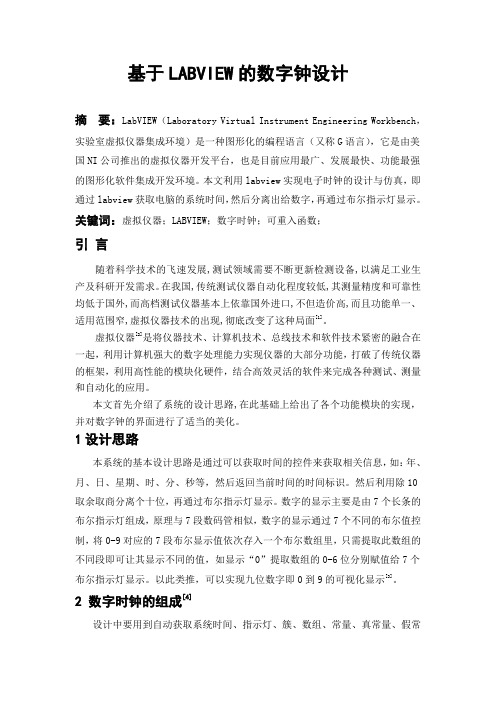

基于LABVIEW的数字钟设计摘要:LabVIEW(Laboratory Virtual Instrument Engineering Workbench,实验室虚拟仪器集成环境)是一种图形化的编程语言(又称G语言),它是由美国NI公司推出的虚拟仪器开发平台,也是目前应用最广、发展最快、功能最强的图形化软件集成开发环境。

本文利用labview实现电子时钟的设计与仿真,即通过labview获取电脑的系统时间,然后分离出给数字,再通过布尔指示灯显示。

关键词:虚拟仪器;LABVIEW;数字时钟;可重入函数;引言随着科学技术的飞速发展,测试领域需要不断更新检测设备,以满足工业生产及科研开发需求。

在我国,传统测试仪器自动化程度较低,其测量精度和可靠性均低于国外,而高档测试仪器基本上依靠国外进口,不但造价高,而且功能单一、适用范围窄,虚拟仪器技术的出现,彻底改变了这种局面[1]。

虚拟仪器[2]是将仪器技术、计算机技术、总线技术和软件技术紧密的融合在一起,利用计算机强大的数字处理能力实现仪器的大部分功能,打破了传统仪器的框架,利用高性能的模块化硬件,结合高效灵活的软件来完成各种测试、测量和自动化的应用。

本文首先介绍了系统的设计思路,在此基础上给出了各个功能模块的实现,并对数字钟的界面进行了适当的美化。

1设计思路本系统的基本设计思路是通过可以获取时间的控件来获取相关信息,如:年、月、日、星期、时、分、秒等,然后返回当前时间的时间标识。

然后利用除10取余取商分离个十位,再通过布尔指示灯显示。

数字的显示主要是由7个长条的布尔指示灯组成,原理与7段数码管相似,数字的显示通过7个不同的布尔值控制,将0-9对应的7段布尔显示值依次存入一个布尔数组里,只需提取此数组的不同段即可让其显示不同的值,如显示“0”提取数组的0-6位分别赋值给7个布尔指示灯显示。

以此类推,可以实现九位数字即0到9的可视化显示[3]。

2 数字时钟的组成[4]设计中要用到自动获取系统时间、指示灯、簇、数组、常量、真常量、假常量、加减乘除、条件判断、case结构等控件,主要由以下模块组成。

七段数码管驱动电路设计

七段数码管驱动电路设计说起这七段数码管驱动电路设计,咱们得先来聊聊它是个啥宝贝。

想象一下,那些电子钟、计算器上闪烁的数字,还有咱们游戏机上计分用的那些酷炫数字,它们背后可都离不开这七段数码管的默默付出。

今儿个,咱们就来手把手,用大白话聊聊怎么给这七段数码管搭个温馨的小窝,让它能在咱的电路世界里大放异彩。

一、初探七段数码管首先,咱们得认识这位主角——七段数码管。

它呀,就像是个简约版的霓虹灯,由七条线段(a到g)和一个小数点组成,通过不同的组合,能显示出0到9这十个数字,外加一些简单的字符。

想象一下,这七条线段就像是小朋友手里的画笔,一笔一划地勾勒出数字的模样,多有趣!1.1 挑选合适的数码管挑数码管,得看看它是共阳极的还是共阴极的。

这就像选房子,有的房子阳台朝南采光好(共阳极),有的则朝北凉爽些(共阴极)。

选对了,后续设计才省心。

1.2 理解工作原理数码管工作的秘密在于电流。

咱们通过控制哪些线段通电,哪些不通电,来“画”出不同的数字。

这就像是在玩灯光秀,开灯关灯之间,数字就活灵活现地出现了。

二、设计驱动电路接下来,就是给数码管找个好搭档——驱动电路。

这就像是给数码管找了个司机,告诉它啥时候该亮,啥时候该暗。

2.1 选择驱动芯片市面上有好多驱动芯片,比如74HC595、TM1637等,它们就像是不同类型的汽车,有的省油(功耗低),有的跑得快(驱动能力强)。

咱们得根据实际需求,挑个最合适的。

2.2 搭建电路框架搭电路就像搭积木,把电源、驱动芯片、数码管还有必要的电阻电容按规矩摆好。

电源是心脏,驱动芯片是大脑,数码管是显示屏,电阻电容则是调节器,保证电路稳定运行。

2.3 编程控制电路搭好了,还得给它编个程序,告诉它怎么工作。

这就像是在教小朋友跳舞,一步步指导它怎么迈步、转身。

编程时,咱们得设定好每个数字对应的线段组合,让数码管能按咱们的意愿显示。

三、调试与优化电路搭完,程序编好,接下来就是见证奇迹的时刻了。

实验五-7段数码显示译码器设计

实验五7段数码显示译码器设计实验报告一、实验要求1、GW48实验箱2、写出7段数码显示译码器程序3、总结实验步骤和实验结果二、实验内容1、说明例中各语句的含义,以及该例的整体功能。

在max+plus2或quartus2上对以下该例进行编辑、编译、综合、适配仿真,给出其所有信号的时序仿真波形。

module zdw(in,out);output [6:0]out;input [3:0]in;reg[6:0]out;always@(in)begincase(in)4'd0: out=7'b1111110;4'd1: out=7'b0110000;4'd2: out=7'b1101101;4'd3: out=7'b1111001;4'd4: out=7'b0110011;4'd5: out=7'b1011011;4'd6: out=7'b1011111;4'd7: out=7'b1110000;4'd8: out=7'b1111111;4'd9: out=7'b1111011;4'd10: out=7'b1110111;4'd11: out=7'b0011111;4'd12: out=7'b1001110;4'd13: out=7'b0111101;4'd14: out=7'b1001111;4'd15: out=7'b1000111;default: out=7'bx;endcaseendendmodule2、引脚锁定以及硬件下载测试。

建议选实验电路模式6,用数码8显示译码输出(PIO46—PIO40)。

键8,键7,键6,键5四位控制输入,硬件验证译码器的工作性能。

Quartus ii 11.0 Qsys实现7段数码管实验

cnt[0]++; // 10 进制 if( 10 == cnt[0] ) { cnt[0] = 0; cnt[1] ++; } if( 6 == cnt[1] ) { cnt[1] = 0; cnt[2] ++; } if( 10 == cnt[2] ) { cnt[2] = 0; cnt[3] ++; } if( 6 == cnt[3] ) { cnt[3] = 0; } // 清除中断标志寄存器 IOWR_ALTERA_AVALON_TIMER_STATUS( TIMER_BASE, 0x00 ); }

Qsys 中:

原理图:

Nios 代码:

/******************************** Includes ********************************/ #include "system.h" #include "altera_avalon_pio_regs.h" #include "altera_avalon_timer_regs.h" #include "alt_types.h" #include "sys/alt_irq.h"

alt_ic_isr_register( TIMER_IRQ_INTERRUPT_CONTROLLER_ID, TIMER_IRQ,

{ IOWR_ALTERA_AVALON_TIMER_STATUS( TIMER_BASE, 0x00 ); // 清除中断标志寄存器 IOWR_ALTERA_AVALON_TIMER_PERIODL( TIMER_BASE, 50000000 ); // 设置定时周期 1s IOWR_ALTERA_AVALON_TIMER_PERIODH( TIMER_BASE, 50000000>>16 ); IOWR_ALTERA_AVALON_TIMER_CONTROL( TIMER_BASE, 0x07 ); ISR_handle_timer, NULL, 0x0 ); // 注册中断 } // 使能中断

七段LED数码管显示电路设计(精)

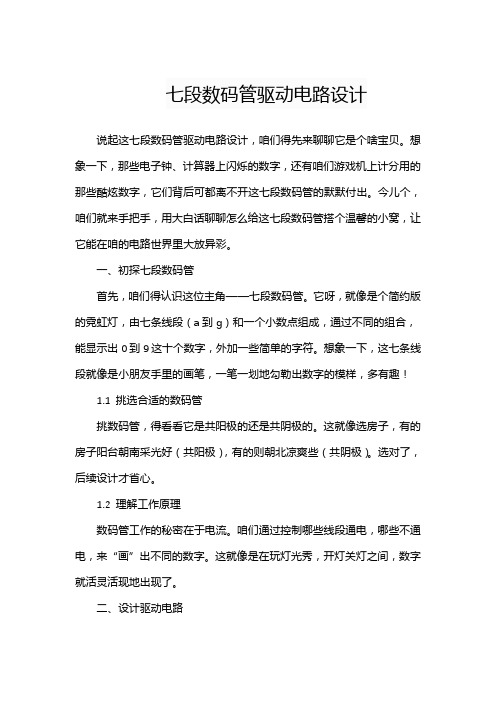

实验七七段LED数码管显示电路设计一、实验目的1.学习EDA软件的基本操作2.学习使用原理图进行设计输入3.初步掌握软件输入、编译、仿真和编程的过程4.学习实验开发系统的使用方法二、实验说明本实验通过七段LED数码管显示电路的设计,初步掌握EDA 设计方法中的设计输入、编译、综合、仿真和编程的基本过程。

七段LED数码管显示电路有四个数据输入端(D0-D3),七个数据输出端(A-G。

三、实验要求1、完成七段LED数码管显示电路的原理图输入并进行编译2、对设计的电路经行仿真验证3、编程下载并在实验开发系统上验证设计结果四、实验步骤1、新建工程2、新建Verilog HDL文件3、在文本输入窗口键入代码4、保存HDL文件5、编译文件直至没有错误6、新建波形文件7、添加观察信号8、添加输入激励,保存波形文件9、功能仿真七段LED数码管显示电路真值表:输入D3D2D1D0G F E D C B A 000000111111 100010000110 200101011011 300111001111 401001100110 501011101101 601101111101 701110001111 810001111111910011101111 A10101110111 B10111111100 C11001111001 D110111011110 E11101111001 F11111110001五、电路原理图啊Verilog代码描述:module qiduan(data_in,data_out;input [3:0]data_in;output [6:0]data_out;reg [6:0]data_out;always @(data_inbegincasex(data_in4'b0000:data_out<=7'b0111111;4'b0001:data_out<=7'b0000110; 4'b0010:data_out<=7'b1011011; 4'b0011:data_out<=7'b1001111; 4'b0100:data_out<=7'b1100110; 4'b0101:data_out<=7'b1101101; 4'b0110:data_out<=7'b1111100; 4'b0111:data_out<=7'b0000111; 4'b1000:data_out<=7'b1111111; 4'b1001:data_out<=7'b1100111; 4'b1010:data_out<=7'b1110111; 4'b1011:data_out<=7'b1111100; 4'b1100:data_out<=7'b0111001; 4'b1101:data_out<=7'b1011110; 4'b1110:data_out<=7'b1111001; 4'b1111:data_out<=7'b1110001; default:data_out<=7'b0000000; endcaseendendmodule仿真波形:六、实验体会七段LED数码管显示电路是常用的数码管之一,它有四个数据输入端(D0-D3),七个数据输出端(A-G。

实验4~七段数码管

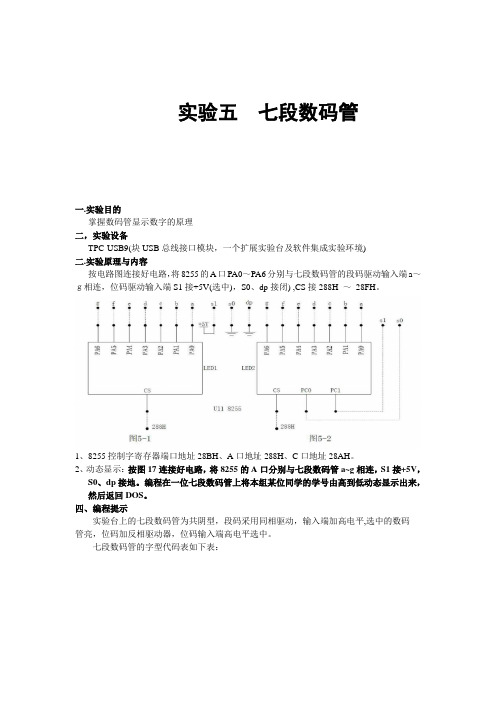

实验五七段数码管一.实验目的掌握数码管显示数字的原理二,实验设备TPC-USB9(块USB总线接口模块,一个扩展实验台及软件集成实验环境)二.实验原理与内容按电路图连接好电路,将8255的A口PA0~PA6分别与七段数码管的段码驱动输入端a~g相连,位码驱动输入端S1接+5V(选中),S0、dp接闭) ,CS接288H ~28FH。

1、8255控制字寄存器端口地址28BH、A口地址288H、C口地址28AH。

2、动态显示:按图17连接好电路,将8255的A口分别与七段数码管a~g相连,S1接+5V,S0、dp接地。

编程在一位七段数码管上将本组某位同学的学号由高到低动态显示出来,然后返回DOS。

四、编程提示实验台上的七段数码管为共阴型,段码采用同相驱动,输入端加高电平,选中的数码管亮,位码加反相驱动器,位码输入端高电平选中。

七段数码管的字型代码表如下表:五、程序流程图六、汇编程序stack segment stack ‘stack’dw 32 dup(0)stack endsdata segmentbegin proc farassume cs:code,ds:data,ss:stackpush dssub ax,axpush axmov ax,datamov ds,ax;/**************************************************************/ MOV DX,28BH ;设置8255为端口A的工作方式0 MOV AL,00HOUT DX,ALMOV DX,288H ;设置端口A的地址MOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AL,3FH ;显示数字0OUT DX,ALCALL DELAYMOV AL,07H ;显示数字7OUT DX,ALCALL DELAYMOV AL,3FH ;显示数字0OUT DX,ALCALL DELAYMOV AL,4FH ;显示数字3OUT DX,ALCALL DELAYMOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AL,4FH ;显示数字3OUT DX,ALCALL DELAYMOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AH,4CH ;返回DOSINT 21HRETBEGIN ENDPDELAY PROC ;设置延时程序PUSH AXPUSH BXPUSH CXPUSH DXMOV BX,20000L1:MOV CX,1000L2:LOOP L2DEC DXJNZ L1POP DXPOP CXPOP BXPOP AXRETDELAY ENDPCODE ENDSEND BEGIN六、心得体会:通过本次试验,让我熟悉了用EDIT进行汇编程序编写的操作,也加强了在DOS上编译、连接、运行汇编程序的步骤。

计数器7段数码管控制接口技术课程设计报告材料

《EDA技术综合设计》课程设计报告报告题目:计数器7段数码管控制接口技术作者所在系部:作者所在专业:作者所在班级:作者姓名:作者学号:指导教师姓名:完成时间:内容摘要掌握VHDL语言基本知识,并熟练运用VHDL语言来编写程序,来下载实践到硬件上,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

利用VHDL语言设计一个七段数码管控制引脚,在时钟信号的控制下,使6位数码管动态刷新显示十进制计数器及其进位,十二进制计数器,四位二进制可逆计数器,六十进制计数器的计数结果,这期间需要seltime分频器来动态的给各个计数器分配数码管,并显示数字的变化。

关键词:VHDL语言编程七段数码管控制引脚芯片目录一概述 (1)二方案设计与论证 (1)三单元电路设计与参数计算 (1)3.1数码管译码器 (1)3.2 十进制计数器 (2)3.3六十进制计数器 (3)3.4四位二进制可逆计数器 (5)3.5时间数据扫描分时选择模块 (6)3.6顶层文件 (8)四总的原理图 (9)五器件编程与下载 (9)六性能测试与分析(要围绕设计要求中的各项指标进行) (10)七实验设备 (10)八心得体会 (10)九参考文献 (10)课程设计任务书一、概述设计一个共阴7段数码管控制接口,在硬件时钟电路的基础上,采用分频器,输出一个1S的时钟信号。

一个带使能输入、进位输出及同步清0的增1十进制计数器。

一个带使能输入及同步清0的六十进制同步加法计数器和一个四位二进制可逆计数器。

要求:在时钟信号的控制下,使6位数码管动态刷新显示上述计数器的计数结果。

二、方案设计与论证首先VHDL语言编写底层文件和三个计数器的程序,再编写分频器和数码管的程序,最后用例化语句编写顶层文件,分别都调试在确认无误后把顶层文件下载到试验箱,连接导线,完成后实现在时钟信号的控制下,6位数码管动态刷新显示三个计数器的技术结果。

三、单元电路设计1.数码管译码器程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity deled isport(num:in std_logic_vector(3 downto 0);led:out std_logic_vector(6 downto 0));end deled;architecture fun of deled isbegin-- abcdefgled<="1111110"when num="0000"else "0110000"when num="0001"else"1101101"when num="0010"else"1111001"when num="0011"else"0110011"when num="0100"else"1011011"when num="0101"else"1011111"when num="0110"else"1110000"when num="0111"else"1111111"when num="1000"else"1111011"when num="1001"else"1110111"when num="1010"else"0011111"when num="1011"else"1001110"when num="1100"else"0111101"when num="1101"else"1001111"when num="1110"else"1000111"when num="1111";end fun;原理图2.十进制计数器程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk,clr,en:in std_logic;co:out std_logic;q:buffer std_logic_vector(3 downto 0)); end cnt10;architecture behave of cnt10 isbeginprocess(clk,clr,en)beginif(en='0')then q<="0000";elsif(clk'event and clk='1')thenif(clr='1')then q<="0000";elsif(q=9)then q<="0000";co<='1';else q<=q+1;co<='0';end if;end if;end process;end behave;原理图仿真波形图3.六十进制计数器程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cnt60 ISPORT(clk,clr,en:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END cnt60;ARCHITECTURE behave OF cnt60 ISSIGNAL qh,ql:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(clk,clr,en)BEGINIF(en='1')THEN ql<="0000";qh<="0000";ELSIF(clk'event and clk='1')THENIF(clr='1')THEN ql<="0000";qh<="0000";ELSIF(ql=9)THEN ql<="0000";IF(qh=5)THEN qh<="0000";ELSE qh<=qh+1;END IF;ELSE ql<=ql+1;END IF;END IF;q<=qh&ql;END PROCESS;END behave;原理图波形图4.四位二进制可逆计数器程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity kn4 isport(clk,clr,plus_sub:in std_logic;q:buffer std_logic_vector(3 downto 0));end kn4;architecture behave of kn4 isbeginprocess(clk,clr,plus_sub)beginif(clk'event and clk='1')thenif(clr='1')then q<="0000";elsif(plus_sub='1')thenif(q=15)then q<="0000";else q<=q+1;end if;elsif(plus_sub='0')thenif(q=0)then q<="1111";else q<=q-1;end if;end if;end if;end process;end behave;原理图波形图5.时间数据扫描分时选择模块程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity seltime isport(clk,reset,ci:in std_logic;Kn4,cnt10:in std_logic_vector(3 downto 0);cnt60:in std_logic_vector(7 downto 0);daout:out std_logic_vector(3 downto 0);dp:out std_logic;sel:out std_logic_vector(2 downto 0));end seltime;architecture fun of seltime issignal count:std_logic_vector(2 downto 0);beginsel<=count;process(clk,reset)beginif(reset='0')thencount<="000";elsif(clk'event and clk='1')thenif(count>="101")thencount<="000";elsecount<=count+1;end if;end if;case count iswhen"000"=>daout<=cnt10(3 downto 0);dp<='0'; when"001"=>daout(3 downto 1)<="000";daout(0)<=ci;dp<='0'; when"010"=>daout<=kn4(3 downto 0);dp<='0'; when"011"=>daout<=cnt60(7 downto 4);dp<='0'; when others=>daout<=cnt60(3 downto 0);dp<='0'; end case;end process;end fun;原理图6.顶层文件程序library ieee;use ieee.std_logic_1164.all;entity ss_top isport(clk,clr,en,plus_sub,clkdsp:in std_logic;a,b,c,d,e,f,g,dpout:out std_logic;sel:out std_logic_vector(2 downto 0));end ss_top;architecture one of ss_top iscomponent cnt60port(clk,clr,en:in std_logic;q:out std_logic_vector(7 downto 0));end component;component kn4port(clk,clr,plus_sub:in std_logic;q:buffer std_logic_vector(3 downto 0)); end component;component cnt10port(clk,clr,en:in std_logic;co:out std_logic;q:buffer std_logic_vector(3 downto 0)); end component;component deledPORT(num:in std_logic_vector(3 downto 0);led:out std_logic_vector(6 downto 0)); end component;component seltimeport(clk,reset,ci:in std_logic;cnt60:in std_logic_vector(7 downto 0);kn4:in std_logic_vector(3 downto 0);cnt10:in std_logic_vector(3 downto 0);dp:out std_logic;daout:out std_logic_vector(3 downto 0);sel:out std_logic_vector(2 downto 0)); end component;signal cnt60_out:std_logic_vector(7 downto 0);signal kn4_out:std_logic_vector(3 downto 0);signal cnt10_out:std_logic_vector(3 downto 0);signal cnt10_co:std_logic;signal ledout:std_logic_vector(6 downto 0);signal seltime_out:std_logic_vector(3 downto 0);Begina<=ledout(6);b<=ledout(5);c<=ledout(4);d<=ledout(3);e<=ledout(2);f<=ledout(1);g<=ledout(0);u1:deled port map(num=>seltime_out,led=>ledout);u2:cnt10 port map(clk=>clk,clr=>clr,en=>en,co=>cnt10_co,q=>cnt10_out);u3:cnt60 port map(clk=>clk,clr=>clr,en=>en,q=>cnt60_out);u4:kn4 port map(clk=>clk,clr=>clr,plus_sub=>plus_sub,q=>cnt16_out);u5:seltimeport map(clk=>clkdsp,reset=>clr,ci=>cnt10_co,cnt60=>cnt60_out,kn4=>kn4_out,cnt10=>cnt10_out,daout=>seltime_out,dp=>dpout,sel=>sel);end one;四、总的原理图五、器件编程与下载用VHDL语言编译四种计数器的、译码器和分时器的程序,然后把他们用例化语句编译成顶层文件,仿真成功以后下载到试验箱通过数码管显示出结果,试验成功。

实验报告2--7段数码管显示实验

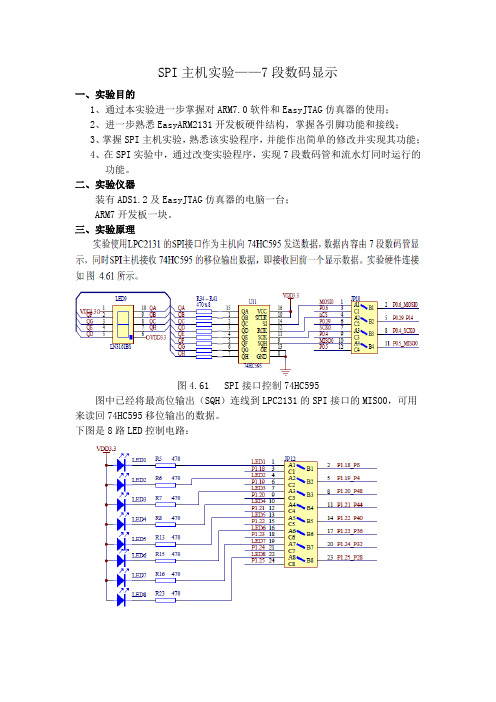

SPI主机实验——7段数码显示一、实验目的1、通过本实验进一步掌握对ARM7.0软件和EasyJTAG仿真器的使用;2、进一步熟悉EasyARM2131开发板硬件结构,掌握各引脚功能和接线;3、掌握SPI主机实验,熟悉该实验程序,并能作出简单的修改并实现其功能;4、在SPI实验中,通过改变实验程序,实现7段数码管和流水灯同时运行的功能。

二、实验仪器装有ADS1.2及EasyJTAG仿真器的电脑一台;ARM7开发板一块。

三、实验原理图4.61 SPI接口控制74HC595图中已经将最高位输出(SQH)连线到LPC2131的SPI接口的MISO0,可用来读回74HC595移位输出的数据。

下图是8路LED控制电路:该实验演示在7段数码管上显示一些字符,字符的字模表存于一数组中,流程图如下图4.62所示。

图4.62 LED数码管显示实验流程图1、特性2、结构SPI总线配置及数据传输3、SPI外设描述4、基本操作5主机操作四、实验内容与结果1、实验程序如下#include "config.h"#define HC595_CS (1 << 29) // P0.29口为74HC595的片选const uint32 LEDS8 = (0xFF << 18); // P1[25:18]控制LED8~LED1,低电平点亮/************************************************************************ ******************************** 函数名称:DelayNS()** 函数功能:长软件延时** 入口参数:dly 延时参数,值越大,延时越久** 出口参数:无************************************************************************* *******************************/void DelayNS(uint32 dly){uint32 i;for(; dly>0; dly--)for(i=0; i<50000; i++);}const uint32 LED_TBL[] = {0x00, 0xFF, // 全部熄灭后,再全部点亮0x01, 0x02, 0x04, 0x08, 0x10, 0x20, 0x40, 0x80, // 依次逐个点亮0x01, 0x03, 0x07, 0x0F, 0x1F, 0x3F, 0x7F, 0xFF, // 依次逐个叠加0xFF, 0x7F, 0x3F, 0x1F, 0x0F, 0x07, 0x03, 0x01, // 依次逐个递减0x81, 0x42, 0x24, 0x18, 0x18, 0x24, 0x42, 0x81, // 两个靠拢后分开0x81, 0xC3, 0xE7, 0xFF, 0xFF, 0xE7, 0xC3, 0x81 // 从两边叠加后递减};/********************************************************************************************************** 函数名称:MSPI_Init()** 函数功能:初始化SPI接口,设置为主机。

两位七段数码管的工作流程

两位七段数码管的工作流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 初始化设置数码管的引脚连接,确定每个引脚的功能(如段选、位选等)。

7段数码管实验报告

7段数码管实验报告实验目的:本实验的目的是通过控制 7 段数码管的亮灭状态来显示不同的数字和字母。

实验原理:7 段数码管常用于显示数字和字母,每个数码管由 7 个 LED灯组成,分别表示 A、B、C、D、E、F、G 等 7 个段。

通过控制这些LED 灯的亮灭状态,就可以显示不同的数字和字母。

在实际应用中,通常需要使用一个译码器来根据输入的数字或字母输出相应的控制信号。

常用的译码器有 7447、DM9368 等。

这些译码器通常都是 BCD 码到 7 段数码管的译码器。

在本实验中,我们将使用 7447 译码器来控制 7 段数码管的亮灭状态。

7447 译码器具有 4 个输入线和 7 个输出线,每个输入线上的 BCD 码可以转换成相应的控制信号,用于控制数码管的 7 个 LED 灯。

实验材料:1. 7 段数码管2. 7447 译码器3. 电路板4. 电压源5. 连接线实验步骤:1. 将 7447 译码器插入电路板上相应的插槽中,并将数码管连接到电路板上。

2. 将电压源连接到电路板上,并调节电压和电流值。

3. 根据所需显示的数字或字母,设置相应的BCD 码输入信号。

4. 打开电源,观察数码管是否能够正确显示。

实验结果:通过本实验,我们可以成功控制 7 段数码管的亮灭状态,实现了数字和字母的显示。

同时,我们也了解了 7447 译码器的原理和使用方法。

实验小结:本实验是电子技术的基础实验之一,通过实验我们深入了解了7 段数码管和 7447 译码器的原理和应用,同时也锻炼了我们的动手能力和实验技能。

在实际应用中,7 段数码管和译码器常常被用于数字显示、计数器、时钟、温度计等电子设备中,具有广泛的应用前景。

vivado七段数码管代码及仿真

文章标题:深入探究Vivado中七段数码管代码及仿真在数字电路设计中,七段数码管是一种常见的数字显示装置,广泛应用于计时器、计数器、仪表等设备中。

Vivado是Xilinx公司推出的一款集成化开发环境软件,用于FPGA设计和开发。

本文将深入探讨在Vivado中编写七段数码管的代码以及进行仿真的方法,以便读者能够更深入地理解数字电路设计和Vivado软件的应用。

一、七段数码管的基本原理要理解在Vivado中编写七段数码管的代码,首先需要了解七段数码管的基本原理。

七段数码管由7根发光二极管组成,分别对应数码管的a、b、c、d、e、f、g片段,可以显示0-9以及一些字母。

在数字电路设计中,需要通过操纵七段数码管的每一个片段,来显示需要的数字或字符。

编写七段数码管的代码,实质上是利用FPGA来控制这7个片段的亮灭。

二、Vivado中七段数码管的代码编写在Vivado中,可以使用Verilog或VHDL等硬件描述语言来编写数字电路设计的代码。

对于七段数码管的代码编写,以Verilog为例,可以按照以下步骤进行:1. 定义输入信号2. 分配七个片段对应的输出信号3. 使用组合逻辑进行数字与片段的对应4. 使用时序逻辑进行信号的控制和时序处理以下是一个简单的七段数码管代码示例:```verilogmodule seven_segment(input [3:0] sw,output reg [6:0] seg);always @(*)begincase (sw)4'b0000: seg = 7'b1000000; // 数字0 4'b0001: seg = 7'b1111001; // 数字1 4'b0010: seg = 7'b0100100; // 数字2 // 其他数字的对应关系default: seg = 7'b1111111; // 默认不显示 endcaseendendmodule```三、Vivado中七段数码管的仿真方法在编写七段数码管的代码之后,需要对其进行仿真以验证设计的正确性。

实验报告模板:实验二7段数码显示译码器

班级:学号:姓名:实验二7段数码显示译码器【实验目的】1.设计七段显示译码器,并在实验板上验证2.学习V erilog HDL文本文件进行逻辑设计输入;3.学习设计仿真工具的使用方法;【实验内容】1.实现BCD/七段显示译码器的“Verilog ”语言设计。

说明:7段显示译码器的输入为:IN0…IN3共5根,7段译码器的逻辑表同学自行设计,要求实现功能为:输入“0…15 ”(二进制),输出“0…9…F ”(显示数码),输出结果应在数码管(共阴)上显示出来。

2.使用工具为译码器建立一个元件符号3.设计仿真文件,进行验证。

4.编程下载并在实验箱上进行验证。

【实验原理】【1】7段数码是纯组合电路。

首先设计程序如下,该程序可按case语句的表述方法写。

【2】设输入的4位码为[3:0],输出控制7段共阴数码管的7位数据为LED7S[6:0].输出信号LED7S的7位分别接共阴数码管的7个段,高位在左,低位在右,例如当LED7S输出为1011011,数码管的7个段g,f,e,d,c,b,a分别接1,0,1,1,0,1,1;接有高电平的段发亮,数码管显示2.注:未考虑小数点的发光管,若考虑则需增加段h,然后将LED7S改为8位输出。

【程序源代码】(加注释)module LED(IN,led7);input [3:0]IN; //四位并行加载数据output[6:0]led7; //计数数据输出reg [6:0]led7; //定义一个内部7位寄存节点always@(IN) //时序过程begincase(IN)4'b0000:led7<=7'b0111111;4'b0001:led7<=7'b0000110;4'b0010:led7<=7'b1011011;4'b0011:led7<=7'b1001111;4'b0100:led7<=7'b1100110;4'b0101:led7<=7'b1101101;4'b0110:led7<=7'b1111101;班级:学号:姓名:4'b0111:led7<=7'b0000111;4'b1000:led7<=7'b1111111;4'b1001:led7<=7'b1101111;default:led7<=7'b0111111;endcase //主块结束endendmodule【仿真和测试结果】班级:学号:姓名:【实验心得和体会】初次学习并应用Verilog语言,作为实战第一类题,我熟悉并熟练掌握了Verilog语言的基本运用方法,这对进一步的学习拥有重要的作用。

七段数码管显示电路的设计与实现

深圳大学实验报告

课程名称:VHDL数字电路设计教程

实验项目名称:七段数码管显示电路的设计与实现学院:信息工程学院

专业:电子信息工程

指导教师:邓小莺

报告人:学号:班级:

实验时间:2013.05.30

实验报告提交时间:2013.06.06

教务部制

实验目的与要求:

1.掌握带7段显示器的模100计数器设计。

方法、步骤:

1.点击图标,运行Xilinx ISE软件,新建文件并保存。

2.编写程序,检验无误后,进行仿真。

3.仿真出波形,并进行相关的比较。

4.运行获得设计完成的电路。

实验过程及内容:(1)程序编写:

(2)仿真波形:

(3)设计电路

指导教师批阅意见:

成绩评定:

指导教师签字:

年月日备注:

注:1、报告内的项目或内容设置,可根据实际情况加以调整和补充。

2、教师批改学生实验报告时间应在学生提交实验报告时间后10日内。

基于Labview制作数码管电子钟设计报告

基于Labview制作数码管电子钟设计报告基于Labview的数码管电子钟制作和仿真物理与光信息科技学院071班作者:李虎(68号),谢秀滨摘要:由于LabVIEW轶件的优越性,用它来制作和仿真数码管电子钟是很方便的,是其它轶件不可比拟的。

这次制作数码管电子钟,所用的控件不多,主要用到了指示灯、获取日期/时间(秒)、格式化日期/时间字符串、截取字符串、While循环、条件结(Case结构)、常量、局部变量、真常量、假常量等等,通过连接就基本制作好一个数码管电子钟了。

在仿真时,通过和计算机时间的对比,完全符合要求,仿真性能很好,达到了这次研究和制作数码管电子钟的目的。

关键词:数码管电子钟,控件,前面板,程序框图,获取日期/时间(秒),格式化日期/时间字符串,截取字符串,While循环,条件结(Case结构)。

数码管电子钟在现实生活、工作中,特别是在科学研究工作中有非常很重要的、广泛的应用。

在这种情况下,对数码管电子钟的研究和制作、仿真是十分很重要。

本文就此讨论数码管电子钟的制作和仿真等等问题。

数码管电子钟可以用多种轶件来制作和仿真,如Proteus、Flash 等等轶件。

现在我们用LabVIEW轶件来制作数码管电子钟。

简单介绍一下LabVIEW,LabVIEW是美国National Instruments公司开发的一种业界领先的工业标准图形化编程系统,应用于数据与控制、数据分析,以及数据表达等方面,对称之为“虚拟仪器”(Virtual Instruments,VIS)的轶件对象进行图形化的组合操作。

我们制作数码管电子钟所用的LabVIEW是8.5版的。

在制作数码管电子钟的过程中,我们用到一个显示控件,四十二个长方形LED组成的数码管,四个圆形LED组成的两个“冒号”,和一个圆形的按钮,其中LED和按钮都是布尔控件,这些控件都是放大前面板的。

而前面板是图形化的人机界面,模拟数码管电子钟工作的过程。

在程序框图上,用到一个获取日期/时间(秒)、一个格式化日期/时间字符串、八个截取字符串、一个While循环、六个条件结(Case结构)、十六个常量、四百十二个局部变量、四十二个真常量、四十二个假常量等等。

LabVIEW之七段数码管实验报告(正式版)

Guangdong Polytechnic Normal UniversityLabVIEW程序设计基础实验报告实验题目:一位七段数码管显示专业:应用电子技术教育(师范)年级班别:13级2班组员姓名:指导教师:向英二级学院:电子与信息学院二◦一六年三月三^一日一位七段数码管显示【实验目的】1. 认识七段数码管并学习七段数码管的工作原理;2. 学习在NI ELVIS II硬件实验平台,并通过LabVIEW程序控制数码管显示的数字。

3. 学会使用NI ELVISII的软件驱动、连接NI ELVIS II实验平台、编写LabVIEW 程序。

【实验原理】利用NI ELVIS II硬件实验平台,采用元器件搭建硬件电路,编写LabVIEW 程序框图与前面板控制窗口,然后运行程序以实现采用自动与手动两种方式在数码管上显示数字的现象。

1. 了解数码管结构:图1 一位七段数码管结构图2 •数码管原理及接线原理:每个数码管的有8个段:a、b、c、d、e、f、g、h (h是小数点),都分别连到对应的P0-P7, 8个数码管分别由8个选通信号P0-P7来选择。

本实验采用共阴极的七段数码显示器,将七段数码显示器的阴极连在一起,为了不让数码管被意外烧掉,将abcdefgh七段数码管分别通过100Q的上拉电阻接入原型实验平台中的数字I/O 口,a接口接入上端数码管,b接口接入右上端数码管,c 接口接入右下端数码管,d接口接入下端数码管,e接口接入右下端数码管,f 接口接入右上端数码管。

当需要哪一段数码管发亮时,只需在LabVIEW的程序控制中输入高电平1即可。

2. 数码管硬件接线原理图。

段符十人进制代码显示号dp0f e d c b a共阴极共阳极0001111113FH COH06H F9H 1000001102010110115BH A4H3010011114FH BOH4010011099H5011011016DH92H601111101S2H70000011107H F8H8011111117FH SOH9011011116FH9OH图3 一位七段数码管真值表【实验所需元器件】所需元器件与器材:【实验步骤】、搭建硬件电路:GND■■■VE f 匸O O Q 1 O O S *■ F * ■■ d !• '* lr * n O O 0 o o H AD SB -M CR5O d 口 €Z3 o o o B F-" ■—* I —»■ED 7 tn 5图4七段数码管硬件连接图、设计程序流程图图5七段数码管程序流程图设计思路的是利用应用数码管显示数字,采用两种方式控制输入显示,每位显示的数字由实验者通过各自的数字输入框控制输入0-9的数值,各位数字的显示间相互独立,互不影响。

七段数码管仿真代码

七段数码管仿真代码```javaimport java.awt.Color;import java.awt.Graphics;import javax.swing.JFrame;import javax.swing.JPanel;public class SevenSegmentDisplay extends JPanel {private int[] segCodes = { 0b00111111, 0b00000110, 0b01011011, 0b01001111, 0b01100110, 0b01101101, 0b01111001, 0b00001111 };private int[] segPos = { 20, 35, 50, 65, 80, 95, 110, 125 };private int digit;private Color onColor = Color.RED;private Color offColor = Color.BLACK;public SevenSegmentDisplay() {// 设置窗口标题JFrame frame = new JFrame("Seven Segment Display");// 设置关闭窗口操作frame.setDefaultCloseOperation(JFrame.EXIT_ON_CLOSE);// 将七段数码管添加到窗口frame.add(this);// 设置窗口的大小frame.setSize(200, 150);// 设置窗口可见frame.setVisible(true);}@Overrideprotected void paintComponent(Graphics g) {super.paintComponent(g);// 获取绘图上下文g.setColor(offColor);// 绘制每个段的背景for (int i = 0; i < 8; i++) {g.fillRect(segPos[i], 25, 15, 10);}// 设置数字显示digit = (digit / 100) % 10;// 根据数字绘制相应的段for (int i = 0; i < 7; i++) {if ((segCodes[digit] & (1 << i)) != 0) {g.setColor(onColor);} else {g.setColor(offColor);}g.fillRect(segPos[i], 25, 15, 10);}}public static void main(String[] args) {SevenSegmentDisplay display = new SevenSegmentDisplay(); for (int i = 0; i < 1000; i++) {display.digit++;display.repaint();try {// 暂停 10 毫秒Thread.sleep(10);} catch (InterruptedException e) {e.printStackTrace();}}}}```上述代码中,创建了一个继承自`JComponent`的`SevenSegmentDisplay`类,用于绘制七段数码管的显示。

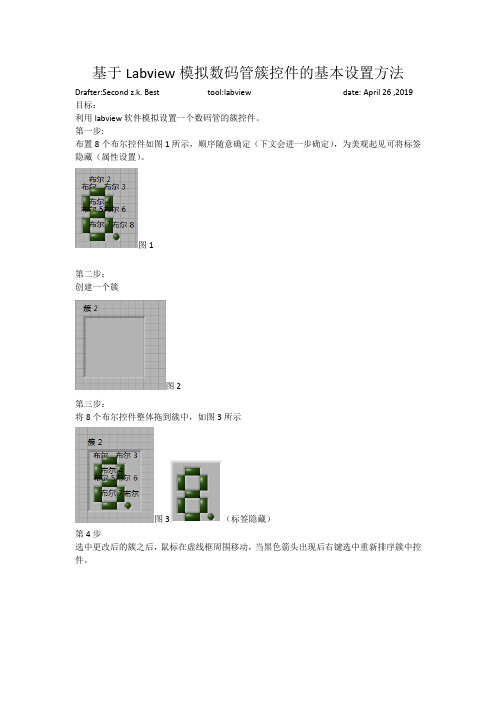

基于Labview模拟数码管簇控件的基本设置方法及应用

基于Labview模拟数码管簇控件的基本设置方法

Drafter:Second z.k. Best tool:labview date: April 26 ,2019 目标:

利用labview软件模拟设置一个数码管的簇控件。

第一步:

布置8个布尔控件如图1所示,顺序随意确定(下文会进一步确定),为美观起见可将标签隐藏(属性设置)。

图1

第二步:

创建一个簇

图2

第三步:

将8个布尔控件整体拖到簇中,如图3所示

图3(标签隐藏)

第4步

选中更改后的簇之后,鼠标在虚线框周围移动,当黑色箭头出现后右键选中重新排序簇中控件。

图4

第五步

将你确定的顺序如abcdefg按所确定的位置点下来。

图5为初始顺序。

图6确定的abcdefg.

图5

图6

如何理解:就是在确定顺序时先点a再点b再点c再点d再点e再点f再点g。

如图7

图7

第六步

然后打勾。

第九步:

如何控制簇中布尔控件。

我们需要用到数组至簇转换。

最重要的一步鼠标右键在簇大小中选择簇中元素的数量为8(图10所示)。

为什么要设置?默认为数量9。

图9图10

前面框

后面框该程序主要通过数组布尔来控制簇中布尔控件显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于labview的虚拟2位7段数码管

作者:Second z.k. Best 工具:labview

1. 主要内容

本文主要利用labview虚拟仪器来模拟一个2位7段数码管。

2. 前面板展示

图1

如图1所示,先创建一个簇,再创建7个布尔控件,将这7个布尔控件布置成一个7段数码管的形状,再复制这个7段数码管,摆成一个2位7段数码管。

然后将这个2位7段数码管复制进簇中摆放合适。

就会如图2所示。

3. 程序框图展示

图3

通过商和余数VI来判断数值的个位十位。

利用条件结构来控制数值0-9时布尔控件的真假,从而在前面板上通过明暗变化来显示0-9的数值变化,最后捆绑到簇。

4. 程序演示

图4

5. 注意事项

如果想连续改变数值来观察运行情况,可利用连续运行或在程序图中加入一个while循环。

但若将此VI作为子VI来使用则切不可加while循环,否则将连续运行子VI。