RTR040N03中文资料

STN4NE03中文资料

Fig. 4: Gate Charge test Circuit

Fig. 5: Test Circuit For Inductive Load Switching And Diode Recovery Times

6/8

®

元器件交易网

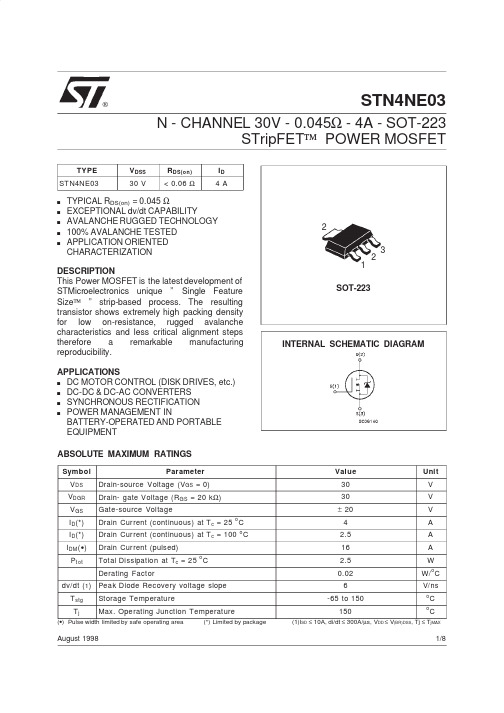

STN4NE03

SOT-223 MECHANICAL DATA

ELECTRICAL CHARACTERISTICS (Tcase = 25 oC unless otherwise specified) OFF

Symb ol V (BR)DSS I DSS Parameter Drain-source Breakdown Voltage Test Cond ition s I D = 250 µ A V GS = 0 Min. 30 1 10 ± 100 Typ . Max. Un it V µA µA nA

®

5/8

元器件交易网

STN4NE03

Fig. 1: Unclamped Inductive Load Test Circuit Fig. 2: Unclamped Inductive Waveform

Fig. 3: Switching Times Test Circuits For Resistive Load

STN4NE03

Output Characteristics Transfer Characteristics

Transconductance

Static Drain-source On Resistance

Gate Charge vs Gate-source Voltage

Capacitance Variations

Static Drain-source On V GS = 10 V Resistance

M-System R3-NC3远程I O通信模块规格书说明书

远程 I/O R3 系列通信模块机型: R3-NC3-①② ①、②在下列代码中选择。

(例如: R3-NC3-N/CE/W/Q)・特殊规格(例如: /C01/SET)①供电电源N: 无供电电源◆交流电源K3: 100~120V AC (允许电压范围 85~132V AC、47~66Hz)*(不符合CE)L3: 200~240V AC (允许电压范围 170~264V AC、47~66Hz)*(不符合CE)◆直流电源R:24V DC (允许电压范围 24V±10%、纹波系数 10%p-p以下)**、与电源模块以及备有电源的通信模块并用时不能选择。

②附加代码 (可指定多项)◆适用标准未填写: 不符合CE/CE: 符合CE◆三菱产双重PLC系统未填写: 不支持该系统/W: 支持该系统◆特殊规格未填写: 无特殊规格/Q: 特殊规格(从特殊规格之项另请选择)/C01: 硅涂层/C02: 聚氨酯涂层/C03: 橡胶涂层◆出厂时的设定/SET: 按照订购表格 (No: ESU-8422) 设定・CC-Link: 连接器型欧式端子盘 (适用电缆线: 0.2~2.5mm2、露线长度为7mm)・内部通信总线: 连接到底座 (机型: R3-BS□) 上・内部电源: 由底座 (机型: R3-BS□) 提供・供电电源、RUN接点输出: M3螺丝2块端子盘连接 (紧固扭矩为0.5N·m)压接端子: 请参照「适用压接端子」图(不能使用带绝缘套的压接端子)・适用电缆线: 0.75~1.25mm2端子螺丝材质: 铁表面镀镍隔离: CC-Link-内部通信总线・内部电源-供电电源-RUN接点输出-FG间主/从切换设定: 用侧面的DIP开关设定数据分配设定: 用侧面的DIP开关设定RUN显示灯: 红/绿2色LED通信正常时亮绿色灯;接收数据时亮红色灯(用DIP开关进行切换)ERR显示灯: 红/绿2色LED通信异常时绿色灯亮灯/闪烁 (电缆断线时熄灯,异常设定时闪烁);发送数据时,亮红色灯(用DIP开关进行切换)■RUN接点输出RUN接点: RUN显示灯亮绿色灯时ON (CC-Link通信正常时ON)额定负载: 250V AC 0.5A (cos ø = 1) 30V DC 0.5A (电阻负载) (满足EU指令时,额定负载小于50V AC。

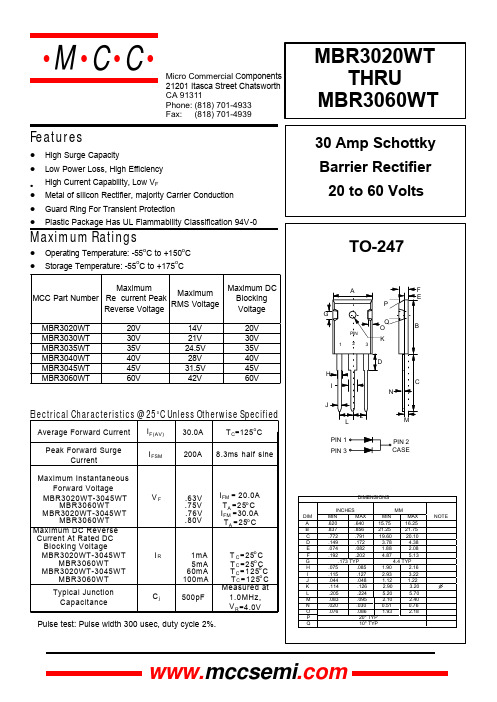

MBR3040WT中文资料

0.1 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

PERCENT OF RATED PEAK REVERSE VOLTAGE ,(%) INSTANTANEOUS FORWARD VOLTAGE , VOLTS

FIG.5 - TYPICAL JUNCTION CAPACITANCE

1

2

5

10

20

50

100

CASE TEMPERATURE , C

NUMBER OF CYCLES AT 60Hz

FIG.3 - TYPICAL REVERSE CHARACTERISTICS

100

FIG.4 - TYPICAL FORWARD CHARACTERISTICS

100

INSTANTANEOUS FORWARD CURRENT ,(A)

o

PIN 3

VF

.63V .75V .76V .80V

I FM = 20 .0A o TA = 2 5 C I FM =30.0A T A = 2 5o C

A B C D E F G H I J K L M N O P Q INCHES MM .620 .640 15.75 16.25 .837 .856 21.25 21.75 .772 .791 19.60 20.10 .149 .172 3.78 4.38 .074 .082 1.88 2.08 .192 .202 4.87 5.13 .173 TYP 4.4 TYP .075 .085 1.90 2.16 .115 .127 2.93 3.22 .044 .048 1.12 1.22 .114 .126 2.90 3.20 .205 .224 5.20 5.70 .083 .095 2.10 2.40 .020 .030 0.51 0.76 .076 .086 1.93 2.18 20° TYP 10° TYP

40N03PC场效应管

VG

VDS D G

TO THE OSCILLOSCOPE

0.8 x RATED VDS

5V QGS

QG QGD

S

VGS

+

1~ 3 mA

-

I

I

G

D

Charge

Q

Fig 15. Gate Charge Circuit

Fig 16. Gate Charge Waveform

Information furnished by Silicon Standard Corporation is believed to be accurate and reliable. However, Silicon Standard Corporation makes no guarantee or warranty, express or implied, as to the reliability, accuracy, timeliness or completeness of such information and assumes no responsibility for its use, or for infringement of any patent or other intellectual property rights of third parties that may result from its use. Silicon Standard reserves the right to make changes as it deems necessary to any products described herein for any reason, including without limitation enhancement in reliability, functionality or design. No license is granted, whether expressly or by implication, in relation to the use of any products described herein or to the use of any information provided herein, under any patent or other intellectual property rights of Silicon Standard Corporation or any third parties.

NSS40500UW3T2G_07资料

NSS40500UW3T2G40 V, 6.0 A, Low V CE(sat) PNP TransistorON Semiconductor’s e2PowerEdge family of low V CE(sat) transistors are miniature surface mount devices featuring ultra low saturation voltage (V CE(sat)) and high current gain capability. These are designed for use in low voltage, high speed switching applications where affordable efficient energy control is important.Typical applications are DC−DC converters and power management in portable and battery powered products such as cellular and cordless phones, PDAs, computers, printers, digital cameras and MP3 players. Other applications are low voltage motor controls in mass storage products such as disc drives and tape drives. In the automotive industry they can be used in air bag deployment and in the instrument cluster. The high current gain allows e2PowerEdge devices to be driven directly from PMU’s control outputs, and the Linear Gain (Beta) makes them ideal components in analog amplifiers.•This is a Pb−Free DeviceMAXIMUM RATINGS (T A = 25°C)Rating Symbol Max Unit Collector-Emitter Voltage V CEO−40Vdc Collector-Base Voltage V CBO−40Vdc Emitter-Base Voltage V EBO−7.0Vdc Collector Current − Continuous I C−5.0Adc Collector Current − Peak I CM−6.0A Electrostatic Discharge ESD HBM Class 3BMM Class C THERMAL CHARACTERISTICSCharacteristic Symbol Max Unit Total Device Dissipation, T A = 25°CDerate above 25°CP D (Note 1)8757.0mW mW/°CThermal Resistance,Junction−to−AmbientR q JA (Note 1)143°C/WTotal Device Dissipation, T A = 25°C Derate above 25°C P D (Note 2) 1.511.8WmW/°CThermal Resistance, Junction−to−AmbientR q JA (Note 2)85°C/WThermal Resistance,Junction−to−Lead #1R q JL (Note 2)23°C/WTotal Device Dissipation (Single Pulse < 10 sec)P Dsingle(Notes 2 & 3)3.0WJunction and Storage Temperature Range T J, T stg−55 to+150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.FR−4 @ 100 mm2, 1 oz copper traces.2.FR−4 @ 500 mm2, 1 oz copper traces.3.Thermal response.Device Package Shipping†ORDERING INFORMATION†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.NSS40500UW3T2G WDFN3(Pb−Free)3000/Tape & ReelELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted)Characteristic Symbol Min Typical Max Unit OFF CHARACTERISTICSCollector−Emitter Breakdown Voltage (I C = −10 mAdc, I B = 0)V(BR)CEO−40−−VdcCollector−Base Breakdown Voltage (I C = −0.1 mAdc, I E = 0)V(BR)CBO−40−−VdcEmitter−Base Breakdown Voltage (I E = −0.1 mAdc, I C = 0)V(BR)EBO−7.0−−VdcCollector Cutoff Current (V CB = −40 Vdc, I E = 0)I CBO−−−0.1m AdcEmitter Cutoff Current (V EB = −7.0 Vdc)I EBO−−−0.1m AdcON CHARACTERISTICSDC Current Gain (Note 4) (I C = −10 mA, V CE = −2.0 V) (I C = −500 mA, V CE = −2.0 V) (I C = −1.0 A, V CE = −2.0 V) (I C = −2.0 A, V CE = −2.0 V) (I C = −3.0 A, V CE = −2.0 V)h FE250250220180150−−300250200−−−−−Collector−Emitter Saturation Voltage (Note 4) (I C = −0.1 A, I B = −0.010 A) (Note 5)(I C = −1.0 A, I B = −0.100 A)(I C = −1.0 A, I B = −0.010 A)(I C=−2.0 A, I B = −0.020 A)(I C = −3.0 A, I B = −0.030 A)(I C = −4.0 A, I B = −0.400 A)V CE(sat)−−−−−−0.010−0.065−0.110−0.190−0.310−0.215−0.015−0.080−0.130−0.220−0.340−0.260VBase−Emitter Saturation Voltage (Note 4) (I C = −1.0 A, I B = −0.01 A)V BE(sat)−−0.76−0.900VBase−Emitter Turn−on Voltage (Note 4) (I C = −2.0 A, V CE = −3.0 V)V BE(on)−−0.80−0.900VCutoff Frequency(I C = −100 mA, V CE = −5.0 V, f = 100 MHz)f T100−−MHzInput Capacitance (V EB = −0.5 V, f = 1.0 MHz)Cibo−475pF Output Capacitance (V CB = −3.0 V, f = 1.0 MHz)Cobo−150pF SWITCHING CHARACTERISTICSDelay (V CC = −30 V, I C = 750 mA, I B1 = 15 mA)t d−−70ns Rise (V CC = −30 V, I C = 750 mA, I B1 = 15 mA)t r−−150ns Storage (V CC = −30 V, I C = 750 mA, I B1 = 15 mA)t s−−600ns Fall (V CC = −30 V, I C = 750 mA, I B1 = 15 mA)t f−−160ns4.Pulsed Condition: Pulse Width = 300 m sec, Duty Cycle ≤ 2%.5.Guaranteed by design but not tested.V C E (s a t ), C O L L E C T O R E M I T T E R S A T U R A T I O N V O L T A G E (V )Figure 5. Base Emitter Turn −On Voltage vs.Collector CurrentFigure 6. Saturation RegionI C , COLLECTOR CURRENT (A)I B , BASE CURRENT (mA)50150h F E , D C C U R R E N T G A I NV B E (o n ), B A S E E M I T T E R T U R N −O N V O L T A G E (V )V CE (V dc )400350300200150250500450C i b o , I N P U T C A P A C I T A N C E (p F )Figure 9. PNP Safe Operating AreaPACKAGE DIMENSIONSWDFN3CASE 506AU −01ISSUE ONOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994 .2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSION b APPLIES TO PLATED TERMINAL AND ISMEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.4.COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.BOTTOM VIEWDIM A MIN NOM MAX MINMILLIMETERS0.700.750.800.028INCHES A10.000.050.000A30.20 REF b 0.250.300.350.010D 2.00 BSC D2 1.40 1.50 1.600.055E 2.00 BSC E20.90 1.00 1.100.0350.0300.0310.0020.008 REF 0.0120.0140.079 BSC0.0590.0630.079 BSC0.0390.043NOM MAX e 0.35 REF 0.014 REFK 1.30 BSC 0.051 BSC 0.350.400.450.0140.0160.018L*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

REF3033AIDBZRG4中文资料

PRODUCT REF3012

PACKAGE-LEAD SO T23-3

"

REF3020

"

SOT23-3

"

DBZ

"

–40°C to +125°C

"

R30B

"

REF3025

"

SOT23-3

"

DBZ

"

–40°C to +125°C

"

R30C

"

REF3030

"

SOT23-3

"to +125°C

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

FEATURES

q MicroSIZE PACKAGE: SOT23-3 q LOW DROPOUT: 1mV q HIGH OUTPUT CURRENT: 25mA q HIGH ACCURACY: 0.2% q LOW IQ: 50µA max q EXCELLENT SPECIFIED DRIFT PERFORMANCE: 50ppm/°C (max) from 0°C to +70°C 75ppm/°C (max) from –40°C to +125°C

GSRG040203;GSLW040203;GSRG160203;GSLW160203;GSRG120203;中文规格书,Datasheet资料

7943..0000

(12 (16

KKeeyy))

93.00

(4,

12

&

16

Key)

83.00

8(122.5&0

(4 16

KKeeyy))

Ø 4.5

R 3.75

h

24

Sealing Gasket

(Not supplied with 4000 series)

Pane Detai Pane

74.00 (12 Key) 93.00 (16 Key)

Current limited to nx20mA @ Vf n = Number of keys Vf = 2.2V (typical) 2.6V (max)

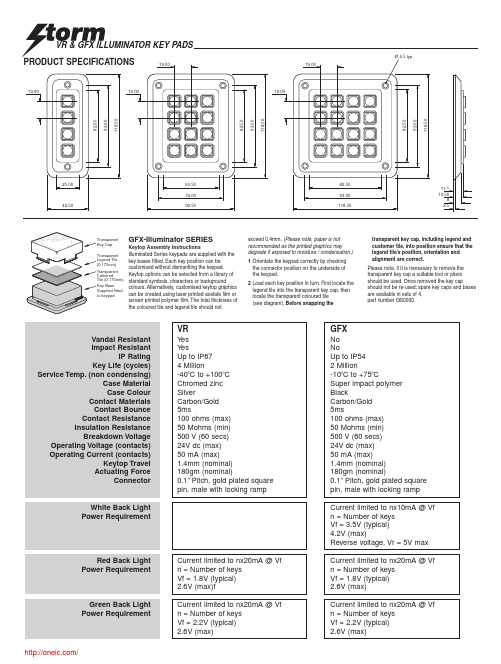

GFX No No Up to IP54 2 Million -100C to +750C Super impact polymer Black Carbon/Gold 5ms 100 ohms (max) 50 Mohms (min) 500 V (60 secs) 24V dc (max) 50 mA (max) 1.4mm (nominal) 180gm (nominal) 0.1” Pitch, gold plated square pin, male with locking ramp

Vandal Resistant Impact Resistant

IP Rating Key Life (cycles) Service Temp. (non condensing)

Case Material Case Colour

Contact Materials Contact Bounce

Contact Resistance Insulation Resistance

Sun SPARC Enterprise M4000 M5000 伺服器文档说明书

存取文件Sun SPARC® Enterprise M4000/M5000 伺服器的全套文件可在以下網址取得:/documentation備註 – 有關 Sun SPARC Enterprise M4000/M5000 伺服器硬體、軟體或文件的最新資訊,請參閱「Sun SPARC Enterprise M4000/M5000 Servers Product Notes」,網址為:/documentationSun SPARC Enterprise M4000/M5000 伺服器文件系統規劃與站點規劃• 「Sun SPARC Enterprise M4000/M5000 伺服器簡介指南」• 「Sun SPARC Enterprise M4000/M5000 伺服器站點規劃指南」• 「Sun SPARC Enterprise 設備機架裝配指南」系統安裝• 「Sun SPARC Enterprise M4000/M5000/M8000/M9000 Servers XSCFUser's Guide」• 「Sun SPARC Enterprise M4000/M5000/M8000/M9000 ServersAdministration Guide」Sun SPARC Enterprise M4000/M5000 伺服器工具組與伺服器包裝在一起,其中包括以下書籍:• 「Sun SPARC Enterprise M4000/M5000 伺服器入門指南」• 「Sun SPARC Enterprise M4000/M5000 伺服器安裝指南」• 「Sun SPARC Enterprise M4000/M5000 Servers Safety and ComplianceManual」管理• 「Sun SPARC Enterprise M4000/M5000/M8000/M9000 ServersAdministration Guide」• 「Sun SPARC Enterprise M4000/M5000/M8000/M9000 Servers XSCFUser's Guide」• 「Sun SPARC Enterprise M4000/M5000/M8000/M9000 Servers XSCFReference Manual」• 「Sun SPARC Enterprise M4000/M5000 Servers Product Notes」• 「Sun SPARC Enterprise M4000/M5000/M8000/M9000 ServersDynamic Reconfiguration (DR) User's Guide」修復與疑難排解• 「Sun SPARC Enterprise M4000/M5000 Servers Service Manual」全球化• 英文、法文、日文、韓文、簡體中文與繁體中文版的「Sun SPARCEnterprise M4000/M5000 伺服器入門指南」、「Sun SPARC EnterpriseM4000/M5000 伺服器安裝指南」、「Sun SPARC Enterprise M4000/M5000 Servers Safety and Compliance Manual」Sun SPARC Enterprise M4000/M5000 伺服器的安裝作業說明步驟 1• 確認電源、空調及底板面積需求。

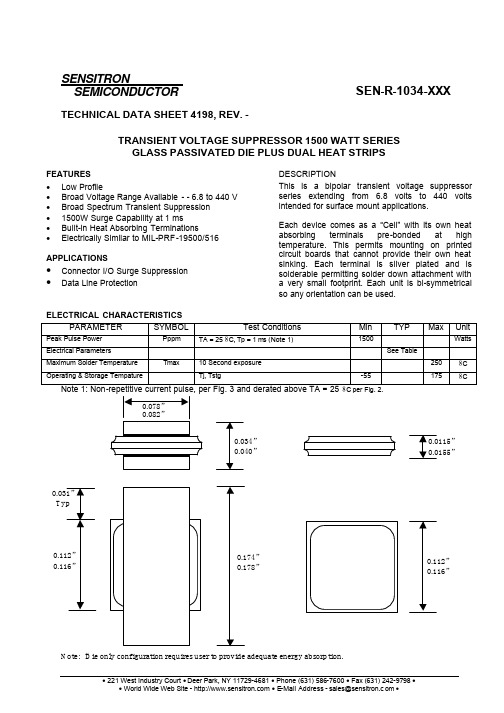

SEN-R-1034-003中文资料

SENSITRON SEMICONDUCTOR TECHNICAL DATA SHEET 4198, REV. -TRANSIENT VOLTAGE SUPPRESSOR 1500 WATT SERIES GLASS PASSIVATED DIE PLUS DUAL HEAT STRIPSFEATURESDESCRIPTION• Low Profile• Broad Voltage Range Available - - 6.8 to 440 V • Broad Spectrum Transient Suppression • 1500W Surge Capability at 1 ms • Built-in Heat Absorbing Terminations• Electrically Similar to MIL-PRF-19500/516APPLICATIONS• Connector I/O Surge Suppression • Data Line ProtectionThis is a bipolar transient voltage suppressor series extending from 6.8 volts to 440 volts intended for surface mount applications.Each device comes as a “Cell” with its own heat absorbing terminals pre-bonded at high temperature. This permits mounting on printed circuit boards that cannot provide their own heat sinking. Each terminal is silver plated and is solderable permitting solder down attachment with a very small footprint. Each unit is bi-symmetrical so any orientation can be used.ELECTRICAL CHARACTERISTICSPARAMETER SYMBOLTest ConditionsMinTYPMaxUnitPeak Pulse Power Pppm TA = 25 8C, Tp = 1 m s (Note 1)1500Watts Electrical ParametersSee TableMaximum Solder Temperature Tmax 10 Second exposure 2508C Operating & Storage TempatureTj, Tstg-551758CNote 1: Non-repetitive current pulse, per Fig. 3 and derated above TA = 25 8C per Fig. 2.Note: “Die only configuration requires user to provide adequate energy absorption.SENSITRON SEMICONDUCTORTECHNICAL DATA SHEET 4198, REV. -SEN-R-1034-XXX 1500 Watt TVS SeriesPart NumberNominalVz (V)Iz (mA)Vz min@ Iz (V)Vz max@ Iz (V)Vr (V)Ir max @ Vr (uA)Vcc (V)Ip (A)SEN-R-1034-001 6.8 10 6.45 7.14 5.80 2000 10.5 144.8 SEN-R-1034-002 7.5 10 7.13 7.88 6.40 1000 11.3 134.5 SEN-R-1034-003 8.2 10 7.79 8.61 7.02 400 12.1 125.6 SEN-R-1034-004 9.1 10 8.65 9.55 7.78 100 13.4 113.4 SEN-R-1034-005 10 1 9.50 10.50 8.55 20 14.5 104.8 SEN-R-1034-006 11 1 10.50 11.60 9.40 10 15.6 97.4 SEN-R-1034-007 12 1 11.40 12.60 10.20 5 16.7 91.0 SEN-R-1034-008 13 1 12.40 13.70 11.10 5 18.2 83.5 SEN-R-1034-009 15 1 14.30 15.80 12.80 5 21.2 71.7 SEN-R-1034-010 16 1 15.20 16.80 13.60 5 22.5 67.6 SEN-R-1034-011 18 1 17.10 18.90 15.30 5 25.2 60.3 SEN-R-1034-012 20 1 19.00 21.00 17.10 5 27.7 54.9 SEN-R-1034-013 22 1 20.90 23.10 18.80 5 30.6 49.7 SEN-R-1034-014 24 1 22.80 25.20 20.50 5 33.2 45.8 SEN-R-1034-015 27 1 25.70 28.40 23.10 5 37.5 40.5 SEN-R-1034-016 30 1 28.50 31.50 25.60 5 41.4 36.7 SEN-R-1034-017 33 1 31.40 34.70 28.20 5 45.7 33.3 SEN-R-1034-018 36 1 34.20 37.80 30.80 5 49.9 30.5 SEN-R-1034-019 39 1 37.10 41.00 33.30 5 53.9 28.2 SEN-R-1034-020 43 1 40.90 45.20 36.80 5 59.3 25.6 SEN-R-1034-021 47 1 44.70 49.40 40.20 5 64.8 23.5 SEN-R-1034-022 51 1 48.50 53.60 43.60 5 70.1 21.7 SEN-R-1034-023 56 1 53.20 58.80 47.80 5 77.0 19.7 SEN-R-1034-024 62 1 58.90 65.10 53.00 5 85.0 17.9 SEN-R-1034-025 68 1 64.60 71.40 58.10 5 92.0 16.5 SEN-R-1034-026 75 1 71.30 78.80 64.10 5 103.0 14.8 SEN-R-1034-027 82 1 77.90 86.10 70.10 5 113.0 13.5 SEN-R-1034-028 91 1 86.50 95.50 77.80 5 125.0 12.2 SEN-R-1034-029 100 1 95.00 105.00 85.50 5 137.0 11.1 SEN-R-1034-030 110 1 105.00 116.00 94.00 5 152.0 10.0 SEN-R-1034-031 120 1 114.00 126.00 102.00 5 165.0 9.2 SEN-R-1034-032 130 1 124.00 137.00 111.00 5 179.0 8.5 SEN-R-1034-033 150 1 143.00 158.00 128.00 5 207.0 7.3 SEN-R-1034-034 160 1 152.00 168.00 136.00 5 219.0 6.9 SEN-R-1034-035 170 1 162.00 179.00 145.00 5 234.0 6.5 SEN-R-1034-036 180 1 171.00 189.00 154.00 5 246.0 6.2 SEN-R-1034-037 200 1 190.00 210.00 171.00 5 274.0 5.5 SEN-R-1034-038 220 1 209.00 231.00 185.00 5 328.0 4.6 SEN-R-1034-039 250 1 237.00 263.00 214.00 5 344.0 4.4 SEN-R-1034-040 300 1 285.00 315.00 256.00 5 414.0 3.7 SEN-R-1034-041 350 1 332.00 368.00 300.00 5 482.0 3.2 SEN-R-1034-042 400 1 380.00 420.00 342.00 5 548.0 2.8 SEN-R-1034-0434401418.00462.00376.005600.02.5SENSITRONSEMICONDUCTORTECHNICAL DATADISCLAIMER:1- The information given herein, including the specifications and dimensions, is subject to change without prior notice to improve product characteristics. Before ordering, purchasers are advised to contact the Sensitron Semiconductor sales department for the latest version of the datasheet(s).2- In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, medical equipment, and safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of users’ fail-safe precautions or other arrangement.3- In no event shall Sensitron Semiconductor be liable for any damages that may result from an accident or any other cause during operation of the user’s units according to the datasheet(s). Sensitron Semiconductor assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in the datasheets.4- In no event shall Sensitron Semiconductor be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.5- No license is granted by the datasheet(s) under any patents or other rights of any third party or Sensitron Semiconductor.6- The datasheet(s) may not be reproduced or duplicated, in any form, in whole or part, without the expressed written permission of Sensitron Semiconductor.7- The products (technologies) described in the datasheet(s) are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.。

3RW40说明书

软起动器 3RW4060947-4-2EN/IEC使用说明书订货号:3ZX1012-0RW40-1AA1在安装、操作或维护本设备之前请阅读并掌握这些操作说明。

危险危险电压。

可能造成人员伤亡。

在操作设备之前须切断电源。

只有使用合格部件才能保证本设备的可靠性能。

危险危险电压可能造成人员伤亡。

为避免触电或被电烧伤,在软起动器带电时不能接触软起动器的接线端。

即使软起动器处于“OFF”状态时,输出端仍然带有电压。

GWA 4NEB 535 2193-10 1复位/测试旁通出厂设定中文x I e 电流极限值 5t Ron 加速时间7 sU s 起动电压50 %t Roff 惰转时间0I e 额定电机电流最大值CLASS 等级10RESET MODE 复位模式手动2GWA 4NEB 535 2193-10对“ON/RUN ”输出13/14进行编程(出厂设定为:ON )RESET / TEST 1)RESET MODE 2)DEVICE 3) STATEBYPASSED 4) FAILURE 5) AUTO按压按钮以便保存按压按钮以便转换英文中文1) RESET / TEST 复位/测试2) RESET MODE 复位模式3) DEVICE设备4) STATE BYPASSED 状态旁通5) FAILURE 故障6)AUTO运行OFFON闪烁闪光警告不要在应用之中使用自动复位模式,因为电机的意外自动重启可能对人员或设备造成伤害。

GWA 4NEB 535 2193-10 3L1/L2/L3, T1/T2/T3:电源电路1. A1, A2, 2/-, 3/+, 1 / IN1, 13, 14/24, 23, 95, 96,98:控制电路/辅助电路2. GWA 4NEB 535 2193-104注意软起动器 3RW40 设计用于A类设备。

在民用环境中使用此类产品可能造成无线电干扰。

注意!切断电压!GWA 4NEB 535 2193-10 53RU1900-2A 远程复位3RU1900-2A 远程复位6GWA 4NEB 535 2193-10GWA 4NEB 535 2193-10 73RW40 5: M6 ... 10 Nm3RW40 7: M8 ... 15 Nma b c d e f g h i k l m n o3RW40 5 180 120 37 17 167 100 223 250 180 148 6,5 153 7 1983RW40 7 210 160 48 25 190 140 240 278 205 166 10 166 9 230注意保留足够的自由空间,以便确保用于冷却所需的空气能够从设备底部流通到顶部。

SUM40N03-30L中文资料

FEATURESD TrenchFET r Power MOSFET D 175_C Junction Temperature D 100% R g TestedN-Channel 30-V (D-S) 175_C MOSFETPRODUCT SUMMARYV (BR)DSS (V)r DS(on) (W)I D (A)Q g (Typ)0.030 @ V GS = 10 V 40300.045 @ VGS = 4.5 V3318DRAIN connected to TABTO-263Top ViewOrdering Information:SUM40N03-30L—E3N-Channel MOSFETGDABSOLUTE MAXIMUM RATINGS (T A = 25_C UNLESS OTHERWISE NOTED)ParameterSymbolLimitUnitDrain-Source Voltage V DS 30Gate-Source VoltageV GS "20VT C = 25_C 40Continuous Drain Current (T J = 175_C)T C = 100_CI D 36Pulsed Drain CurrentI DM 40ASingle Pulse Avalanche Current I AS 30Repetitive Avalanche Energy a L = 0.1 mH E AS 31.25mJ T C = 25_C 100b Maximum Power Dissipation aT A = 25_C c P D 3.75W Operating Junction and Storage Temperature RangeT J , T stg−55 to 175_CTHERMAL RESISTANCE RATINGSParameterSymbolLimitUnitJunction-to-Ambient PCB Mount cR thJA 40Junction-to-CaseR thJC1.5_C/WNotesa.Duty cycle v 1%.b.See SOA curve for voltage derating.c.When mounted on 1” square PCB (FR-4 material).SPECIFICATIONS (T J =25_C UNLESS OTHERWISE NOTED)ParameterSymbol Test Condition Min Typ Max UnitStaticDrain-Source Breakdown Voltage V (BR)DSS V DS = 0 V, I D = 250 m A 30Gate-Threshold Voltage V GS(th)V DS = V GS , I D = 250 m A 13V Gate-Body LeakageI GSSV DS = 0 V, V GS = "20 V "100nAV DS = 30 V, V GS = 0 V1Zero Gate Voltage Drain Current I V DS = 30 V, V GS = 0 V, T J = 125_C 50A g DSS V DS = 30 V, V GS = 0 V, T J = 175_C150m On-State Drain Current aI D(on)V DS w 5 V, V GS = 10 V 30A V GS = 10 V, I D = 15 A0.0200.030Drain Source On State Resistance V GS = 10 V, I D = 15 A, T J = 125_C 0.050Drain-Source On-State Resistancea r DS(on)V GS = 10 V, I D = 15 A, T J = 175_C0.054WV GS = 4.5 V, I D = 12.5 A0.0300.045Forward Transconductance ag fsV DS = 15 V, I D = 15 A1022S Dynamic bInput Capacitance C iss 1170Output CapacitanceC oss V GS = 0 V, V DS = 25 V, f = 1 MHz320pFReverse Transfer Capacitance C rss 60Total Gate Charge b Q g 1826Gate-Source Charge b Q gs V = 15 V, V = 10 V, I = 30 A 5.5nC Gate-Drain Charge b Q gd DS ,GS ,D 2Gate Resistance R g 0.91.82.7WTurn-On Delay Time b t d(on)1020Rise Time bt r V W1020Turn-Off Delay Time b t d(off)DD = 15 V, R L = 0.5 I D ^ 30 A, V GEN = 10 V, R g = 2.5 W2540ns Fall Time bt f1530Source-Drain Diode Ratings and Characteristics (T C = 25_C)cContinuous Current I S 40Pulsed Current I SM 40A Forward Voltage a V SD I F = 30 A, V GS = 0 V1.1 1.5V Reverse Recovery Time t rr 50100ns Peak Reverse Recovery Current I RM I = 30 A, di/dt = 100 A/s 3.97.8A Reverse Recovery ChargeQ rrF m 98390nCNotesa.Pulse test; pulse width v 300 m s, duty cycle v 2%.b.Independent of operating temperature.c.Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.612182430816243240030060090012001500612182430CapacitanceTransconductanceOn-Resistance vs. Drain CurrentV DS − Drain-to-Source Voltage (V)V GS − Gate-to-Source Voltage (V)− G a t e -t o -S o u r c e V o l t a g e (V )− O n -R e s i s t a n c e (Q g − Total Gate Charge (nC)V DS − Drain-to-Source Voltage (V)C − C a p a c i t a n c e (p F )r D S (o n )Ω)V G S − T r a n s c o n d u c t a n c e (S )g f s 01234502468103691215180.000.010.020.030.040.050.060.070123456I D − Drain Current (A)TYPICAL CHARACTERISTICS (25_C UNLESS NOTED)0.60.81.01.21.41.61.8−50−250255075100125150175On-Resistance vs. Junction TemperatureSource-Drain Diode Forward VoltageT J − Junction Temperature (_C)V SD − Source-to-Drain Voltage (V)− S o u r c e C u r r e n t (A )I S 1001010.30.60.91.21.5r D S (o n ) − O n -R e s i i s t a n c e (N o r m a l i z e d )THERMAL RATINGSMaximum Drain Current vs. CaseTemperature01020304050255075100125150175Safe Operating Area− D r a i n C u r r e n t (A )I D 200100.11100T C − Case Temperature (_C)− D r a i n C u r r e n t (A )I DTHERMAL RATINGSN o r m a l i z e d E f f e c t i v e T r a n s i e n t T h e r m a l I m p e d a n c eNormalized Thermal Transient Impedance, Junction-to-CaseSquare Wave Pulse Duration (sec)210.10.0110−410−310−210−113Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon T echnology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?73245.。

TNETX3150资料

2

EA0 EA1 EA2 VCC EA3 EA4 EA5 EA6 EA7 EA8 GND EA9 EA10 EA11 EA12 EA13 EA14 VCC EA15 EA16 EA17 EA18 EA19 EA20 GND DWE DRAS DD0 DD1 VCC(5V) DD2 DD3 DD4 DD5 DD6 DD7

元器件交易网

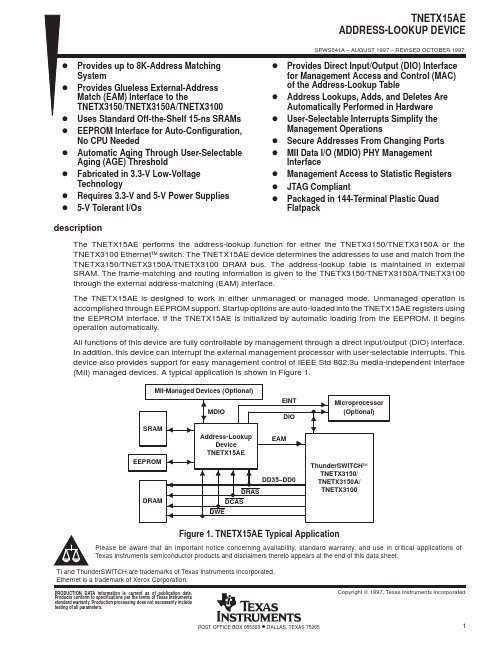

TNETX15AE ADDRESS-LOOKUP DEVICE

SPWS041A – AUGUST 1997 – REVISED OCTOBER 1997

D D D D D D D D

Provides up to 8K-Address Matching System Provides Glueless External-Address Match (EAM) Interface to the TNETX3150/TNETX3150A/TNETX3100 Uses Standard Off-the-Shelf 15-ns SRAMs EEPROM Interface for Auto-Configuration, No CPU Needed Automatic Aging Through User-Selectable Aging (AGE) Threshold Fabricated in 3.3-V Low-Voltage Technology Requires 3.3-V and 5-V Power Supplies 5-V Tolerant I/Os

D D D D D D D D

Provides Direct Input/Output (DIO) Interface for Management Access and Control (MAC) of the Address-Lookup Table Address Lookups, Adds, and Deletes Are Automatically Performed in Hardware User-Selectable Interrupts Simplify the Management Operations Secure Addresses From Changing Ports MII Data I/O (MDIO) PHY Management Interface Management Access to Statistic Registers JTAG Compliant Packaged in 144-Terminal Plastic Quad Flatpack

ULN2003 ULN2003A中文资料

ULN2003 ULN2003A中文资料在自动化密集的的场合会有很多被控元件如继电器,微型电机,风机,电磁阀,空调,水处理等元件及设备,这些设备通常由CPU所集中控制,由于控制系统不能直接驱动被控元件,这需要由功率电路来扩展输出电流以满足被控元件的电流,电压。

ULN2XXXX高压大电流达林顿晶体管阵列系列产品就属于这类可控大功率器件,由于这类器件功能强、应用范围语广。

因此,许多公司都生产高压大电流达林顿晶体管阵列产品,从而形成了各种系列产品。

原理:LN2003也是一个7路反向器电路,即当输入端为高电平时ULN2003输出端为低电平,当输入端为低电平时ULN2003输出端为高电平,继电器得电吸合。

如图九所示功能特点:高电压输出50V输出钳位二极管输入兼容各种类型的逻辑电路应用继电器驱动器ULN200X逻辑图DISSIPATION RATING TABLE耗散评级表TA=25 POWER TA=85 POWER PACKAGEDERATING FACTOR ABOVERATING RATING TA=257.6 mW/? D 950 mW 494 mW9.2 mW/? N 1150 mW 598 mW electrical characteristics, 电气特性(除非另有说明)TA = 25? (unless otherwise noted)ULN2001A ULN2002A TEST CONDITIONS PARAMETEROn-state input voltage VI(on) 6 VCE=2V, IC =300mA 13 V 输入电压II=250μA,IC=100mA 0.9 1.1 0.9 1.1 Collector-emitter 5 VCE(sat) V saturation voltage集电极II=350μA, IC=200mA 1 1.3 1 1.3 -发射极饱和电压II=500μA, IC=350mA 1.2 1.6 1.2 1.6 Clamp forward voltage VF 8 IF = 350mA 1.7 2 1.7 2 V 正向钳位电压1 VCE = 50V, II = 0 50 50 μA Collector cutoff current ICEX II=0 100 100 VCE=50V,TA= 集电极截止电流2 70? VI=6V 500 Off state input current 关VCE=50V,TA=70? II(off)3 50 65 50 65 μA 闭状态下输入电流IC=500μA,Input current 输入电流 II 4 VI = 17 V 0.82 1.25 mAVR=50V, TA=70? 100 100 Clamp reverse current IR 7 μA 反向钳位电流VR = 50 V 50 50 Static forward-currenttransfer ratio 静态正向电hFE 5 VCE=2V, IC =350mA 1000流传输比Input capacitance 输入电 Ci VI = 0, f = 1MHz 15 25 15 25 pF 容electrical characteristics, 电气特性(除非另有说明)TA = 25? (unless otherwise noted)ULN2003A ULN2004APARAMETER TEST CONDITIONSIC=125mA 5IC=200mA 2.4 6IC=250mA 2.7 On state input VI(on) 66 VCE=2V V voltage输入电压IC=275mA 7IC=300mA 3IC=350mA 8ittCollector-emitter II = 250μA, IC=100mA 0.9 1.1 0.9 1.1saturation voltage II = 350μA, IC =200mA 1 1.3 1 1.3 VCE(sat) 5 V 集电极发射极饱和电II = 500μA, IC=350mA 1.2 1.6 1.2 1.6 压1 VCE = 50V, II = 0 50 50 μA Collector cutoffcurrent 集电极截止ICEX II = 0 100 100 VCE=50V,TA=70? 22 电流 VI = 1V 500 Clamp forwardvoltage 正向钳位电VF 8 IF = 350mA 1.7 2 1.7 2 V 压Off state input VCE = 50 V, CE , TA = 70? IC = current 关闭状态下II(off) 33 50 65 50 65 μA 500μA 输入电流Input current输入II 4 VI = 3.85 V 0.93 1.35 mA电流 VI = 5 V 0.35 0.5VI = 12 V 1 1.45Clamp reverse VR = 50 V 50 50 current 反向钳位电IR 77 μA VR = 50 V, TA = 70? 100 100 流Input capacitance Ci VI = 0, f =1MHz 15 25 15 25 pF 输入电容electrical characteristics, 电气特性(除非另有说明)TA = 25? (unless otherwise noted)ULQ2003A ULQ2004A TEST CONDITIONS PARAMETERIC=125mA 5IC=200mA 2.7 6IC=250mA 2.9 On state input voltageVI(on) 6 VCE=2V V 输入电压IC=275mA 7IC=300mA 3IC=350mA 8II = 250μA, IC=100mA 0.9 1.1 0.9 1.1 ittCollector-emittersaturation voltage集电VCE(sat) 5 II = 350μA, IC =200mA 1 1.3 1 1.3 V 极发射极饱和电压II = 500μA, IC=350mA 1.2 1.6 1.2 1.61 VCE = 50V, II = 0 50 50 Collector cutoff current ICEX II = 0 100 100 μA 集电极截止电流 22 VCE=50V VI = 1V 500 Clamp forward voltage VF 8 IF =350mA 1.7 2 1.7 2 V 正向钳位电压Off state input current II(off) 3 VCE =50V, IC=500μA 30 65 50 65μA 关闭状态下输入电流VI = 3.85V 0.93 1.35Input current输入电流 II 4 VI = 5V 0.35 0.5 mAVI = 12V 1 1.45VR = 50V TA =25? 100 50 Clamp reverse current IR 7 μA 反向钳位电流VR = 50V 100 100 Input capacitance输入 Ci VI = 0, f=1MHz 15 25 15 25 pF 电容switching characteristics, 开关特性TA = 25?ULN2001A,ULN2002A, TEST CONDITIONS ULN2003A,ULN2004A PARAMETERPropagation delay time, low- tohigh-level output传播延迟时间,tPLH See Figure 9 0.25 1 μs从低到高输出Propagation delay time, high-to low-level output 传播延迟时tPHL See Figure 9 0.25 1 μs间,从高到低输出High-level output voltage after VS=50V, IO?300mA, See VOH VS–20 mV switching 输出高电平电压 Figure 10switching characteristics over recommended operating conditions (unless otherwisenoted)开关特性的建议运行条件(除非另有说明)ULQ2003A,ULQ2004A TEST CONDITIONS PARAMETERPropagation delay time, low- tohigh-level output 传播延迟时间,tPLH See Figure 9 1 10 μs从低到高输出Propagation delay time, high-to low-level output 传播延迟时tPHL See Figure 9 1 10 μs间,从高到低输出High-level output voltage after VS=50V, IO?300mA, VOH VS–500 mV switching 输出高电平电压 See Figure 10图一 ULN2001A内部电路图图二 ULN2002A内部电路图图三 ULN2003A ULN2004A ULQ2003A ULQ2004A内部电路图图1 ICEX测试电路图2 ICEX测试电路图3 ICEX测试电路图4ICEX测试电路图5 hFE, VCE(sat)测试电路图6 VI(on) 测试电路图四参数测量信息应用电路:图五MOS管加载到输入端图六 TTL电路到输入端图七冲区高电流负载图八使用上拉电阻提高驱动电流图九实际应用的UL2003电路图absolute maximum ratings at=25 free-air temperature (unlessotherwise noted)†at=25Collector-emitter voltage 集电极-发射极电压 50 V Clamp diode reverse voltage 钳位二极管的反向电压(见注1 ) 50 V Input voltage, VI (see Note 1) 输入电压 30 V Peak collector current (see Figures 14 and 15)峰值集电极电流 500 mA Output clamp current, IOK .输出钳位电流 500 mA Totalemitter-terminal current 共发射极端子电流–2.5 A Continuous total power dissipation . 连续总功耗 See Dissipation Rating Table73?/W D packagePackage thermal impedance, θJA 封装热阻(see 67?/W N package Note 2):64?/W NS package–20? to 70? ULN200xA Operating free-air temperature range, TA 自由空气的温度范围内–40? to 85? ULQ200xA260? Lead temperature 1.6mm(1/16inch)from case for 10 seconds Storage temperature range, Tstg 储存温度范围–65? to 150?。

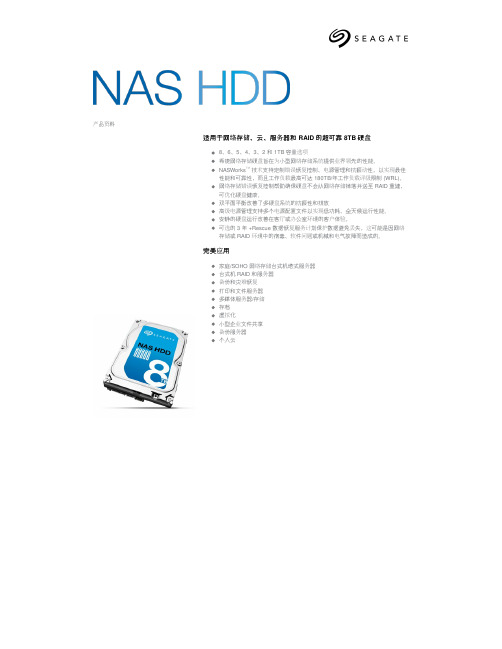

希捷网络存储硬盘说明书

产品资料适用于网络存储、云、服务器和规格8TB6TB4TB型号ST8000VN0002ST6000VN0021ST4000VN000Rescue 型号ST8000VN0012ST6000VN0031ST4000VN003无卤素有有有NASWorks支持的硬盘盘位 1 至 8 1 至 8 1 至 8双平面平衡有有有NASWorks 技术错误恢复控制有有有性能缓存256MB128MB64MB最高可持续传输率216MB/s216MB/s180MB/s接口SATA 6Gb/秒SATA 6Gb/秒SATA 6Gb/秒电源管理启动电流 (12V, A) 2.0 2.0 2.0平均运行功率9.0瓦9.0瓦 4.8瓦平均闲置功率7.2瓦7.2瓦 3.95瓦待机/休眠模式(瓦)0.6瓦/0.6瓦0.6瓦/0.6瓦0.5瓦/0.5瓦环境/温度运行时温度 (°C)0°C ~ 60°C0°C ~ 60°C0°C ~ 70°C非运行时温度 (°C)-40°C ~ 60°C-40°C ~ 60°C-40°C ~ 70°C温度梯度,运行时/非运行时(最大)20°每小时摄氏度/30°每小时摄氏度20°每小时摄氏度/30°每小时摄氏度20°每小时摄氏度/30°每小时摄氏度环境/冲击运行时冲击/非运行时冲击:2 毫秒 (最大)70G/250G70G/250G80G/300G环境/声强空闲(典型)1 2.5贝尔 2.5贝尔 2.3贝尔运行时(典型) 2.6贝尔 2.6贝尔 2.5贝尔可靠性加载/卸载次数2600,000600,000600,000最大不可恢复错误/被读数据(位)1/10E151/10E151/10E15开机小时数876087608760平均无故障时间1,000,000hr1,000,000hr1,000,000hr质保年限333物理规格高度(毫米/英寸)26.11毫米/1.028英寸26.11毫米/1.028英寸26.11毫米/1.028英寸最大宽度(毫米/英寸)101.60毫米/4.0英寸101.6毫米/4.0英寸101.60毫米/4.000英寸, 101.6毫米/4.0英寸最大长度(毫米/英寸)146.99毫米/5.787英寸146.99毫米/5.787英寸146.99毫米/5.787英寸, 26.11毫米/1.028英寸重量(克/磅)780克/1.72磅780克/1.72磅610克/1.345磅纸箱单位数量202020箱数/托盘 / 箱数/层40 / 840 / 840 / 81 闲置测量于“闲置功率1”状态2 加载/卸载测试为 600,000 次循环型号ST3000VN000ST2000VN000ST1000VN000Rescue 型号—ST2000VN001ST1000VN001无卤素有有有支持的硬盘盘位 1 至 8 1 至 8 1 至 8双平面平衡有有无NASWorks 技术错误恢复控制有有有缓存64MB64MB64MB最高可持续传输率180MB/s180MB/s180MB/s接口SATA 6Gb/秒SATA 6Gb/秒SATA 6Gb/秒启动电流 (12V, A) 2.0 2.0 1.2平均运行功率 5.6瓦 5.0瓦 3.6瓦平均闲置功率 4.9瓦 3.7瓦 2.5瓦待机/休眠模式(瓦)0.5瓦/0.5瓦0.8瓦/0.8瓦0.8瓦/0.8瓦运行时温度 (°C)0°C ~ 70°C0°C ~ 70°C0°C ~ 70°C非运行时温度 (°C)-40°C ~ 70°C-40°C ~ 70°C-40°C ~ 70°C温度梯度,运行时/非运行时(最大)20°每小时摄氏度/30°每小时摄氏度20°每小时摄氏度/30°每小时摄氏度20°每小时摄氏度/30°每小时摄氏度运行时冲击/非运行时冲击:2 毫秒 (最大)80G/300G80G/300G80G/300G空闲(典型)1 2.3贝尔 2.3贝尔 2.1贝尔运行时(典型) 2.4贝尔 2.4贝尔 2.3贝尔加载/卸载次数2600,000600,000600,000最大不可恢复错误/被读数据(位)1/10E151/10E151/10E15开机小时数876087608760平均无故障时间1,000,000hr1,000,000hr1,000,000hr质保年限333高度(毫米/英寸)26.11毫米/1.028英寸26.11毫米/1.028英寸19.98毫米/0.787英寸最大宽度(毫米/英寸)101.60毫米/4.0英寸101.60毫米/4.0英寸101.60毫米/4.0英寸最大长度(毫米/英寸)146.99毫米/5.787英寸146.99毫米/5.787英寸146.99毫米/5.787英寸重量(克/磅)610克/1.345磅535克/1.18磅400克/0.88磅纸箱单位数量202025箱数/托盘 / 箱数/层40 / 840 / 840 / 81 闲置测量于“闲置功率1”状态2 加载/卸载测试为 600,000 次循环亚太地区Seagate Singapore International Headquarters Pte. Ltd. 7000 Ang Mo Kio Avenue 5, Singapore 569877, 65-6485-3888欧洲、中东和非洲Seagate Technology SAS 16-18, rue du Dôme, 92100 Boulogne-Billancourt, France, 33 1-4186 10 00美洲地区Seagate Technology LLC 10200 South De Anza Boulevard, Cupertino, California 95014, United States, 408-658-1000© 2015 年希捷科技有限公司版权所有。

安川伺服驱动器 cn3串口通信(中文)

1998年11月12日Σ-Ⅱ系列AC伺服单元SGDM-□□□DA形关于电脑通信方式此规格说明书是SGDM-□□□D形式的作为版本升级模式的SGDM-□□□DA形(设计次序A)用的通信规格说明书。

请在确认机种后再使用。

《目录》1.前言 (5)2.基本通信规格 (5)3.硬件规格 (5)4.连接 (6)4-1.1轴通信连接 (6)4-2.多轴通信连接 (7)4-3.RS232C连接 (8)5.通信用连接器规格 (9)5-1.驱动器CN3 (9)5-2.连接器 (10)6.通信方式 (10)6-1.共通项目 (10)6-2.基本通信定时 (11)6-3.按命令解说 (12)7.地址 (15)7-1.参数区域 (15)7-2.一时参数区域 (16)7-3.操作区域 (16)7-4.跟踪区域 (20)7-5.跟踪控制区域 (20)7-6.监视区域 (26)8.功能 (32)8-1.JOG运转功能 (32)8-2.原点搜索功能 (33)8-3.用户常数初始化功能 (34)8-4.警报跟踪备份清除功能 (35)8-5.在线自动调谐结果写入功能 (36)8-6.旋转圈数数据清除/编码器报警复位功能 (37)8-7.模拟指令自动零调功能 (39)8-8.速度指令手动零调功能 (40)8-9.转矩指令手动零调功能 (41)8-10.模拟监视器手动零调功能 (42)8-11.模拟监视器手动增益调节功能 (43)8-12.电流检测自动零调功能 (44)8-13.电流检测手动零调功能 (45)8-14.数据跟踪功能 (46)8-15.警报复位功能 (50)8-16.指令脉冲计数器清除功能 (50)8-17.反馈脉冲计数器清除功能 (51)8-18.软件复位功能 (52)8-19.旋转圈数上限设定 (54)【使用上的注意】1. 在接计算机进行通信时,因使用了CN3所以就不能连接数字操作器(JUSP-OP02A-2)。

CN3的拔出和插入必须在双方电源关闭的情况下进行。

M295V040-120XN3R中文资料

AI0137219A0-A18W DQ0-DQ7V CCM29F040GE V SS8Figure 1. Logic DiagramM29F0404 Mbit (512Kb x8, Uniform Block) Single Supply Flash MemoryNOT FOR NEW DESIGNM29F040 is replaced by the M29F040B5V ± 10% SUPPLY VOLTAGE for PROGRAM,ERASE and READ OPERATIONS FAST ACCESS TIME: 70nsBYTE PROGRAMMING TIME: 10µs typical ERASE TIME–Block: 1.0 sec typical –Chip: 2.5 sec typicalPROGRAM/ERASE CONTROLLER (P/E.C.)–Program Byte-by-Byte–Data Polling and Toggle bits Protocol for P/E.C. StatusMEMORY ERASE in BLOCKS–8 Uniform Blocks of 64 KBytes each –Block Protection –Multiblock EraseERASE SUSPEND and RESUME MODES LOW POWER CONSUMPTION–Read mode: 8mA typical (at 12MHz)–Stand-by mode: 25µA typical –Automatic Stand-by mode100,000 PROGRAM/ERASE CYCLES per BLOCK20 YEARS DATA RETENTION –Defectivity below 1ppm/year ELECTRONIC SIGNATURE –Manufacturer Code: 20h –Device Code: E2h A0-A18Address Inputs DQ0-DQ7Data Input / Outputs E Chip Enable G Output Enable W Write Enable V CC Supply Voltage V SSGroundTable 1. Signal NamesPLCC32 (K)TSOP32 (N)8 x 20 mmNovember 19991/31This is information on a product still in production but not recommended for new designs.A1A0DQ0A7A4A3A2A6A5A13A10A8A9DQ7A14A11G E DQ5DQ1DQ2DQ3DQ4DQ6A17W A16A12A18V CC A15AI01379M29F040(Normal)8191617242532V SS Figure 2B. TSOP Pin ConnectionsAI01378A 17A13A10D Q 517A1A0DQ0D Q 1D Q 2D Q 3D Q 4A7A4A3A2A6A59W A81A 16A9DQ7A 12A1432A 18V C C M29F040A 15A11D Q 6G E 25V S S Figure 2A. LCC Pin ConnectionsA1A0DQ0A7A4A3A2A6A5A13A10A8A9DQ7A14A11G E DQ5DQ1DQ2DQ3DQ4DQ6A17W A16A12A18V CC A15AI01174BM29F040(Reverse)8191617242532V SS Figure 2C. TSOP Reverse Pin ConnectionsDESCRIPTIONThe M29F040 is a non-volatile memory that may be erased electrically at the block level, and pro-grammed Byte-by-Byte.The interface is directly compatible with most mi-croprocessors. PLCC32 and TSOP32 (8 x 20mm)packages are available. Both normal and reverse pin outs are available for the TSOP32 anisationThe Flash Memory organisation is 512K x8 bits with Address lines A0-A18 and Data Inputs/Outputs DQ0-DQ7. Memory control is provided by Chip Enable, Output Enable and Write Enable Inputs.Erase and Program are performed through the internal Program/Erase Controller (P/E.C.).Data Outputs bits DQ7 and DQ6 provide polling or toggle signals during Automatic Program or Erase to indicate the Ready/Busy state of the internal Program/Erase Controller.Memory BlocksErasure of the memory is in blocks. There are 8uniform blocks of 64 Kbytes each in the memory address space. Each block can be programmed and erased over 100,000 cycles. Each uniform block may separately be protected and unpro-2/31M29F040Symbol Parameter Value Unit T A Ambient Operating Temperature (3)–40 to 125 °CT BIAS Temperature Under Bias–50 to 125 °CT STG Storage Temperature–65 to 150 °CV IO (2)Input or Output Voltages–0.6 to 7 VV CC Supply Voltage–0.6 to 7 VV A9 (2)A9 Voltage–0.6 to 13.5 V Notes:1.Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings"may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any otherconditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute MaximumRating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.2.Minimum Voltage may undershoot to –2V during transition and for less than 20ns.3.Depends on range.Table 2. Absolute Maximum Ratings (1)tected against program and erase. Block erasure may be suspended, while data is read from other blocks of the memory, and then resumed.Bus OperationsSeven operations can be performed by the appro-priate bus cycles, Read Array, Read Electronic Signature, Output Disable, Standby, Protect Block, Unprotect Block, and Write the Command of an Instruction.Command InterfaceCommand Bytes can be written to a Command Interface (C.I.) latch to perform Reading (from the Array or Electronic Signature), Erasure or Pro-gramming. For added data protection, command execution starts after 4 or 6 command cycles. The first, second, fourth and fifth cycles are used to input a code sequence to the Command Interface (C.I.). This sequence is equal for all P/E.C. instruc-tions. Command itself and its confirmation - if it applies - are given on the third and fourth or sixth cycles.InstructionsSeven instructions are defined to perform Reset, Read Electronic Signature, Auto Program, Block Auto Erase, Chip Auto Erase, Block Erase Suspend and Block Erase Resume. The internal Pro-gram/Erase Controller (P/E.C.) handles all timing and verification of the Program and Erase instruc-tions and provides Data Polling, T oggle, and Status data to indicate completion of Program and Erase Operations.Instructions are composed of up to six cycles. The first two cycles input a code sequence to the Com-mand Interface which is common to all P/E.C. instructions (see Table 7 for Command Descrip-tions). The third cycle inputs the instruction set up command instruction to the Command Interface. Subsequent cycles output Signature, Block Protec-tion or the addressed data for Read operations. For added data protection, the instructions for pro-gram, and block or chip erase require further com-mand inputs. For a Program instruction, the fourth command cycle inputs the address and data to be programmed. For an Erase instruction (block or chip), the fourth and fifth cycles input a further code sequence before the Erase confirm command on the sixth cycle. Byte programming takes typically 10µs while erase is performed in typically 1.0 sec-ond.Erasure of a memory block may be suspended, in order to read data from another block, and then resumed. Data Polling, Toggle and Error data may be read at any time, including during the program-ming or erase cycles, to monitor the progress of the operation. When power is first applied or if V CC falls below V LKO, the command interface is reset to Read Array.3/31M29F040Operation E G W DQ0 - DQ7 Read V IL V IL V IH Data Output Write V IL V IH V IL Data Input Output Disable V IL V IH V IH Hi-Z Standby V IH X X Hi-ZNote:X = V IL or V IHTable 3. OperationsCode E G W A0A1A6A9OtherAddressesDQ0 - DQ7 Manufact. Code V IL V IL V IH V IL V IL V IL V ID Don’t Care20h Device Code V IL V IL V IH V IH V IL V IL V ID Don’t Care E2h Table 4. Electronic SignatureCode E G W A0A1A6A16A17A18OtherAddressesDQ0 - DQ7 Protected Block V IL V IL V IH V IL V IH V IL SA SA SA Don’t Care01h Unprotected Block V IL V IL V IH V IL V IH V IL SA SA SA Don’t Care00h Note:SA = Address of block being checkedTable 5. Block Protection StatusDEVICE OPERATIONSignal DescriptionsAddress Inputs (A0-A18). The address inputs for the memory array are latched during a write opera-tion. The A9 address input is used also for the Electronic Signature read and Block Protect veri-fication. When A9 is raised to V ID, either a Read Manufacturer Code, Read Device Code or Verify Block Protection is enabled depending on the com-bination of levels on A0, A1 and A6. When A0, A1 and A6 are Low, the Electronic Signature Manufac-turer code is read, when A0 is High and A1 and A6 are Low, the Device code is read, and when A1 is High and A0 and A6 are low, the Block Protection Status is read for the block addressed by A16, A17, A18.Data Input/Outputs (DQ0-DQ7). The data input is a byte to be programmed or a command written to the C.I. Both are latched when Chip Enable E and Write Enable W are active. The data output is from the memory Array, the Electronic Signature, the Data Polling bit (DQ7), the Toggle Bit (DQ6), the Error bit (DQ5) or the Erase Timer bit (DQ3). Ou-puts are valid when Chip Enable E and Output Enable G are active. The output is high impedance when the chip is deselected or the outputs are disabled.Chip Enable (E). The Chip Enable activates the memory control logic, input buffers, decoders and sense amplifiers. E High deselects the memory and reduces the power consumption to the standby level. E can also be used to control writing to the command register and to the memory array, while W remains at a low level. Addresses are then latched on the falling edge of E while data is latched on the rising edge of E. The Chip Enable must be forced to V ID during Block Unprotect operations. Output Enable (G). The Output Enable gates the outputs through the data buffers during a read operation. G must be forced to V ID level during Block Protect and Block Unprotect operations. Write Enable (W). This input controls writing to the Command Register and Address and Data latches. Addresses are latched on the falling edge of W, and Data Inputs are latched on the rising edge of W. V CC Supply Voltage. The power supply for all operations (Read, Program and Erase).V SS Ground. V SS is the reference for all voltage measurements.4/31M29F040Mne.Instr.Cyc.1st Cyc.2nd Cyc.3rd Cyc.4th Cyc.5th Cyc.6th Cyc.7th Cyc.RST (4,10)Read Array/Reset 1+Addr.(3,7)XRead Memory Array until a new write cycle is initiated.Data F0h3+Addr.(3,7)5555h2AAAh5555h Read Memory Array until a new writecycle is initiated.Data AAh55h F0hRSIG (4)ReadElectronicSignature3+Addr.(3,7)5555h2AAAh5555h Read Electronic Signature until a newwrite cycle is initiated. See Note 5.Data AAh55h90hRBP (4)Read BlockProtection3+Addr.(3,7)5555h2AAAh5555h Read Block Protection until a new writecycle is initiated. See Note 6.Data AAh55h90hPG Program4Addr.(3,7)5555h2AAAh5555h ProgramAddress Read Data Polling or Toggle Bituntil Program completes.Data AAh55h A0h ProgramDataBE Block Erase6Addr.(3,7)5555h2AAAh5555h5555h2AAAh BlockAddressAdditionalBlock (8) Data AAh55h80h AAh55h30h30hCE Chip Erase6Addr.(3,7)5555h2AAAh5555h5555h2AAAh5555hNote 9 Data AAh55h80h AAh55h10hES EraseSuspend1Addr.(3,7)X Read until Toggle stops, then read all the data needed from anyuniform block(s) not being erased then Resume Erase.Data B0hER EraseResume1Addr.(3,7)X Read Data Polling or Toggle Bit until Erase completes or Eraseis suspended another timeData30hNotes:mand not interpreted in this table will default to read array mode.2.While writing any command or during RSG and RSP execution, the P/E.C. can be reset by writing the command 00h to the C.I.3.X = Don’t Care.4.The first cycle of the RST, RBP or RSIG instruction is followed by read operations to read memory array, Status Register orElectronic Signature codes. Any number of read cycles can occur after one command cycle.5.Signature Address bits A0, A1, A6 at V IL will output Manufacturer code (20h). Address bits A0 at V IH and A1, A6 at V IL will outputDevice code.6.Protection Address: A0, A6 at V IL, A1 at V IH and A16, A17, A18 within the uniform block to be checked, will output the Block Protectionstatus.7.Address bits A15-A18 are don’t care for coded address inputs.8.Optional, additional blocks addresses must be entered within a 80µs delay after last write entry, timeout status can be verifiedthrough DQ3 value. When full command is entered, read Data Polling or T oggle bit until Erase is completed or suspended.9.Read Data Polling or T oggle bit until Erase completes.10.A wait time of 5µs is necessary after a Reset command, if the memory is in a Block Erase status, before startingany operation.Table 6. Instructions (1,2)5/31M29F040Memory BlocksThe memory blocks of the M29F040 are shown in Figure 3. The memory array is divided in 8 uniform blocks of 64 Kbytes. Each block can be erased separately or any combination of blocks can be erased simultaneously. The Block Erase operation is managed automatically by the P/E.C. The opera-tion can be suspended in order to read from any other block, and then resumed.Block Protection provides additional data security. Each uniform block can be separately protected or unprotected against Program or Erase. Bringing A9 and G to V ID initiates protection, while bringing A9, G and E to V ID cancels the protection. The block affected during protection is addressed by the in-puts on A16, A17, and A18. Unprotect operation affects all blocks.OperationsOperations are defined as specific bus cycles and signals which allow Memory Read, Command Write, Output Disable, Standby, Read Status Bits, Block Protect/Unprotect, Block Protection Check and Electronic Signature Read. They are shown in Tables 3, 4, 5.Read. Read operations are used to output the contents of the Memory Array, the Status Register or the Electronic Signature. Both Chip Enable E and Output Enable G must be low in order to read the output of the memory. The Chip Enable input also provides power control and should be used for device selection. Output Enable should be used to gate data onto the output independent of the device selection. The data read depends on the previous command written to the memory (see instructions RST and RSIG, and Status Bits).Write. Write operations are used to give Instruction Commands to the memory or to latch input data to be programmed. A write operation is initiated when Chip Enable E is Low and Write Enable W is Low with Output Enable G High. Addresses are latched on the falling edge of W or E whichever occurs last. Commands and Input Data are latched on the rising edge of W or E whichever occurs first.Output Disable. The data outputs are high imped-ance when the Output Enable G is High with Write Enable W High.Standby. The memory is in standby when Chip Enable E is High and Program/Erase Controller P/E.C. is Idle. The power consumption is reduced to the standby level and the outputs are high im-pedance, independent of the Output Enable G or Write Enable W inputs.Automatic Standby. After 150ns of inactivity and when CMOS levels are driving the addresses, the chip automatically enters a pseudo standby mode where consumption is reduced to the CMOS standby value, while outputs are still driving the bus.Electronic Signature. Two codes identifying the manufacturer and the device can be read from the memory, the manufacturer’s code for STMicroelec-tronics is 20h, and the device code is E2h for the M29F040. These codes allow programming equip-ment or applications to automatically match their interface to the characteristics of the particular manufacturer’s product. The Electronic Signature is output by a Read operation when the voltage applied to A9 is at V ID and address inputs A1 and A6 are at Low. The manufacturer code is output when the Address input A0 is Low and the device code when this input is High. Other Address inputs are ignored. The codes are output on DQ0-DQ7. This is shown in Table 4.The Electronic Signature can also be read, without raising A9 to V ID by giving the memory the instruc-tion RSIG (see below).Block Protection. Each uniform block can be separately protected against Program or Erase. Block Protection provides additional data security, as it disables all program or erase operations. This mode is activated when both A9 and G are set to V ID and the block address is applied on A16-A18. Block Protection is programmed using a Presto F program like algorithm. Protection is initiated on the edge of W falling to V IL. Then after a delay of 100µs, the edge of W rising to V IH ends the protection operation. Protection verify is achieved by bringing G, E and A6 to V IL while W is at V IH and A9 at V ID. Under these conditions, reading the data output will yield 01h if the block defined by the inputs on A16-A18 is protected. Any attempt to program or erase a protected block will be ignored by the device.Any protected block can be unprotected to allow updating of bit contents. All blocks must be pro-tected before an unprotect operation. Block Un-protect is activated when A9, G and E are at V ID. The addresses inputs A6, A12, A16 must be main-tained at V IH. Block Unprotect is performed through a Presto F Erase like algorithm. Unprotect is initi-ated by the edge of W falling to V IL. After a delay of 10ms, the edge of W rising to V IH will end the unprotection operation. Unprotect verify is achieved by bringing G and E to V IL while A6 and W are at V IH and A9 at V ID. In these conditions, reading the output data will yield 00h if the block defined by the inputs on A16-A18 has been suc-cessfully unprotected. All combinations of A16-A18 must be addressed in order to ensure that all of the 8 uniform blocks have been unprotected. Block Protection Status is shown in Table 5.6/31M29F04064K Bytes Block AI01362B7FFFFh 6FFFFh 5FFFFh 4FFFFh 3FFFFh 2FFFFh 1FFFFh 0FFFFhTOP ADDRESS 70000h 60000h 50000h 40000h 30000h 20000h 10000h 00000hBOTTOM ADDRESS A181164K Bytes Block 64K Bytes Block64K Bytes Block 64K Bytes Block A1711A16101100100011100010Figure 3. Memory Map and Block Address TableHex Code Command00h Read10h Chip Erase Confirm30h Block Erase Resume/Confirm 80h Set-up Erase90h Read Electronic Signature/Block Protection Status A0h Program B0h Erase Suspend F0hRead Array/ResetTable 7. CommandsInstructions and CommandsThe Command Interface (C.I.) latches commands written to the memory. Instructions are made up from one or more commands to perform Read Array/Reset, Read Electronic Signature, Block Erase, Chip Erase, Program, Block Erase Suspend and Erase Resume. Commands are made of ad-dress and data sequences. Addresses are latched on the falling edge of W or E and data is latched on the rising of W or E. The instructions require from 1 to 6 cycles, the first or first three of which are always write operations used to initiate the com-mand. They are followed by either further write cycles to confirm the first command or execute the command immediately. Command sequencing must be followed exactly. Any invalid combination of commands will reset the device to Read Array.The increased number of cycles has been chosen to assure maximum data security. Commands are initialised by two preceding coded cycles which unlock the Command Interface. In addition, for Erase, command confirmation is again preceeded by the two coded cycles.P/E.C. status is indicated during command execu-tion by Data Polling on DQ7, detection of Toggle onDQ6, or Error on DQ5 and Erase Timer DQ3 bits.Any read attempt during Program or Erase com-mand execution will automatically output those four bits. The P/E.C. automatically sets bits DQ3, DQ5,DQ6 and DQ7. Other bits (DQ0, DQ1, DQ2 and DQ4) are reserved for future use and should be masked.7/31M29F040DQ Name Logic Level Definition Note7DataPolling’1’Erase CompleteIndicates the P/E.C. status, check duringProgram or Erase, and on completionbefore checking bits DQ5 for Program orErase Success.’0’Erase on GoingDQ Program CompleteDQ Program on Going6Toggle Bit ’-1-0-1-0-1-0-1-’Erase or Program on Going Successive read output complementarydata on DQ6 while Programming or Eraseoperations are going on. DQ6 remain atconstant level when P/E.C. operations arecompleted or Erase Suspend isacknowledged.’-0-0-0-0-0-0-0-’Program (’0’ on DQ6)Complete’-1-1-1-1-1-1-1-’Erase or Program(’1’ on DQ6) Complete5Error Bit ’1’Program or Erase Error This bit is set to ’1’ if P/E.C. has excededthe specified time limits.’0’Program or Erase on Going4’1’’0’3EraseTime Bit ’1’Erase Timeout Period Expired P/E.C. Erase operation has started. Onlypossible command entry is Erase Suspend(ES). An additional block to be erased inparallel can be entered to the P/E.C.’0’Erase Timeout Period onGoing2Reserved1Reserved0ReservedNote:Logic level ’1’ is High, ’0’ is Low. -0-1-0-0-0-1-1-1-0- represent bit value in successive Read operations. Table 8. Status RegisterData Polling bit (DQ7). When Programming op-erations are in progress, this bit outputs the com-plement of the bit being programmed on DQ7. During Erase operation, it outputs a ’0’. After com-pletion of the operation, DQ7 will output the bit last programmed or a ’1’ after erasing. Data Polling is valid only effective during P/E.C. operation, that is after the fourth W pulse for programming or after the sixth W pulse for Erase. It must be performed at the address being programmed or at an address within the block being erased. If the byte to be programmed belongs to a protected block the com-mand is ignored. If all the blocks selected for era-sure are protected, DQ7 will set to ’0’ for about 100µs, and then return to previous addressed memory data. See Figure 9 for the Data Polling flowchart and Figure 10 for the Data Polling wave-forms.Toggle bit (DQ6). When Programming operations are in progress, successive attempts to read DQ6 will output complementary data. DQ6 will toggle following toggling of either G or E when G is low.The operation is completed when two successive reads yield the same output data. The next read will output the bit last programmed or a ’1’ after erasing. The toggle bit is valid only effective during P/E.C. operations, that is after the fourth W pulse for programming or after the sixth W pulse for Erase. If the byte to be programmed belongs to a protected block the command will be ignored. If the blocks selected for erasure are protected, DQ6 will toggle for about 100µs and then return back to Read. See Figure 11 for Toggle Bit flowchart and Figure 12 for Toggle Bit waveforms.Error bit (DQ5). This bit is set to ’1’ by the P/E.C when there is a failure of byte programming, block erase, or chip erase that results in invalid data being programmed in the memory block. In case of error in block erase or byte program, the block in which the error occured or to which the pro-grammed byte belongs, must be discarded. Other blocks may still be used. Error bit resets after Reset (RST) instruction. In case of success, the error bit will set to ’0’ during Program or Erase and to valid data after write operation is completed.8/31M29F040AI01275B3VHigh Speed0V1.5V2.4VStandard 0.45V2.0V 0.8VFigure 4. AC Testing Input Output Waveform AI01276B1.3VOUTC LC L = 30pF for High Speed C L = 100pF for Standard C L includes JIG capacitance3.3k Ω1N914DEVICE UNDER TESTFigure 5. AC Testing Load CircuitSymbol ParameterTest ConditionMinMax Unit C IN Input Capacitance V IN = 0V 6pF C OUTOutput CapacitanceV OUT = 0V12pFNote: 1.Sampled only, not 100% tested.Table 10. Capacitance (1) (T A = 25 °C, f = 1 MHz )Erase Timer bit (DQ3). This bit is set to ’0’ by the P/E.C. when the last Block Erase command has been entered to the Command Interface and it is awaiting the Erase start. When the wait period is finished, after 80 to 120µs, DQ3 returns back to ’1’.Coded Cycles. The two coded cycles unlock the Command Interface. They are followed by a com-mand input or a comand confirmation. The coded cycles consist of writing the data AAh at address 5555h during the first cycle and data 55h at address 2AAAh during the second cycle. Addresses are latched on the falling edge of W or E while data is latched on the rising edge of W or E. The coded cycles happen on first and second cycles of the command write or on the fourth and fifth cycles.Read Array/Reset (RST) instruction. The Reset instruction consists of one write operation giving the command F0h. It can be optionally preceded by the two coded cycles. A wait state of 5µs before read operations is necessary if the Reset command is applied during an Erase operation.Read Electronic Signature (RSIG) instruction.This instruction uses the two coded cycles followed by one write cycle giving the command 90h to address 5555h for command setup. A subsequent read will output the manufacturer code, the device code or the Block Protection status depending on the levels of A0, A1, A6, A16, A17 and A18. The manufacturer code, 20h, is output when the ad-dresses lines A0, A1 and A6 are Low, the device code, E2h is output when A0 is High with A1 and A6 Low.High SpeedStandard Input Rise and Fall Times ≤ 10ns ≤ 10ns Input Pulse Voltages0 to 3V 0.45V to 2.4V Input and Output Timing Ref. Voltages1.5V0.8V and 2VTable 9. AC Measurement Conditions9/31M29F040Symbol ParameterTest Condition MinMax Unit I LI Input Leakage Current 0V ≤ V IN ≤ V CC ±1µA I LO Output Leakage Current 0V ≤ V OUT ≤ V CC ±1µA I CC1Supply Current (Read) E = V IL , G = V IH , f = 6MHz15mA I CC2Supply Current (Standby) TTL E = V IH 1mA I CC3Supply Current (Standby) CMOS E = V CC ± 0.2V 50µA I CC4Supply Current (Program or Erase)Byte Program, Block Erase 20mA I CC5Supply Current Chip Erase in progress40mA V IL Input Low Voltage –0.50.8V V IH Input High Voltage 2V CC + 0.5V V OL Output Low Voltage I OL = 10mA 0.45V V OHOutput High Voltage TTLI OH = –2.5mA 2.4V Output High Voltage CMOSI OH = –100µA V CC –0.4V I OH = –2.5mA0.85 V CC V V ID A9 Voltage (Electronic Signature)11.512.5V I ID A9 Current (Electronic Signature)A9 = V ID50µA V LKOSupply Voltage (Erase and Program lock-out)3.24.2VTable 11. DC Characteristics(T A = 0 to 70°C, –20 to 85°C, –40 to 85°C or –40 to 125°C; V CC = 5V ± 10%)Read Block Protection (RBP) instruction. The use of Read Electronic Signature (RSIG) command also allows access to the Block Protection status verify. After giving the RSIG command, A0 and A6are set to V IL with A1 at V IH , while A16, A17 and A18 define the block of the block to be verified. A read in these conditions will output a 01h if block is protected and a 00h if block is not protected.This Read Block Protection is the only valid way to check the protection status of a block. Neverthe-less, it must not be used during the Block Protection phase as a method to verify the block protection.Please refer to Block Protection paragraph.Chip Erase (CE) instruction. This instruction uses six write cycles. The Erase Set-up command 80h is written to address 5555h on third cycle after the two coded cycles. The Chip Erase Confirm com-mand 10h is written at address 5555h on sixth cycle after another two coded cycles. If the second com-mand given is not an erase confirm or if the coded cycles are wrong, the instruction aborts and the device is reset to Read Array. It is not necessary to program the array with 00h first as the P/E.C. will automatically do this before erasing to FFh. Read operations after the sixth rising edge of W or E output the status register bits. During the execu-tion of the erase by the P/E.C. the memory accepts only the Reset (RST) command. Read of Data Polling bit DQ7 returns ’0’, then ’1’ on completion.The T oggle Bit DQ6 toggles during erase operation and stops when erase is completed. After comple-tion the Status Register bit DQ5 returns ’1’ if there has been an Erase Failure because the erasure has not been verified even after the maximum number of erase cycles have been executed.10/31M29F040SymbolAltParameterTest ConditionM29F040Unit-70-90V CC = 5V ± 5%V CC = 5V ± 10%Standard Interface Standard Interface MinMaxMin Maxt AVAV t RC Address Valid to Next Address Valid E = V IL , G = V IL 7090ns t AVQV t ACC Address Valid to Output Valid E = V IL , G = V IL7090ns t ELQX (1)t LZ Chip Enable Low to Output Transition G = V IL 0ns t ELQV (2)t CE Chip Enable Low to Output Valid G = V IL 7090ns t GLQX (1)t OLZ Output Enable Low to Output TransitionE = V IL 0ns t GLQV (2)t OE Output Enable Low to Output Valid E = V IL 3035ns t EHQX t OH Chip Enable High to Output TransitionG = V IL 0ns t EHQZ (1)t HZ Chip Enable High to Output Hi-Z G = V IL 2020ns t GHQX t OH Output Enable High to Output TransitionE = V IL 0ns t GHQZ (1)t DF Output Enable High to Output Hi-Z E = V IL 2020ns t AXQXt OHAddress Transition to Output TransitionE = V IL , G = V IL2020ns Notes:1.Sampled only, not 100% tested.2.G may be delayed by up to t ELQV - t GLQV after the falling edge of E without increasing t ELQV .3.The temperature range –40 to 125°C is guaranteed at 70ns with High Speed Interface test condition and V CC = 5V ± 5%.Table 12A. Read AC Characteristics(T A = 0 to 70°C, –20 to 85°C, –40 to 85°C or –40 to 125°C)(3)Block Erase (BE) instruction . This instruction uses a minimum of six write cycles. The Erase Set-up command 80h is written to address 5555h on third cycle after the two coded cycles. The Block Erase Confirm command 30h is written on sixth cycle after another two coded cycles. During the input of the second command an address within the block to be erased is given and latched into the memory. Additional Block Erase confirm com-mands and block addresses can be written sub-sequently to erase other blocks in parallel, without further coded cycles. The erase will start after an Erase timeout period of about 100µs. Thus, addi-tional Block Erase commands must be given within this delay. The input of a new Block Erase com-mand will restart the timeout period. The status of the internal timer can be monitored through the level of DQ3, if DQ3 is ’0’ the Block Erase Com-mand has been given and the timeout is running, if DQ3 is ’1’, the timeout has expired and the P/E.Cis erasing the block(s). Before and during Erase timeout, any command different from 30h will abort the instruction and reset the device to read array mode. It is not necessary to program the block with 00h as the P/E.C. will do this automatically before erasing to FFh. Read operations after the sixth rising edge of W or E output the status register bits.During the execution of the erase by the P/E.C., the memory accepts only the ES (Erase Suspend) and RST (Reset) instructions. Data Polling bit DQ7returns ’0’ while the erasure is in progress and ’1’when it has completed. The Toggle Bit DQ6 toggles during the erase operation. It stops when erase is completed. After completion the Status Register bit DQ5 returns ’1’ if there has been an Erase Failure because erasure has not completed even after the maximum number of erase cycles have been executed. In this case, it will be necessary to input a Reset (RST) to the command interface in order to reset the P/E.C.11/31。

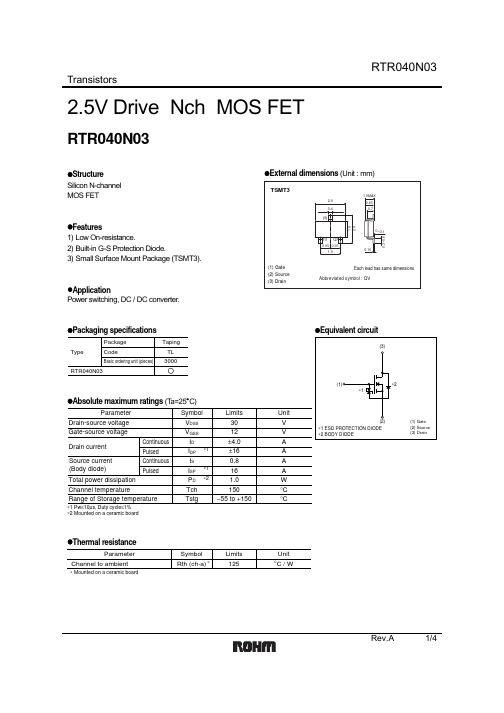

rtr040n03

Transistors Rev.A 1/42.5V Drive Nch MOS FETRTR040N03z StructureSilicon N-channel MOS FETz Features1) Low On-resistance.2) Built-in G-S Protection Diode.3) Small Surface Mount Package (TSMT3).z ApplicationPower switching, DC / DC converter.z External dimensions (Unit : mm)z Packaging specificationsz Absolute maximum ratings (T a=25°C)∗1∗1∗2ParameterV V DSS Symbol 30V V GSS 12A I D±4.0A I DP ±16A I S0.8A I SP 16W P D 1.0°C Tch 150°CTstg −55 to +150Limits Unit Drain-source voltage Gate-source voltage Drain current Total power dissipation Channel temperatureRange of Storage temperatureContinuous Pulsed Continuous Pulsed∗1 Pw ≤10µs, Duty cycle ≤1%∗2 Mounted on a ceramic boardSource current (Body diode)z Equivalent circuitz Thermal resistance°C / WRth (ch-a)125ParameterSymbol Limits Unit Channel to ambient∗ Mounted on a ceramic board∗Transistors Rev.A 2/4z Electrical characteristics (T a=25°C)z Body diode characteristics (Source-drain) (T a=25°C)V SD−−1.2VForward voltageI S = 0.8A, V GS =0VParameterSymbol Min.Typ.Max.Unit ConditionsTransistors Rev.A 3/4z Electrical characteristic curves0.0010.010.1110GATE-SOURCE VOLTAGE : V GS (V)Fig.1 Typical Transfer CharacteristicsD R A I N C U R RE N T : I D (A)S T A T I C D R A I N -S O U R C E O N -S TA T E R E S I S T A N C E : R D S (o n ) (m Ω)DRAIN CURRENT : I D (A)Fig.2 Static Drain-Source On-StateResistance vs. Drain Current S T A T I C D R A I N -S O U R C E O N -S T A T ER E S I S T A N C E : R D S (o n ) (m Ω)DRAIN CURRENT : I D (A)Fig.3 Static Drain-Source On-StateResistance vs. Drain CurrentS T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n ) (m Ω)DRAIN CURRENT : I D (A)Fig.4 Static Drain-Source On-StateResistance vs. Drain CurrentS T A T I CD R A I N -S O U R CE O N -S T A T E R E S I S T A N C E : R D S (o n ) (m Ω)GATE SOURCE VOLTAGE : V GS (V)Fig.5 Static Drain-Source On-StateResistance vs. Gate-Source Voletage S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E :R D S (o n ) (m Ω)DRAIN CURRENT : I D (A)Fig.6 Static Drain-Source On-StateResistance vs. Drain CurrentS O U R C E C U R R E N T : I S (A )SOURCE-DRAIN VOLTAGE : V S D (V)Fig.7 Source Currentvs. Source-Drain Voltage101001000CA P A C I T A N C E : C (p F )DRAIN SOURCE VOLTAGE : V DS (V)Fig.8 Typical Capacitancevs. Drain-Source VoltageS W I T C H I N G T I M E : t (n s )DRAIN CURRENT : I D (A)Fig.9 Switching CharacteristicsTransistors Rev.A 4/4G A T E -S O U R C E V O L T A G E : V G S (V )TOTAL GATE CHARGE : Qg (nC)Fig.10 Dynamic Input CharacteristicszMeasurement circuitsFig.11 Switching Time Test Circuit V DSFig.12 Switching Time WaveformsV GS V DSFig.13 Gate Charge Test CircuitI V DSFig.14 Gate Charge Waveform VAppendixAbout Export Control Order in JapanProducts described herein are the objects of controlled goods in Annex 1 (Item 16) of Export T rade ControlOrder in Japan.In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause)on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.Appendix1-Rev1.1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Transistors 1/4

Switching (30V, 4.0A)

RTR040N03

z Features

1) Low On-resistance.

2) Built-in G-S Protection Diode.

3) Small and Surface Mount Package (TSMT3).

z Application

Power switching, DC / DC converter.

z Structure

Silicon N-channel MOS FET

z External dimensions (Unit : mm)

z Absolute maximum ratings (T a=25°C)

∗1∗1∗2Parameter

V V DSS Symbol 30V V GSS 12A I D

±4.0A I DP ±16A I S

0.8A I SP 16W P D 1.0°C Tch 150°C

Tstg −55 to +150Limits Unit Drain-source voltage Gate-source voltage Drain current Total power dissipation Channel temperature

Range of Storage temperature

Continuous Pulsed Continuous Pulsed

∗1 Pw ≤10µs, Duty cycle ≤1%∗2 Mounted on a ceramic board

Source current (Body diode)

z Equivalent circuit

z Thermal resistance (T a=25°C)

°C / W

Rth (ch-a)

125

Parameter

Symbol Limits Unit Channel to ambient

Transistors

z Electrical characteristics (T a=25°C)

2/4

Transistors 3/4

z Electrical characteristic curves

0.001

0.01

0.11

10

GATE-SOURCE VOLTAGE : V GS (V)

Fig.1 Typical Transfer Characteristics

D R A I N C U R R

E N T : I D (A

)

S T A T I C D R A I N -S O U R C E O N -S T

A T E R E S I S T A N C E : R D S (o n ) (m Ω)

DRAIN CURRENT : I D (A)Fig.2 Static Drain-Source On-State

Resistance vs. Drain Current S T A T I C D R A I N -S O U R C E O N -S T A T E

R E S I S T A N C E : R D S (o n ) (m Ω)

DRAIN CURRENT : I D (A)

Fig.3 Static Drain-Source On-State

Resistance vs. Drain Current

S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n ) (m Ω)

DRAIN CURRENT : I D (A)Fig.4 Static Drain-Source On-State

Resistance vs. Drain Current

S T A T I C

D R A I N -S O U R C

E O N -S T A T E R E S I S T A N C E : R D S (o n ) (m Ω)

GATE SOURCE VOLTAGE : V GS (V)Fig.5 Static Drain-Source On-State

Resistance vs. Gate-Source Voletage S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E :

R D S (o n ) (m Ω)

DRAIN CURRENT : I D (A)

Fig.6 Static Drain-Source On-State

Resistance vs. Drain Current

S O U R C E C U R R E N T : I S (A )

SOURCE-DRAIN VOLTAGE : V S D (V)Fig.7 Source Current

vs. Source-Drain Voltage 10100

1000

C A P A C I T A N C E : C (p F )

DRAIN SOURCE VOLTAGE : V DS (V)

Fig.8 Typical Capacitance

vs. Drain-Source Voltage

S W I T C H I N G T I M E : t (n s )

DRAIN CURRENT : I D (A)

Fig.9 Switching Characteristics

Transistors 4/4

G A T E -S O U R C E V O L T A G E : V G S (V )

TOTAL GATE CHARGE : Qg (nC)

Fig.10 Dynamic Input Characteristics

z Measurement circuits

Fig.11 Switching Time Test Circuit V DS

Fig.12 Switching Time Waveforms

V GS V DS

Fig.13 Gate Charge Test Circuit

I V DS

Fig.14 Gate Charge Waveform V

Appendix

About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export T rade Control

Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause)

on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.

Appendix1-Rev1.1。