xilinxfpga引脚功能详细介绍

Xilinx FPGA 引脚功能详细介绍之令狐文艳创作

XilinxFPGA引脚功能详细介绍令狐文艳注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

关于XilinxFPGAZYNQ的引脚定义

关于XilinxFPGAZYNQ的引脚定义器件的引脚定义如何获得?在官⽹找到Pin-Out⽂件,⽹址:⽂件⾥⾯给出了引脚编号对应的引脚名称、IO Bank分组、IO种类(MIO,High Rate通⽤IO,DDR等)。

这些封装对应到Processing System 7 IP中的MIO设定,就可以得到MIO的固定引脚。

另外,ZYNQ7000系列的引脚定义⽂件在这⾥(CSV和TXT)://**********************************************************************************************************************************//**********************************************************************************************************************************//**********************************************************************************************************************************例如,IP核中选择以太⽹MAC控制器的引脚是MIO[27:16],则在下表中寻找MIO[16],……,MIO[27]即可,最左边即是引脚编号。

(电路设计时注意Bank500和Bank501的IO电压分配)在UG585(v1.12.2)中的Table 2-4:MIO-at-a-Glance中,对MIO的功能进⾏了详细的描述:表中信息包括了MIO编号、所在的IO Bank、引脚复⽤情况、引脚对应外设的功能。

如果使⽤以太⽹控制器ETH0,则MIO16是TX_CLK,MIO17~MIO20是TX_DATA[0]~TX_DATA[3],MIO21是TX_CTRL对于不明确的MIO引脚定义,将⿏标悬停在MIO编号栏就可以看到信号定义:我们还通过Block Diagram综合后的报告查看,⽬标位于:${Vivado Project Path}\eth_mac_01.srcs\sources_1\bd\block_01\ip\block_01_processing_system7_0_2,是以html格式呈现的:这样就完成了MIO功能到封装引脚的映射过程。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx-FPGA器件管脚说明doc

弱上拉

I/O

内部有弱上拉。可以随逻辑需要配置成输入或输出。在配置完成前,这些引脚有内部上拉电阻(25K-100K)至高电平。

在配置模式,这些引脚有弱上拉电阻。对大多数流行的配置模式来而言,在从动串行模式下,模式引脚不需要连接。在有或没有弱上拉或上拉电阻的情况下,三个模式输入引脚可以独自配置。推荐上拉电阻值为4.7K。在特殊定义时,这些引脚只能被作为输入或输出。为应用这些引脚,必须使用库元件MD0、MD1和MD2代替通常的PAD,同时必须使用输入输出缓冲器。

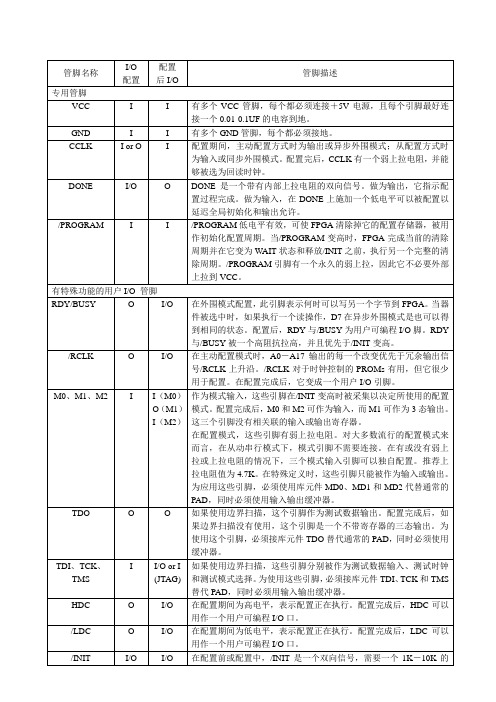

管脚名称

I/O

配置

配置

后I/O

管脚描述

专用管脚

VCC

I

I

有多个VCC管脚,每个都必须连接+5V电源,且每个引脚最好连接一个0.01-0.1UF的电容到地。

GND

I

I

有多个GND管脚,每个都必须接地。

CCLK

I or O

I

配置期间,主动配置方式时为输出或异步外围模式;从配置方式时为输入或同步外围模式。配置完后,CCLK有一个弱上拉电阻,并能够被选为回读时钟。

HDC

O

I/O

在配置期间为高电平,表示配置正在执行。配置完成后,HDC可以用作一个用户可编程I/O口。

/LDC

O

I/O

在配置期间为低电平,表示配置正在执行。配置完成后,LDC可以用作一个用户可编程I/O口。

/INIT

I/O

I/O

在配置前或配置中,/INIT是一个双向信号,需要一个1K-10K的外部上拉电阻。作为一个低电平有效输出,/INIT在电源稳定和清除内部配置内存期间保持低电平。作为一个低电平有效输入,/INIT能在开始配置前保持FPGA在内部WAIT状态。主动模式下,在/INIT变高后,器件将在WAIT状态保持30+300US。在配置期间,输出为低表示配置数据错误。当I/O有效后,/INIT为一个用户可编程I/O引脚。

AlteraFPGA和Xilinx-FPGA-引脚功能详解解读

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

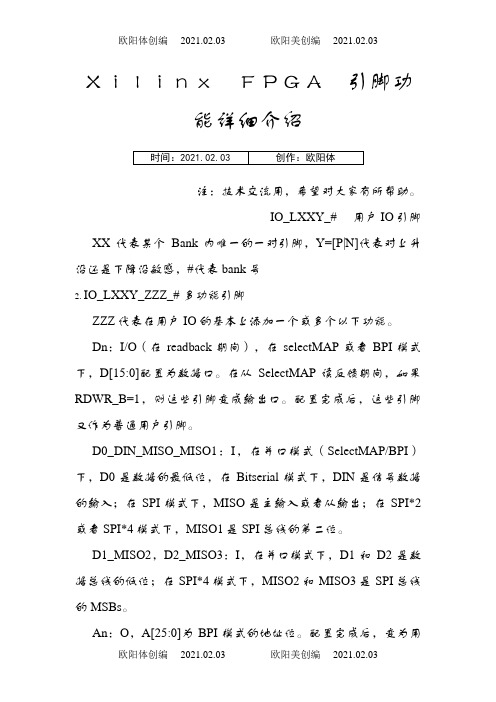

Xilinx FPGA 引脚功能详细介绍之欧阳体创编

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

FPGA__xilinx管脚说明

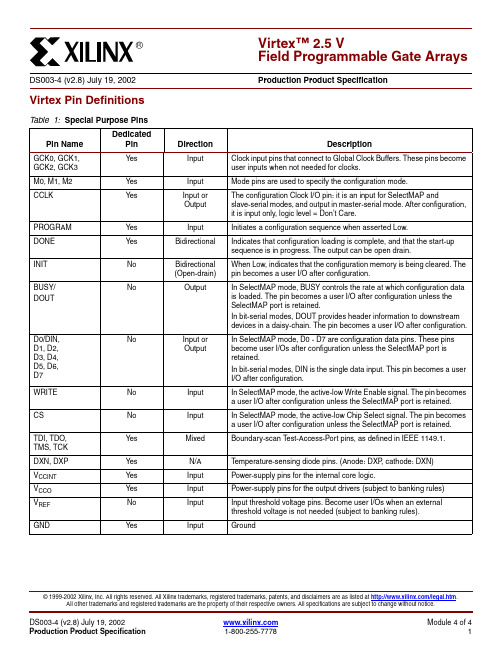

© 1999-2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.Virtex Pin DefinitionsVirtex™ 2.5 VField Programmable Gate ArraysDS003-4 (v2.8) July 19, 2002Production Product SpecificationTable 1: Special Purpose PinsPin NameDedicatedPinDirectionDescriptionGCK0, GCK1, GCK2, GCK3Y es Input Clock input pins that connect to Global Clock Buffers. These pins become user inputs when not needed for clocks.M0, M1, M2Y es InputMode pins are used to specify the configuration mode.CCLKY esInput or Output The configuration Clock I/O pin: it is an input for SelectMAP andslave-serial modes, and output in master-serial mode. After configuration, it is input only, logic level = Don’t Care.PROGRAM Y es Input Initiates a configuration sequence when asserted Low.DONE Y es Bidirectional Indicates that configuration loading is complete, and that the start-up sequence is in progress. The output can be open drain.INIT No Bidirectional (Open-drain)When Low, indicates that the configuration memory is being cleared. The pin becomes a user I/O after configuration.BUSY/DOUTNoOutputIn SelectMAP mode, BUSY controls the rate at which configuration data is loaded. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.In bit-serial modes, DOUT provides header information to downstream devices in a daisy-chain. The pin becomes a user I/O after configuration.D0/DIN,D1, D2,D3, D4,D5, D6,D7NoInput or OutputIn SelectMAP mode, D0 - D7 are configuration data pins. These pins become user I/Os after configuration unless the SelectMAP port is retained.In bit-serial modes, DIN is the single data input. This pin becomes a user I/O after configuration.WRITE No Input In SelectMAP mode, the active-low Write Enable signal. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.CS No Input In SelectMAP mode, the active-low Chip Select signal. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.TDI, TDO,TMS, TCK Y es Mixed Boundary-scan T est-Access-Port pins, as defined in IEEE 1149.1.DXN, DXP Y es N/A Temperature-sensing diode pins. (Anode: DXP , cathode: DXN)V CCINT Y es Input Power-supply pins for the internal core logic.V CCO Y es Input Power-supply pins for the output drivers (subject to banking rules)V REF No Input Input threshold voltage pins. Become user I/Os when an external threshold voltage is not needed (subject to banking rules).GNDY esInputGroundVirtex Pinout InformationPinout TablesSee for updates or additional pinout information. For convenience, Table2, T able3 and Table4 list the locations of special-purpose and power-supply pins. Pins not listed are either user I/Os or not connected, depending on the device/package combination. See the Pinout Diagrams starting on page17 for any pins not listed for a particular part/package combination.Table 2: Virtex Pinout Tables (Chip-Scale and QFP Packages)Pin Name Device CS144TQ144PQ/HQ240GCK0All K79092GCK1All M79389GCK2All A719210GCK3All A616213M0All M111060M1All L211258M2All N210862CCLK All B1338179PROGRAM All L1272122DONE All M1274120INIT All L1371123BUSY/DOUT All C1139178D0/DIN All C1240177D1All E1045167D2All E1247163D3All F1151156D4All H1259145D5All J1363138D6All J1165134D7All K1070124WRITE All C1032185CS All D1033184TDI All A1134183TDO All A1236181TMS All B11432TCK All C32239V CCINT All A9, B6, C5, G3,G12, M5, M9, N610, 15, 25, 57, 84, 94,99, 12616, 32, 43, 77, 88, 104,137, 148, 164, 198,214, 225V CCO All Banks 0 and 1:A2, A13, D7Banks 2 and 3:B12, G11, M13Banks 4 and 5:N1, N7, N13Banks 6 and 7:B2, G2, M2No I/O Banks in thispackage:1, 17, 37, 55, 73, 92,109, 128No I/O Banks in thispackage:15, 30, 44, 61, 76, 90,105, 121, 136, 150, 165,180, 197, 212, 226, 240V REF, Bank 0(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50C4, D65, 13218, 232 XCV100/150... + B4... + 7... + 229 XCV200/300N/A N/A... + 236 XCV400N/A N/A... + 215 XCV600N/A N/A... + 230 XCV800N/A N/A... + 222V REF, Bank 1(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50A10, B822, 30191, 205 XCV100/150... + D9... + 28... + 194 XCV200/300N/A N/A... + 187 XCV400N/A N/A... + 208 XCV600N/A N/A... + 193 XCV800N/A N/A... + 201V REF, Bank 2(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50D11, F1042, 50157, 171 XCV100/150... + D13... + 44... + 168 XCV200/300N/A N/A... + 175 XCV400N/A N/A... + 154 XCV600N/A N/A... + 169 XCV800N/A N/A... + 161Table 2: Virtex Pinout Tables (Chip-Scale and QFP Packages) (Continued)Pin Name Device CS144TQ144PQ/HQ240V REF, Bank 3(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50H11, K1260, 68130, 144 XCV100/150... + J10... + 66... + 133 XCV200/300N/A N/A... + 126 XCV400N/A N/A... + 147 XCV600N/A N/A... + 132 XCV800N/A N/A... + 140V REF, Bank 4(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50L8, L1079, 8797, 111 XCV100/150... + N10... + 81... + 108 XCV200/300N/A N/A... + 115 XCV400N/A N/A... + 94 XCV600N/A N/A... + 109 XCV800N/A N/A... + 101V REF, Bank 5(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50L4, L696, 10470, 84 XCV100/150... + N4... + 102... + 73 XCV200/300N/A N/A... + 66 XCV400N/A N/A... + 87 XCV600N/A N/A... + 72 XCV800N/A N/A... + 80Table 2: Virtex Pinout Tables (Chip-Scale and QFP Packages) (Continued)Pin Name Device CS144TQ144PQ/HQ240V REF, Bank 6(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50H2, K1116, 12336, 50 XCV100/150... + J3... + 118... + 47 XCV200/300N/A N/A... + 54 XCV400N/A N/A... + 33 XCV600N/A N/A... + 48 XCV800N/A N/A... + 40V REF, Bank 7(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, allV REF pins are general I/O.XCV50D4, E1133, 1409, 23 XCV100/150... + D2... + 138... + 12 XCV200/300N/A N/A... + 5 XCV400N/A N/A... + 26 XCV600N/A N/A... + 11 XCV800N/A N/A... + 19GND All A1, B9, B11, C7,D5, E4, E11, F1,G10, J1, J12, L3,L5, L7, L9, N129, 18, 26, 35, 46, 54, 64,75, 83, 91, 100, 111, 120,129, 136, 144,1, 8, 14, 22, 29, 37, 45, 51,59, 69, 75, 83, 91, 98, 106,112, 119, 129, 135, 143,151, 158, 166, 172, 182,190, 196, 204, 211, 219,227, 233Table 2: Virtex Pinout Tables (Chip-Scale and QFP Packages) (Continued)Pin Name Device CS144TQ144PQ/HQ240Table 3: Virtex Pinout Tables (BGA)Pin Name Device BG256BG352BG432BG560 GCK0All Y11AE13AL16AL17 GCK1All Y10AF14AK16AJ17 GCK2All A10B14A16D17 GCK3All B10D14D17A17 M0All Y1AD24AH28AJ29 M1All U3AB23AH29AK30 M2All W2AC23AJ28AN32 CCLK All B19C3D4C4 PROGRAM All Y20AC4AH3AM1 DONE All W19AD3AH4AJ5 INIT All U18AD2AJ2AH5 BUSY/DOUT All D18E4D3D4 D0/DIN All C19D3C2E4 D1All E20G1K4K3 D2All G19J3K2L4 D3All J19M3P4P3 D4All M19R3V4W4 D5All P19U4AB1AB5 D6All T20V3AB3AC4 D7All V19AC3AG4AJ4 WRITE All A19D5B4D6 CS All B18C4D5A2 TDI All C17B3B3D5 TDO All A20D4C4E6 TMS All D3D23D29B33 TCK All A1C24D28E29 DXN All W3AD23AH27AK29 DXP All V4AE24AK29AJ28V CCINTNotes:•Superset includes all pins, including the ones in boldtype. Subset excludes pins in bold type.•In BG352, for XCV300 all the V CCINT pins in the supersetmust be connected. ForXCV150/200, V CCINT pins in the subset must beconnected, and pins in boldtype can be left unconnected (these unconnected pinscannot be used as user I/O.)•In BG432, forXCV400/600/800 all V CCINTpins in the superset must be connected. For XCV300,V CCINT pins in the subsetmust be connected, and pins in bold type can be leftunconnected (theseunconnected pins cannot be used as user I/O.)•In BG560, for XCV800/1000 all V CCINT pins in thesuperset must be connected.For XCV400/600, V CCINTpins in the subset must beconnected, and pins in boldtype can be left unconnected (these unconnected pinscannot be used as user I/O.)XCV50/100C10, D6,D15, F4,F17, L3,L18, R4,R17, U6,U15, V10N/A N/A N/AXCV150/200/300Same asaboveA20, C14,D10, J24,K4, P2, P25,V24, W2,AC10, AE14,AE19,B16, D12,L1, L25,R23, T1,AF11, AF16A10, A17, B23,C14, C19, K3,K29, N2, N29,T1, T29, W2,W31, AB2,AB30, AJ10,AJ16, AK13,AK19, AK22,B26, C7, F1,F30, AE29, AF1,AH8, AH24N/AXCV400/600/800/1000N/A N/A Same as above A21, B14, B18,B28, C24, E9,E12, F2, H30,J1, K32, N1,N33, U5, U30,Y2, Y31, AD2,AD32, AG3,AG31, AK8,AK11, AK17,AK20, AL14,AL27, AN25,B12, C22, M3,N29, AB2,AB32, AJ13,AL22V CCO, Bank 0All D7, D8A17, B25,D19A21, C29, D21A22, A26, A30,B19, B32V CCO, Bank 1All D13, D14A10, D7,D13A1, A11, D11A10, A16, B13,C3, E5V CCO, Bank 2All G17, H17B2, H4, K1C3, L1, L4B2, D1, H1, M1,R2V CCO, Bank 3All N17, P17P4, U1, Y4AA1, AA4, AJ3V1, AA2, AD1,AK1, AL2V CCO, Bank 4All U13, U14AC8, AE2,AF10AH11, AL1,AL11AM2, AM15,AN4, AN8, AN12V CCO, Bank 5All U7, U8AC14, AC20,AF17AH21, AJ29,AL21AL31, AM21,AN18, AN24,AN30V CCO, Bank 6All N4, P4U26, W23,AE25AA28, AA31,AL31W32, AB33,AF33, AK33,AM32Table 3: Virtex Pinout Tables (BGA) (Continued)Pin Name Device BG256BG352BG432BG560V CCO, Bank 7All G4, H4G23, K26,N23A31, L28, L31C32, D33, K33,N32, T33V REF, Bank 0(VREF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50A8, B4N/A N/A N/A XCV100/150... + A4A16,C19,C21N/A N/AXCV200/300... + A2... + D21B19, D22, D24,D26N/A XCV400N/A N/A... + C18A19, D20,D26, E23, E27 XCV600N/A N/A... + C24... + E24 XCV800N/A N/A... + B21... + E21 XCV1000N/A N/A N/A... + D29V REF, Bank 1(VREF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50A17, B12N/A N/A N/A XCV100/150... + B15B6, C9,C12N/A N/AXCV200/300... + B17... + D6A13, B7,C6, C10N/AXCV400N/A N/A... + B15A6, D7,D11, D16, E15 XCV600N/A N/A... + D10... + D10 XCV800N/A N/A... + B12... + D13 XCV1000N/A N/A N/A... + E7V REF, Bank 2(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50C20, J18N/A N/A N/A XCV100/150... + F19E2, H2,M4N/A N/AXCV200/300... + G18... + D2E2, G3,J2, N1N/AXCV400N/A N/A... + R3G5, H4,L5, P4, R1 XCV600N/A N/A... + H1... + K5 XCV800N/A N/A... + M3... + N5 XCV1000N/A N/A N/A... + B3Table 3: Virtex Pinout Tables (BGA) (Continued)Pin Name Device BG256BG352BG432BG560V REF, Bank 3(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50M18, V20N/A N/A N/AXCV100/150... + R19R4, V4, Y3N/A N/AXCV200/300... + P18... + AC2V2, AB4, AD4,AF3N/AXCV400N/A N/A... + U2V4, W5,AD3, AE5, AK2 XCV600N/A N/A... + AC3... + AF1 XCV800N/A N/A... + Y3... + AA4 XCV1000N/A N/A N/A... + AH4V REF, Bank 4(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50V12, Y18N/A N/A N/A XCV100/150... + W15AC12, AE5,AE8,N/A N/AXCV200/300... + V14... + AE4AJ7, AL4, AL8,AL13N/AXCV400N/A N/A... + AK15AL7, AL10,AL16, AM4,AM14 XCV600N/A N/A... + AK8... + AL9 XCV800N/A N/A... + AJ12... + AK13 XCV1000N/A N/A N/A... + AN3V REF, Bank 5(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50V9, Y3N/A N/A N/A XCV100/150... + W6AC15, AC18,AD20N/A N/AXCV200/300... + V7... + AE23AJ18, AJ25,AK23, AK27N/AXCV400N/A N/A... + AJ17AJ18, AJ25,AL20, AL24,AL29 XCV600N/A N/A... + AL24... + AM26 XCV800N/A N/A... + AH19... + AN23 XCV1000N/A N/A N/A... + AK28V REF, Bank 6(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50M2, R3N/A N/A N/AXCV100/150... + T1R24, Y26,AA25,N/A N/AXCV200/300... + T3... + AD26V28, AB28,AE30, AF28N/AXCV400N/A N/A... + U28V29, Y32, AD31,AE29, AK32 XCV600N/A N/A... + AC28... + AE31 XCV800N/A N/A... + Y30... + AA30 XCV1000N/A N/A N/A... + AH30Table 3: Virtex Pinout Tables (BGA) (Continued)Pin Name Device BG256BG352BG432BG560V REF , Bank 7(V REF pins are listedincrementally. Connect all pins listed for both the required device and allsmaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50G3, H1N/A N/A N/A XCV100/150... + D1D26, G26,L26N/AN/AXCV200/300... + B2... + E24F28, F31,J30, N30N/AXCV400N/A N/A ... + R31E31, G31, K31, P31, T31XCV600N/A N/A ... + J28... + H32XCV800N/A N/A ... + M28... + L33XCV1000N/A N/AN/A... + D31GNDAllC3, C18, D4, D5, D9, D10, D11, D12, D16, D17, E4, E17, J4, J17, K4, K17, L4, L17, M4, M17, T4, T17, U4, U5, U9, U10, U11, U12, U16, U17, V3, V18A1, A2, A5, A8, A14,A19, A22,A25, A26,B1, B26, E1,E26, H1,H26, N1,P26, W1,W26, AB1, AB26, AE1,AE26, AF1,AF2, AF5, AF8, AF13,AF19, AF22, AF25, AF26A2, A3, A7, A9,A14, A18, A23, A25, A29, A30, B1, B2, B30, B31, C1, C31, D16, G1, G31, J1, J31, P1, P31, T4, T28, V1, V31, AC1, AC31,AE1, AE31, AH16, AJ1, AJ31, AK1, AK2,AK30, AK31, AL2, AL3, AL7, AL9 AL14, AL18AL23, AL25, AL29, AL30A1, A7, A12, A14, A18, A20, A24, A29, A32, A33, B1, B6, B9, B15, B23, B27, B31, C2, E1, F32, G2, G33, J32, K1, L2, M33, P1, P33, R32, T1, V33, W2, Y1, Y33, AB1, AC32, AD33, AE2, AG1, AG32, AH2, AJ33, AL32, AM3, AM7, AM11, AM19, AM25, AM28, AM33, AN1, AN2, AN5, AN10, AN14, AN16, AN20, AN22, AN27,AN33GND (1)AllJ9, J10, J11, J12, K9, K10, K11, K12, L9, L10, L11, L12, M9, M10, M11, M12N/A N/AN/A No Connect All N/AN/A N/AC31, AC2, AK4,AL3Notes:1.16 extra balls (grounded) at package center.Table 3: Virtex Pinout Tables (BGA) (Continued)Pin NameDevice BG256BG352BG432BG560Table 4: Virtex Pinout Tables (Fine-Pitch BGA)Pin Name Device FG256FG456FG676FG680 GCK0All N8W12AA14AW19 GCK1All R8Y11AB13AU22 GCK2All C9A11C13D21 GCK3All B8C11E13A20 M0All N3AB2AD4AT37 M1All P2U5W7AU38 M2All R3Y4AB6AT35 CCLK All D15B22D24E4 PROGRAM All P15W20AA22AT5 DONE All R14Y19AB21AU5 INIT All N15V19Y21AU2 BUSY/DOUT All C15C21E23E3 D0/DIN All D14D20F22C2 D1All E16H22K24P4 D2All F15H20K22P3 D3All G16K20M22R1 D4All J16N22R24AD3 D5All M16R21U23AG2 D6All N16T22V24AH1 D7All N14Y21AB23AR4 WRITE All C13A20C22B4 CS All B13C19E21D5 TDI All A15B20D22B3 TDO All B14A21C23C4 TMS All D3D3F5E36 TCK All C4C4E6C36 DXN All R4Y5AB7AV37 DXP All P4V6Y8AU35V CCINT All C3, C14, D4,D13, E5,E12, M5,M12, N4,N13, P3,P14E5, E18, F6,F17, G7, G8, G9,G14, G15, G16,H7, H16, J7,J16, P7, P16,R7, R16, T7, T8,T9, T14, T15,T16, U6, U17,V5, V18G7, G20, H8, H19,J9, J10, J11, J16,J17, J18, K9, K18,L9, L18, T9, T18,U9, U18, V9, V10,V11, V16, V17,V18, W8, W19, Y7,Y20AD5, AD35,AE5, AE35, AL5,AL35, AM5,AM35, AR8,AR9, AR15,AR16, AR24,AR25, AR31,AR32, E8, E9,E15, E16, E24,E25, E31, E32,H5, H35, J5,J35, R5, R35,T5, T35V CCO, Bank 0All E8, F8F7, F8, F9, F10G10, G11H9, H10, H11,H12, J12, J13E26, E27, E29,E30, E33, E34V CCO, Bank 1All E9, F9F13, F14, F15,F16, G12, G13H15, H16, H17,H18, J14, J15E6, E7, E10,E11, E13, E14V CCO, Bank 2All H11, H12G17, H17, J17,K16, K17, L16J19, K19, L19,M18, M19, N18F5, G5, K5, L5,N5, P5V CCO, Bank 3All J11, J12M16, N16, N17,P17, R17, T17P18, R18, R19,T19, U19, V19AF5, AG5, AN5,AK5, AJ5, AP5V CCO, Bank 4All L9. M9T12, T13, U13,U14, U15, U16, V14, V15, W15,W16, W17, W18AR6, AR7,AR10, AR11,AR13, AR14V CCO, Bank 5All L8, M8T10, T11, U7,U8, U9, U10V12, V13,W9,W10, W11,W12AR26, AR27,AR29, AR30,AR33, AR34V CCO, Bank 6All J5, J6M7, N6, N7, P6,R6, T6P9, R8, R9, T8,U8, V8AF35, AG35,AJ35, AK35,AN35, AP35V CCO, Bank 7All H5, H6G6, H6, J6, K6,K7, L7J8, K8, L8, M8,M9, N9F35, G35, K35,L35, N35, P35V REF, Bank 0(VREF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50B4, B7N/A N/A N/AXCV100/150... + C6A9, C6, E8N/A N/AXCV200/300... + A3... + B4N/A N/AXCV400N/A N/A A12, C11, D6, E8,G10XCV600N/A N/A... + B7A33, B28, B30,C23, C24, D33 XCV800N/A N/A... + B10... + A26 XCV1000N/A N/A N/A... + D34V REF, Bank 1(VREF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50B9, C11N/A N/A N/A XCV100/150... + E11A18, B13, E14N/A N/A XCV200/300... + A14... + A19N/A N/A XCV400N/A N/A A14, C20, C21,D15, G16N/AXCV600N/A N/A... + B19B6, B8, B18,D11, D13, D17 XCV800N/A N/A... + A17... + B14 XCV1000N/A N/A N/A... + B5V REF, Bank 2(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50F13, H13N/A N/A N/AXCV100/150... + F14F21, H18, K21N/A N/AXCV200/300... + E13... + D22N/A N/AXCV400N/A N/A F24, H23, K20,M23, M26N/AXCV600N/A N/A... + G26G1, H4, J1, L2,V5, W3 XCV800N/A N/A... + K25... + N1 XCV1000N/A N/A N/A... + D2V REF, Bank 3(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50K16, L14N/A N/A N/AXCV100/150... + L13N21, R19, U21N/A N/AXCV200/300... + M13... + U20N/A N/AXCV400N/A N/A R23, R25, U21,W22, W23N/AXCV600N/A N/A... + W26AC1, AJ2, AK3,AL4, AR1, Y1 XCV800N/A N/A... + U25... + AF3 XCV1000N/A N/A N/A... + AP4V REF, Bank 4(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50P9, T12N/A N/A N/A XCV100/150... + T11AA13, AB16,AB19N/A N/A XCV200/300... + R13... + AB20N/A N/A XCV400N/A N/A AC15, AD18,AD21, AD22,AF15N/AXCV600N/A N/A... + AF20AT19, AU7,AU17, AV8,AV10, AW11 XCV800N/A N/A... + AF17... + AV14 XCV1000N/A N/A N/A... + AU6V REF, Bank 5(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50T4, P8N/A N/A N/A XCV100/150... + R5W8, Y10, AA5N/A N/A XCV200/300... + T2... + Y6N/A N/A XCV400N/A N/A AA10, AB8, AB12,AC7, AF12N/AXCV600N/A N/A... + AF8AT27, AU29,AU31, AV35,AW21, AW23 XCV800N/A N/A... + AE10... + AT25 XCV1000N/A N/A N/A... + AV36V REF, Bank 6(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50J3, N1N/A N/A N/A XCV100/150... + M1N2, R4, T3N/A N/A XCV200/300... + N2... + Y1N/A N/A XCV400N/A N/A AB3, R1, R4, U6,V5N/AXCV600N/A N/A... + Y1AB35, AD37,AH39, AK39,AM39, AN36 XCV800N/A N/A... + U2... + AE39 XCV1000N/A N/A N/A... + AT39V REF, Bank 7(V REF pins are listed incrementally. Connect all pins listed for both the required device and all smaller devices listed in the same package.)Within each bank, if input reference voltage is not required, all V REF pins are general I/O.XCV50C1, H3N/A N/A N/AXCV100/150... + D1E2, H4, K3N/A N/AXCV200/300... + B1... + D2N/A N/AXCV400N/A N/A F4, G4, K6, M2,M5N/AXCV600N/A N/A... + H1E38, G38, L36,N36, U36, U38 XCV800N/A N/A... + K1... + N38 XCV1000N/A N/A N/A... + F36GND All A1, A16, B2,B15, F6, F7,F10, F11,G6, G7, G8,G9, G10,G11, H7,H8, H9, H10,J7, J8, J9,J10, K6, K7,K8, K9, K10,K11, L6, L7,L10, L11,R2, R15, T1,T16A1, A22, B2,B21, C3, C20,J9, J10, J11,J12, J13, J14,K9, K10, K11,K12, K13, K14,L9, L10, L11,L12, L13, L14,M9, M10, M11,M12, M13, M14,N9, N10, N11,N12, N13, N14,P9, P10, P11,P12, P13, P14,Y3, Y20, AA2,AA21, AB1,AB22A1, A26, B2, B9,B14, B18, B25,C3, C24, D4, D23,E5, E22, J2, J25,K10, K11, K12,K13, K14, K15,K16, K17, L10,L11, L12, L13,L14, L15, L16,L17, M10, M11,M12, M13, M14,M15, M16, M17,N2, N10, N11,N12, N13, N14,N15, N16, N17,P10, P11, P12,P13, P14, P15,P16, P17, P25,R10, R11, R12,R13, R14, R15,R16, R17, T10,T11, T12, T13,T14, T15, T16,T17, U10, U11,U12, U13, U14,U15, U16, U17,V2, V25, AB5,AB22, AC4, AC23,AD3, AD24, AE2,AE9, AE13, AE18,AE25, AF1, AF26A1, A2, A3, A37,A38, A39, AA5,AA35, AH4,AH5, AH35,AH36, AR5,AR12, AR19,AR20, AR21,AR28, AR35,A T4, AT12, A T20,A T28, AT36,AU1, AU3, AU20,AU37, AU39,AV1, AV2, AV38,AV39, AW1,AW2, AW3,AW37, AW38,AW39, B1, B2,B38, B39, C1,C3, C20, C37,C39, D4, D12,D20, D28, D36,E5, E12, E19,E20, E21, E28,E35, M4, M5,M35, M36, W5,W35, Y3, Y4, Y5,Y35, Y36, Y37No Connect(No-connect pins are listed incrementally. All pins listed for both the required device and all larger devices listed in the same package are no connects.)XCV800N/A N/A A2, A3, A15, A25,B1, B6, B11, B16,B21, B24, B26,C1, C2, C25, C26,F2, F6, F21, F25,L2, L25, N25, P2,T2, T25, AA2,AA6, AA21, AA25,AD1, AD2, AD25,AE1, AE3, AE6,AE11, AE14,AE16, AE21,AE24, AE26, AF2,AF24, AF25N/AXCV600N/A N/A same as above N/A XCV400N/A N/A... + A9, A10, A13,A16, A24, AC1,AC25, AE12,AE15, AF3, AF10,AF11, AF13,AF14, AF16,AF18, AF23, B4,B12, B13, B15,B17, D1, D25,H26, J1, K26, L1,M1, M25, N1, N26,P1, P26, R2, R26,T1, T26, U26, V1N/AXCV300N/A D4, D19, W4,W19N/A N/AXCV200N/A... + A2, A6, A12,B11, B16, C2,D1, D18, E17,E19, G2, G22,L2, L19, M2,M21, R3, R20,U3, U18, Y22,AA1, AA3, AA11,AA16, AB7,AB12, AB21,N/A N/AXCV150N/A... + A13, A14,C8, C9, E13,F11, H21, J1, J4,K2, K18, K19,M17, N1, P1, P5,P22, R22, W13,W15, AA9,AA10, AB8,AB14N/A N/APinout DiagramsThe following diagrams, CS144 Pin Function Diagram ,page 17 through FG680 Pin Function Diagram , page 27,illustrate the locations of special-purpose pins on Virtex FPGAs. Table 5 lists the symbols used in these diagrams.The diagrams also show I/O-bank boundaries.CS144 Pin Function DiagramTable 5: Pinout Diagram Symbols Symbol Pin Function✳General I/O❄Device-dependent general I/O, n/c on smaller devices V V CCINTv Device-dependent V CCINT , n/c on smaller devices O V CCO R V REFr Device-dependent V REF , remains I/O on smaller devices G Ground Ø, 1, 2, 3Global Clocks❿, ❶, ❷M0, M1, M2➉, ➀, ➁,➂,➃, ➄, ➅, ➆D0/DIN, D1, D2, D3, D4, D5, D6, D7B DOUT/BUSY D DONE P PROGRAM I INIT K CCLK W WRITE S CST Boundary-scan Test Access Port +Temperature diode, anode –Temperature diode, cathode nNo connect Table 5: Pinout Diagram Symbols (Continued)Symbol Pin FunctionFigure 1: CS144 Pin Function Diagram123456791011121381ØCS144(Top view)23❶❿❷K P D I B ➉➀➁➂➃➄➅➆W S T ✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳G ✳✳✳✳✳✳12345679101112138A B C D E F GH J K L M NT ✳V ✳O ✳✳✳R ✳✳✳✳✳G ✳A B C D E F G H J K L M N✳✳✳✳T T V V V V V V V O O O O O O O O O O O R r R R r R R r R R r R R R R r R R r R R r G G G G G G G G G G G G G G r Bank 0Bank 1Bank 5Bank 3Bank 4Bank 6Bank 2Bank 7TQ144 Pin Function DiagramFigure 2: TQ144 Pin Function Diagram123456791011121314151617192021222324252627293031323334353681828373940414243444546474950515253545556575960616263646566384858676970717268737475767779808182838485868789909192939495967888979910098101102103104105106107108109110111112113114115116117119120121122123124125126127129130131132133134135136118128137139140141142143144138✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳1Ø✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳✳TQ144(Top view)23❶❿❷K PD I B ➉➀➁➂➃➄➅➆W S T TT T V V V V V V V V O O O O OOO O R r R R R R R R R R R R R R R R R G G G G G G G G G G G G G G G G r r r r r r r Bank 0Bank 7Bank 6Bank 5Bank 1Bank 4Bank 2Bank 3。

Xilinx FPGA 引脚功能详细介绍.pptx

TCK:I,JTAG 边界扫描时钟。 TDI :I,JTAG 边界扫描数据输入。 TDO:O,JTAG 边界扫描数据输出。 TMS:I,JTAG 边界扫描模式选择 5.保留引脚 NC:N/A, CMPCS_B_2:I,保留,不接或者连 VCCO_2 6.其它 GND: VBATT:RAM内存备份电源。一旦 VCCAUX 应用了,VBATT可以不接;如果 KEY RAM 没有使用,推荐把VBATT 接到 VCCAUX 或者 GND,也可以不接。 VCCAUX:辅助电路电源引脚 VCCINT:内部核心逻辑电源引脚 VCCO_#:输出驱动电源引脚 VFS:I,(LX45 不可用)编程时,key EFUSE 电源供电引脚。当不编程时,这个引脚 的电压应该限制在 GND 到 3.45V;当不使用 key EFUSE 时,推荐把该引脚连接到 VCCAUX 或者 GND,悬空也可以。 RFUSE:I,(LX45 不可用)编程时,key EFUSE 接地引脚。当不编程时或者不使用 key

VREF_#:N/A,这些是输入临界电压引脚。当外部涯

普通引脚。当做作bank 内参考电压时,所有的VRef 都必须被接上。 3.多功能内存控制引脚

M#DQn:I/O,bank# 内 存 控 制 数 据 线 D[15:0] M#LDQS:I/O,bank#内存控制器低数据选通脚 M#LDQSN:I/O,bank#中内存控制器低数据选通 N M#UDQS:I/O,bank#内存控制器高数据选通脚 M#UDQSN:I/O,bank#内存控制器高数据选通 N M#An :O,bank# 内 存 控 制 器 地 址 线 A[14:0] M#BAn:O,bank# 内 存 控 制 bank 地 址 BA[2:0] M#LDM:O,bank#内存控制器低位掩码 M#UDM:O, bank#内存控制器高位掩码 M#CLK:O,bank#内存控制 器时钟 M#CLKN:O,bank#内存控制器时钟,低电平 有效 M#CASN:O,bank#内存控制器低电平有效行地址 选通 M#RASN:O,bank#内存控制器低电平有效列地址 选通 M#ODT:O,bank#内存控制器外部内存的终端信 号控制 M#WE:O,bank#内存控制器写使能 M#CKE: O,bank#内存控制器时钟使能 M#RESET:O,bank#内 存控制器复位

Altera FPGA和 Xilinx-FPGA-引脚功能详解

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

FPGA的配置引脚说明

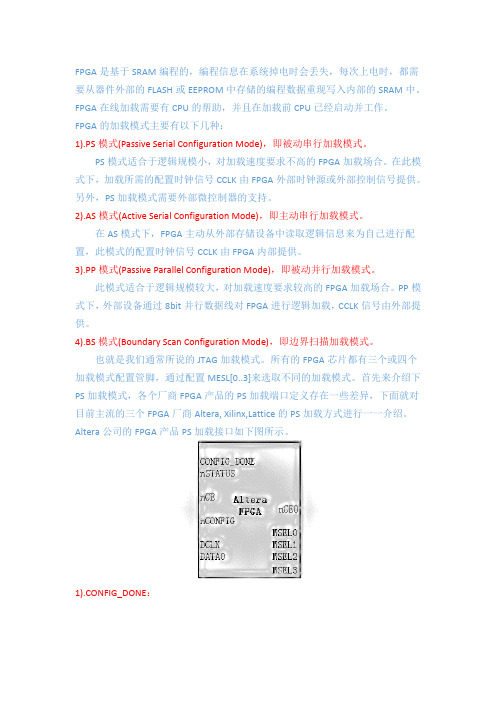

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。

FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。

FPGA的加载模式主要有以下几种:1).PS模式(Passive Serial Configuration Mode),即被动串行加载模式。

PS模式适合于逻辑规模小,对加载速度要求不高的FPGA加载场合。

在此模式下,加载所需的配置时钟信号CCLK由FPGA外部时钟源或外部控制信号提供。

另外,PS加载模式需要外部微控制器的支持。

2).AS模式(Active Serial Configuration Mode),即主动串行加载模式。

在AS模式下,FPGA主动从外部存储设备中读取逻辑信息来为自己进行配置,此模式的配置时钟信号CCLK由FPGA内部提供。

3).PP模式(Passive Parallel Configuration Mode),即被动并行加载模式。

此模式适合于逻辑规模较大,对加载速度要求较高的FPGA加载场合。

PP模式下,外部设备通过8bit并行数据线对FPGA进行逻辑加载,CCLK信号由外部提供。

4).BS模式(Boundary Scan Configuration Mode),即边界扫描加载模式。

也就是我们通常所说的JTAG加载模式。

所有的FPGA芯片都有三个或四个加载模式配置管脚,通过配置MESL[0..3]来选取不同的加载模式。

首先来介绍下PS加载模式,各个厂商FPGA产品的PS加载端口定义存在一些差异,下面就对目前主流的三个FPGA厂商Altera, Xilinx,Lattice的PS加载方式进行一一介绍。

Altera公司的FPGA产品PS加载接口如下图所示。

1).CONFIG_DONE:加载完成指示输出信号,I/O接口,高有效,实际使用中通过电阻上拉到VCC,使其默认状态为高电平,表示芯片已加载完毕,当FPGA正在加载时,会将其驱动为低电平。

xilinxfpga管脚类型

xilinxfpga管脚类型

xilinx fpga 管脚类型

xilinx fpga 管脚类型

XilinxFPGA是一种可编程逻辑设备,它的管脚类型包括以下几种:

1.输入型(Input):用于向FPGA中输入数据或控制信息。

2.输出型(Output):用于从FPGA中输出数据或控制信息。

3.双向型(Bidirectional):用于同时进行输入和输出操作。

4.三态型(TriState):具有三态输出能力,可以将输出置为高阻态(High-Z)。

5.时钟型(Clock):用于提供时钟信号,通常用于同步输入和输出数据。

6.电源与接地型(Power and Ground):用于连接到电源和地线,提供电源和接地功能。

FPGA管脚类型的选择取决于具体的应用需求。

在设计过程中,需要根据信号类型、频率和电压等因素选择合适的管脚类型。

同时,还需要考虑管脚的数量和布局,以便满足整个系统的电路连接需求。

- 1 -。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_#用户IO引脚XX代表某个Bank内唯一得一对引脚,Y=[P|N]代表对上升沿还就是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO得基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0就是数据得最低位,在Bit—serial模式下,DIN就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1就是SPI总线得第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1与D2就是数据总线得低位;在SPI*4模式下,MISO2与MISO3就是SPI总线得MSBs.An:O,A[25:0]为BPI模式得地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式得状态输出引脚。

SUSPEND就是一个专用引脚,AW A KE就是一个多功能引脚。

除非SUSPEND模式被使能,AW AKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B就是一个低电平有效得片选信号;在SPI*2或者SPI*4得模式下,MISO0就是SPI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FOE_B:O,BPI flash得输出使能信号FWE_B:O,BPIflash 得写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AW AKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Get格雅XilinxFPGA引脚功能详细介绍

Xilinx-FPGA-引脚功能详细介绍XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的根本上添加一个或多个以下功能。

Dn:I/O〔在readback期间〕,在selectMAP 或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反应期间,如果RDWR_B=1,那么这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式〔SelectMAP/BPI〕下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

(完整word版)XilinxFPGA引脚功能详细介绍

Xilinx FPGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户10引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2. IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户10的基本上添加一个或多个以下功能。

Dn:I/O (在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

DO_DIN_MISO_MISO1 : I,在并口模式(SelectMAP/BPI )下,D0 是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3 : I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An : O, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE : O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0 : I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOO是SPI总线的第一位数据。

FCS_B: O, BPI flash 的片选信号。

FOE_B : O, BPI flash的输出使能信号FWE_B : O, BPI flash的写使用信号LDC : O,BPI模式配置期间为低电平HDC : O,BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

XilinxFPGA引脚功能详细介绍.docx

XilinX FPGA 引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P∣N]代表对上升沿还是下降沿敏感,#代表bank 号2. IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O (在readback期间),在SeleCtMAP或者BPI模式下,D[15:0]配置为数据口。

在从SeIeCtMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1 : I ,在并口模式(SeIeCtMAP/BPI )下,D0 是数据的最低位,在Bit-SeriaI模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3 : I ,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBS。

An : O, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE : O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0 : I/O ,在SPI模式下,主输出或者从输入;在SeIeCtMAP模式下,CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOo是SPI总线的第一位数据。

FCS_B: O, BPI flash 的片选信号。

FOE_B : O, BPI flash的输出使能信号FWE_B : O, BPI flash的写使用信号LDC : O,BPI模式配置期间为低电平HDC : O,BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

ilin fpga 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

在SPI模式下,为SPI flsah片选信号。

IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。

DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT提供配置数据流。

RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。

HSWAPEN:I,在配置之后和配置过程中,低电平使用上拉。

INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC状态。

SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。

CMPMOSI,CMPMISO,CMPCLK:N/A,保留。

M0,M1:I,配置模式选择。

M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。

CCLK:I/O,配置时钟,主模式下输出,从模式下输入。

USERCCLK:I,主模式下,可行用户配置时钟。

GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。

VREF_#:N/A,这些是输入临界电压引脚。

当外部的临界电压不必要时,他可以作为普通引脚。

当做作bank内参考电压时,所有的VRef都必须被接上。

3.多功能内存控制引脚M#DQn:I/O,bank#内存控制数据线D[15:0]M#LDQS:I/O,bank#内存控制器低数据选通脚M#LDQSN:I/O,bank#中内存控制器低数据选通NM#UDQS:I/O,bank#内存控制器高数据选通脚M#UDQSN:I/O,bank#内存控制器高数据选通NM#An:O,bank#内存控制器地址线A[14:0]M#BAn:O,bank#内存控制bank地址BA[2:0]M#LDM:O,bank#内存控制器低位掩码M#UDM:O,bank#内存控制器高位掩码M#CLK:O,bank#内存控制器时钟M#CLKN:O,bank#内存控制器时钟,低电平有效M#CASN:O,bank#内存控制器低电平有效行地址选通M#RASN:O,bank#内存控制器低电平有效列地址选通M#ODT:O,bank#内存控制器外部内存的终端信号控制M#WE:O,bank#内存控制器写使能M#CKE:O,bank#内存控制器时钟使能M#RESET:O,bank#内存控制器复位4.专用引脚DONE_2:I/O,DONE是一个可选的带有内部上拉电阻的双向信号。

作为输出,这个引脚说明配置过程已经完成;作为输入,配置为低电平可以延迟启动。

PROGRAM_B_2:I,低电平异步复位逻辑。

这个引脚有一个默认的弱上拉电阻。

SUSPEND:I,电源保护挂起模式的高电平有效控制输入引脚。

SUSPEND是一个专用引脚,而AWAKE是一个复用引用。

必须通过配置选项使能。

如果挂起模式没有使用,这个引脚接地。

TCK:I,JTAG边界扫描时钟。

TDI:I,JTAG边界扫描数据输入。

TDO:O,JTAG边界扫描数据输出。

TMS:I,JTAG边界扫描模式选择5.保留引脚NC:N/A,CMPCS_B_2:I,保留,不接或者连VCCO_26.其它GND:VBATT:RAM内存备份电源。

一旦VCCAUX应用了,VBATT可以不接;如果KEY RAM没有使用,推荐把VBATT接到VCCAUX或者GND,也可以不接。

VCCAUX:辅助电路电源引脚VCCINT:内部核心逻辑电源引脚VCCO_#:输出驱动电源引脚VFS:I,(LX45不可用)编程时,key EFUSE电源供电引脚。

当不编程时,这个引脚的电压应该限制在GND到;当不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,悬空也可以。

RFUSE:I,(LX45不可用)编程时,key EFUSE接地引脚。

当不编程时或者不使用key EFUSE 时,推荐把该引脚连接到VCCAUX或者GND,然而,也可以悬空。

引脚MGTAVCC:收发器混合信号电路电源引脚MGTAVTTTX,MGTAVTTRX:发送,接收电路电源引脚MGTAVTTRCAL:电阻校正电路电源引脚MGTAVCCPLL0,MGTAVCCPLL1:锁相环电源引脚MGTREFCLK0/1P,MGTREFCLK0/1N:差分时钟正负引脚MGTRREF:内部校准终端的精密参考电阻引脚MGTRXP[1:0],MGTRXN[1:0]:差分接收端口MGTTXP[1:0],MGTTXN[1:0]:差分发送端口1. Spartan-6系列封装概述Spartan-6系列具有低成本、省空间的封装形式,能使用户引脚密度最大化。

所有Spartan-6 LX器件之间的引脚分配是兼容的,所有Spartan-6 LXT器件之间的引脚分配是兼容的,但是Spartan-6 LX和Spartan-6 LXT器件之间的引脚分配是不兼容的。

表格 1Spartan-6系列FPGA封装2. Spartan-6系列引脚分配及功能详述Spartan-6系列有自己的专用引脚,这些引脚是不能作为Select IO使用的,这些专用引脚包括:专用配置引脚,表格2所示 GTP高速串行收发器引脚,表格3所示表格 2Spartan-6 FPGA专用配置引脚注意:只有LX75, LX75T, LX100, LX100T, LX150, and LX150T器件才有VFS、VBATT、RFUSE引脚。

表格 3Spartan-6器件GTP通道数目注意:LX75T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676中封装了8个GTP通道;LX100T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676 和 FG(G)900中封装了8个GTP通道。

如表4,每一种型号、每一种封装的器件的可用IO引脚数目不尽相同,例如对于LX4 TQG144器件,它总共有引脚144个,其中可作为单端IO引脚使用的IO个数为102个,这102个单端引脚可作为51对差分IO使用,另外的32个引脚为电源或特殊功能如配置引脚。

表格 4Spartan6系列各型号封装可用的IO资源汇总表格 5引脚功能详述引脚名方向描述User I/O PinsIO_LXXY_#Input/OutputIO表示这是一个具有输入输出功能的引脚,XX表示该引脚在其Bank内的惟一标识,Y表示是差分引脚的P还是N引脚3. Spartan-6系列GTP Transceiver引脚v1.0 可编辑可修改MGTREFCLK0/1P Input正极参考时钟MGTREFCLK0/1N Input负极参考时钟MGTRREF Input内部校准电路的精密参考电阻MGTRXP[0:1]Input收发器接收端正极MGTRXN[0:1]Input收发器接收端负极MGTTXP[0:1]Output收发器发送端正极MGTTXN[0:1]Output收发器发送端负极如表6所示,对LX25T,LX45T而言,只有一个GTP Transceiver通道,它的位置是X0Y0,所再Bank号为101;其他信号GTP Transceiver的解释类似。

表格 6GTP Transceiver所在Bank编号关于XILINX FPGA中VRP/VRN管脚的使用XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚。

VRP/VRN管脚是一对多功能管脚,当一个BANK使用到某些DCI(Digitally Controlled Impedance)接口电平标准时,需要通过该BANK的VRP/VRN管脚接入参考电阻。

此时,VRN通过一个参考电阻R上拉到Vcco,VRP通过一个参考电阻R下拉到地。

VRP/VRN管脚提供一个参考电压供DCI内部电路使用,DCI内部电路依据此参考电压调整IO输出阻抗与外部参考电阻R匹配。

当使用到DCI级联时,仅主BANK(master)需要通过VRP/VRN提供参考电压,从BANK(slave)不需要使用VRP/VRN,从BANK的VRP/VRN管脚可当成普通管脚使用。

当VRP/VRN不用于DCI 功能时,可用于普通管脚。

不需要VRP/VRN外接参考电阻的DCI输出接口电平标准有:HSTL_I_DCIHSTL_III_DCIHSTL_I_DCI_18HSTL_III_DCI_18SSTL2_I_DCISSTL18_I_DCISSTL15_DCI不需要VRP/VRN外接参考电阻的DCI输入接口电平标准有:LVDCI_15LVDCI_18LVDCI_25LVDCI_DV2_15LVDCI_DV2_18LVDCI_DV2_25。