AMBA APB4 与 AMBA3 AHB-Lite 1.0 协议介绍

AMBA APB4 与 AMBA3 AHB

AMBA APB4 与AMBA3 AHB而我们检查, 即使是 transfer with no wait state, 也最少消耗了 3 cycles. 这里我们理解, 在图例1中, T3 状态下, finish 本次transfer后, 假如要延续操作下一个写传递的过程, 那么则在 T3 状态下保持 PSEL asserted, 协作 PREADY unasserted, 恰好又进入了如T1 cycle 相同的 setup state, 这时需要 bridge 更新地址 PWRITE, 以及数据 PWDATA. 也就是在延续 transfer(针对同一个 slave)的操作中, transfer 最少只消耗 2 cycle.我们没有在 APB 协议中, 获得上述猜想的详解, 我们保留上述对 "2 cycles" 的理解猜想于此.总结我们通过对 APB protocol 的理解, 得知 APB 是 unpipeline 的 bus.无论如何, setup state 将占领一个 cycle, 而 access state 将占领另一个. 这种 unpipeline 的设计, 很可能就是 APB 被作为衔接外围的, 而不是用于 processor 之间的 memory 衔接的 BUS 的重要缘由. 因其不要求外围在一个 cycle 中对 address 举行取样, 这也给外围更多的时光反应, 起码比较而言, 用法 APB 的外围可以具备更小的bandwidth.[AMBA AHB-Lite]AHB-LiteAHB: Advanced High-performance Bus用于高表现力高clock频率的系统. 最常常的用法是衔接 internal memeory device, external memory interface, 以及 high bandwidth 外围. 其基本组元是: Master, Slave, Decoder, Multiplexor.在 address/control phase 与 data phase 中, 存在 fixed pipeline.AHB: 仅仅支持 AMBA AXI protocol 的功能子集(subset).AHB-Lite: 假如除去在 master 与 slave IP 开发中不需要的部分, 则 AHB protocol 的这个 subset 则定义为 AHB-Lite.Operation每一个 trasfer 都包括 Address phase 与 Data Phase.Address 不允许被 extend, 即便是来自 Slave 的哀求, 因此我们可以想象, 所有的 Slaves 都必需在 Address phase(1 cycle) 完成sampling address.但是与 APB 一样, Slave 也可以通过 HREADY signal 哀求 extend data phase, 增强额外的时光去 sample data.HRESP signal 被用来解释 transfer 的胜利与否.Address 总是可以在一个 single HCLK cycle 中完成, 除非是之前的bus transfer 被 extend(我们理解, 这里应当是惟独 data 才干做这个 extend).Data 可以占有数个 HCLK cycle, 这取决于 HREADY signal 是否extend transfer.因此, Address phase 可以与 Data phase 的 overlapping, 就是pipeline 的基础.[图例4: 在不同地址上的3个transfer的例子]。

AMBA_3_APB协议规范

AMBA_3_APB协议规范AMBA(高级微处理器总线)是一种用于系统级互连的开放标准协议,它由ARM公司开发,被广泛应用于嵌入式系统中。

AMBA_3_APB(高级微处理器总线第3代-高性能总线)是AMBA协议的一部分,它定义了一种高性能、低功耗的片内总线协议,用于连接处理器和外设。

1.信号:AMBA_3_APB协议规范定义了一系列信号,包括时钟信号、复位信号、总线控制信号、数据传输信号等。

时钟信号主要包括时钟线以及时钟使能信号,用于控制数据传输的时序。

复位信号用于重置外设以及总线控制器的状态。

总线控制信号用于控制总线的访问权限以及传输模式等。

数据传输信号用于在总线上传输数据。

2.传输:AMBA_3_APB协议规范定义了四种传输类型,分别是单个传输、设置传输、清除传输以及数据传输。

单个传输用于传输单个数据项,例如读取外设的寄存器值。

设置传输用于设置外设的寄存器值,例如写入配置信息。

清除传输用于清除外设的寄存器值,例如重置外设。

数据传输用于传输大量数据,例如读取或写入外设的缓冲区。

3.协议:AMBA_3_APB协议规范定义了一套协议,包括方法、地址空间、读写传输、保持传输、错误传输以及确认传输。

方法用于指示执行的操作类型,包括读、写等。

地址空间用于指定外设的寄存器地址。

读写传输用于实现读取或写入寄存器的操作。

保持传输用于在外设的寄存器繁忙时保持总线传输。

错误传输用于指示总线传输过程中的错误信息。

确认传输用于确认总线传输的完成。

4.时序:AMBA_3_APB协议规范定义了一套时序要求,包括时钟周期、数据有效性以及总线传输的顺序。

时钟周期用于控制数据传输的时序,包括时钟上升沿和下降沿的作用周期。

数据有效性用于指示数据在总线上的有效时间段,以及数据的采样时间。

总线传输的顺序用于指示多个传输之间的先后顺序,以及传输的优先级。

总结起来,AMBA_3_APB协议规范是一种用于连接处理器和外设的高性能、低功耗的片内总线协议。

AMBA_3_APB协议规范

AMBA 3 APB 协议规范关于该规范该规范使用于AMBA 3 APB 协议,引用自AMBA 3 (不适用AMBA 2 或更早版本)使用范围该规范用来帮助硬件或软件工程师设计使用APB协议的系统或模块使用该规范该规范按照以下章节进行组织:Chapter 1 简介Chapter 2 传输Chapter 3 操作状态Chapter 4 信号描述目录第一章简介 (2)1.1 关于AMBA 3 APB (2)1.2 AMBA 3 APB 协议规范v1.0修改 (2)第二章传输 (3)2.1 写传输 (3)2.1.1 无等待状态 (3)2.1.2 有等待状态 (3)2.2 读传输 (4)2.2.1 无等待状态 (4)2.2.2 有等待状态 (4)2.3 错误响应 (5)2.3.1 写传输 (5)2.3.2 写传输 (6)2.3.3 PSLVERR映射 (6)第三章操作状态 (7)3.1 操作状态 (7)第四章信号描述 (8)4.1 AMBA 3 APB 信号 (8)1.1 关于AMBA 3 APBAPB属于AMBA 3 协议系列,它提供了一个低功耗的接口,并降低了接口的复杂性。

APB接口用在低带宽和不需要高性能总线的外围设备上。

APB是非流水线结构,所有的信号仅与时钟上升沿相关,这样就可以简化APB 外围设备的设计流程,每个传输至少耗用两个周期。

APB可以与AMBA高级高性能总线(AHB-Lite) 和AMBA 高级可扩展接口(AXI)连接。

1.2 AMBA 3 APB 协议规范v1.0修改该版本包括:• 一个准备好信号PREADY, 来扩展APB传输• 一个错误信号PSLVERR, 来指示传输失败2.1 写传输写传输包括两种类型:• 无等待状态• 有等待状态2.1.1 无等待状态图2-1 显示了一个基本的无等待状态的写传输。

图2-1 无等待的写传输地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。

amba发展历史

AMBA发展历史

AMBA(Advanced Microcontroller Bus Architecture)是一种用于在微控制器和其他系统中实现高性能、低功耗互连的总线架构。

下面是AMBA的发展历史:

1. AMBA 1.0:于1995年发布,包括ASB(Advanced System Bus)和APB(Advanced Peripheral Bus)两种总线协议。

ASB提供高速数据传输和低功耗,而APB则提供简单的单周期访问。

2. AMBA 2.0:于2001年发布,引入了AHB(Advanced High-performance Bus)协议,用于高速数据传输。

AHB提供了更好的带宽和更低的延迟,适用于需要快速响应的应用场景。

3. AMBA 3.0:于2007年发布,引入了AXI(Advanced eXtensible Interface)协议,用于高级可扩展性和灵活性。

AXI 支持各种不同的数据传输大小和地址映射方式,适用于不同的应用场景。

4. AMBA 4.0:于2013年发布,进一步增强了AMBA的性能和可扩展性。

AMBA 4.0引入了AHB3和AXI4协议,支持更高的带宽和更低的延迟,并提供更灵活的协议配置选项。

总的来说,AMBA的发展历程是从简单的ASB和APB

协议到更复杂的AHB和AXI协议,不断地提高性能和可扩展性,以适应不断发展的应用需求。

AMBA、AHB、APB总线简介

AMBA、AHB、APB总线简介AMBA简介随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。

数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。

在基于IP复用的SoC设计中,片上总线设计是最关键的问题。

为此,业界出现了很多片上总线标准。

其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

AMBA片上总线AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。

AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。

AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

下面将简要介绍比较重要的AHB和APB总线。

基于AMBA的片上系统一个典型的基于AMBA总线的系统框图如图3所示。

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。

主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。

另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL 设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。

AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。

AMBA AHB APB 概述

AHB Decoder

• AHB系统中有一个核心地址译码器,它提供HSELx信号到各 个AHB Slave; • Decoder本身只负责位地址译码,为纯组合逻辑电路; • Slave只有在HSELx和HREADY都为High才采样地址/控制信号; • AHB地址线有32条,为简化译码器译码时间,AHB Spec.规 定每个Slave的最小地址空间为1KB,因此译码器最多只需 要对22条地址线进行译码。

HWRITE & HSIZE[2:0]

• Transfer Direction、Transfer Size由Master发出: – HWRITE为HIGH,Master在data phase将数据通过write data bus(HWDATA[31:0])发往Slave – HWRITE为LOW,Slave在data phase将数据通过read data bus (HRDATA[31:0])发往Master

允许某个主设备控制总线 发起一个请求给仲 裁器

驱动地址和控 制信号

仅选中的从设备响应地 址/控制信号

拉高HREADY信号,总线 传输完成

AHB Transfer

• Basic transfer – Address phase

• 传输address和control signal

– Data phase

• 传输write/read data和response signal

• 传输在data phase时若一个clock cycle无法完成传 输,Slave可通过拉低HREADY信号延长传输,传输 结束时状态由Slave HRESP信号反映。

Master sample the data

Master release address and control

AMBA_AHB_APB_AXI协议对比分析..

9

HREADY:S应答M是否读写操作传输完成: 1-传输完 成, 0-需延长传输周期。需要注意的是,HREADY 做 为总线上的信号,它是M和S 的输入;同时每个S 需 要输出自己的HREADY。所以对于S 会有两个 HREADY 信号,一个来自总线的输入,一个自己给到 多路器的输出。 HRESP:S应答当前传输状态,OKAY、ERROR、 RETRY、SPLIT HRDATA:读数据总线,从S读到M

3

一个典型的基于AMBA 总线的SOC 系统架构

这种SOC架构以AHB为主干,挂上CPU,片上内 存,和其它DMA设备。

4

AHB 主要是针对高效率、高频宽及快速系统模块所设 计的总线,它可以连接如微处理器、芯片上或芯片外 的内存模块和DMA等高效率模块 AMBA 中的APB 主要用在低速且低功率的外围,可 针对外围设备作功率消耗及复杂接口的最佳化 APB在AHB和低带宽的外围设备之间提供了通信的桥 梁,所以APB是AHB或者ASB的二级扩展总线

19

APB/AHB/AXI对比

APB 低功耗 AHB 高速度 AXI 高速度,高带宽 管道化互联 单向通道 只需首地址 读写并行 支持乱序 支持非对齐操作 有效支持初始延迟 较高的外设

20

连线非常多

AHB总线互连

7

允许某个主设备控制总线 发起一个请求给仲 裁器

驱动地址和控 制信号

仅选中的从设备响应地 址/控制信号

拉高HREADY信号,总线 传输完成

8

AHB基本信号

HADDR:32位系统地址总线 HTRANS: M指示传输状态,NONSEQ、SEQ、IDLE、 BUSY HWRITE:传输方向:1-写,0-读 HSIZE:传输单位 HBURST:传输的burst类型 HWDATA:写数据总线,从M写到S

AMBAAPB协议规范

AMBA 3 APB 协议规范关于该规范该规范使用于AMBA 3 APB 协议,引用自AMBA 3 (不适用AMBA 2 或更早版本)使用范围该规范用来帮助硬件或软件工程师设计使用APB协议的系统或模块使用该规范该规范按照以下章节进行组织:Chapter 1 简介Chapter 2 传输Chapter 3 操作状态Chapter 4 信号描述目录第一章简介 (2)1.1 关于AMBA 3 APB (2)1.2 AMBA 3 APB 协议规范v1.0修改 (2)第二章传输 (3)2.1 写传输 (3)2.1.1 无等待状态 (3)2.1.2 有等待状态 (3)2.2 读传输 (4)2.2.1 无等待状态 (4)2.2.2 有等待状态 (4)2.3 错误响应 (5)2.3.1 写传输 (5)2.3.2 写传输 (6)2.3.3 PSLVERR映射 (6)第三章操作状态 (7)3.1 操作状态 (7)第四章信号描述 (8)4.1 AMBA 3 APB 信号 (8)1.1 关于AMBA 3 APBAPB属于AMBA 3 协议系列,它提供了一个低功耗的接口,并降低了接口的复杂性。

APB接口用在低带宽和不需要高性能总线的外围设备上。

APB是非流水线结构,所有的信号仅与时钟上升沿相关,这样就可以简化APB 外围设备的设计流程,每个传输至少耗用两个周期。

APB可以与AMBA高级高性能总线(AHB-Lite) 和AMBA 高级可扩展接口(AXI)连接。

1.2 AMBA 3 APB 协议规范v1.0修改该版本包括:• 一个准备好信号PREADY, 来扩展APB传输• 一个错误信号PSLVERR, 来指示传输失败2.1 写传输写传输包括两种类型:• 无等待状态• 有等待状态2.1.1 无等待状态图2-1 显示了一个基本的无等待状态的写传输。

图2-1 无等待的写传输地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。

amba手册

amba手册

AMBA(Advanced Microcontroller Bus Architecture)是一种高级微控制器总线架构,它定义了高性能嵌入式微控制器的通信标准。

以下是AMBA手册的主要内容:

一、AMBA概述

AMBA是一种总线架构,用于连接和通信各种IP核和外设。

它不是芯片与外设之间的接口,而是ARM内核与芯片上其他元件进行通信的接口。

AMBA包括多种总线类型,如AHB、ASB、APB和AXI等,这些总线类型提供了不同的性能和功能。

二、AMBA的应用

AMBA被广泛应用于各类芯片和集成电路中,包括微控制器、数字信号处理器(DSP)以及通信和消费电子等多种应用。

它为这些应用提供了优秀的性能表现。

三、AMBA的版本历史

AMBA协议手册介绍了AMBA版本的历史,从最初的AMBA 到现在的AMBA ,每一版都进行了改进和扩展,以适应不断发展的微控制器和集成电路技术。

四、AMBA的总线类型

AMBA手册详细介绍了各种总线类型,包括AHB、ASB、APB和AXI等。

每种总线类型都有其特点和适用范围,可以根据实际需求选择适合的总线类型。

五、AMBA的IP核和外设

AMBA手册还介绍了各种IP核和外设,这些是构成微控制器和集成电路的基本元件。

手册中详细描述了每个IP核和外设的特点和功能,以及如何使用它们来实现高性能的嵌入式系统。

总的来说,AMBA手册是一本非常全面的参考资料,它详细介绍了AMBA 的各个方面,包括概述、应用、版本历史、总线类型、IP核和外设等。

对于从事嵌入式系统设计和开发的人员来说,这是一本非常有价值的参考资料。

AMBA APB4 与 AMBA3 AHB-Lite 1.0 协议介绍

AMBA APB4 与 AMBA3 AHB-Lite 1.0 协议介绍2013年09月18日 16:09 绝对好文关键词:AMBA , APB4 , AHB-Lite作者:Allen Zhan[介绍]根据ARM的说法, 今天 AMBA 已经成为了业界事实上的总线标准. 本文我们简单对AMBA4 中的 APB v2.0(也称为 APB4), 以及 AMBA3 AHB-Lite v1.0 进行简单的了解. 我们的介绍集中在, 我们比较有兴趣的地方. 尽管如此, 也可能几乎覆盖了协议中几个最重要的部分.[AMBA APB]AMBAAdvanced Microcontroller Bus Architecture, 由ARM定义的总线架构(标准), 由一个协议家族组成. ARM 声称这一标准已经称为事实上的 uController 业界通用标准.APBThe Advanced Peripheral Bus(APB) 是 AMBA 协议家族中一个组成部分.它被定义为一个 low-cost 的接口, 为了最小能耗与减小接口的复杂性进行的优化设计.被用于连接通用外围, 比如 timers, inerrupt controllers, UART是, and IOs. 通过 system-to-peripheral bus bridge 与 main system bus 相连, 有助于降低能耗.APB 版本当前(2013年9月), 最近的 APB协议版本是 AMBA APB Protocol Specification v2.0. 或者因为属于 AMBA4 家族中的发布协议, 一般也被称为 APB4.而在第一个版本(APB2 )中, APB 的基本组元, APB bridge 与 APB slave 被定义.而在 APB3 中, Ready signal 被引入, 这意味着增加了操作状态中, 增加了wait state. 另外增加了 PSLVERR, 用于错误报告的 signal.最近的 APB4, 增加了 PPROT 与 PSTRB signal.APB bridge 与 APB slave我们可以挂载各种"慢速"的外设在 APB 上, 比如 IO, 比如 UART, 比如 SPI, etc. 它们都作为 slave 的角色存在.但是, 我们想想看, bridge 这个 role 就蛮有意思. 它实际上暗示我们, APB 不能"单独存在". 我们这里所谓不能"单独存在"的意思, 是说 APB 一定不能直接连接在 processor 上(或者说 arm core上). 而最可能的, 是通过 APB bridge 而连接在高速的 bus 上.实际上, 在 AHB-Lite 协议中, 我们发现 APB bridge 被作为 AHB-Lite 的slave 而被定义.Data busesAPB 协议有两个独立的 data bus, 一个用来读 data, 一个用来写 data.因为没有独立的握手信号, 所以在两根bus上, 同一时刻数据传输不能同时发生.Write Transfers我们简单对 APB 的 trasfers 过程进行分析, 比如我们分析 write transfer with no wait states:[图例1: Write transfer with no wait states]T0: Idle stateT1: Setup statewrite address PADDR, write data PWDATAsetup state 仅仅只保持 1pcs clock cycle, 而在下一个 PCLK 的上升沿, 一定进入 Access state.T2: Access stateAPB bridge 通过拉高 PENABLE, 通知slave 第二阶段(也就是 access phase)开始.因为是 no wait states, 我们见到了 PREADY 在此被拉高, 表示 slave 通知bridge, 在下一个 PCLK 的上升沿, 本次 transfer 的过程可以结束.T3: finish transfer, then enter Idle state again or the next setup. PREADY 拉低, 说明 slave 通知本次 transfer 结束. 在 PREADY unasserted 之前, PADDR, PWDATA, 以及其他的 signals 都应该保持有效.从上述时序中, 我们了解到, write transfer 看来至少需要 3 cycles. setup - access - finish而在一个 write transfer with wait states 时序中,[图例2: Write transfer with wait states]我们见到了, Slave 通过 unassert 的方式(拉低), 延迟了2pcs cycles(根据图例的例子), 这样在 T2 状态上的拉高动作, 被延时到 T4 进行拉高. 也就是Slave 通知在 T5 cycle 中结束本次 transfer.这就是通过 PREADY 引入了 wait state 后现象, 我们注意到, 一般的术语被称为"extend the transfer".Operating StatesRead Transfer 的情形与 Write Transfer 类似, 这样, 我们就基本完备讲述了APB protocol, 附上 Operating States 进行理解:[图例3: State Diagram]transfer cyclesAPB protocol 中, 明确指出: "每个 Transfer 至少消耗 2 cycles".而我们检查, 即使是 transfer with no wait state, 也最少消耗了 3 cycles. 这里我们理解, 在图例1中, T3 状态下, finish 本次 transfer后, 如果要连续操作下一个写传递的过程, 那么则在 T3 状态下保持 PSEL asserted, 配合PREADY unasserted, 恰好又进入了如 T1 cycle 相同的 setup state, 这时需要 bridge 更新地址 PWRITE, 以及数据 PWDATA. 也就是在连续 transfer(针对同一个 slave)的操作中, transfer 最少只消耗 2 cycle.我们没有在 APB 协议中, 获得上述猜测的详解, 我们保留上述对 "2 cycles" 的理解猜测于此.总结我们通过对 APB protocol 的理解, 得知 APB 是 unpipeline 的 bus. 无论如何, setup state 将占据一个 cycle, 而 access state 将占据另一个.这种 unpipeline 的设计, 很可能就是 APB 被作为连接外围的, 而不是用于processor 之间的 memory 连接的 BUS 的重要原因. 因其不要求外围在一个cycle 中对 address 进行取样, 这也给外围更多的时间反应, 至少比较而言, 使用 APB 的外围可以具备更小的 bandwidth.[AMBA AHB-Lite]AHB-LiteAHB: Advanced High-performance Bus用于高表现力高clock频率的系统. 最经常的使用是连接 internal memeory device, external memory interface, 以及 high bandwidth 外围. 其基本组元是: Master, Slave, Decoder, Multiplexor.在 address/control phase 与 data phase 中, 存在 fixed pipeline. AHB: 仅仅支持 AMBA AXI protocol 的功能子集(subset).AHB-Lite: 如果除去在 master 与 slave IP 开发中不需要的部分, 则 AHB protocol 的这个 subset 则定义为 AHB-Lite.Operation每一个 trasfer 都包括 Address phase 与 Data Phase.Address 不允许被 extend, 即便是来自 Slave 的请求, 因此我们可以想象, 全部的 Slaves 都必须在 Address phase(1 cycle) 完成 sampling address.但是与 APB 一样, Slave 也可以通过 HREADY signal 请求 extend data phase, 增加额外的时间去 sample data.HRESP signal 被用来说明 transfer 的成功与否.Address 总是可以在一个 single HCLK cycle 中完成, 除非是之前的 bus transfer 被 extend(我们理解, 这里应该是只有 data 才能做这个 extend).Data 可以占有数个 HCLK cycle, 这取决于 HREADY signal 是否 extend transfer.因此, Address phase 可以与 Data phase 的 overlapping, 就是 pipeline 的基础.[图例4: 在不同地址上的3个transfer的例子]Transfer typesTransfer types 包括: IDLE, BUSY, NONSEQ, SEQ同猜想的一样, 对于 Slave, 可以通过 HREADY 实现 extend transfer, 我们觉得, 这或者就是"较为慢速"的 Slave 实现 delay 的方式.而 Master 如果在 HTRANS[1:0] 中使用 BUSY, 也可以在 burst transfer 的过程中, 插入idle cycles. 这让人觉得, 这应算是 master 试图做 delay 的方式.[图例5: BUSY Transfer type]值得注意的是, 该例子, 使用了 4-beat 的 burst operation.Locked transfers通过 HMASTLOCK, master 可以要求完成"锁定"的 transfer, 不能被打断. 而这个用法, 往往在多个 master 的用法中存在.[图例6: Locked transfers]Default slave如果不存在的的 memory map 被 master 点中, AHB-Lite 协议给出了一个解决方案, 就是必须存在一个增加的 default slave 来进行回应.Slave transfer responsesAHB-Lite 协议中指出, Master 一旦开始一个 transfer后, 将无法主动取消这个 transfer.因此, 通过来自 Slave 的 HRESP signal 的状态, 判断 transfer 的成功与否将是重要的.HWDATA 与 HRDATA同 APB 协议一样, data bus 的 read 与 write 是分离的.所以不需要"三态"的 drivers. 我们此时有点大脑短路, 不太理解这里的意思, 这应该是说, 如果我们在单一的, 而不是分离的 data bus 上实现 read data 以及 write data, 那么我们就需要"三态驱动器"? 这里的 tristate 为何意? --有知道的同行, 这里定能有教于我.[参考文献]1. AMBA3 AHB-Lite Protocol v1.0 Specification2. AMBA APB protocol v2.0 Specification[结语]让我们引用 Sailing 的文章 "ARM与x86之4--EAGLE is Coming!" (From: /s/blog_6472c4cc0100mnza.html) 中的论述 AMBA 的片段作为结语:<剪切>"最令Intel尴尬的是,x86处理器并没有一个与 AMBA 总线类似的SoC平台总线,这是Intel 进军嵌入式领域一个不小的障碍。

AMBA 3 AHB-Lite协议中文第一版

AMBA®3AHB-Lite协议v1.0中文版版权© 2001, 2006 ARM有限公司版权所有ARM IHI 0033AXingguangyi翻译目录第一章简介 (4)1.1 关于本协议 (4)1.1.1 Master (5)1.1.2 Slave (5)1.1.3 解码器 (6)1.1.4 多路转换器 (6)1.2 操作 (6)1.3 多层AHB-Lite (7)第二章信号描述 (8)2.1 全局信号 (8)2.2 Master信号 (8)2.3 Slave信号 (9)2.4 解码器信号 (9)2.5 多路转换器信号 (10)第三章传输 (10)3.1 基本传输 (10)3.2 传输类型 (12)3.3 锁定传输 (14)3.4 传输大小 (15)3.5 Burst 操作 (16)3.5.1 Burst在一个BUSY传输后终止 (17)3.5.2 早期Burst终止 (18)3.5.3 Burst举例 (18)3.6 等待传输 (22)3.6.1 在传输等待期间改变传输类型 (23)3.6.2 在等待状态期间的地址更改 (26)3.7 保护控制 (29)第四章总线互连 (29)4.1 地址解码 (30)4.1.1 默认值 (30)4.2 总线互连 (30)第五章Slave响应信号 (31)5.1 Slave传输响应 (32)5.1.1 传输完毕 (32)5.1.2 传输挂起 (32)5.1.3 ERROR响应 (33)第六章数据总线 (34)6.1 数据总线 (35)6.1.1 HWDATA (35)6.1.2 HRDATA (35)6.1.3 大小端模式 (36)6.2 数据总线宽度 (36)6.2.1 在一个宽总线上调用窄Slave (37)6.2.2 在窄总线上调用宽Slave (37)6.2.3 在宽总线上调用Master (38)第七章时钟和复位 (38)7.1 时钟和复位要求 (39)7.1.1 时钟 (39)7.1.2 复位 (39)第一章简介1.1 关于本协议AMBA AHB-Lite是面向高性能的可综合设计,提供了一个总线接口来支持Master并提供高操作带宽。

amba总线协议3.0

竭诚为您提供优质文档/双击可除amba总线协议3.0篇一:amba协议总结1基于amba的微控制器结构基于amba的微控制器典型地由一个高性能系统中枢总线(ahb或者asb)组成,能够支持外部存储器带宽,包括cpu\片上存储器和其他直接数据存取(dma)设备(amba总线协议3.0)。

这条总线为上述单元之间大多数的传输提供高带宽接口。

在这条高性能总线上也有一个桥接器以连接低带宽的apb,而在apb上连接着大多数的系统外设。

图1基于amba的典型微控制器1.1ahb总线架构图2ahb结构框图ahb系统设计包括以下的成分:ahb主机总线主机能够通过提供地址和控制信息发起读写操作。

任何时候只允许一个总线主机处于有效状态并能使用总线。

ahb从机总线从机在给定的地址空间范围内响应读写操作。

总线从机将成功、失败或者等待数据传输的信号返回给有效的主机。

ahb仲裁器总线仲裁器确保每次只有一个总线主机被允许发起数据传输。

即使仲裁协议已经固定,任何一种仲裁算法,比如最高优先级或者公平访问都能根据应用要求而得到执行。

地址、写数据总线多路选择器地址、写数据总线多路选择器根据hmaster总线仲裁结果进行主机地址、写数据的选通输出。

ahb译码器ahb译码器用来对每次传输进行地址译码并且在传输中包含一个从机选择信号。

所有ahb执行都必须仅要求有一个中央译码器,从而进行从机的选通。

读数据、响应总线多路选择器读数据、响应总线多路选择器根据hsel信号从机选通信号,进行读数据和响应信号的选通输出。

apb桥apb桥是ambaapb中的唯一总线主机。

另外,apb桥也是ahb总线中的一个从机。

其实现ahb总线到apb总线的转换。

1.2本设计支持模式hburst中支持单一传输、未定长度增量突发、定长增量突发,不支持回环突发模式。

hresp不支持Retry、split模式。

仲裁中,不支持未定长增量突发提前终止。

传输数据大小支持字节、半字、字传输。

AMBA总结

AMBA(Advanced Microcontroller Bus Architecture),即高级微控制器总线体系。

目前,AMBA总线标准一共有四套版本,各个版本的协议都沿用至今。

1)第一套AMBA 1.0总线。

2)第二套AMBA 2.0总线。

3)第三套AMBA 3.0 AXI总线。

4)第四套AMBA4.0总线。

➢AMBA1.0只包含ASB总线和APB总线,这时候的总线协议都是三态总线,但是三态总线要设计者花很多的精力去注意时钟。

➢AMBA2.0总线新增了AHB总线,并且采用了分享型的互连结构,增加了新的特性。

➢为了顺应快速发展的SoC技术,ARM公司推出了具有更强灵活性的AMBA3.0 AXI总线。

➢2010年ARM公司发布了SoC片上总线标准的新版本AMBA4.0总线,由AXI4、AXI4-Lite、AXI4-Stream三种标准构成。

AMBA4.0规范是多家企业共同为行业而设定的,包括业界领先的OEM厂商、半导体及EDA供应商等。

AMBA4.0规范的特殊设计将使嵌入式系统达到过去只有台式电脑、笔记本电脑和网络设备才能达到的水准。

1AMBA 2.0版本标准2.0版AMBA标准定义了三种不同的总线:●AHB(Advanced High-performance Bus)高级高性能总线;●ASB(Advanced System Bus)高级系统总线;●APB(Advanced Peripheral Bus)高级外设总线。

典型的基于AMBA总线的系统框图如图:大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。

主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。

另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

AMBA_AXI3_v1.0协议中文完整翻译

求,但是相同 ID 的 transaction 必须按顺序传输。所以重要的是通过 ID 来区分,而 outstanding 则与 ID 无关) 易于通过添加寄存器达到时序收敛

AXI 协议包含了可选的扩展,该扩展覆盖了用于低功耗操作的信号。

1.2 架构

AXI 协议是基于突发的。每个事物在地址通道上都具有地址和控制信息,来描述要传输的数据特性。在主机和从 机之间传输的数据,使用一个到从机的写数据通道,或一个到主机的读地址通道。在写事物中,所有数据流是从主机 到从机的,AXI 协议有一个附加的写响应通道,可以让从机通知主机写事物完成。

写响应通道 从机使用写响应通道来响应写传输。所有写传输都要求在写响应通道上返回完成信号。 对每个突发,完成信号只产生一次,而不是突发中每个单个的数据传输都回产生一次完成信号。

1.2.2 接口和互联

一个典型的系统由通过某种互联方式连接到一起的若干个主机和从机组成,如图 1-3 所示。

图 1-3 接口和互联 AXI 协议提供了一个单一的接口定义来描述接口: 在主机和 interconnect 之间 在从机和 interconnect 之间 在主机和从机之间

读和写地址通道 读和写事物都各自有自己的地址通道。地址通道用于传送一次传输所需的所有地址和控制信息。AXI 协议支持以 下机制:

长度可变的突发,每个突发中的数据传输个数可以从 1 到 16 个 突发中一个传输的大小可以是 8-1024 bits 回环,增量或固定长度突发

001AMBA总线概述

001AMBA总线概述AMBA总线协议是⼀套由ARM提供的互连规范,该规范标准化了各种IP之间的芯⽚通信机制。

这些设计通常有⼀个或多个微处理器以及集成其他⼀些组件——内部存储器或外部存储器桥、DSP、DMA、加速器和各种其他外围设备,如USB、UART、PCIE、I2C等。

AMBA协议的主要⽬的是⽤⼀种标准和⾼效的⽅法来重⽤这些跨多个设计的IP。

学习AMBA协议的第⼀步是了解这些不同的协议在哪⾥使⽤,是如何演进的,以及它们适合什么样SOC设计。

⼀、AMBA总线发展史AMBA是由公司研发推出的⼀种⾼级微控制器总线架构(Advanced Microcontroller Bus Architecture)。

AMBA 1.0ASB 和 APBAMBA 2.0AHB, ASB 和 APBAMBA 3.0AMBA Advanced eXtensible Interface (AXI)AMBA 4.0AXI4,AXI4-lite,AXI4-stream,ACE,ACE-liteAMBA 5.0AXI5,AXI5-lite,ACE5,ACE5-lite,ACE5-liteDVM下图展⽰了传统基于AMBA2.0的SOC设计,它使⽤AHB(⾼级⾼性能)协议进⾏⾼带宽互连,以及针对低带宽外围互连的APB(⾼级外围总线)协议。

随随着越来越多的IP集成到SOC设计中,读写共享的AHB、APB总线已经⽆法满⾜互联需求了。

2003年,AMBA3.0引⼊了点对点连接协议——AXI(⾼级可扩展接⼝)。

此外在2010年,⼜推出了⼀个增强版——AXI4。

下图说明了协议的演变以及⾏业中的SOC设计趋势。

下图说明了如何使⽤AXI互连来构建各种IP通信的的SOC。

与以前的AHB/ASB总线相⽐,AXI互连有助于提⾼连接数量。

在移动和智能⼿机时代发⽣了进⼀步的演进,SOC集成了2/4/8核处理器和共享cache,并且需要跨内存⼦系统的硬件管理⼀致性。

AMBA AHB APB总线协议总结

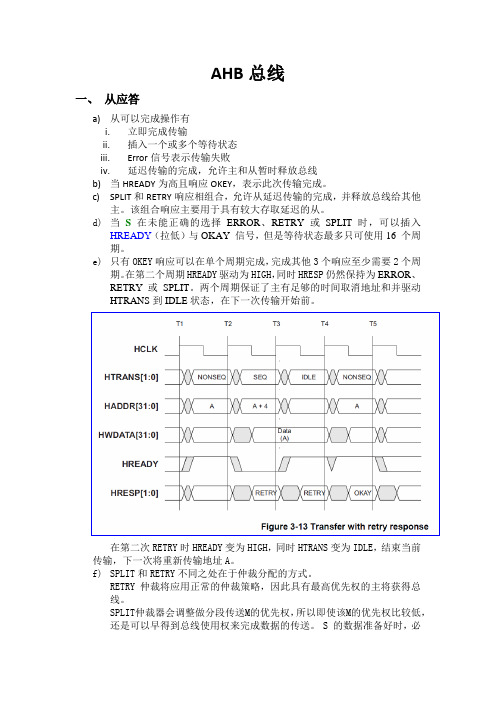

AHB总线一、从应答a)从可以完成操作有i.立即完成传输ii.插入一个或多个等待状态iii.Error信号表示传输失败iv.延迟传输的完成,允许主和从暂时释放总线b)当HREADY为高且响应OKEY,表示此次传输完成。

c)SPLIT和RETRY响应相组合,允许从延迟传输的完成,并释放总线给其他主。

该组合响应主要用于具有较大存取延迟的从。

d)当S 在未能正确的选择ERROR、RETRY 或SPLIT 时,可以插入HREADY(拉低)与OKAY 信号,但是等待状态最多只可使用16 个周期。

e)只有OKEY响应可以在单个周期完成,完成其他3个响应至少需要2个周期。

在第二个周期HREADY驱动为HIGH,同时HRESP仍然保持为ERROR、RETRY 或SPLIT。

两个周期保证了主有足够的时间取消地址和并驱动HTRANS到IDLE状态,在下一次传输开始前。

在第二次RETRY时HREADY变为HIGH,同时HTRANS变为IDLE,结束当前传输,下一次将重新传输地址A。

f)SPLIT和RETRY不同之处在于仲裁分配的方式。

RETRY仲裁将应用正常的仲裁策略,因此具有最高优先权的主将获得总线。

SPLIT仲裁器会调整做分段传送M的优先权,所以即使该M的优先权比较低,还是可以早得到总线使用权来完成数据的传送。

S 的数据准备好时,必须告知仲裁器,让相关M完成其要求。

二、仲裁机制a)主需要持续发出HBUSREQ直到获得GRANGT,对于不定长burst需要持续发出HBUSREQ。

在HGRANT有效后的下一个时钟上升沿可以地址和控制信号放到总线上。

对于需要等待的情况,可以在HGRANT有效后将HREADY拉低,表示需要等待。

b)当在两个主间进行总线移交时,需要在前一个主的倒数第二个地址被采样后(T5沿仲裁器采样到倒数第二个地址),同时切换HGRANT(T6沿主接受到grant信号),移交总线。

The arbiter changes the HGRANTx signals when the penultimate (one before last) address has been sampled. The new HGRANTx information will then be sampled at the same point as the last address of the burst is sampled.三、SPLIT传输当M和主采样到到SPLIT或RETRY响应后(T3沿),M必须立刻完成一个IDLE传输,同时仲裁器将该M的grant信号置为无效。

AMBA总线介绍

计算机基本知识AMBA总线介绍一:背景介绍ARM公司定义了AMBA(Advanced Microcontroller Bus Architecture)总线规范,它是一组针对基于ARM核的、片上系统之间通信而设计的标准协议。

因为ARM处理器的广泛使用而拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用。

在AMBA总线规范中,定义了AHB ,APB ,ASB这3种总线。

最初的AMBA总线是ASB和APB。

在它的第二个版本中,ARM引入了AHB。

(l)AHB:Advanced High Performace Bus,用于高性能系统模块的连接,支持突发模式数据传输和事务分割;(2)ASB:Advanced System Bus,也用于高性能系统模块的连接,支持突发模式数据传输,这是较老的系统总线格式,后来由AHB总线替代;(3)APB:Advanced PeriPheral Bus,用于较低性能外设的简单连接,一般是接在AHB或ASB系统总线上的第二级总线。

图1 典型的基于AMBA总线的系统[1]一个以AMBA 为架构的SOC,图1是个典型的系统架构,一般来说包含了high-performance 的system bus –AHB以及low speed, low power 的peripheral bus - APB 。

System bus 是负责连接例如ARM 之类的embedded processor 以及DMA controller,on-chip memory 和其他interface,或其他需要high bandwidth的模块。

而peripheral bus 则是用来连接系统的外围慢速模块,其协议规则相对AHB来说较为简单,它以AHB之间则通过Bridge 相连,期望能減少system bus 的loading。

二:结构以及仲裁原理1 .AHB BusAHB System是由Master,Slave,Infrastructure 三部分所组成。

第2章 AMBA协议规范

从接口

从接口 从接口

准备好。从设备使用该信号来扩展APB传输。

读取的数据。当PWRITE位低,在读周期,所选择的从设 备驱动这个总线。这个总线最多个32位宽度。 这个信号表示传输失败。APB外设不要求PSLVERR引脚。 对已经存在和新APB外设设计。当外设不包含这个引脚时, 33 到APB桥的合适的数据拉低。

25

AMBA APB错误响应

--写传输失败的例子

26

AMBA APB错误响应

--读传输失败的例子

27

AMBA APB错误响应

--PSLVERR映射(桥接时)

从AXI到APB

一个APB错误被映射回RRRSP/BRESP=SLVERR,这可以通

过将PSLVERR映射到RRESP[1]信号(用于读)和BRESP[1](用

一个典型amba系统中包括ahb和apb总线结构ambaahb规范ambaahb结构38amba高级高性能总线ahbamba高级外设总线apb?高性能?流水线操作?猝发传输?多个总线主设备?分裂交易?低功耗?锁存的地址和控制?简单的接口?适合很多外设ahb和apb总线的特性比较ambaahb规范ambaahb结构39基于中心多路复用互联机制设计ambaahb总线协议?使用这个机制所有总线主设备驱动地址和控制信号用于指示它们所希望执行的传输和仲裁器用于决定哪个主设备将其地址和控制信号布线到所有的从设备

嵌入式微控制器。它被ARM公司和众多的厂商所支持。

3

AMBA协议规范

--AMBA规范导论

应用领域

AMBA用于片上系统(System-on- a-chip, SoC)的片上总线。

自从AMBA出现后,其应用领域早已超出了微控制器设备,现在 被广泛的应用于各种范围的ASIC和SOC器件,包括用于便携设备 的应用处理器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AMBA APB4 与 AMBA3 AHB-Lite 1.0 协议介绍2013年09月18日 16:09 绝对好文关键词:AMBA , APB4 , AHB-Lite作者:Allen Zhan[介绍]根据ARM的说法, 今天 AMBA 已经成为了业界事实上的总线标准. 本文我们简单对AMBA4 中的 APB v2.0(也称为 APB4), 以及 AMBA3 AHB-Lite v1.0 进行简单的了解. 我们的介绍集中在, 我们比较有兴趣的地方. 尽管如此, 也可能几乎覆盖了协议中几个最重要的部分.[AMBA APB]AMBAAdvanced Microcontroller Bus Architecture, 由ARM定义的总线架构(标准), 由一个协议家族组成. ARM 声称这一标准已经称为事实上的 uController 业界通用标准.APBThe Advanced Peripheral Bus(APB) 是 AMBA 协议家族中一个组成部分.它被定义为一个 low-cost 的接口, 为了最小能耗与减小接口的复杂性进行的优化设计.被用于连接通用外围, 比如 timers, inerrupt controllers, UART是, and IOs. 通过 system-to-peripheral bus bridge 与 main system bus 相连, 有助于降低能耗.APB 版本当前(2013年9月), 最近的 APB协议版本是 AMBA APB Protocol Specification v2.0. 或者因为属于 AMBA4 家族中的发布协议, 一般也被称为 APB4.而在第一个版本(APB2 )中, APB 的基本组元, APB bridge 与 APB slave 被定义.而在 APB3 中, Ready signal 被引入, 这意味着增加了操作状态中, 增加了wait state. 另外增加了 PSLVERR, 用于错误报告的 signal.最近的 APB4, 增加了 PPROT 与 PSTRB signal.APB bridge 与 APB slave我们可以挂载各种"慢速"的外设在 APB 上, 比如 IO, 比如 UART, 比如 SPI, etc. 它们都作为 slave 的角色存在.但是, 我们想想看, bridge 这个 role 就蛮有意思. 它实际上暗示我们, APB 不能"单独存在". 我们这里所谓不能"单独存在"的意思, 是说 APB 一定不能直接连接在 processor 上(或者说 arm core上). 而最可能的, 是通过 APB bridge 而连接在高速的 bus 上.实际上, 在 AHB-Lite 协议中, 我们发现 APB bridge 被作为 AHB-Lite 的slave 而被定义.Data busesAPB 协议有两个独立的 data bus, 一个用来读 data, 一个用来写 data.因为没有独立的握手信号, 所以在两根bus上, 同一时刻数据传输不能同时发生.Write Transfers我们简单对 APB 的 trasfers 过程进行分析, 比如我们分析 write transfer with no wait states:[图例1: Write transfer with no wait states]T0: Idle stateT1: Setup statewrite address PADDR, write data PWDATAsetup state 仅仅只保持 1pcs clock cycle, 而在下一个 PCLK 的上升沿, 一定进入 Access state.T2: Access stateAPB bridge 通过拉高 PENABLE, 通知slave 第二阶段(也就是 access phase)开始.因为是 no wait states, 我们见到了 PREADY 在此被拉高, 表示 slave 通知bridge, 在下一个 PCLK 的上升沿, 本次 transfer 的过程可以结束.T3: finish transfer, then enter Idle state again or the next setup. PREADY 拉低, 说明 slave 通知本次 transfer 结束. 在 PREADY unasserted 之前, PADDR, PWDATA, 以及其他的 signals 都应该保持有效.从上述时序中, 我们了解到, write transfer 看来至少需要 3 cycles. setup - access - finish而在一个 write transfer with wait states 时序中,[图例2: Write transfer with wait states]我们见到了, Slave 通过 unassert 的方式(拉低), 延迟了2pcs cycles(根据图例的例子), 这样在 T2 状态上的拉高动作, 被延时到 T4 进行拉高. 也就是Slave 通知在 T5 cycle 中结束本次 transfer.这就是通过 PREADY 引入了 wait state 后现象, 我们注意到, 一般的术语被称为"extend the transfer".Operating StatesRead Transfer 的情形与 Write Transfer 类似, 这样, 我们就基本完备讲述了APB protocol, 附上 Operating States 进行理解:[图例3: State Diagram]transfer cyclesAPB protocol 中, 明确指出: "每个 Transfer 至少消耗 2 cycles".而我们检查, 即使是 transfer with no wait state, 也最少消耗了 3 cycles. 这里我们理解, 在图例1中, T3 状态下, finish 本次 transfer后, 如果要连续操作下一个写传递的过程, 那么则在 T3 状态下保持 PSEL asserted, 配合PREADY unasserted, 恰好又进入了如 T1 cycle 相同的 setup state, 这时需要 bridge 更新地址 PWRITE, 以及数据 PWDATA. 也就是在连续 transfer(针对同一个 slave)的操作中, transfer 最少只消耗 2 cycle.我们没有在 APB 协议中, 获得上述猜测的详解, 我们保留上述对 "2 cycles" 的理解猜测于此.总结我们通过对 APB protocol 的理解, 得知 APB 是 unpipeline 的 bus. 无论如何, setup state 将占据一个 cycle, 而 access state 将占据另一个.这种 unpipeline 的设计, 很可能就是 APB 被作为连接外围的, 而不是用于processor 之间的 memory 连接的 BUS 的重要原因. 因其不要求外围在一个cycle 中对 address 进行取样, 这也给外围更多的时间反应, 至少比较而言, 使用 APB 的外围可以具备更小的 bandwidth.[AMBA AHB-Lite]AHB-LiteAHB: Advanced High-performance Bus用于高表现力高clock频率的系统. 最经常的使用是连接 internal memeory device, external memory interface, 以及 high bandwidth 外围. 其基本组元是: Master, Slave, Decoder, Multiplexor.在 address/control phase 与 data phase 中, 存在 fixed pipeline. AHB: 仅仅支持 AMBA AXI protocol 的功能子集(subset).AHB-Lite: 如果除去在 master 与 slave IP 开发中不需要的部分, 则 AHB protocol 的这个 subset 则定义为 AHB-Lite.Operation每一个 trasfer 都包括 Address phase 与 Data Phase.Address 不允许被 extend, 即便是来自 Slave 的请求, 因此我们可以想象, 全部的 Slaves 都必须在 Address phase(1 cycle) 完成 sampling address.但是与 APB 一样, Slave 也可以通过 HREADY signal 请求 extend data phase, 增加额外的时间去 sample data.HRESP signal 被用来说明 transfer 的成功与否.Address 总是可以在一个 single HCLK cycle 中完成, 除非是之前的 bus transfer 被 extend(我们理解, 这里应该是只有 data 才能做这个 extend).Data 可以占有数个 HCLK cycle, 这取决于 HREADY signal 是否 extend transfer.因此, Address phase 可以与 Data phase 的 overlapping, 就是 pipeline 的基础.[图例4: 在不同地址上的3个transfer的例子]Transfer typesTransfer types 包括: IDLE, BUSY, NONSEQ, SEQ同猜想的一样, 对于 Slave, 可以通过 HREADY 实现 extend transfer, 我们觉得, 这或者就是"较为慢速"的 Slave 实现 delay 的方式.而 Master 如果在 HTRANS[1:0] 中使用 BUSY, 也可以在 burst transfer 的过程中, 插入idle cycles. 这让人觉得, 这应算是 master 试图做 delay 的方式.[图例5: BUSY Transfer type]值得注意的是, 该例子, 使用了 4-beat 的 burst operation.Locked transfers通过 HMASTLOCK, master 可以要求完成"锁定"的 transfer, 不能被打断. 而这个用法, 往往在多个 master 的用法中存在.[图例6: Locked transfers]Default slave如果不存在的的 memory map 被 master 点中, AHB-Lite 协议给出了一个解决方案, 就是必须存在一个增加的 default slave 来进行回应.Slave transfer responsesAHB-Lite 协议中指出, Master 一旦开始一个 transfer后, 将无法主动取消这个 transfer.因此, 通过来自 Slave 的 HRESP signal 的状态, 判断 transfer 的成功与否将是重要的.HWDATA 与 HRDATA同 APB 协议一样, data bus 的 read 与 write 是分离的.所以不需要"三态"的 drivers. 我们此时有点大脑短路, 不太理解这里的意思, 这应该是说, 如果我们在单一的, 而不是分离的 data bus 上实现 read data 以及 write data, 那么我们就需要"三态驱动器"? 这里的 tristate 为何意? --有知道的同行, 这里定能有教于我.[参考文献]1. AMBA3 AHB-Lite Protocol v1.0 Specification2. AMBA APB protocol v2.0 Specification[结语]让我们引用 Sailing 的文章 "ARM与x86之4--EAGLE is Coming!" (From: /s/blog_6472c4cc0100mnza.html) 中的论述 AMBA 的片段作为结语:<剪切>"最令Intel尴尬的是,x86处理器并没有一个与 AMBA 总线类似的SoC平台总线,这是Intel 进军嵌入式领域一个不小的障碍。