基于FPGA汉字显示的VHDL语言实现

基于VHDL语言的汉字滚屏显示系统设计

摘要现代电子设计技术的核心是EDA(Electronic Design Automation,电子设计自动化)技术。

它融合多学科于一体,打破了软硬件间的壁垒,使计算机的软件技术与硬件实现、设计效率和产品性能综合在一起,它代表了电子设计技术和应用的发展。

因此,掌握EDA技术是通信电子类高校学生就业的一个基本条件。

80年代后期由美国国防部开发的VHDL语言,正好满足了广大用户所期盼的面向设计的多层次、多领域且得到一致认同。

MAX+PLUSII软件是Altera提供的FPGA/CPLD开发集成环境,它具有原理图输入、文本输入、波形输入等多种输入方式,设计者利用它所配备的编辑、编译、仿真、综合芯片编程等功能完成将描述程序变换为基本的逻辑单元写入到可编程器件PLD中。

本论文主要研究的是应用一种硬件描述语言VHDL,借助MAX+PLUSII 软件开发工具,设计开发一个汉字滚屏显示系统,能够在试验箱上滚动(上、下、左、右)显示已被存于ROM中的汉字内容,用VHDL语言编程实现,编译通过后,将其下载到FPGA芯片中具体实现其功能。

关键词:电子设计自动化;VHDL硬件描述语言;MAX+PLUSII;现场可编程逻辑器件;汉字滚动显示。

ABSTRACTEDA(electronic design automation)technology is the core of the modern electronic design technology. It mixes together a lot of subjects, breaks the barrier between software and hardware, makes the technology of software and the complement of hardware and the efficiency of design and function of product synthesize one object. It represents the direction of development of electronic design technology and use. Thus, mastering EDA technology is a primary condition for students of communication electronic university to obtain employment.The language of VHDL of the American Ministry of National Defense development, is a kind of software which face to the multilayers, many realm and get the consistent approbation.MAX+PLUSII that supplied by Altera is a surrounding for CPLD/FPGA development and integration. It has graphic input and text input and waveform input and so on. Designers can write their diagram into the programming device with utilizing edit complier simulator synthesize chip editor, etc, function that provided by the software, make into ASIC chip.This thesis main research to VHDL Hardware description language draw support MAX+PLUSII, design a system to character rolling. And it can lode into the FPGA chip to rolling to left, right, up and down.Key words:EDA; MAX+PLUSII; FPGA; VHDL; The Ch.charaiter Rolling Display目录第1章绪论 (1)1.1引言 (1)1.2课题简介 (2)1.2.1课题介绍 (2)1.2.2课题意义 (2)1.3本论文研究内容 (3)第2章相关知识介绍 (4)2.1 EDA技术 (4)2.1.1EDA技术简介 (4)2.1.2EDA技术实现目标 (5)2.1.3EDA技术的发展趋势 (7)2.2硬件描述语言VHDL (9)2.2.1 VHDL语言程序设计的基本结构 (10)2.2.2 VHDL语言的数据类型及运算操作符 (11)2.2.3 VHDL语言的主要描述语句 (12)2.2.4 VHDL语言构造体的描述方式 (13)2.2.5 VHDL语言设计基本逻辑电路 (14)2.3 MAX+PLUSⅡ概述 (15)2.3.1 MAX+PLUSII的特点 (15)2.3.2 MAX+PLUSII的设计流程 (16)2.3.3 MAX+PLUSII的使用 (17)2.4 PLD简介 (21)2.4.1 PLD技术概述 (21)2.4.2 PLD的基本结构 (22)2.4.3 PLD教学实验箱简介 (23)2.5 本章小结 (26)第3章系统实现方法 (27)3.1 系统的实现方法 (27)3.1.1 数字系统的设计方法 (27)3.1.2本系统的实现方法 (28)3.2 VHDL实现系统功能 (30)3.2.1快、慢信号的控制显示 (30)3.2.2汉字信息的取得及其存储器的实现 (30)3.2.3汉字上下左右滚动的控制实现 (31)3.3本章小结 (32)第4章系统的仿真与调试 (33)4.1 系统的仿真 (33)4.2 VHDL实现的系统编译 (33)4.3仿真的下载演示 (35)4.4本章小结 (35)结论 (36)参考文献 (37)致谢 (38)附录 VHDL实现的系统程序清单 (39)第1章绪论1.1引言进入20世纪后半段,集成电路技术的发展是电子系统的实现方式发生了很大的变化。

基于FPGA的汉字点阵显示系统设计

Ara 现 场 可编程 门 阵列 ) 设 计 , P r, 来 F GA 是一 种 高 密度 可 编程逻 辑 器 件 , 支 持 系 统 可 编 程 , 过 写 它 通 入不 同 的配置数 据 就可 以实现 不 同 的逻辑 功 能 , 使

用 F G 来 设 计 电 子 系 统 , 有 设 计 周 期 短 、 于 P A 具 易

本 设 计 通 过 F GA 的 引 入 , 用 E P 利 DA 工 具 软

成 为信 息传 播 的划 时代 产 品 , 在铁 路 、 民航 、 育场 体

馆 、 议 厅 、 速 公 路 、 场 、 型 商 场 、 行 、 券 会 高 广 大 银 证 市 场 以及 多 种监 控调 度 中得 到 了广 泛 的应用 。 本 系统 采用 F G F e r ga P A( i d P o rmma l Gae l be t

Ke r s y wo d :PL ;FP D GA ;LED ip a ;V HDL ;Qu r u I ds ly a t sI

L D显 示 屏 技 术 是 集 光 电 子 技 术 、 电 子 技 E 微

术 、 算机 技 术 和视 频 技 术 为 一体 的 高 科 技 产 品 , 计

第 1 1卷 第 5期

Vo . 1 1 1 No 5 .

无 锡 职 业 技 术 学 院 学 报

J OuRNAL 0F W UXII TI NS TUTE OF TECHNOL OGY

21 0 2年 1 O月

oc.2 1 t O 2

基 于 F GA 的汉 字 点 阵显 示 系统 设 计 P

c e, a t rt e t e t wih FPG A , t h od fe r am n t o t e LED o a rx d s a i he c r e po i g cr u t c nt o , i d t m t i ipl y, n t o r s nd n ic i o r l t c n t a f r fe e tChi s ha a t r .The s s e a r a p ia i n v l . a r ns o m dif r n ne e c r c e s y t m h s a b o d a plc to a ue

FPGA中文VHDL语言教程

第5章VHDL深入本章仍将沿用第3章中通过一些实例引出了相关的VHDL语法结构和语言现象,并给予一定说明的方法,介绍一些新的实例及相关的VHDL语法知识,使读者进一步深入了解VHDL语言现象和语句规则的特点,以及应用VHDL表达与设计电路的方法。

下面首先对第3章出现的一些语法现象作更为深入的讨论,然后再引出一些新的实例,帮助读者对相关的语法现象作更详细的了解。

5.1 数据对象及其示例说明在VHDL中,数据对象有三类,即变量(V ARIABLE)、常量(CONSTANT)和信号(SIGNAL)。

如前所述,数据对象类似于一种容器,它接受不同数据类型的赋值。

变量和常量可以从软件语言中找到对应的类型,然而信号的表现较特殊,它具有更多的硬件特征,是VHDL中最有特色的语言要素之一。

尽管信号和变量已在前面一些示例中出现过,但都没有作更详细的解释,这势必影响对VHDL程序的更好理解,以下将针对数据对象给出一些示例,以作进一步的说明。

5.1.1 常数常数的定义和设置主要是为了使程序更容易阅读和修改。

例如,将逻辑位的宽度定义为一个常量,只要修改这个常量就能很容易地改变宽度,从而改变硬件结构。

在程序中,常量是一个恒定不变的值,一旦作了数据类型和赋值定义后,在程序中不能再改变,因而具有全局性意义。

常数定义的一般表述如下:CONSTANT 常数名:数据类型 := 表达式;例如:CONSTANT FBT : STD_LOGIC_VECTOR := "010110" ; -- 标准位矢类型CONSTANT DATAIN : INTEGER := 15 ; -- 整数类型第1句定义常数FBT的数据类型是STD_LOGIC_VECTOR,它等于"010110";第2句定义常数DATAIN的数据类型是整数INTEGER,它等于15 。

VHDL要求所定义的常量数据类型必须与表达式的数据类型一致。

基于FPGA及VHDL的LED点阵汉字滚动显示设计方案【VIP专享】

基于FPGA及VHDL的LED点阵汉字滚动显示设计方案发布: 2011-8-31 | 作者: —— | 来源:wangliuguo| 查看: 555次| 用户关注:汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如Qua汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如QualtusⅡ软件,将硬件描述语言——VHDL程序固化于具有丰富I/O口、内部逻辑和连线资源的FPGA(现场可编程门阵列)中。

该技术具有系统设计效率高、集成度好、保密性强、易于修改、易于实现等优点,成为当今数字系统设计主流技术。

此方式所制作的LED点阵控制器,由于是纯硬件行为,具有速度快、可靠性高、抗干扰能力强、开发周期短等显著优点。

1 EDA点阵显示汉字原理以8×8的LED点阵为例,8×8的LED点阵是由64个发光二极管按矩阵形式排列而成,每一行上的发光管有一个公共的阳极(或阴极),每一列上的发光管有一个公共的阴极(或阳极),一般按动态扫描方式显示汉字或图形。

扫描分为点扫描、行扫描和列扫描三种方式。

行扫描需要按行抽取字型码,列扫描则需要按列抽取字型码。

用FPGA设计LED汉字滚动显示器

摘要:本文主要讨论了使用EDA工具设计汉字滚动显示器的技术问题。

文中首先描述了基于现场可编程门阵列(FPGA)的硬件电路;然后研究了在8×8LED发光二极管点阵上显示滚动汉字的原理,并给出了基于ALTERA的参数化模型库LPM描述其功能的VHDL语言程序设计;最后对使用EDA工具软件加工被显示数据文件的方法进行了讨论。

采用传统方法设计的汉字滚动显示器,通常需要使用单片机、存储器和制约逻辑电路来进行PCB(印制电路板)板级的系统集成。

尽管这种方案有单片机软件的支持较为灵活,但是由于受硬件资源的限制,未来对设计的变更和升级,总是难以避免要付出较多研发经费和较长投放市场周期的代价。

随着电子设计自动化(EDA)技术的进展,基于可编程ASIC器件的数字电子系统设计的完整方案越来越受到人们的重视,并且以EDA技术为核心、的能在可编程ASIC器件上进行系统芯片集成的新设计方法,也正在快速地取代基于PCB板的传统设计方式。

如何使用EDA工具设计电子系统是人们普遍关心的问题。

在EDA工具软件MAX+PLUS Ⅱ的支持下,本设计通过了编译、适配和软件仿真验证。

最后用载入真实实验系统的硬件实验证明了它的正确性。

硬件设计为了简化讨论,本文只研究在单个8×8 LED 发光二极管点阵上滚动显示多汉字信息的问题。

图1给出的就是一个使用美国ALTERA公司10K系列FPGA设计的可支持滚动显示多汉字信息的通用硬件电路。

在图中,标准JTAG接口与PC机并口相连,用于下载设计数据至FPGA中;LED点阵的data线由FPGA的I/O线串300Ω限流电阻后驱动,而sw线直接由FPGA的I/O 线驱动。

LED点阵采用扫描式工作方式,控制sw线的循环扫描信号为低电平有效,显示数据data为高电平有效。

由于ALTERA的10K10LC84-4芯片内部有足够的RAM资源,所以本设计没有采用外部RAM。

另外,图中的配置EPROM为可选件,只有当要求汉字滚动显示器脱机运行时才需要采用。

基于FPGA的点阵汉字显示

FPGA综合设计实验报告题目 16×16点阵汉字显示作者徐双健专业微电子0902 日期 2013年4月1号第一章前言 (3)1.1本设计的研究背景和研究目的 (3)1.2LED点阵显示特点 (3)1.3FPGA设计的特点 (3)第二章系统设计 (5)2.1设计任务与要求 (5)2.1.2设计要求 (5)2.2设计原理 (5)2.2.1总体设计方案 (5)2.3扫描控制模块2.3.1LED的显示原理 (5)2.4方案一: (6)此法太过麻烦! (18)2.5方案二 (19)2.5.1汉字的存储 (19)2.5.1汉字显示 (21)第三章系统调试与仿真 (24)3.1开发环境介绍 (24)3.2调试与仿真 (24)3.2.1 创建工程 (24)3.2.2 编译前设置 (24)3.2.3 全程编译 (26)3.2.4时序仿真 (27)第四章结束语 (29)答谢辞...............................................................错误!未定义书签。

第一章前言1.1 本设计的研究背景和研究目的鉴于LED的自身优势,主要应用于以下几大方面:∙显示屏、交通讯号显示光源的应用LED灯具有抗震耐冲击、光响应速度快、省电和寿命长等特点,广泛应用于各种室内、户外显示屏,分为全色、双色和单色显示屏,全国共有100多个单位在开发生产。

交通信号灯主要用超高亮度红、绿、黄色LED,因为采用LED信号灯既节能,可靠性又高,所以在全国范围内,交通信号灯正在逐步更新换代,而且推广速度快,市场需求量很大,是个很好的市场机会。

∙汽车工业上的应用汽车用灯包含汽车内部的仪表板、音响指示灯、开关的背光源、阅读灯和外部的刹车灯、尾灯、侧灯以及头灯等。

汽车用白炽灯不耐震动撞击、易损坏、寿命短,需要经常更换。

1987年,我国开始在汽车上安装LED高位刹车灯。

由于LED响应速度快,可以及早提醒司机刹车,减少汽车追尾事故,在发达国家,使用LED制造的中央后置高位刹车灯已成为汽车的标准件,美国HP公司在1996年推出的LED汽车尾灯模组可以随意组合成各种汽车尾灯。

基于FPGA的点阵汉字显示课程设计论文

基于FPGA 的点阵显示控制的设计一.课程要求1、技术要求:(1)掌握8X8点阵显示的工作原理;(2)熟练掌握Quartus Ⅱ6.0 软件的使用方法;(3)能运用VHDL 语言根据要求实现显示不同汉字;(4)能根据要求对设计电路进行仿真和测试。

2、功能要求:实现显示汉字“电气二加油”的一屏一屏显示。

3、本人的工作:负责软件的编写,仿真,下载,调试。

二.设计方案:1、硬件部分(框图)2、软件部分library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity wen is ---函数库port(clk,k,l:in std_logic;ld,com:out std_logic_vector(7 downto 0));end wen; ----主函数architecture one of wen issignal st:std_logic_vector(7 downto 0);signal osc,osd:std_logic;signal d_ff:std_logic_vector(29 downto 0);signaldata,d0,d1,d2,d3,d4,d5,d6,d7,d8,d9,d10,d11,d12,d13,d14,d15:std_logic_vector(7 downto 0);signal lie0:std_logic_vector(6 downto 0); ---定义变量begincom<=data;ld<=st;d0<="00000000"when lie0(6 downto 0)="0000000"else"00000100"when lie0(6 downto 0)="0000001"else"00100000"when lie0(6 downto 0)="0000010"else"01000100"when lie0(6 downto 0)="0000011"else"10001010"when lie0(6 downto 0)="0000100"else"11111111"when lie0(6 downto 0)="0000101"else"11111011"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"10111011"when lie0(6 downto 0)="0001000"else"01110101"when lie0(6 downto 0)="0001001"else"00000000";d1<="00111110"when lie0(6 downto 0)="0000000"else"00010010"when lie0(6 downto 0)="0000001"else"00100000"when lie0(6 downto 0)="0000010"else"00111110"when lie0(6 downto 0)="0000011"else"01010100"when lie0(6 downto 0)="0000100"else"11000001"when lie0(6 downto 0)="0000101"else"11101101"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"11000001"when lie0(6 downto 0)="0001000"else"10101011"when lie0(6 downto 0)="0001001"else"00000000";d2<="00101010"when lie0(6 downto 0)="0000000"else"00010101"when lie0(6 downto 0)="0000001"else"00100100"when lie0(6 downto 0)="0000010"else"10000100"when lie0(6 downto 0)="0000011"else"00000000"when lie0(6 downto 0)="0000100"else"11010101"when lie0(6 downto 0)="0000101"else"11101010"when lie0(6 downto 0)="0000110"else"11011011"when lie0(6 downto 0)="0000111"else"01111011"when lie0(6 downto 0)="0001000"else"00000000";d3<="11111111"when lie0(6 downto 0)="0000000"else "00010101"when lie0(6 downto 0)="0000001"else "00100100"when lie0(6 downto 0)="0000010"else "01111100"when lie0(6 downto 0)="0000011"else "11111100"when lie0(6 downto 0)="0000100"else "00000000"when lie0(6 downto 0)="0000101"else "11101010"when lie0(6 downto 0)="0000110"else "11011011"when lie0(6 downto 0)="0000111"else "10000011"when lie0(6 downto 0)="0001000"else "00000011"when lie0(6 downto 0)="0001001"else "00000000";d4<="10101010"when lie0(6 downto 0)="0000000"else "00010101"when lie0(6 downto 0)="0000001"else "00100100"when lie0(6 downto 0)="0000010"else "00000000"when lie0(6 downto 0)="0000011"else "10010100"when lie0(6 downto 0)="0000100"else "01010101"when lie0(6 downto 0)="0000101"else "11101010"when lie0(6 downto 0)="0000110"else "11011011"when lie0(6 downto 0)="0000111"else "11111111"when lie0(6 downto 0)="0001000"else "01101011"when lie0(6 downto 0)="0001001"else "00000000";d5<="10111110"when lie0(6 downto 0)="0000000"else "01110101"when lie0(6 downto 0)="0000001"else "00100100"when lie0(6 downto 0)="0000010"else "01111100"when lie0(6 downto 0)="0000011"else "11111111"when lie0(6 downto 0)="0000100"else "01000001"when lie0(6 downto 0)="0000101"else "10001010"when lie0(6 downto 0)="0000110"else "11011011"when lie0(6 downto 0)="0000111"else "10000011"when lie0(6 downto 0)="0001000"else "00000000"when lie0(6 downto 0)="0001001"else "00000000";d6<="11000000"when lie0(6 downto 0)="0000000"else "10000000"when lie0(6 downto 0)="0000001"else "00100000"when lie0(6 downto 0)="0000010"else "01000100"when lie0(6 downto 0)="0000011"else "10010100"when lie0(6 downto 0)="0000100"else"01111111"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"10111011"when lie0(6 downto 0)="0001000"else"01101011"when lie0(6 downto 0)="0001001"else"00000000";d7<="00000000"when lie0(6 downto 0)="0000000"else"11000000"when lie0(6 downto 0)="0000001"else"00100000"when lie0(6 downto 0)="0000010"else"01111100"when lie0(6 downto 0)="0000011"else"11111100"when lie0(6 downto 0)="0000100"else"11111111"when lie0(6 downto 0)="0000101"else"00111111"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"10000011"when lie0(6 downto 0)="0001000"else"00000011"when lie0(6 downto 0)="0001001"else"00000000"; ---字库电气二加油d8<="00000000"when lie0="00000000"else"00111110"when lie0="00000001"else"00101010"when lie0="00000010"else"11111111"when lie0="00000011"else"10101010"when lie0="00000100"else"10111110"when lie0="00000101"else"11000000"when lie0="00000110"else"00000000"when lie0="00000111"else"00000000"when lie0="00001000"else"00000000"when lie0="00001001"else"00000000";d9<="00111110"when lie0="00000000"else"00101010"when lie0="00000001"else"11111111"when lie0="00000010"else"10101010"when lie0="00000011"else"10111110"when lie0="00000100"else"11000000"when lie0="00000101"else"00000000"when lie0="00000110"else"00000000"when lie0="00000111"else"00000000"when lie0="00001000"else"00000000"when lie0="00001001"else"00000000";d10<="00101010"when lie0="00000000"else"10101010"when lie0="00000010"else "10111110"when lie0="00000011"else "11000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00000000"when lie0="00000110"else "00000000"when lie0="00000111"else "00000000"when lie0="00001000"else "00111110"when lie0="00001001"else "00000000";d11<="11111111"when lie0="00000000"else "10101010"when lie0="00000001"else "10111110"when lie0="00000010"else "11000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00000000"when lie0="00000110"else "00000000"when lie0="00000111"else "00111110"when lie0="00001000"else "00101010"when lie0="00001001"else "00000000";d12<="10101010"when lie0="00000000"else "10111110"when lie0="00000001"else "11000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00000000"when lie0="00000110"else "00111110"when lie0="00000111"else "00101010"when lie0="00001000"else "11111111"when lie0="00001001"else "00000000";d13<="10111110"when lie0="00000000"else "11000000"when lie0="00000001"else "00000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00111110"when lie0="00000110"else "00101010"when lie0="00000111"else "11111111"when lie0="00001000"else"00000000";d14<="11000000"when lie0="00000000"else "00000000"when lie0="00000001"else "00000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00111110"when lie0="00000101"else "00101010"when lie0="00000110"else "11111111"when lie0="00000111"else "10101010"when lie0="00001000"else "10111110"when lie0="00001001"else"00000000";d15<="00000000"when lie0="00000000"else "00000000"when lie0="00000001"else "00000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00111110"when lie0="00000100"else "00101010"when lie0="00000101"else "11111111"when lie0="00000110"else "10101010"when lie0="00000111"else "10111110"when lie0="00001000"else "11000000"when lie0="00001001"else"00000000"; ---字库循环电first:process-----分频beginwait until clk='1';if d_ff(29 downto 0)>=2e8 thend_ff(29 downto 0)<="000000000000000000000000000000"; elsed_ff(29 downto 0)<=d_ff+1;end if;osc<=not d_ff(10);if l='0' thenosd<=not d_ff(26);else osd<= not d_ff(24);---程序分频取第26位24 位end if;end process first;second:process(osc)----扫描部分beginif(osc='1' and osc'event)thencase k iswhen '1'=> ---一屏一屏显示电气二加油if st(7 downto 0)="00000000"or st(7 downto 0)="01111111" then st(7 downto 0)<="11111110";data<=d0;elsif st(7 downto 0)="11111110"thenst(7 downto 0)<="11111101";data<=d1;elsif st(7 downto 0)="11111101" thenst(7 downto 0)<="11111011";data<=d2;elsif st(7 downto 0)="11111011" thenst(7 downto 0)<="11110111";data<=d3;elsif st(7 downto 0)="11110111" thenst(7 downto 0)<="11101111";data<=d4;elsif st(7 downto 0)="11101111" thenst(7 downto 0)<="11011111";data<=d5;elsif st(7 downto 0)="11011111" thenst(7 downto 0)<="10111111";data<=d6;elsif st(7 downto 0)="10111111" thenst(7 downto 0)<="01111111";data<=d7;end if; ---逐列扫描when '0'=> ---滚动显示电if st(7 downto 0)="00000000"or st(7 downto 0)="01111111" then st(7 downto 0)<="11111110";data<=d8;elsif st(7 downto 0)="11111110"thenst(7 downto 0)<="11111101";data<=d9;elsif st(7 downto 0)="11111101" thenst(7 downto 0)<="11111011";data<=d10;elsif st(7 downto 0)="11111011" thenst(7 downto 0)<="11110111";data<=d11;elsif st(7 downto 0)="11110111" thenst(7 downto 0)<="11101111";data<=d12;elsif st(7 downto 0)="11101111" thenst(7 downto 0)<="11011111";data<=d13;elsif st(7 downto 0)="11011111" thenst(7 downto 0)<="10111111";data<=d14;elsif st(7 downto 0)="10111111" thenst(7 downto 0)<="01111111";data<=d15;end if;end case;end if;end process second;third:process(osd)---循环beginif(osd='1' and osd'event)thenif lie0(6 downto 0)="0001001"thenlie0(6 downto 0)<="0000000";else lie0(6 downto 0)<=lie0+1;end if;end if;end process third;end one;三.软件设计的过程1.初始的设计:构思是按照列共阳行共阴设计“电气二”三个字一频一频显示。

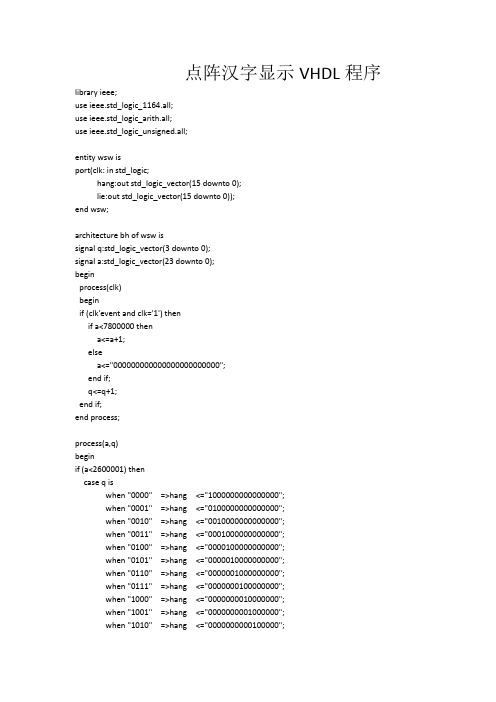

点阵汉字显示VHDL程序

点阵汉字显示VHDL程序libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entitywsw isport(clk: in std_logic;hang:outstd_logic_vector(15 downto 0);lie:outstd_logic_vector(15 downto 0));endwsw;architecturebh of wsw issignal q:std_logic_vector(3 downto 0);signal a:std_logic_vector(23 downto 0);beginprocess(clk)beginif (clk'event and clk='1') thenif a<7800000 thena<=a+1;elsea<="000000000000000000000000";end if;q<=q+1;end if;end process;process(a,q)beginif (a<2600001) thencase q iswhen "0000" =>hang <="1000000000000000"; when "0001" =>hang <="0100000000000000"; when "0010" =>hang <="0010000000000000"; when "0011" =>hang <="0001000000000000"; when "0100" =>hang <="0000100000000000"; when "0101" =>hang <="0000010000000000"; when "0110" =>hang <="0000001000000000"; when "0111" =>hang <="0000000100000000"; when "1000" =>hang <="0000000010000000"; when "1001" =>hang <="0000000001000000"; when "1010" =>hang <="0000000000100000";when "1011" =>hang <="0000000000010000"; when "1100" =>hang <="0000000000001000"; when "1101" =>hang <="0000000000000100"; when "1110" =>hang <="0000000000000100"; when "1111" =>hang <="0000000000000001"; end case;case q iswhen "0000" =>lie <="1111111111111111"; when "0001" =>lie <="1000000000000011"; when "0010" =>lie <="1111111011111111"; when "0011" =>lie <="1111111011111111"; when "0100" =>lie <="1111111011111111"; when "0101" =>lie <="1111111011111111"; when "0110" =>lie <="1111111011111111"; when "0111" =>lie <="1100000000000011"; when "1000" =>lie <="1111111011111111"; when "1001" =>lie <="1111111011111111"; when "1010" =>lie <="1111111011111111"; when "1011" =>lie <="1111111011111111"; when "1100" =>lie <="1111111011111111"; when "1101" =>lie <="0000000000000000"; when "1110" =>lie <="1111111111111111"; when "1111" =>lie <="1111111111111111";end case;elsif (a<5200000) thencase q iswhen "0000" =>hang<="1000000000000000"; when "0001" =>hang<="0100000000000000"; when "0010" =>hang<="0010000000000000"; when "0011" =>hang<="0001000000000000"; when "0100" =>hang<="0000100000000000"; when "0101" =>hang<="0000010000000000"; when "0110" =>hang<="0000001000000000"; when "0111" =>hang<="0000000100000000"; when "1000" =>hang<="0000000010000000"; when "1001" =>hang<="0000000001000000"; when "1010" =>hang<="0000000000100000"; when "1011" =>hang<="0000000000010000"; when "1100" =>hang<="0000000000001000"; when "1101" =>hang<="0000000000000100"; when "1110" =>hang<="0000000000000100"; when "1111" =>hang<="0000000000000001";end case;case q iswhen "0000" =>lie<="1111111111111111"; when "0001" =>lie<="1000000100000001"; when "0010" =>lie<="1111110111111101"; when "0011" =>lie<="1111110111111101"; when "0100" =>lie<="1011110110111101"; when "0101" =>lie<="1101101111011011"; when "0110" =>lie<="1110101111101011"; when "0111" =>lie<="1111011111110111"; when "1000" =>lie<="1111001111110011"; when "1001" =>lie<="1110110111101101"; when "1010" =>lie<="1110111011011110"; when "1011" =>lie<="1101111110111111"; when "1100" =>lie<="1011111101111111"; when "1101" =>lie<="0111111011111111"; when "1110" =>lie<="1111111111111111"; when "1111" =>lie<="1111111111111111";end case;elsecase q iswhen "0000" =>hang <="1000000000000000"; when "0001" =>hang <="0100000000000000"; when "0010" =>hang <="0010000000000000"; when "0011" =>hang <="0001000000000000"; when "0100" =>hang <="0000100000000000"; when "0101" =>hang <="0000010000000000"; when "0110" =>hang <="0000001000000000"; when "0111" =>hang <="0000000100000000"; when "1000" =>hang <="0000000010000000"; when "1001" =>hang <="0000000001000000"; when "1010" =>hang <="0000000000100000"; when "1011" =>hang <="0000000000010000"; when "1100" =>hang <="0000000000001000"; when "1101" =>hang <="0000000000000100"; when "1110" =>hang <="0000000000000100"; when "1111" =>hang <="0000000000000001"; end case;case q iswhen "0000" =>lie <="1111011110111111";when "0001" =>lie <="1111011110111111"; when "0010" =>lie <="1110011110111111"; when "0011" =>lie <="1110100000000011"; when "0100" =>lie <="1110111110111111"; when "0101" =>lie <="1100110000000011"; when "0110" =>lie <="1100111110111111"; when "0111" =>lie <="1010111110111111"; when "1000" =>lie <="0110100000000011"; when "1001" =>lie <="1110111110111011"; when "1010" =>lie <="1110111110111011"; when "1011" =>lie <="1110111110111011"; when "1100" =>lie <="1110111110101011"; when "1101" =>lie <="1110111110110011"; when "1110" =>lie <="1110111110111111"; when "1111" =>lie <="1110111110111111"; end case;end if;end process;endbh;。

基于FPGA的汉字显示系统设计

基于FPGA的汉字显示系统设计董莹【摘要】This paper introduces the basic principles and design method of displaying Chinese characters by Chinese characters display system based on FPCA in 16x16 dot matrix display; expounds design principle of Chinese characters display system based on FPCA, analyzes ways of designing cycle display of Chinese characters with simpler method, combining with an example; finally the Block Diagram / Schematic File and part VHDL source file are given.%文章介绍了FPGA构建的汉字显示系统在16×16点阵显示器上显示汉字的基本原理和系统设计方法;阐述了基于FPGA的汉字显示系统设计的原理,并结合实例分析如何用较为简单的方法设计循环汉字显示;最后给出了Block Diagram/Schematic File和部分VHDL源文件.【期刊名称】《价值工程》【年(卷),期】2012(031)010【总页数】2页(P166-167)【关键词】LED点阵显示;VHDL;汉字显示;FPGA;EDA【作者】董莹【作者单位】青海民族大学,西宁810007;西安电子科技大学研究生院,西安710071【正文语种】中文【中图分类】TP310 引言随着技术的发展,人们对信息交换手段的不断提出新的要求,同时对文字和图形现实的要求也越来越高。

传统的数字电路、单片机以及EDA技术都为今天的文字和图形图像显示提供了技术支持。

毕业设计 基于VHDL的汉字点阵动态显示系统的设计

目录摘要 (1)关键词 (1)Abstract (1)Key words (1)引言 (1)1 设计方案1.1 方案一 (2)1.2 方案二 (2)1.3 方案比较 (3)2 扫描控制模块2.1 LED点阵原理 (3)2.2 汉字的存储 (4)2.3 汉字的显示 (5)2.4 滚动速度的控制 (6)3 VHDL语言程序设计3.1扫描频率控制的部分关键程序 (6)3.2单个汉字扫描的部分关键程序 (7)3.3汉字滚动速度控制的部分关键程序 (8)4 系统调试4.1开发环境介绍 (9)4.2调试、仿真与体会 (10)5系统功能、指标参数 (14)6 设计结论 (14)致谢 (14)参考文献 (14)基于VHDL的汉字点阵动态显示系统的设计摘要:主要研究基于VHDL的 Led点阵汉字滚动显示。

首先描述了基于现场可编程门阵列(FPGA)的硬件电路,以及点阵显示汉字的原理;然后在单个16X16 LED发光二极管点阵上滚动汉字的原理;最后给出了描述其功能的VHDL语言程序设计方法。

通过编程、调试、仿真、下载正确地实现了汉字滚动显示扫描结果,其硬件系统的实验验证也获得了与软件模拟仿真结论相吻合的结果。

关键词:LED点阵;FPGA;VHDL语言;汉字滚动显示Design of Chinese characters scrolling display on LED dotmatrix based on VHDLAbstract:The design of this subject mainly researches Chinese characters scrolling display on LED dot matrix screen based on FPGA and VHDL . This article firstly describes the hardware circuit based on logic cell array,as well as the principle of Chinese characters display on LED dot matrix .Finally,the article gives the method of VHDL design which describes the function.This design realizes the results of Chinese characters scrolling and scanning correctly by programming ,debugging ,sinulation and download ,Also the experimintal verificattion of hardware systerns has received the conclusions in accordance with the results of software simulation .Key words:LED dot matrix;FPGA;VHDL;Chinese characters scrolling display引言随着我国经济的高速发展,对公共场合发布信息的需求日益增长,利用LED 点阵滚动显示汉字的出现正好适应了这一市场需求,已经成为信息传播的一种重要手段。

基于fpga的点阵汉字显示[整理版]

![基于fpga的点阵汉字显示[整理版]](https://img.taocdn.com/s3/m/8734da0a58eef8c75fbfc77da26925c52cc5913f.png)

基于FPGA的点阵汉字显示摘要:本课程设计主要研究基于FPGA的点阵汉字动态显示。

首先介绍了LED点阵显示汉字的原理,然后通过编程控制可以显示中英文字符、图形及视频动态图形。

LED显示以其组构方式灵活、亮度高、技术成熟、成本低廉等特点在证券、运动场馆及各种室内外显示场合得到广泛的应用。

本实验结合实例运用基于FPGA的VHDL语言编程使其循环显示“武汉理工大学信息工程学院庞锦”这几个字。

论文描述了基于现场可编程门阵(FPGA)的硬件电路,以及点阵显示汉字的原理;然后介绍在单个16X16 LED点阵上滚动汉字的原理;最后给出了描述其功能的VHDL语言程序设计方法。

通过编程、调试、仿真、下载正确地实现了汉字滚动显示扫描结果,其硬件系统的实验验证也获得了与软件模拟仿真结论相吻合的结果。

关键词:FPGA VHDL语言点阵汉字显示The dot matrix characters display based on FPGAAbstract:This course design is primary research based on VHDL of the dot-matrix characters displayed. Firstly introduces the principle of LED dot-matrix display characters, Then through the programming control can show Chinese and English characters, graphics and video dynamic graphics. LED display with its group structure flexible, high brightness, mature technology and low cost characteristics widely used in the securities, sports venues and a variety of indoor and outdoor show occasion. In this study, with examples using VHDL language programming of FPGA-based make the cyclic display "wu han university of science and technology information engineering college Pang J in” the words. The papers first described based on field programmable gate array (FPGA) hardware circuit, as well as the principle character dot matrix display; and then in a single 16X16 LED scrolling LED dot matrix on the principles of Chinese characters; Finally, the VHDL description language program of its functions design. Through programming, debugging, simulation, download the correct character scroll achieved scan results, the experimental verification of its hardware and software are also obtained findings consistent with simulation results.Keywords: FPGA; VHDL language; Dot matrix characters display;一、引言随着世界和我国经济的高速发展,在公共场所动态显示信息已相当显眼,利用LED点阵滚动显示汉字的出现正好适应了这一市场需求,已经成为信息传播的一种重要手段。

基于FPGA和VHDL的汉明码编解码器设计

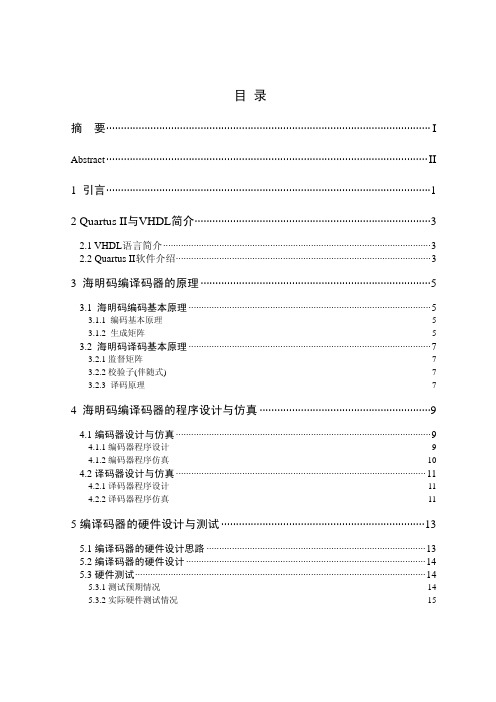

3.1 海明码编码基本原理 ·······························································································5

目录

摘 要·············································································································· I

Abstract ·············································································································II

如果一个分组码的数据位长度为k校验位长度为r总的编码长度为kr则总的可以编码的合法码字的个数为2k总的码字个数为2n可以看出检验位的长度越长合法码字所占的比例就越小如果这些码字能够尽可能地在所有的码字中均匀分布的话合法码字之间的最小海明码距就越大编码的抗干扰能力也就越强因此设计编码方法的最重要的任务就是尽量使合法码字尽可能地均匀分差错控制编码在通信电子系统中得到广泛应用其中一类重要的差错控制编码是线性分组码线性分组码中信息位和监督位通过代数方程相联系

5.3.1 测试预期情况 ······················································································································14 5.3.2 实际硬件测试情况 ··············································································································15

基于FPGA汉字显示设计

目录0引言与摘要----------------------------------------------------------------------2 1系统设计功能与要求----------------------------------------------------------3 2系统设计思路----------------------------------------------------------------3 3现场可编程门阵列FPGA与QualtusⅡ软件的简介-------------4 3.1现场可编程门阵列FPGA的简介-------------------------------------4 3.1.1 FPGA概述-------------------------------------------------------------4 3.1.2 FPGA基本结构-------------------------------------------------------4 3.2 QualtusⅡ软件的简介------------------------------6 4各模块设计说明、源代码及仿真结果---------------------------------------7 4.1分频模块的设计----------------------------------------------------------7 4.2计数电路模块的设计---------------------------------------------10 4.3并臵电路模块的设计-------------------------------------------------13 4.4存储电路模块的设计---------------------------------------------------15 5系统整体设计说明、源代码及仿真结果--------------------------------15 5.1系统整体设计说明------------------------------------15 5.2系统整体仿真----------------------------------------16 6设计创新点说明及设计心得-----------------------------------------16 7参考文献------------------------------------------------------------------------17基于FPGA的汉字循环显示设计青海民族大学罗泽攀王鹏梁倩摘要:简单介绍16x16点阵显示的基本原理;结合实例分析如何用较为简单的方法设计循环汉字显示,并且给出了部分VHDL源文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$ " " # = ’ ’ ’?@ A = = # ’ ’ ( ’ #?’ = ’ >?’ B ! 文章编号 !

基于 2 C <$ 汉字显示的 )4D 1 语言实现

张庆玲

" 西安航空技术高等专科学校 # 陕西 西安 !> $ = ’ ’ > >

) ) 实体描述 H S N G N & * L I [ G Q) OH % ( _ * * & N# R + X! & H Q H N G SQ N I + * G R % J _ _ # $ * I ’( G SQ N I + * G R \ H R N * & ’N *> J ( _ _ # $ * K I * T N Q N I + * G R \ H R N * & ’N *= ( J ( _ _ # $ * * T N Q N I + * G R \ H R N * & ’N *B ] J ( _ _ # $ * I R * T N Q N I + * G R \ H R N * & ’N *= @ J ( _ $ * * H * T N Q N I + * G R J * H S IH & * L I [ % ) ) 构造体描述 K & R Z G N H R N T & H& N + * ^ H & * L I [ G Q) % ( _ _ # $ * G S K + Q Q N I + * G R \ H R N * & = (I * P S N *’ !!Q J ] J _ _ # $ * Q G S K + Q =( Q N I + * G R \ H R N * & ’N *B J ] J _ _ # $ * Q G S K + Q #( Q N I + * G R \ H R N * & ’N *> J _ J _ _ # $ * Q G S K + Q =( Q N I + * G R \ H R N * & ’N *> J _ J _ _ # $ * Q G S K + Q #! Q #( Q N I + * G R \ H R N * & ’N *= J ] J M H G S J # $ ) ) ) 列扫描信号产生单元 * R + X & * R H Q Q % * \ K & G K M + H] E ’( G S N H H & J M H G S J # $ G ^ R + X ‘ H \ H S N K S IR + Xa ‘ = ‘ N Z H S 万方数据 # $ G ^ & H Q H N a ‘ = ‘ N Z H S

图 B! 行驱动控制!列驱动控制 !!!!!!!!!!!!! 图 (! 系统结构图 #" #!)4D 1 语言实现

& ’ 本汉字显示系统用通用硬件描述语言 )4D 1 编程 =!( ! Z Y [ Q " \ Z I源 程 序 的 构 造 体 由 ( 个 进 程 组 成! 分别为行驱动进程 % 列驱动进程 % 计数器进程及连接进程 ! 部分程序清单如下 (

( )曾繁泰 " 清华大学出版社 % = 7 D $ 工程概论 ( V) "北京 ! # ’ ’ #年" ( )徐志军 " * 电子工业出版社 % # : C 1 D 2 C <$ 的开发与应用 ( V) "北京 ! # ’ ’ #年" ( )赵雅兴 " 设计与应用 ( 天津大学出版社 % B 2 C <$ 原理 + V) "天津 ! = F F F年" ( )王毅平 ")4D 北京 ! 人民邮电出版社 % ( 1 编程与仿真 ( V) " # ’ ’ ’年"

% & ’ (( ) * + , ) + -. & / * 0 -0 & 12 3 ) 0 ’1 *4 5 + )

c 4$0< U G S d + G S J J

# % % $ 7 + H R N & G RD H K & N H L H S N : * + + H H* ^5 G ‘ K S$ H & * N H R Z S G R K + 5 G ‘ K S> = ’ ’ > >% R Z G S K % J

源程序封装模块见图 @’ $! 结束语 该系统设计简单 % 自运行以来工作 正 常 % 性 能 稳 定% 显 示 可 靠’ 涵 盖 汉 字 显 示 系 统 的 7 D $ 实验仪已 完成课程设计实践训练两届 % 效果良好 % 在训练过程中 % 也进行 了一 些改 进 % 例 如! 行列驱动将三极管换为 芯片 % 使得程序更简单 ’ 在实际应用中 % 采用 $ + N H & K 公司 V$5 > ’ ’ ’ 3 系列 器件 制作万 年历 % 2 1 7 5 = ’ W系 列器件制作银行利率表等 % 运行可靠 % 修 改 方 便% 只 须 在 线 编 程 即 可’ 该 系 统 既 可 以 作 为 7 D $ 课程的应 也可以用作广告设计 ’ 用设计实践训练 % 参 考 文 献

图 @! 源程序封装模块

M H G S J # $ G ^ R + X ‘ H \ H S N K S IR + Xa ‘ = ‘ N Z H S # $ N Z H S #a= G ^ ] #! a’" ] # $ H + Q G ^ N Z H S #a’ ] #! a] #b=" ] H + Q H a] #b=" #! ] " H S I G ^ " H S I G ^ _ _ _ # $ " Q #% aR * S \ Q N I + * G R \ H R N * & #% # ] J ] Q #% a] Q #" " H S I% & * R H Q Q

!" #!!!!!!!!!!!!!!! !!!! 陕西科技大学学报 !!!!!!!!!!!!!!!!!!$ & " # ’ ’ ( % -./ 0$ 123 4$$0 5 6.0 6 ) 7 / 3 6 8 923 : 6 7 0 : 7;8 7 :401 < 9!!!!! ! ) * + " # # !!!!!!, = ’ >!

摘!要! 介绍了 )4D 并结合实例介绍了用 2 1 语言编程和 = E#= E 点 阵 的 基 本 概 念" C <$ 实 现汉字显示的设计思路和设计要点 " 给出了 = 在实际运行 E#= E 点阵的 )4D 1 语言描述方法 " 时状态稳定 # 良好 $ 关键词 ! 点阵模块 % 汉字显示 2 C <$% )4D 1 语言 % 中图分类号 ! 80 ( F #!!! 文献标识码 ! $ !! 引言 当今 # 数字系统的设计可以直接面向用户的需求 # 根据 系统功 能的 要 求 # 从上到下逐层完成相应的描 =’ 述% 综合 % 优化 % 仿真与验证 # 直到生成器件 & (而 2 " # 现场 可编程 门 C <$ 2 G H + IC & * & K LL K M + H< K N H$ & & K J O 以设计灵活及速度快的特点 # 在数字专用集成电路的设计中得到了广泛应用 ( 本文介绍的汉字显示 阵列 $ 系统将 = 采用 )4D # 硬件描 述 E#= E 点阵与 2 C <$ 巧妙结合 # 1" )4 3 6 :4 K & I P K & HD H Q R & G N G * S1 K S T K H % J J (’ 语言 $ 进行功能描述 & # 在作者所开发 的 7 实 验 仪 上 调 试 成 功 # 该 汉 字 显 示 系 统 在 实 际 应 用 中 得到了 D $ 检验 # 效果十分理想 ( "! 点阵模块说明 此设计采用 ( 块 A#A 的点阵块组成 = E#= E 的点阵显示模块 ( =" =!A#A 点阵块工作原理 如图 = 所示 (A#A 点阵块工作 方 式 ) 当: U 端 加 正 电 压# : -V 端 接 地 时 发 光 二 管 点 亮 (例 如 # -V A 接地且 U 第一行亮 ( 同理 # 当: 第 二 行 亮( =!U A 分别接高电平时 # -V > 接地 # U =!U A 分别 接高 电平时 # 依此类推 ( 当 U 分别让 : 第一列亮 ( 其它列依此类推 ( @ 端加高电平时 # -V =!: -V A 接地 # =" #!= E#= E 点阵模块 用 ( 块 A#A 的点阵块组成 = 连接关系如 图 # 所 示 (U E#= E 的点阵模块显示汉字 # ’!U = @ 成为点 阵 块的行线 # : -V ’!: -V = @ 形成点阵块的列线 (

=" (! 行列控制 行列控制电路如图 B 所示 " 由 2 当某一位有输出# 高 电 平$ 时! 三极 C <$ 发 来 的 数 据 接 至 3 6 C = E 上! 管导通 ! U5 端就会输出信号 " 由2 经> 汉字 C <$ 输出计数值到 3 6 C (! ( 1 3 = @ ( 译码由 > ( 1 3 ’ ( 反向后由 . 1 0 # A ’ B 驱动点阵的列线 ! 的显示亮度由行线的驱动电流 % 列线的驱动电流 % 列线的扫描频率共同决定 ! 只要选择合适的参数 ! 点阵显 示就可以达到设计的要求 " #!)4D 1 语言实现 #" =! 汉字显示系统的组成 用2 通过对 2 C <$ 实现汉字显示的硬件系统如图 ( 所 示 "= E#= E点阵与 2 C <$ 结 合 ! C <$ 芯 片 的 编程把存在 7 中的字库读出来 ! 并扫描到 的 点阵模块上显示 " 由 产 C / -V = E#= E 1 7 D 2 C <$ 生控制 信 号和地址信号 ! 并将 数据读 出缓存 ! 每 读 完一 个 字 的内 容 ! 由2 地 C <$ 统 一发 出 ": 1 W 接= X 4 Y 的时 钟 ! 址线由 2 数据线读入 2 读写信号 程 序 编 译 运 行 通 过% 下载后按自 C <$ 读出 ! C <$ 芯片 ! 7 低 电 平 有 效! 动分配的管脚进行正确连接 ! 字库中的字依次显示 "