基于FPGA静态和动态功耗解决方案介绍

基于FPGA+DSP架构的动态功耗管理设计

• 132•介绍了一种基于FPGA+DSP 为核心架构的信号处理态动态功耗管理硬件设计方案,通过一定的硬件架构设计,完成DSP 和FPGA 的低功耗设计及流程处理。

1 设计案例本文提供了一种基于DSP+FPGA 架构的低功耗处理方式。

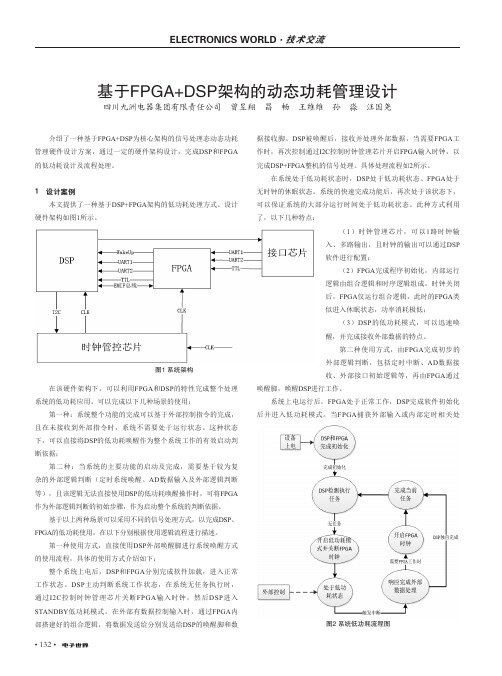

设计硬件架构如图1所示。

基于FPGA+DSP架构的动态功耗管理设计四川九洲电器集团有限责任公司 曾昱翔 昌 畅 王维维 孙 淼 汪国尧据接收脚。

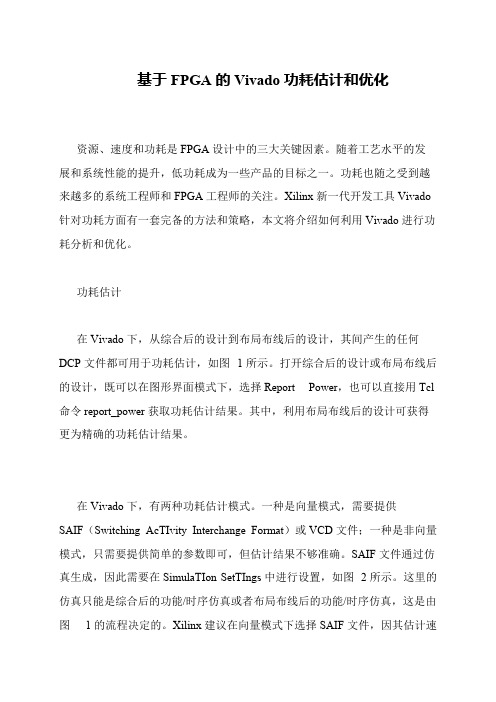

DSP 被唤醒后,接收并处理外部数据,当需要FPGA 工作时,再次控制通过I2C 控制时钟管理芯片开启FPGA 输入时钟,以完成DSP+FPGA 整机的信号处理。

具体处理流程如2所示。

在系统处于低功耗状态时,DSP 处于低功耗状态、FPGA 处于无时钟的休眠状态。

系统的快速完成功能后,再次处于该状态下,可以保证系统的大部分运行时间处于低功耗状态。

此种方式利用了,以下几种特点:图1 系统架构在该硬件架构下,可以利用FPGA 和DSP 的特性完成整个处理系统的低功耗应用。

可以完成以下几种场景的使用:第一种:系统整个功能的完成可以基于外部控制指令的完成,且在未接收到外部指令时,系统不需要处于运行状态。

这种状态下,可以直接将DSP 的低功耗唤醒作为整个系统工作的有效启动判断依据;第二种:当系统的主要功能的启动及完成,需要基于较为复杂的外部逻辑判断(定时系统唤醒、AD 数据输入及外部逻辑判断等),且该逻辑无法直接使用DSP 的低功耗唤醒操作时,可将FPGA 作为外部逻辑判断的初始步骤,作为启动整个系统的判断依据。

基于以上两种场景可以采用不同的信号处理方式,以完成DSP 、FPGA 的低功耗使用,在以下分别根据使用逻辑流程进行描述。

第一种使用方式,直接使用DSP 外部唤醒脚进行系统唤醒方式的使用流程,具体的使用方式介绍如下:整个系统上电后,DSP 和FPGA 分别完成软件加载,进入正常工作状态。

DSP 主动判断系统工作状态,在系统无任务执行时,通过I2C 控制时钟管理芯片关断FPGA 输入时钟,然后DSP 进入STANDBY 低功耗模式。

基于FPGA的Vivado功耗估计和优化

基于FPGA的Vivado功耗估计和优化

资源、速度和功耗是FPGA设计中的三大关键因素。

随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。

功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。

Xilinx新一代开发工具Vivado 针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

功耗估计

在Vivado下,从综合后的设计到布局布线后的设计,其间产生的任何DCP文件都可用于功耗估计,如图1所示。

打开综合后的设计或布局布线后的设计,既可以在图形界面模式下,选择Report Power,也可以直接用Tcl 命令report_power获取功耗估计结果。

其中,利用布局布线后的设计可获得更为精确的功耗估计结果。

在Vivado下,有两种功耗估计模式。

一种是向量模式,需要提供

SAIF(Switching AcTIvity Interchange Format)或VCD文件;一种是非向量模式,只需要提供简单的参数即可,但估计结果不够准确。

SAIF文件通过仿真生成,因此需要在SimulaTIon SetTIngs中进行设置,如图2所示。

这里的仿真只能是综合后的功能/时序仿真或者布局布线后的功能/时序仿真,这是由图1的流程决定的。

Xilinx建议在向量模式下选择SAIF文件,因其估计速。

电信应用基于FPGA的功耗优化解决方案

电信应用基于FPGA的功耗优化解决方案

引言针对中心机房功耗越来越大的问题,某些电信运营商制定了采购设备功耗每年降低20%的目标。

半导体是功耗问题的关键所在,其解决方法是重新设计芯片实施和交付方案,而最新一代FPGA 可以说是主要的推动力量。

通过采用基于40nm 的半导体最新制造工艺以及创新方法来优化这些复杂的器件,设计人员能够在单芯片中集成更多的功能。

这不但降低了总功耗,而且还可以降低后续工艺节点每一相应功能的功耗。

TPACK 便是能够充分发挥低功耗优势的公司之一,它是世界上最大的电信

系统供应商之一,可提供基于Altera Stratix IV FPGA 的运营商级以太网芯片解决方案。

Altera 高性能、低功耗技术与TPACK 高度集成复杂器件专业技术相

结合,将为系统供应商提供低功耗的芯片方案,供他们在此基础上持续提高带宽容量,并完成更智能的处理。

此外,TPACK 提供的芯片解决方案可以导入到最新的FPGA 中,进一步降

低功耗。

最终实现的系统不但大大降低了目前的功耗,而且在未来几年中,仍能满足继续降低功耗的要求。

解决功耗挑战

在前沿硅片技术中处理功耗问题涉及到多种方法,包括工艺、体系结构和设计优化等。

下面介绍开发功耗优化方案时采用的工艺优化、体系结构优化和设计优化方法。

对功耗进行优化的关键方法是可编程功耗技术,根据一定的设计要求,可选择性地接通或者关断每个逻辑阵列模块(LAB)、存储器和数字信号

处理(DSP)模块,从而降低功耗。

工艺优化

在针对功耗而优化Altera 40nm FPGA 的各种技术中,每一种都有各自的优缺。

fpga动态功耗

fpga动态功耗摘要:I.引言- 介绍FPGA 动态功耗的概念- 说明FPGA 动态功耗在现代电子设计中的重要性II.FPGA 动态功耗的定义与计算- 定义FPGA 动态功耗- 介绍计算FPGA 动态功耗的方法III.FPGA 动态功耗的影响因素- 列举影响FPGA 动态功耗的主要因素- 解释每个因素如何影响FPGA 的功耗IV.降低FPGA 动态功耗的方法- 介绍降低FPGA 动态功耗的主要方法- 分析这些方法的优缺点V.FPGA 动态功耗的未来发展趋势- 预测FPGA 动态功耗在未来可能会如何变化- 解释这些变化对电子设计的影响正文:I.引言FPGA(现场可编程门阵列)是一种集成电路,它可以通过编程来改变其逻辑功能。

FPGA 的动态功耗是一个重要的性能指标,因为它直接影响了FPGA的能效和运行成本。

在现代电子设计中,降低FPGA 动态功耗已经成为了一个迫切的问题。

II.FPGA 动态功耗的定义与计算FPGA 动态功耗是指在FPGA 工作时,由于其内部逻辑和布线的开关操作而产生的功耗。

动态功耗通常是通过计算FPGA 中所有逻辑门和布线的开关电流和电压来得到的。

III.FPGA 动态功耗的影响因素FPGA 动态功耗受许多因素影响,包括FPGA 的制程技术、逻辑门和布线的数量、工作频率、输入输出电平等等。

这些因素会影响FPGA 的功耗,因此设计人员需要考虑这些因素来优化FPGA 的功耗。

IV.降低FPGA 动态功耗的方法有许多方法可以降低FPGA 的动态功耗。

例如,可以优化FPGA 的逻辑设计,减少逻辑门和布线的数量;可以降低FPGA 的工作频率,减少开关电流;还可以使用低功耗技术,如睡眠模式和关断模式,来减少FPGA 的功耗。

V.FPGA 动态功耗的未来发展趋势随着制程技术的不断发展,FPGA 的动态功耗有望得到进一步降低。

FPGA的静态功耗分析与降低技术

FPGA的静态功耗分析与降低技术曹正州;曹靓【摘要】FPGA已经被广泛用于实现大规模的数字电路和系统,随着CMOS工艺发展到深亚微米,芯片的静态功耗已成为关键挑战之一.文章首先对FPGA的结构和静态功耗在FPGA中的分布进行了介绍.接下来提出了晶体管的漏电流模型,并且重点对FPGA中漏电流单元亚阈值漏电流和栅漏电流进行了详细的分析.最后根据FPGA的特点采用双阈值电压晶体管,关键路径上的晶体管采用低阈值电压栅的晶体管,非关键路径上的晶体管采用高阈值电压栅的晶体管,以此来降低芯片的静态功耗.【期刊名称】《电子与封装》【年(卷),期】2013(013)001【总页数】4页(P26-29)【关键词】FPGA;亚阈值漏电流;布线开关;双阈值电压【作者】曹正州;曹靓【作者单位】中国电子科技集团公司第58研究所,江苏无锡214035【正文语种】中文【中图分类】TN4021 引言FPGA因其可以降低成本和设计周期,已经被广泛用于实现大规模的数字电路和系统。

随着数字电路规模越来越大,时钟频率越来越高,也增加了FPGA的复杂性和技术难度。

在深亚微米技术下,随着导电沟道越来越短,静态功耗越来越大,FPGA面临许多新的挑战。

本文首先简单介绍了FPGA的结构和静态功耗在FPGA 中的分布,接下来介绍了晶体管漏电流的原理,提出了FPGA结构中基本单元漏电流的模型并进行了分析,最后提出降低静态功耗的解决措施。

2 FPGA的结构和静态功耗分布2.1 FPGA的结构和基本组成单元一个FPGA的结构如图1所示。

FPGA中含有规则灵活的可编程配置逻辑块,简称CLB,在它们周围是一圈可编程输入输出模块,简称IOB,两边有两列BRAM,位置是在CLB和IOB的中间。

CLB、BRAM和IOB之间是互联资源。

图1 FPGA结构FPGA的功能是基于查找表LUT来实现的,LUT是SRAM的阵列来实现真值表。

图2说明了2输入查找表的结构。

图2 2输入查找表结构FPGA的布线互联是基于SRAM控制的可编程开关实现的,有三种基本结构,如图3所示。

fpga动态功耗

fpga动态功耗FPGA动态功耗FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,广泛应用于数字电路设计和嵌入式系统中。

在FPGA的应用过程中,功耗一直是一个重要的考量因素。

本文将围绕FPGA动态功耗展开讨论,探讨FPGA动态功耗的原理、影响因素以及如何优化功耗。

一、FPGA动态功耗的原理FPGA的动态功耗是指在运行过程中由于信号的切换而产生的功耗。

当FPGA中的逻辑门发生状态变化时,会存在电流从Vdd到GND 的瞬态路径,这就导致了功耗的消耗。

动态功耗与逻辑门的切换频率、电压、电流等因素密切相关。

二、FPGA动态功耗的影响因素1. 逻辑门切换频率:逻辑门切换频率越高,FPGA的动态功耗就越大。

因此,在设计FPGA电路时,需要合理安排逻辑门的布局,减少逻辑门的切换频率。

2. 电压:FPGA的动态功耗与电压的平方成正比。

因此,降低FPGA的工作电压可以有效减少功耗。

但是,降低电压也会带来性能下降的问题,需要在功耗和性能之间做出权衡。

3. 电流:FPGA的动态功耗与电流成正比。

在设计FPGA电路时,可以通过减小电流的方式来降低功耗。

例如,采用低功耗的逻辑门、减小驱动强度等方法。

4. 温度:温度对FPGA的功耗有一定影响。

当FPGA工作在高温环境下时,会增加动态功耗。

因此,在布局和散热设计时,需要考虑合理的散热方案,保持FPGA在适宜的温度范围内运行。

三、优化FPGA动态功耗的方法1. 逻辑优化:合理设计电路的逻辑结构,减少逻辑门的切换频率,可以有效降低功耗。

例如,可以使用多级逻辑来代替单级逻辑,减少逻辑门的切换次数。

2. 时钟优化:合理设计时钟树结构,减少时钟分配的功耗。

例如,可以使用时钟缓冲器来降低时钟信号的功耗消耗。

3. 电压优化:选择合适的工作电压,降低功耗。

例如,可以采用动态电压调节技术,根据工作负载的变化动态调整工作电压。

4. 电流优化:选择低功耗的逻辑门,减小驱动强度,降低功耗。

fpga的io功耗 -回复

fpga的io功耗-回复FPGA(Field-Programmable Gate Array)是一种可重构硬件设备,可以自定义电路连接和功能。

在FPGA开发中,IO(Input/Output)功耗是一个重要的考虑因素。

IO功耗主要与IO接口的电气特性、访问速度、驱动能力以及IO的数量有关。

本文将详细介绍FPGA的IO功耗,并分步回答各个相关问题。

第一步:什么是IO功耗?IO功耗是指FPGA中用于连接外部器件的接口所消耗的电能。

这些接口可以是输入(I/O Input)或输出(I/O Output)引脚,用于连接到外部设备,如传感器、通信接口、外部存储器等。

第二步:IO功耗的主要来源是什么?IO功耗的主要来源包括两个方面:静态功耗和动态功耗。

1. 静态功耗:静态功耗是因为引脚电流保持在一定的值上而消耗的能量。

它主要与驱动能力有关,即引脚能够提供的电流和电压能力。

驱动能力越强,引脚的静态功耗就越高。

2. 动态功耗:动态功耗是因为输入输出的信号切换而产生的能耗。

当引脚发生电平变化时,会有瞬态电流产生,这会导致电能消耗。

动态功耗主要和IO接口的电气特性以及切换频率有关。

第三步:如何计算IO功耗?计算IO功耗需要考虑引脚电流、电压和切换频率。

1. 引脚电流:引脚电流是指引脚所能提供的电流能力。

它可以通过FPGA器件的手册或数据表来查找。

通常,IO接口会有特定的引脚电流规格,开发者需要确保引脚电流不超过规格要求,以避免超功率运行。

2. 引脚电压:引脚电压是指引脚所能提供或接收的电压范围。

同样,可以通过FPGA 器件的手册或数据表查找引脚电压规格。

开发者需要确保引脚电压在有效范围内,以保证正确的电气特性。

3. 切换频率:切换频率是指IO接口电平发生变化的频率。

通常,IO接口的切换频率越高,动态功耗就越高。

因此,在设计过程中,开发者需要平衡性能和功耗,选择合适的切换频率。

根据以上信息,可以使用以下公式计算IO功耗:IO功耗= 引脚电流×引脚电压×切换频率第四步:如何降低IO功耗?降低IO功耗对于提高整体系统的效率和延长电池续航时间具有重要意义。

Xilinx FPGA的功耗优化设计

Xilinx FPGA的功耗优化设计(1)对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA设计以及相应的PCB板在功率方面效率更高。

静态和动态功耗及其变化在90nm工艺时,电流泄漏问题对ASIC和FPGA都变得相当严重。

在65nm工艺下,这一问题更具挑战性。

为获得更高的晶体管性能,必须降低阈值电压,但同时也加大了电流泄漏。

Xilinx公司在降低电流泄漏方面做了许多努力,尽管如此,源于泄漏的静态功耗在最差和典型工艺条件下的变化仍然有2:1。

泄漏功耗受内核电压(VCCINT)的影响很大,大约与其立方成比例,哪怕VCCINT仅上升5%,静态功耗就会提高约15%。

最后,泄漏电流还与结(或芯片)温密切相关。

FPGA中静态功耗的其它来源是工作电路的直流电流,但在很大程度上,这部分电流随工艺和温度的变化不大。

例如I/O电源(如HSTL、SSTL和LVDS等I/O标准的端接电压)以及LVDS等电流驱动型I/O的直流电流。

有些FPGA模拟模块也带来静态功耗,但同样与工艺和温度的关系不大。

例如,Xilinx FPGA中用来控制时钟的数字时钟管理器(DCM);Xilinx Virtex-5 FPGA中的锁相环(PL L);以及Xilinx FPGA中用于输入和输出信息可编程延迟的单元IODELAY。

动态功耗是指FPGA内核或I/O的开关活动引起的功耗。

为计算动态功耗,必须知道开关晶体管和连线的数量、电容和开关频率。

FPGA中,晶体管在金属连线间实现逻辑和可编程互连。

电容则包括晶体管寄生电容和金属互连线电容。

动态功率的公式:PDYNAMIC=nCV2f,其中,n=开关结点的数量,C=电容,V=电压摆幅,f=开关频率。

更紧凑的逻辑封装(通过内部FPGA架构改变)可以减少开关晶体管的数量。

采用更小尺寸的晶体管可以缩短晶体管之间的连线长度,从而降低动态功率。

因此,Virtex-5 FPGA中的65nm晶体管栅极电容更小、互连线长度也更短。

基于FPGA的静态无功补偿装置(SVC)

路及外 壳设计和封 装。现场运行的反 馈 是 稳 定 性 差 ,阆 试 排 错 困 难 ,导 致

整 个 控 制器 的上 市 时 间延 长 。在上 海 聚 星 仪 器 的 协 助 下 我 们 尝 试 在 NI C mp c I  ̄ 台上 开 发 控 制 算 法 ,硬 o at O' R Z

『] 2 宋建波 基于DS P的S VC控制器研究[ ]西安理 工大学;0 6 D 2 0 年 『]扬晓萍 _ 3 孙晓娟 新型静止无功 发生器的控制方 研究 电机电 去

器 技 术 ,0 4 01 20年 期

『] 4 郑世林 锁相环自锁定技术的研究及应用 1 电子测量技术 0 7 20

集 成 F G 技 术 的 C mpcR O' 台 , P A o at I - I z

压 参 考 值 , “ 压 调 节 器 ” 会 根 据 测 电

参 考 文 献

f] 司广 新 , 新 刚 , 江 S 1 刘 李 VC; 网 型 风 电 场 运 行 性 能 的 影 响 分 析 q并 f1 网 与 清 洁 能 源 : 0 0 第 9 J电 21年 期

高 可 靠 的 F GA技 术 和 简 单 易 用 的 P lb I W 软 件 平 台 为 客 户 节 省 了大 量 aV E

开 发 时 间 ,模 拟 输 入 模 块 NI 2 5 90 、 NI 2 5 5 / T 高 速 双 向数 字 i o 9 1和 V T L /模 块 NI 4 1 9 0 、NI 4 3 9 0 出色 地 完成 了 从 数 据 采 集 到 脉 冲 控 制 的 全 过 程 ,使 这 套

m和 参 考 电 压 之 间 的 差 值 , 在 一 个 月 内完 成 了 全 数 字 控 制 系 统 的 量 电 压 v 发 布 计算 出 耍 保 持 母 线 电 压 恒 定 所 需 要 的

基于ISE设计提供低功耗FPGA解决方案

基于ISE设计提供低功耗FPGA解决方案

从公司推出二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字的优选平台。

今日,功耗日益成为FPGA供给商及其客户关注的问题。

降低FPGA功耗是降低封装和散热成本、提高器件牢靠性以及打开移动设备等新兴市场之门的关键。

Xilinx在提供低功耗FPGA解决计划方面较有阅历。

本文解释如何应用计算机辅助设计(CAD)技术,如Xilinx ISE(集成软件环境)9.2i版本软件使功能有效降低。

电路中的功耗由静态(漏电)功耗和动态功耗两部分组成。

动态功耗是由电路信号上的瞬变所致,由下式打算:式中Ci表示信号i的;fi为"开关率",表示信号i上的瞬变率;V是电源。

静态功耗是电路在静止、空闲状态下的功耗。

工艺尺寸缩小(如65纳米工艺)意味着更低的电源电压和更小的晶体管尺寸,致使导线长度缩短、电容量减小以及总动态功耗降低。

较小的工艺几何尺寸还意味着较短的晶体管沟道和较薄的栅极氧化层,致使静态功耗随着工艺尺寸缩小而增强。

FPGA的功耗

对于实现给定的规律电路而言,FPGA的可编程性和灵便性使其功耗效率比定制ASIC要低。

FPGA的配置电路和配置存储器要占用硅片面积,致使导线延伸和互连电容增强。

在FPGA中,预制金属导线段上附加的可编程布线开关产生互连,从而加重了信号产生的电容性负载。

FPGA中的动态功耗大部分消耗在可编程布线架构中。

同理,静态功耗与晶体管总宽度成正比。

FPGA的晶体管有相当一部分是互连架构,这

第1页共5页。

FPGA设计中的低功耗解决方案

研究开发

电脑知识与技术

FPGA设计中的低功耗解决方案

吴方明, 陈军宁, 柯导明, 丁峰 ( 安徽大学电子科学与技术学院, 安徽 合肥 230039)

Key words :discuss briefly on;Maya;cartoon making;process

1 引言

在动画制作行业中, 传统的二维动画越来越被三维动画所挤 压, 当然传统动画永远是不会被三维动画所取代的, 因为它们的 本质是相同的, 两者都是动画的一种表现形式, 三维动画技术只 是科技发展的产物, 只是表现的方式发生了改变。在三维动画行 业中, 用 Maya 来制作动画片已经成为一种潮流。

Low P ower Los s S olution In FP GA Des ign WU Fang- ming,CHEN Jun- ning,KE Dao- ming,DING Feng (School of Electronics,Anhui University,Hefei 230039,China) Abs tract:This article discussed in the FPGA design low power loss issue. Begin from the power loss production reason and the correlation formula, proposed the corresponding solution in view of the static state and the dynamic main power loss. Take Actel the eX series as well as the SX/ SX- A series component as an example, elaborated the component unique feature and the low power loss design skill. Key words :low power loss;FPGA

基于FPGA的静态无功补偿装置(SVC)

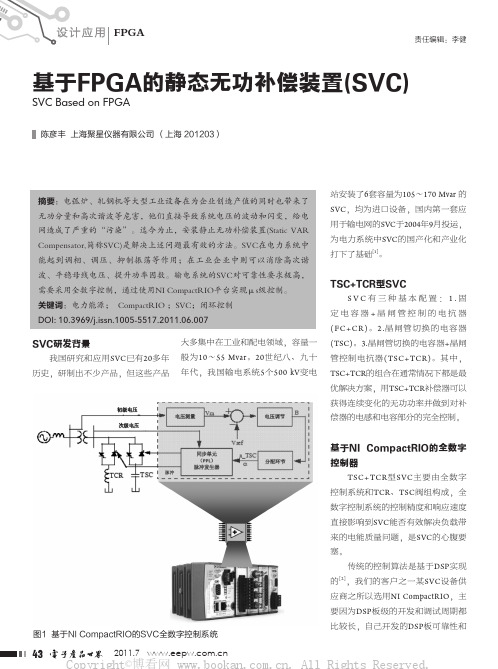

2011.7FPGA责任编辑:李健SVC研发背景我国研究和应用SVC 已有20多年历史,研制出不少产品,但这些产品基于FPGA的静态无功补偿装置(SVC)SVC Based on FPGA陈彦丰 上海聚星仪器有限公司 (上海 201203)摘要:电弧炉、轧钢机等大型工业设备在为企业创造产值的同时也带来了无功分量和高次谐波等危害,他们直接导致系统电压的波动和闪变,给电网造成了严重的“污染”。

迄今为止,安装静止无功补偿装置(Static VAR Compensator,简称SVC)是解决上述问题最有效的方法。

SVC在电力系统中能起到调相、调压、抑制振荡等作用;在工业企业中则可以消除高次谐波、平稳母线电压、提升功率因数。

输电系统的SVC对可靠性要求极高,需要采用全数字控制,通过使用NI CompactRIO平台实现µs级控制。

关键词:电力能源; CompactRIO ;SVC;闭环控制DOI: 10.3969/j.issn.1005-5517.2011.06.007大多集中在工业和配电领域,容量一般为10~55 Mvar 。

20世纪八、九十年代,我国输电系统5个500 kV 变电站安装了6套容量为105~170 Mvar 的SVC ,均为进口设备,国内第一套应用于输电网的SVC 于2004年9月投运,为电力系统中SVC 的国产化和产业化打下了基础[1]。

TSC+TCR型SVCS V C 有三种基本配置:1.固定电容器+晶闸管控制的电抗器(FC+CR)。

2.晶闸管切换的电容器(TSC)。

3.晶闸管切换的电容器+晶闸管控制电抗器(TSC+TCR)。

其中,TSC+TCR 的组合在通常情况下都是最优解决方案,用TSC+TCR 补偿器可以获得连续变化的无功功率并做到对补偿器的电感和电容部分的完全控制。

基于NI CompactRIO的全数字控制器TSC+TCR 型SVC 主要由全数字控制系统和TCR 、TSC 阀组构成,全数字控制系统的控制精度和响应速度直接影响到SVC 能否有效解决负载带来的电能质量问题,是SVC 的心腹要塞。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA静态和动态功耗解决方案介绍

传统上,数字逻辑并不耗费大量静态功耗,但随着工艺节点的不断精微,这一情况在发生显著变化。

现在,随着工艺尺度的不断缩微,数字逻辑中的漏电流成为FPGA 的主要挑战。

因在65nm工艺节点静态功耗会显著增加,所以,若不采取降耗措施,则功耗将成为一个关键问题。

因各种原因导致的漏电流的增加,静态功耗将会显著增加(图1)。

功耗由静态功耗和动态功耗组成。

静态功耗是FPGA在被编程目标文件(.pof)编程时、但时钟不工作的状态下所需的功耗。

数字和模拟逻辑都消耗静态功耗。

在模拟系统中,静态功耗主要包括由其接口模拟电路的静态电流决定的功耗(图2和表)。

动态功耗是当器件工作时增加的功耗,它由切换信号及容性负载的充放电引起。

影响动态功耗的主要变量是电容充电、工作电压和时钟频率(图3)。

借助工艺节点的不断缩微带来的减小电容和降低电压的好处,动态功耗的降低遵从摩尔定律。

挑战在于,伴随每一工艺节点的缩微以及最高时钟频率的增加所引发的问题。

虽然就相同的电路来说,其功耗随每一工艺节点的缩微在一直下降,但同时FPGA的容量在翻番,且最高时钟频率也在不断增加。

FPGA架构

在架构、工艺技术和电路技术方面的进步有助于解决这些功耗挑战。

Altera的Stratix III FPGA就是这样一种产品。

Altera的可编程电源技术(Programmable Power Technology)有助于降低高端FPGA的功耗。

传统上,所有高性能的FPGA都由高性能的建构实现,其中,每一逻辑单元(LE)都以大的漏电功耗为代价来提供最佳性能。

可编程电源技术利用如下事实:设计中的许多电路具有剩余能力,所以并不需要最高性能的逻辑。

图4显示的是一个典型的剩余能力柱状图,其中,大多路径(左侧)具有剩余,。