基于FPGA的DDS设计

基于FPGA的简易DDS信号源设计

基于FPGA的简易DDS信号源设计一、设计方案背景信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。

函数信号发生器的实现方法通常是采用分立元件或单片专用集成芯片,但其频率不高,稳定性较差,且不易调试,开发和使用上都受到较大限制。

随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。

本设计用大赛要求的赛灵思芯片,研究基于FPGA的DDS信号发生器设计,实现了满足预定指标的多波形输出。

二、设计方案论证2.1 总体方案论证与比较方案一:采用模拟锁相环实现模拟锁相环技术是一项比较成熟的技术。

应用模拟锁相环,可将基准频率倍频,或分频得到所需的频率,且调节精度可以做到相当高、稳定性也比较好。

但模拟锁相环模拟电路复杂,不易调节,成本较高,并且频率调节不便且调节范围小,输出波形的毛刺较多,得不到满意的效果。

方案二:采用直接数字频率合成,用单片机作为核心控制部件,能达到较高的要求,实现各种波形输出,但受限于运算位数和运算速度,产生的波形往往达不到满意效果,并且频率可调范围小,很难得到较高频率,并且单片机的引脚少,存储容量少,这就导致了外围电路复杂。

方案三:采用直接数字频率合成,用FPGA器件作为核心控制部件,精度高稳定性好,得到波形平滑,特别是由于FPGA的高速度,能实现较高频率的波形。

控制上更方便,可得到较宽频率范围的波形输出,步进小,外围电路简单易实现。

因此采用方案三。

2.2 DDS模块方案论证方案一:采用高性能DDS 单片电路的解决方案随着微电子技术的飞速发展,目前高超性能优良的DDS 产品不断推出,主要有Qualcomm 、AD、Sciteg 和Stanford 等公司单片电路(monolithic)。

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器的设计和实现引言在电子领域中,正弦信号是一种重要的基础信号,被广泛应用于通信、音频、视频等各个领域。

而DDS(Direct Digital Synthesis)直接数字合成技术则是一种通过数字方式生成高精度、高稳定性的正弦波信号的方法。

本文将详细介绍基于FPGA的DDS正弦信号发生器的设计和实现。

设计目标本次设计旨在实现一个可配置频率范围广泛且精度高的DDS正弦信号发生器。

具体设计目标如下: 1. 实现频率范围可调节,覆盖从几Hz到数十MHz; 2. 提供高精度的频率控制,满足特定应用场景对频率稳定性和相位精度的要求; 3. 支持模数转换器(DAC)输出,并能够通过外部接口控制输出幅值; 4. 使用FPGA作为主要硬件平台,以满足高速计算和灵活配置需求。

系统架构基于FPGA的DDS正弦信号发生器主要由以下几个部分组成: 1. 数字控制模块(Digital Control Module):负责接收外部输入的频率、相位和幅值等参数,并将其转换为对DDS核心模块的控制信号; 2. DDS核心模块(DDS Core Module):根据接收到的控制信号,通过数学运算生成正弦波形的离散采样值; 3. 数字模拟转换模块(Digital-to-Analog Converter, DAC):将DDS核心模块输出的数字采样值转换为模拟电压信号; 4. 输出放大器(Amplifier):用于放大DAC输出的电压信号,并通过外部接口提供可调节幅值的正弦波输出。

DDS核心模块设计DDS核心模块是整个系统中最关键的部分,它负责根据输入参数生成正弦波的离散采样值。

下面是DDS核心模块设计中需要考虑的几个关键要素:相位累加器相位累加器是DDS核心模块中最基础且重要的组件之一。

它根据输入的频率和时钟信号,在每个时钟周期内累加相位增量,从而实现相位连续变化。

相位累加器可以使用一个定点数或浮点数寄存器来表示,并通过固定步长进行相位递增。

基于FPGA的DDS设计

基于FPGA的DDS设计初始频率设置为7.3682307MHz,系统频率为100MHz,根据DDS输出频率公式能计算出相位累加字:其中f为DDS输出频率;fclk为DDS系统频率;N为相位累加器的位数;DATA为相位累加器的累加值。

要得到7.3682307MHz的输出频率,相位累加值DATA=(100101101110011010111111110101101101111011100)2FPGA采用Xilinx Spartan3E XC3S500E,IP核+VerilogHDL+Sch编程。

下图为整个FPGA的原理框图:DCM_100MHz其中DCM_100MHz用了Spartan3E里面的DCM(时钟管理单元),由于输入的时钟为有正负的正弦波(100MHz 幅值5V 峰峰10V的正弦信号),所以经过DCM后,能得到一个很好的方波。

输出100MHz给DA作为DA的时钟,其中还经过一个BUFG,目的是使ROM的正弦数据输出稳定后,时钟才到来,DA才能读入数字值,这可以参考AD9744的Datasheet其中ts至少为2.0ns,如果少于2.0ns或时钟和DA数据同时甚至提前到达的话,DA 输出的模拟值会出错。

所以要加一个BUFG,但BUFG延时不太确定,.....(方面的我还不懂L)MCU_FPGA51单片机通过串口接受PC机给出的DATA(相位累加值),再通过与FPGA的通信,告诉FPGA相位累加模块(Accumulator)累加值。

MCU_FPGA所做的工作是把收到的数据出入模块内的ROM里,使得改变模块里的ROM地址,就能改变输出的累加值。

FPGA_MCU通信的时序为:DIN:48位累加值串行输入CLK_WR:输入写信号时钟,DIN的数据稳定后,CLK_WR上升沿写入FPGA内部的寄存器,寄存器的数据移位。

DIN_PRO:写保护,DIN_PRO=0时,模块内ROM的输出随地址变化而变化;DIN_PRO=1,模块内ROM的输出锁存,输出保持DIN_PRO=0时ROM地址所对应的ROM 值。

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

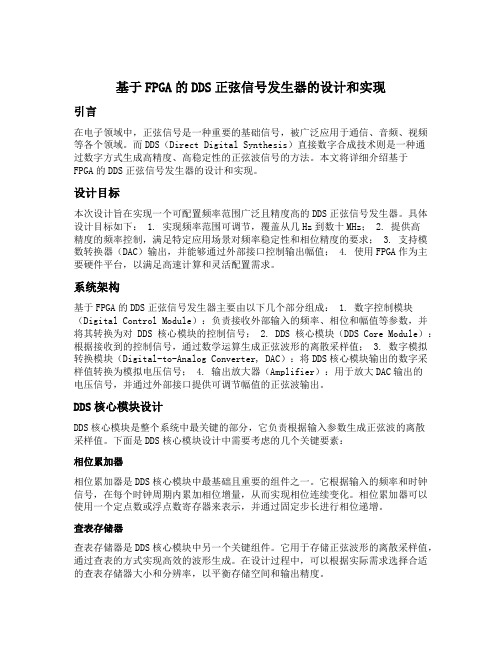

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

基于fpga的dds正弦信号发生器的设计和实现

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器可以使用数字信号处理技术实现。

下面是一个基本的设计和实现步骤:

1. 确定系统需求:首先,确定所需的输出信号频率范围、分辨率和采样率等系统参数。

这些参数可以根据实际应用来确定。

2. 设计正弦表:根据系统需求,设计一个包含所需频率范围内所有可能的正弦波的正弦表。

可以使用固定小数点表示法来表示正弦表中的采样值。

3. 设计相位累加器:使用一个32位计数器作为相位累加器,其计数速度由所需的输出信号频率和FPGA时钟频率决定。

每个时钟周期,计数器值自动增加到下一个相位值。

4. 选择相位值:使用相位累加器的值在正弦表中查找对应的相位值,并将其作为输出信号的采样值。

5. 数字输出:将采样值经过DAC(数字模拟转换器)转换为模拟信号,并将其输出。

6. 配置FPGA:将设计好的数字电路加载到FPGA芯片中,并配置FPGA内部的寄存器、时钟和IO管脚等。

7. 测试和调试:对设计好的系统进行测试和调试,确保输出信号的频率、精确度和稳定性符合要求。

这是一个基本的设计和实现步骤,具体的实现方法和细节可能因FPGA型号、工具和应用需求而异。

在实际应用中,还可以加入滤波器、幅度控制、相位调制等功能以满足更多需求。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着数字信号处理(DSP)技术的发展,直接数字频率合成器(DDS)逐渐取代了传统的频率合成器,成为一种高性能的信号发生器。

DDS信号发生器通过数字信号直接产生模拟信号,具有频率精度高、可编程性强和快速调频等优点。

本文将通过FPGA实现DDS信号发生器的设计。

首先,我们需要了解DDS信号发生器的基本原理。

DDS信号发生器的核心是相位累加器、查找表和数模转换器(DAC)。

通过累加器产生相位累积,将相位累积的结果通过查找表得到对应的振幅值,并经过数模转换器输出模拟信号。

1.确定需要生成的信号的参数,包括输出频率、相位步进精度、振幅等。

根据这些参数,计算累加器的增量值,即每个时钟周期累加器需要累加的值。

2.在FPGA中设计相位累加器。

相位累加器的宽度取决于相位步进精度,一般为32位或64位。

通过在每个时钟周期加上增量值,实现相位的累加。

3.设计查找表。

查找表的大小取决于数字信号的分辨率,一般为2^N 位。

通过输入相位值查找对应的振幅值。

4.设计数模转换器(DAC)。

通过DAC将数字信号转换为模拟信号输出。

5.在FPGA中实现控制逻辑,包括控制相位累加器和查找表的读写操作,使其按照设定的参数进行相位累加和振幅输出。

6.将设计好的FPGA模块进行综合、布局和时序约束,生成比特流文件。

通过以上步骤,基于FPGA的DDS信号发生器的设计就完成了。

设计好的FPGA模块可以实现高精度、高稳定性的信号发生器,广泛应用于通信、雷达、医疗设备等领域。

需要注意的是,在设计过程中需要考虑到FPGA的资源限制,包括LUT资源的利用、频率分辨率和输出频率的限制等。

此外,还可以通过增加相位累积周期、使用多路查找表和多路DAC等方法进一步优化设计。

综上所述,基于FPGA的DDS信号发生器设计是一个较为复杂的过程,需要对DDS原理有深入的理解,并结合FPGA的特点进行设计。

通过合理的设计和优化,可以实现高性能的DDS信号发生器。

基于FPGA的两种DDS实现

基于FPGA的两种DDS实现直接数字频率合成(Direct Digital Synthesis,DDS)是一种基于数字信号处理的频率合成方法,通过将一个连续的幅度和相位可调的数字信号与一个时钟信号相乘,可以产生高精度的频率信号。

在FPGA(Field Programmable Gate Array)中,DDS可以通过数字逻辑实现。

本文将介绍两种基于FPGA的DDS实现方法。

LUT是FPGA中常用的存储组件,可以用于存储预先生成的数字信号样本。

基于LUT的DDS实现方法是将一个固定的正弦波样本表存储在LUT 中,然后通过改变LUT的读指针位置来产生不同频率的正弦波信号。

具体实现步骤如下:1)根据需要生成的信号频率,计算出每一个时钟周期对应的读指针步进量,即相位步进量。

2)初始化读指针位置为0,以时钟信号为基准,每一个时钟周期将读指针位置加上相位步进量。

3)将读指针位置作为索引,从LUT中读取相应的正弦波样本值。

4)将读取到的正弦波样本值输出为DDS的输出信号。

基于LUT的DDS实现有以下优点:-简单易于实现,适合低频率应用。

-输出信号的频率可精确控制,具有较高的频率精度。

-可以通过修改LUT中的正弦波表,实现不同幅度和相位的输出信号。

另一种常见的DDS实现方法是基于相位累加器。

相位累加器是一个用于存储和计算相位信息的寄存器,通过不断累加相位步进量来产生不同频率的输出信号。

具体实现步骤如下:1)根据需要生成的信号频率,计算出每一个时钟周期对应的相位步进量。

2)初始化相位累加器为0,在每一个时钟周期将相位步进量加到累加器中。

3)将相位累加器的高位作为正弦波LUT的读指针,将读取到的正弦波样本值输出为DDS的输出信号。

基于相位累加器的DDS实现有以下优点:-输出信号的频率可精确控制,具有较高的频率精度。

-可以通过修改相位步进量,实现不同频率的输出信号。

-相位累加器可以很容易地实现相位调制和频率调制等功能,具有较高的灵活性。

基于FPGA的DDS设计报告

DDS设计报告摘要:DDS信号发生器能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。

随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。

本文研究了基于FPGA的DDS信号发生器设计,实现了满足预定指标的多波形输出。

同时采用STM32来进行控制频率,幅度的输入以及对波形类型,频率,幅度值进行显示,从而很好地实现了人机交界。

关键字:DDS信号发生器FPGA STM32 频率幅度值目录1.系统设计 (3)1.1设计要求 (3)1.1.1任务 (3)1.1.2要求 (3)1.1.3说明 (3)1.2总体设计方案……………………………………………………………………………………………………..1.2.1设计思路…………………………………………………………………………………………………1.2.2方案论证与比较……………………………………………………………………………………….1.2.3系统组成…………………………………………………………………………………………………..2.单元硬件电路设计………………………………………………………………………………………………………2.1电路的设计…………………………………………………………………………………………………….2.2……………………………………………………………………………………………………..2.3………………………………………………………………………………………………………2.4……………………………………………………………………………………………………….3.软件设计……………………………………………………………………………………………………………………..3.1软件设计与硬件设计的关系…………………………………………………………………………………3.2部分程序设计…………………………………………………………………………………………………..3.3部分程序设计………………………………………………………………………………………………….4.系统测试…………………………………………………………………………………………………………………………4.1测试使用的仪器…………………………………………………………………………………………………….4.2指标测试和测试结果…………………………………………………………………………………………….4.3结果分析………………………………………………………………………………………………………………..5.结论………………………………………………………………………………………………………………………………. 参考文献………………………………………………………………………………………………………………………………附录1 主要元器件清单……………………………………………………………………………………………………附录2 电路原理图及印刷板图……………………………………………………………………………………….附录3 程序清单………………………………………………………………………………………………………………..1.系统设计1.1设计要求1.1.1设计任务设计并制作一个波形发生器,该波形发生器能产生正弦波、方波、三角波和由用户编辑的特定波形形状。

基于FPGA的DDS设计

摘 要 : 用现 场 可编 程 门 阵 列 ( P 利 F GA) 计 并 实 现 直 接 数 字 频 率 合 成 器 ( 设 DDS) 结合 DDS的 结 构 和 原 理 , 出 系统 设 。 给

计 方 法 , 推 导 得 到 参 考 频 率 与输 出频 率 间的 关 系 、D S具 有 高稳 定度 . 并 D 高分 辨 率 和 高 转换 速 度 , 时利 用 A tr 公 同 l a e

Ab ta tThsd sg SSf l lga sr c : i e in U ( edp’ rmma l aeary ( P 'i o beg t ra F GA)o raiedrc ii lsnh szr ( t el i tdgt y teies DDS .o z e a )C mmbnn iig

De i n o i e tdi ia y t sz r b s d o sg fd r c g t ls n he ie a e n FPGA

L O i— a U Jeb n.CHE NG a gwe Gu n — i

(col ’lc oi I om t nE gneig X ’ k eh o g a U i rt, i帆 7 0 3 , hn ) S ho Ee t n n r ai nier , i( cn l i l n esy X ’ r c f o n IT l oc v i 10 2 C ia

te DD S sr ct c a d p n i l , se e i n meh d r ie a d t e r l t n h p ewe n r f r n e fe u n y a d h S’ [ lt r n r cp es t m d s t o s a e gv n, n h e ai s i sb t e e e e c r q e c n t l i y g o o t u rq Cly a' d d c d D a ih sa i t hg e ou in a d h g o v r in s e d, sn tr o o t u p tfe U I l e u e . DS h s a h g tb l y, ih r s lt n i h c n e so p e u i g Al a Nis s f c e i o e — C r e st t i ly h u p t r q e c , ih i v r o v n e ta d h sa h g e e r e o tg a in O e s t i al d s a s t eo t u e u n y wh c s e y c n e in , n a i h rd g e f n e r t . p d p f i o

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着现代科技的不断发展,数字信号发生器(DDS)已成为各种电子设备中常用的一种功能模块。

使用DDS技术可以生成高质量、高稳定性的各种频率和波形的信号。

而FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,具有高集成度、高速度和灵活性等优势,逐渐成为了实现DDS信号发生器的主要选择之一一、DDS技术概述DDS(Direct Digital Synthesis)技术是一种基于数字直接合成的方法,通过计算机算法精确地合成期望的波形。

它的工作原理是将时钟信号分频得到一系列的离散相位值,再通过查表和插值的方法得到对应的幅值,最后通过一个DAC(Digital to Analog Converter)将数字信号转换为模拟信号输出。

二、基于FPGA的DDS信号发生器设计步骤1.系统架构设计根据DDS信号发生器的要求,确定所需的系统架构。

一般包括时钟模块、相位累加器、查找表、插值器、DAC和控制逻辑等模块。

2.时钟模块使用FPGA内部的资源或外部时钟源生成所需的系统时钟信号。

可以通过时钟分频和PLL(Phase-Locked Loop)锁相环技术来实现对系统时钟的精确控制。

3.相位累加器利用FPGA的寄存器或分频模块实现相位累加功能。

通过周期性地累加相位增量,可以得到DDS信号的相位。

4.查找表利用FPGA内部的RAM(Random Access Memory)存储相位对应的幅值。

根据相位的大小来查找对应的幅值,存储在RAM中。

5.插值器可以通过线性插值或差值的方法对相位查找表的输出进行插值,以提高输出信号的精度和稳定性。

6.DAC将插值器输出的数字信号转换为模拟信号,通过FPGA的IO端口或专用的DAC芯片输出到外部电路。

7.控制逻辑设计合适的控制逻辑,可以通过外部接口或FPGA内部的控制模块来控制DDS信号发生器的频率、幅值、相位偏移等参数。

基于FPGA的DDS信号源设计培训

基于FPGA的DDS信号源设计培训基于FPGA的DDS信号源设计是一种使用数字直接合成技术(DDS)在可编程逻辑器件(FPGA)上实现信号源的方法。

DDS是一种通过数字计算方式生成任意频率和相位的信号的技术。

在传统信号源设计中,通常使用锁相环(PLL)或震荡器电路来生成特定频率的信号。

而DDS信号源通过数字计算的方式,可以实现更高的频率分辨率和频率稳定性。

在基于FPGA的DDS信号源设计中,首先需要将输入的参考时钟进行数字化。

通常使用的是外部时钟源,如晶振或GPS同步时钟等。

然后,通过时钟分频和相位累加器等数字逻辑电路,将参考时钟转换为所需的频率和相位。

接下来,使用数字幅度调制电路对信号进行幅度调制,以实现所需的信号形式,如正弦波、方波、三角波等。

FPGA作为可编程逻辑器件,具有高度灵活性和可重配置性。

它可以通过编程方式实现不同的信号生成算法和信号处理功能。

通过使用FPGA实现DDS信号源,可以满足不同应用领域中对信号源的复杂要求,如通信系统、雷达系统、医疗设备、音频设备等。

在基于FPGA的DDS信号源设计过程中,需要考虑以下几个关键问题:1.时钟频率选择:选择合适的时钟频率对于实现高分辨率和频率稳定性至关重要。

较高的时钟频率可以提供更高的频率分辨率,但也会增加硬件复杂度和功耗。

较低的时钟频率可能导致频率稳定性下降。

因此,需要根据具体应用需求进行权衡和选择。

2.相位累加器设计:相位累加器是DDS信号源的核心部件,负责将参考时钟转换为所需的相位。

设计相位累加器时需要考虑相位分辨率和相位误差。

相位分辨率取决于相位累加器的位宽,而相位误差受到时钟抖动和积累误差等因素的影响。

因此,需要合理设计相位累加器的位宽和时钟抖动控制电路。

3.数字幅度调制:数字幅度调制(AM)可以实现信号的幅度调制,例如调制成正弦波、方波等。

常用的数字幅度调制技术包括加权输出和查找表法。

加权输出法通过在幅度控制寄存器中存储不同幅度值,并按照权重进行输出。

以FPGA为基础的DDS控制电路设计方案详解

以FPGA为基础的DDS控制电路设计方案详解FPGA是一种可编程逻辑设备,可以实现数字电路的设计和控制。

FPGA可用于设计频率合成器,其中直接数字频率合成(DDS)是一种常见的应用。

DDS是一种用于产生多种频率信号的技术,它使用数字控制寄存器来生成高精度的数字频率控制。

以下是以FPGA为基础的DDS控制电路设计方案的详细解释:1. 整体架构设计:FPGA DDS控制电路的整体架构包括一个相位累加器(phase accumulator)、一个频率控制字寄存器(frequency control word register)和一个查找表(look-up table)。

相位累加器用于生成相位控制信号,频率控制字寄存器用于存储频率控制信息,查找表用于将相位信息转换为实际的输出信号。

2.相位累加器设计:相位累加器是DDS控制电路的核心部分,它通过累加相位控制字来生成输出信号。

相位累加器通常由一个计数器和一个累加器组成。

计数器用于产生一个固定的时钟信号,累加器用于累加相位控制字。

相位控制字决定了相位累加器的累加速度,从而决定了输出信号的频率。

相位累加器的输出信号将作为查找表的输入信号。

3.频率控制字寄存器设计:频率控制字寄存器用于存储频率控制信息。

频率控制信息可以来自外部输入或来自FPGA内部的控制逻辑,例如通过串行接口输入到FPGA中。

频率控制字寄存器将频率控制信息转换为相位控制字,并将相位控制字输入到相位累加器中。

4.查找表设计:查找表用于将相位信息转换为实际的输出信号。

查找表是一个存储器单元,其中包含了预先计算好的正弦波形数据。

查找表根据输入的相位信息,从存储器中读取对应的正弦波形数据,并将数据作为输出信号输出。

查找表的大小取决于输出信号的需求精度,较大的查找表会提供更高的输出精度。

5.时钟和状态控制:DDS控制电路通常需要一个高精度的时钟信号来驱动相位累加器和频率控制字寄存器。

时钟信号的频率和相位可以通过FPGA内部的时钟控制器进行调整。

基于FPGA的DDS设计

摘要:介绍了直接数字频率的工作原理和结构合成器。

本文选择查找表的技术,因为它有很多设计dds优势,如消费较少的硬件资源,结构简单,输出只有小延迟等等等等。

作为一个结果,信号发生器可以产生许多波形具有良好的稳定性和高频率分辨率。

最后,测试表明,三角信号频率的输出波形是大于1mhz和最高正弦波频率为30mhz,峰峰值在~ 4v电压连续可调范围。

研究结果将为该研究提供理论指导。

0 引言随着微电子技术的迅速发展,直接数字频率合成器技术外观。

该技术已被广泛用于通信系统,因为它比传统的频率合成器技术在相对带宽上的优势,调制功能,相位连续性,相位噪声,任意波形输出,分辨率高,集成方面。

许多的任意波形发生器是基于专用dds最近。

然而,该芯片已固化,使灵活性差。

因此,本文设计基于fpga任意波形可根据完整的dds 系统设计采用altera公司的cyclone ii系列器件[1-5] dds原理。

1 dds的工作原理及结构dds系统的核心是n位相位累加器,它由n位全加器和n位累加器登记。

该寄存器将在一个累积的时间输出相位数据馈送到n位全加器和加法器的输入相位控制字k时,每个时钟脉冲触发一次,然后将蓄能器寄存器的数据输入的结果添加到相位蓄能器和下一个时钟相位控制数据的作用继续下去。

因此,该相位器在参考时钟作用下完成线性相位累积。

每个相位在线性查找表中有相应的幅度,它完成一个周期时的相位蓄能器溢出作用。

周期信号的dds 合成时间。

相位累加器溢出频率dds输出信号的频率。

最后,它可以得到一个完整的波/输出数据的变化和低通滤波器。

的相位和振幅之间的对应关系是显示在图2。

每个阶段是对应于一个特定的大小。

相位已完成一个周期的幅度对应完成一个周期。

它是基本原理的之间的相位和幅度dds dds输出波形的频率,f0和时钟频率fc的关系,和时钟控制字可以用公式表示(1)。

(1)在频率控制字的地方,是相位的输出的宽度。

k时等于1,最小频率输出系统可以用公式表示(2)。

基于FPGA的DDS设计

基于FPGA的DDS设计FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,在数字信号处理中有广泛应用。

DDS(Direct Digital Synthesis)是一种通过数字方式生成连续、离散或者周期信号的技术。

本文将介绍基于FPGA的DDS设计。

DDS是数字方式实现频率和相位可编程的信号生成器,其核心部件是相位累加器和查找表(LUT)。

相位累加器是一个自增计数器,用来累加相位增量,并将累加结果作为地址输入到LUT中。

LUT是一个存储器单元,其中存储着一个完整的周期信号的离散样本值,通过查找LUT可以得到相应的数据输出。

DDS可以根据相位增量的改变来实现频率的可编程,同时可以控制相位步进的大小来实现相位的可编程。

1.相位累加器:相位累加器的实现可以利用FPGA的计数器模块。

计数器的初始值和步进值可以设定为对应频率的相位增量。

通过适当地改变计数器的初始值和步进值,可以实现频率的可编程。

2.查找表(LUT):LUT用来存储一个完整的周期信号的离散样本值。

在FPGA中,LUT可以使用一块专门的存储器单元,也可以使用分布式RAM实现。

LUT的大小往往需要根据生成的信号的精度和频率范围来确定。

3.相位步进控制:相位步进的大小可以通过在相位累加器中添加一个乘法器实现。

乘法器的输入可以由一个可编程寄存器控制,通过改变寄存器的值可以实现相位步进的可编程。

4.数字到模拟转换:DDS生成的信号是数字信号,需要经过数字到模拟转换(D/A转换)才能输出。

FPGA中有内置的D/A转换器模块,也可以通过外部的模数转换器实现。

1.灵活性:FPGA是可编程逻辑器件,可以根据需要自定义算法和硬件结构。

因此,在DDS的设计中可以根据具体的需求进行优化和改进。

2.速度快:FPGA具有并行计算的能力,可以同时处理多个数据和任务。

这使得基于FPGA的DDS设计具有更高的运算速度,能够实现更高的信号生成频率。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计一、引言随着科技的不断发展,数字信号处理(Digital Signal Processing,简称DSP)在各个领域得到广泛应用。

其中,一种常见的应用是通过数字直接合成(Digital Direct Synthesis,简称DDS)来生成各种信号。

DDS信号发生器能够快速准确地产生高质量的信号,被广泛应用于通信、电子测量、医疗器械等领域。

本文将阐述基于现场可编程门阵列(Field-Programmable Gate Array,简称FPGA)的DDS信号发生器设计。

二、FPGA的简介FPGA是一种可编程的逻辑器件,其内部包含了大量可编程的逻辑单元和存储单元。

FPGA具有灵活性高、可重构性强等特点,可以根据设计者的需求,灵活地实现各种数字电路。

因此,FPGA成为DDS信号发生器设计的理想平台。

三、DDS技术原理DDS技术通过数字控制相位累加器和振荡器来实现信号的直接合成。

其中,相位累加器用于控制振荡器输出频率的连续调节,振荡器则根据相位累加器的输出产生正弦波。

DDS信号发生器的主要步骤如下:1. 初始化相位累加器:将初始相位值存入相位累加器。

2. 累加相位值:相位累加器根据设定的增量值不断累加,得到一个新的相位值。

3. 查表获得振荡器的输出值:通过查表法,根据相位值获得振荡器的输出幅度。

4. 输出信号:根据振荡器的输出幅度,形成DDS信号。

四、1. 系统架构设计:本设计采用基于FPGA的硬件逻辑实现DDS信号发生器。

系统由相位累加器、振荡器、幅度调节模块和输出模块组成。

其中,相位累加器使用FPGA中的计数器实现,振荡器采用三角函数计算逼近的方式实现,幅度调节模块用于调节振荡器的输出幅度,输出模块将DDS信号输出到外部。

2. 相位累加器设计:相位累加器是DDS信号发生器的核心模块。

本设计采用基于FPGA的计数器实现相位累加器,通过控制计数器的计数速度来调节信号的频率。

基于FPGA的DDS设计实验

基于FPGA的DDS设计实验1.1 DDS的基本原理直接数字频率合成技术(Direct Digital Frequency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需波形的一种新的频率合成技术。

近年来,技术和器件水平不断发展,这使DDS 合成技术也得到了飞速的发展,它在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成化等一系列性能指标方面已远远超过了传统的频率合成技术所能达到的水平,完成了频率合成技术的又一次飞跃,是目前运用最广泛的频率合成技术。

1.1.1DDS的基本原理和优化构想DDS的主要思想是从相位的概念出发合成所需的波形,其结构由相位累加器,正弦ROM查找表, D/A转换器和低通滤波器组成。

它的基本原理框图如图1.1所示。

图1.1 DDS原理图图1.1中, fc为时钟频率, K为频率控制字, N为相位累加器的字长, m为ROM地址线位数, n为ROM的数据线宽度(一般也为D/A转换器的位数) , fo为输出频率, 输出频率fo由fC和K共同决定: fo = fC×K/2N。

又因为DDS遵循奈奎斯特(Nyquist)取样定律:即最高的输出频率是时钟频率的一半,即fo = fC/2。

实际中DDS的最高输出频率由允许输出的杂散水平决定,一般取值为fo≤40% fC。

对DDS进行优化设计,目的是在保持DDS原有优点的基础上,尽量减少硬件复杂性,降低芯片面积和功耗,提高芯片速度等。

为了减小DDS的设计成本, 对其结构进行优化,优化后DDS的核心结构框图如下所示。

图1.2优化后的DDS核心框图其中的地址转换器是根据adri[14]的数值判断数值是增长(0~π/2)或减少(π/2~π) ,数据转换器是根据adri[15]的数值判断生成波形的前半个周期(0~π)或者后半个周期(π~2π) 。

1.1.2 DDS的工作原理图1.3所示是一个基本的DDS电路工作原理框图。

基于FPGA的DDS信号源设计的开题报告

基于FPGA的DDS信号源设计的开题报告一、研究背景随着电子技术的不断发展,数字信号处理技术在通信、雷达、测量等领域得到了广泛的应用。

其中,基于FPGA的DDS(Direct Digital Synthesizer,直接数字合成器)信号源是实现高精度、高速、具有频率和相位可编程功能的一种常见的数字信号处理技术。

因此,本研究旨在探究基于FPGA的DDS信号源设计,以期应用于通信、雷达等领域。

二、研究内容本研究将以FPGA为硬件平台,采用Verilog HDL语言进行开发,实现一个基于DDS的数字信号源。

具体研究内容如下:1. DDS原理及数学模型研究。

介绍DDS的基本工作原理、数学模型及相关数学知识,为后续开发奠定基础。

2. DDS信号源实现原理研究。

介绍基于FPGA实现DDS信号源的原理,探究其设计方法及特点。

3. Verilog HDL语言研究。

介绍Verilog HDL语言基本语法及常用方法,为后续开发提供必要的编程技能。

4. DDS信号源设计与开发。

采用Verilog HDL语言进行设计和开发,根据实际需求和要求进行相关参数的设置和优化,进一步完善DDS信号源功能。

5. DDS信号源性能测试与评估。

通过实验对DDS信号源进行性能测试和评估,验证硬件实现的正确性和稳定性,并进一步改进性能。

三、研究意义1. 提高频率、相位、稳定性等指标。

DDS信号源的设计旨在提高其精度和速度,以满足通信、雷达等领域对信号源的高要求。

2. 减少噪声和失真。

基于FPGA的DDS信号源可以减少噪声和失真的发生,增强信号质量,提高传输质量。

3. 升级现有设备。

DDS信号源可以作为现有设备的升级组件,提高设备的效率和性能,降低后续维护和改进的成本。

四、预期成果本研究旨在开发一个高精度、高速、相位和频率可编程的DDS信号源。

通过测试和评估,期望得到下列预期成果:1. 实现一个基于FPGA的DDS信号源原型。

2. 确定DDS信号源的性能指标。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的DDS设计与实现摘要随着现代电子技术的不断发展,在通信系统中往往需要在一定频率范围内提供一系列稳定和准确的频率信号,一般的振荡器己不能满足要求,这就需要频率合成技术。

直接数字频率合成(Direct Digital Frequency Synthesis,DDS)是把一系列数据量形式的信号通过D/A转换器转换成模拟量形式的信号合成技术。

DDS具有相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号等优点,已成为现代频率合成技术中的姣姣者。

目前在高频领域中,专用DDS芯片在控制方式、频率控制等方面与系统的要求差距很大,利用FPGA来设计符合自己需要的DDS 系统就是一个很好的解决方法。

现场可编程门阵列(FPGA)器件具有工作速度快、集成度高、可靠性高和现场可编程等优点,并且FPGA支持系统现场修改和调试,由此设计的DDS电路简单,性能稳定,也基本能满足绝大多数通信系统的使用要求。

AbstractWith the continuous development of modern electronic technology in communications systems often require a certain frequency range provides a range of stable and accurate frequency signal, the general oscillator has been unable to meet the requirements, which require frequency synthesis。

Direct Digital Frequency Synthesis :“DDS”。

It is to form a data signal through D / A converter converts the signal into analog form of synthesis。

DDS has a relatively wide bandwidth, frequency conversion time is short, high frequency resolution, the output phase continuous, can produce a variety of broadband quadrature modulation signals and other advantages, has become a modern synthesizer technology leader. Present in high frequency areas, special DDS chip control, frequency control and other aspects of system requirements differ greatly, the use of FPGA to design DDS system suits their needs is a good solution.Field programmable gate array (FPGA) devices have to work fast, high integration, high reliability and the advantages of field programmable and support system for FPGA-site to modify and debug the design of the DDS circuit which is simple, stable performance, but also the basic communications systems can meet most requirements.关键词(keywords):频率合成(Frequency Synthesizer);DDS技术(DDS technology);频率控制(Frequency Control);FPGA设计(FPGA Design)目录1 DDS产生波形的原理 (3)2 DDS的结构原理 (6)3 DDS调频系统在FPGA中的实现的模块设计 (7)3.1 相位累加器控制模块的设计 (7)3.2 波形储存器ROM的设计 (8)4 连接原理图 (9)5 DDS的仿真 (10)1 DDS产生波形的原理利用DDS技术产生波形的过程是:基于奈奎斯特抽样定理对需要产生的波形进行采样、量化后存入存储器(例如ROM)中作为待产生信号波形的数据表;在需要输出波形时,从数据表中依次读出数据,产生数字化信号,这个信号再通过D/A转换器和滤波器后就变成了所需的模拟信号波形。

如果改变数据表中的内容,就可以得到不同的信号波形。

下面以正弦波信号波形的产生为例说明DDS工作原理。

基于DDS产生正弦信号波形的原理框图如图1所示。

图中,fclk为相位累加器的时钟信号,其周期为T0;相位累加器(从0~(2^n-1)计数)在fclk的作用下,产生数据存储器所需的地址信号。

如何获取正弦波形存储器中的数据呢?我们知道,某一个频率的正弦信号可以表示为式中,A为正弦波的振幅,w为正弦信号的频率(角频率),为初始相位。

由于A和不随时间而变化,可以令A=1,=0,得到归一化的正弦信号表达式如果将上述正弦信导的一个完整周期内的相位0~2pi的变化用单位圆表示,其相位与幅度一一对应,即单位团上的每一点均对应输出一个特定的幅度值,如图8.6.3所示。

例如,在圆上取16个相位点就有16种幅度值与之对应,如果在圆上取2^N个相位点,则相位分辨率为2pi/2^N。

根据奈空斯特定理,以等量的相位间隔对其进行相位/幅度抽样得到一个周期性的正弦信号的离散相位的幅度序列,并且对模拟幅度进行量化,旦化后的幅值采用相应的二进制数据编码。

这样就把一个周期的正弦波连续信号转换成为一系列离散的二进制数字量,然后通过一定的手段固化在只读存储器ROM中,每个存储单元的地址即是相位取样地址,存储单元的内容是已经量化了正弦波幅值。

这样的一个只读存储器就构成了一个与2pi周期内相位取样相对应的正弦函数表,因它存储的是一个周期的正弦波波形幅值,因此称其为正弦波形存储器,又称作查找表。

对于一个连续的正弦信号,其相位是时间的线性函数,相位对时间的导数为w,即当角频率w为一定位时,其相位斜率也是一个确定值。

此时,正弦波形信号的相位与时间呈线性关系,即。

根据这一基本关系,在一定频率的时钟信号作用下,通过一个线性的地址计数器对已得到的正弦波波形存储器进行扫描,进而周期性地读取波形存储器中的数据,其输出通过D/A转换器及低通滤波器就可以合成一个完整的、具有一定频率的正弦波信号。

假设存储器有2^n个存储单元,如果重复地从0~(2^n-1)单元读出数据存储器中的数据,在数据存储器的输出端就会得到周期性的正弦序列,如图8.6.4中的空心圆点所示;再将周期的正弦序列送到D/A转换器和低通滤波器进行变换,就可以得到连续的正弦信号。

显然,如果提高时钟信号fclk的频率,则从数据存储器中读出数据的速度就会加快,数据点之间的时间间隔就会缩短,读取一个周期的正弦数据所用的时间缩短,从而输出正弦信号的周期变小、频率增大。

由图8.6.4可知,输出正弦信号的周期T与地址计数器时钟信号的周期T0。

存在如下关系:式中f为输出正弦信号的频率,fo为计数器时钟信号的频率。

由上述分析可知,正弦波形存储器的地址数目决定了相位量化误差,而存储器的位数决定了幅度量化误差。

在实际的DDS中,可利用正弦波的对称性,将360度范围内的幅位、相位点减少到90度内,或利用正弦函数的压缩算法降低ROM的存储容量。

2 DDS的结构原理DDS的基本原理是利用有限的离散数据,通过查表法得到信号的幅值,通过数模转换器D/A后生成连续波。

DDS的原理框图如图1所示。

其中:频率控制字为fword;相位累加器的位数为N。

相位累加器以步长fword做累加,产生所需的频率控制数据;把得到的频率控制数据作为地址对ROM存储器进行寻址。

数据存储器(ROM)实质是一个相位/幅度转换电路,ROM中存储二进制码表示所需合成信号的相位/幅度值,相位寄存器每寻址一次ROM,就输出一个相对应的信号相位/幅度值。

理想情况下,累加器的N位全部用来寻址时,DDS的合成频率为:式中:fword为频率控制字;N为相位累加器位数;fclk为输入时钟。

当fword=1时,得DDS的最小分辨率。

如果改变频率控制字,就可以改变合成的频率的频偏。

3 DDS调频系统在FPGA中的实现的模块设计3.1 相位累加器控制模块的设计相位累加器由地址加法器和寄存器构成。

加法器完成加法,寄存器将加法器的结果加以保存作为下一次相加用。

周而复始直到加法器出现溢出。

相位累加器的速度主要由累加器来决定。

加法器的设计主要有三种方法:串行加法器、流水线加法器、并行加法器。

其中串行加法器结构简单,但速度较慢。

并行加法器虽速度较快,但占处理器的资源大。

本次课设使用的是流水线加法器,将加法器和寄存器结合在一起设计。

本设计中采用的是10位的频率控制字。

在满足性能的前提下为节省资源开销,从32位的相位累加器结果中提取高10位作为ROM的查询地址,由此而产生的误差会对频谱纯度有影响,但是对波形的精度的影响是可以忽略的。

以下是相位累加器的实现程序:module counter(clk,fre_word,address);input clk;input [9:0]fre_word;output reg[9:0]address;reg [31:0] phaseadder;//声明32位锁存器always@(posedge clk)beginphaseadder=phaseadder+fre_word;//以fre_word的作为总步长进行累加(例如fre_word=512,即一个周期以512步组成)。

address=phaseadder[26:15];//锁存输出取15到26位的地址值endendmodule3.2 波形储存器ROM的设计1、本设计中,要求DDS系统能输出方波,三角波和正弦波三种波形。

定制三个ROM (ROM:1-PORT),分别加载波形数据文件正弦波sinrom.mif、三角波triangle.mif、方波rectangle.mif。

ROM通过Tools中的MegaWizard Plug-In Manager…定制的。

2、定制三个ROM(ROM:1-PORT),分别加载波形数据文件正弦波sinrom.mif、三角波triangle.mif、方波rectangle.mif。