allegro初级培训教材

Cadence.Allegro入门培训系列 (4)约束管理器

电子技术论坛 电子发烧友目录第一章约束管理器介绍 (4)1.1 约束管理器简介 (4)1.2 约束管理器界面简介 (8)1.2.1worksheet selector (8)1.2.2用户接口 (9)1.2.3View选项 (9)1.3 启动约束管理器 (11)第2章OBJECTS介绍 (12)2.1 P IN-P AIRS (13)2.1.1Pin-Pair规则 (14)2.2 N ETS和X NETS (14)2.3 B USES (15)2.4 M ATCH G ROUPS (15)2.4.1如何确定target pin pair (16)2.4.2相对/匹配的群组规则 (16)2.5 D IFF P AIRS (16)2.5.1差分对工作表 (17)2.5.2差分计算器(Differential Calculator)的使用方法 (19)2.5.3差分对规则 (19)2.6 D ESIGNS AND S YSTEMS (20)第3章设置网络的走线约束 (21)3.1.1设置网络的最大最小传输延迟 (21)3.1.2设置网络相对传输延迟 (24)3.1.3设置差分对约束 (26)3.1.4查看网络规范格式和物理格式 (28)第4章设置网络的时序和信号完整性约束 (30)4.1 设置时序约束 (30)4.2 设置信号完整性约束 (32)4.2.1设置电气属性约束 (32)0 第一章约束管理器介绍2 4.2.2设置反射属性约束 (33)第5章电子约束创建和应用 (35)5.1 创建ECS ET (35)5.2 指定ECS ET给网络 (40)5.3 不考虑ECS ET的缺省约束值 (41)5.4 在原理图中查看ECS ET (41)第6章ECOS实现 (43)6.1 在原理图中增加网络 (43)6.2 在原理图中修改约束 (45)6.3 在约束管理器中修改约束 (46)6.4 在约束管理器中删除约束 (46)6.5 在原理图中重新命名网络 (47)第7章在原理图和PCB之间同步约束 (50)7.1 从原理图中输出约束 (50)7.2 在PCB D ESIGN中查看和添加约束 (50)7.3 在原理图中导入并查看约束 (51)7.4 在PCB和原理图之间同步约束的两种模式 (52)7.4.1用原理图中的约束重写PCB中的约束 (53)7.4.2在原理图中导入PCB中变更的约束 (56)第8章约束分析 (58)8.1 查看工作表单元格和对象 (58)8.2 定制约束、定制测量和定制激励 (59)8.2.1定制约束 (59)8.2.1.1 用户定义的属性 (59)8.2.1.2 约束的定制测量 (59)第9章SCHEDULING NETS (61)9.1 S CHEDULING N ETS (61)9.2 S CHEDULING N ETS-R EVISITED (65)第10章相对传输延迟 (68) 电子技术论坛 电子发烧友约束管理器简介3第11章 MATCH DELAY (73)第12章 解决DRC 冲突 (74)第13章 约束管理器 (76)13.1 层次设计中的电子约束...............................................................................................76 电子技术论坛 电子发烧友0 第一章约束管理器介绍4第一章约束管理器介绍约束管理器是一个交叉的平台,以工作簿和工作表的形式在Cadence PCB设计流程中用于管理所有工具的高速电子约束。

科通集团_Cadence_Allegro_基础培训_第五期

/

光绘输出——其他

• Valor检查所需文件

– Valor是通过光绘文件和网表文件(IPC356)来进行检查

44

科通集团

/

光绘输出——其他

• SMT所需坐标文件

45

科通集团

/

8

科通集团

/

PCB后处理——丝印(Silkscreen)

• 丝印重命名及反标

– 器件编号重命名

• 器件附上Auto_Rename属性

9

科通集团

/

PCB后处理——丝印(Silkscreen)

• 丝印重命名及反标

/

光绘输出——CAM输出

• Artwork光绘设置

42

科通集团

/

光绘输出——CAM输出

• Artwork光绘设置

– 光绘范围(Photoplot outline)

如果设定Photoplot outline, 对Artwork旋转、镜像时,将以 Photoplot outline的中心为基准点, 如果不设定,就以Extents 的原点为基准点。

23

科通集团

/

PCB后处理——输出光绘前的检查流程

• 报表检查

– Component Report

24

科通集团

/

PCB后处理——输出光绘前的检查流程

• 报表检查

– Component Report

PCB后处理——DFX要求

• DFM、DFA、DFT、DFC…

3

科通集团

/

PCB后处理——DFX要求

• DFM、DFA、DFT、DFC…

4

科通集团

/

PCB后处理——丝印(Silkscreen)

Allegro_SPB_16-3速成教材

电子工程师俱乐部--高级PCB论坛,一个可以免费教会你PCB设计的地方Allegro SPB 16.3版PCB画板速成教材:目录:1.创建平面元器件图2.绘制原理图并添加好其属性3.生成网表4.制作PCB焊盘5.制作PCB封装器件6.新建PCB板(画板框设板层)7.导入网表8.布局9.布线10.覆铜11.DRC检查12.出光绘说明:这是一个简单明了的画图过程,而不讲细节,否则正如其它500多页的教材那样,让你一下子没有个清晰的概念,而这部教材是为了让你有个全过程的基础概念并可真正画出PCB板来,以后细节(或高级)部分你再慢慢去深究就不会觉得迷茫了。

(软件界面的介绍就省了,各大教材都已说得很清楚)可能有些细节上写得不对,仅供学习参考.By:龍治铭E-mail:693303589@2011/01/09一、 创建电路原理中的新元器件 (目的:库里没有现成的元器件就得自己创建以便在画原理图时调用)打开Allegro Design Entry CIS ,先创建自己的一个元器件库(以后你可以拷到U 盘备份或到其它电脑用)如下图:点Library 后弹出右图如上右图所示,library1.olb 就是刚才建的库名称,如果你再建一个那就是library2.olb 了。

右击library1.0lb 那行,出现如下左边图所示:接着点New Part 出现给元器件命名的对话框,如上右边图所示,PCB Footpring 栏我们一般不在这里填,空着吧,原因很简单,以后你可能要它用作0603或0805的封装都不一定,所以先不理。

Parts per Pkg 一栏意思就是你这个元器件你要分为几部分来画,比如LM358如果两个放大器我们分为两个来画,那就填2。

点OK 后正式进入创建元器件界面如下图所示:点Place pin 按钮开始加管脚,最后虚线元器件外框要加外框变为实线。

特别注意的是,各管脚名不可同名,否则生成网表时会报错而无法生成网表。

Allegro基础训练第二课

对于不同的操作命令,控制面盘的显示(设置)的内容是不同的。对于参数的修改,是立即生效的。 而且它们优先于在其它环境中同样的参数设置。比如:在 Add\Text 命令的控制面盘中,如果你修改文字 旋转的参数,它就忽略在 Setup/Drawing Option(图 1.13)中设置的这个参数。

图 2.13 回放时可以选择的 Script 库文件

8

Allegro 14.2 训练 第二课

poqi055

Lab 2 Script 以及颜色设置和可视性的训练

本训练使用 Script 文件控制颜色和物理元素的可视性。方法是要改变内置层的可视性和颜色设置。 L2-1.1 开始 Script 文件纪录 1. 选择主菜单 File > Script,出现 Script 对话框 The Scripting dialog box appears. 2. 在文本栏中输入建立的 Script 文件名“colors”(注意不要回车) 3. 点击 Record.按钮

高亮显示的颜色是在颜色控制面盘中的 Display 组中设定:

7

Allegro 14.2 训练 第二课

poqi055

1.2.5 操作记录文件“Script”

该功能可以录制一些常用动作或一些简单的操作,当下次要使用到相同动作时就可以回放这录制的 Script 文件。

录制过程:

1。选择 File>Script 2。输入正确的路径和文件名 3。Record 4。做你想要的动作 5。Stop

2

Allegro 14.2 训练 第二课

第二课 管理 Allegro 工作环境

学习目标: 控制颜色和物体的可视性 建立运行记录(script) 在控制面盘中使用寻找物体 定位 PCB 板上物件的数据并作出报告

Allegro 技术知识

B. “第二天 Book 1”

Book 1 -

Lesson 6 - Importing a Logical Design into Allegro Lesson 7 - Setting Design Constraints Lesson 8 - Component Placement Lesson 9 - Advanced Placement Lesson 10 – Routing

1.2.3.1 画图区域尺寸设置 1.2.3.2 画图的参数设置 1.2.3.3 用户参数设置 1.2.4 练习 1.2.4.1 关于“World View”窗口 1.2.4.2 控制面盘位置设定 1.2.4.3 显示工具条的设置 1.2.4.4 画图设置练习 1.2.4.5 用户界面设置(改变光标形状)

4

Allegro 14.2 训练 第一课

poqi055

C. “第三天 Book 1”

Book 1 -

Lesson 11 - Copper Areas and Positive or Negative Planes Lesson 12 - Preparing for Post Processing Lesson 13 - Preparing the Board Design for Manufacturing

DB Doctor:检查数据库完整性,具备修复功能

图 1.1 Allegro 的应用程序

1.1.3 Cadence 中印制板设计工具

PCB Design Expert PCB Design PCB Studio Performance PCB Studio

Cadence 工具包中,关于 PCB 设计的模型有许多,在安装 界面可以根据需要(Lic 状况),进行选择安装。图 1.2 是几个 相关的选项。表 1.1 是关于 PCB 设计模型的说明。

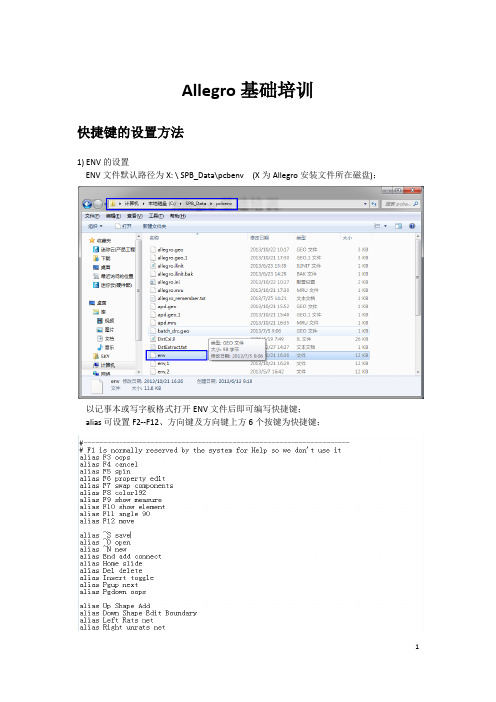

Allegro基础培训

Allegro基础培训快捷键的设置方法1) ENV的设置ENV文件默认路径为X: \ SPB_Data\pcbenv (X为Allegro安装文件所在磁盘);以记事本或写字板格式打开ENV文件后即可编写快捷键;alias可设置F2--F12、方向键及方向键上方6个按键为快捷键;funckey可设置字母键及数字键为快捷键;2) Stroke快捷键设置首先设置一下用户参数:Setup---> User Preferences;进入用户参数编辑界面,勾选Ui--->Input下的no_drapopup选项;然后进行Stroke快捷键的设置:Tools-->Utilities-->Stroke Editor;进入右键手势设置界面, 同一命令可设置多个相似手势,方便软件识别。

录制完成点击保存后即可使用右键手势。

3) 录制SCR文件进行快捷键设置:即将一系列动作进行录制后生成一个SCR文件,然后可在layout过程中调用SCR文件达到一键完成多个动作的效果。

录制方法:File-->Script ,在name栏输入需要录制的SCR文件名后点击Record开始录制。

开始录制后即可进行操作,例如设置格点的操作:设置完成后再次运行:File-->Script ,点击Stop结束录制。

此时brd文件所在目录下已生成了一个xxxxx.scr文件,然后在任意盘新建一个用于存放录制的scr文件的文件夹:接下来还需在ENV中设置一下调用命令:replay后的路径即为存放SCR文件的路径。

设置完成后重新启动软件即可使用快捷键来设置相应的格点。

铜皮的处理1) shape菜单功能介绍2) Global Dynamic Params 动态铜皮参数设置:3) 铺铜应注意事项:a、最好使用5的格点铺设铜皮。

b、铜皮边缘不要有直角及锐角。

c、小面积铺铜时使用静态铜皮。

电源模块布局布线1) 电源模块布局a、布局时需考虑电源回路路径,滤波电容尽量靠近电源输入或输出管脚,使回流路径尽量短。

Allegro使用基础_课案

Cadence Allegro学习与使用目录一.常用基本命令‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐二、设计规则检查(DRC)‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐三.覆铜(Shape)‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐四、ALLEGRO参数设置‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐五、直接在Allegro里面新增一个零件‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐六.Xnet 等长设置‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐七.尺寸标注‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐八.ALLEGRO生成钻孔文件‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐九.ALLEGRO生成光绘Gerber文件‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐一.常用基本命令(一)、首先说明鼠标的操作使用,在Allegro 系统中,鼠标三个按键之功能如下:1. 鼠标左键–选取功能(1) 用来在菜单内选择命令,并执行之。

(2) 用来选取欲动作的对象或对象。

2. 鼠标中键–画面控制功能(1) 按住鼠标中键不放开,并同时移动鼠标,可以平移目前的可视画面位置。

(2) 按一下鼠标中键,可以控制屏幕的大小,至于是做放大或缩小的功能,则需视上一次是做放大或缩小的功能而定,即与上一次做相同的功能。

3. 鼠标右键–弹出式选单。

当有使用命令时,可在Design Window 中下按一下鼠标右键,会拉出目前命令的弹出式菜单,而每一个命令的弹出式选单,可能会有不一样的选项,以下介绍各个选项:(1) Done:执行本命令后,才结束本命令。

(2) Oops :复原上一次的动作 ( Undo 功能 )。

(3) Cancel:取消本命令的执行。

(4) Temp Group :开始进行“自由多点选取” 的动作(5) Complete:结束“自由多点选取” 的动作。

Cadence Allegro中文培训教材(可编辑)

Cadence Allegro中文培训教材Shanghai Winnet Electronic Co Ltd 上海银利电子有限公司Shanghai Winnet Electronic Co Ltd技术文档标题Cadence Allegro 160中文培训教材Document Type 技术手册Product AllegroProduct Version 160Author Jack LiuCreate Date comRemarkShanghai Winnet Electronic Co LtdHttpcomcn1 90Shanghai Winnet Electronic Co Ltd第一章 Allegro 的用户界面本章的主要内容介绍Cadence 公司的Allegro 印刷电路板布线系统软件的用户界面通过本章学习可以对 Allegro 的工作界面有了大致的了解同时也能体现出 Allegro PCB Editor 的强大功能11程序的启动单击除了以上Allegro 主程序我们还会常用到以下几个常用工具Pad DesignerPadstack EditorDB doctorPADS TranslatorPCB Editor toSPECCTRAPad Designer 的作用是建立和修改Pad 具体会在下面章节中讲到DB doctor 的作用有三个 1板子 Data-base 的检查2板子 Data-base 的修复3更新板子上的 DRCPADS Translator 的作用是把PADS 格式的 PCB 板直接读进Allegro 中PCB Editor to SPECCTRA 的作用是把Allegro 中的设计数据自动传递到SPECCTRA 自动布线器中支持的文件为 brd mcm mdd psm dra pad and sav database2 90Shanghai Winnet Electronic Co Ltd12 Cadence Allegro 产品模块介绍Cadence PCB设计工具包括OrCAD和SPB两个系列其PCBlayout均采用AllegroAllegro 有以下 4 个版本用户可以根据自己的设计层次需求购买不同版本的Allegro 开发平台主要功能差别见下表Allegro PCB Design GXL 最高端的产品对于高速高密度PCB 设计的完整高性能设计工具包括高速信号线的电气物理特性的设定和协同设计功能Allegro PCB Design XL 没有高速信号的电气设定其他功能与 AllegroPCB Design GXL 相同Allegro PCB Performance option 和 Allegro PCB Design L 功能相同包含复杂设计规则如route to lengthparallelismdifferential pairsAllegro PCB Design L 完整的 PCB设计工具没有高速信号线特性设定不能用 skill如果用户购买有不同版本的 Allegro 开发平台在开启该平台时会弹出如下对话框选择所要使用的版本当选择后启动产品时在以后打开系统时会直接进入上次所选用的Allegro 开发平台若想在使用过程中更改产品你可以在点击菜单 File 下面的 Change Editor在出现上面对话框时选择所需产品3 90Shanghai Winnet Electronic Co Ltd13 Allegro 常用文件类型的介绍Allegro 根据不同性质功能的文件类型保存不同的文件后缀主要的类型可以参照下表文件后缀名文件类型brd 普通的电路板文件dra Symbols或Pad的可编辑保存文件pad Padstack文件在做symbols时可以直接调用psm Library文件存一般元件package part symbolsosm Library文件存格式化 symbolsbsm Library文件存机构 symbolsfsm Library文件存flash symbolsssm Library文件存shape symbolsmdd Library文件存module definition tap 输出的包含NC drill数据的文件scr Script 和macro 文件art 输出的底片文件log 输出的一些临时信息文件txt 普通文字档文件color View层面切换文件14 Allegro 的目录结构Allegro 的文件目录可以分为两部分安装路径工作路径安装路径系统默认的安装路径为C\Cadence\OrCAD在安装时用户可以根据自己随意更改安装路径工作路径系统默认的工作路径为C\ OrCAD _DATA 在安装时建议用户把工作路径设在非系统盘上如D\WORK 之类的4 90Shanghai Winnet Electronic Co Ltd工作路径设定与更改因为Allegro 在打开文件时有一个工作目录它做的所以动作都会以当前工作目录为基准如保存当前文件输出产生的各类文件所以我们在新建文件或者打开文件时就要将 Change Directory 打勾这样在保存或输出时才会存在正确的路径上15 电路板的预览功能Allegro 具有板子预览功能在打开对话框的右下角有两个按钮预览电路板的参数预览电路板的框架5 90Shanghai Winnet Electronic Co Ltd16 Allegro 的工作界面Cadence Allegro 的工作界面与之前版本相比有了较大的变化添加了Cadence 商标美化了工具栏图标扩展了工作区域面积从图中就可以了解Allegro 的整个工作界面和环境工具栏菜单栏标题栏控制面板工作区命令窗口状态栏视窗1标题栏显示当前所选择的Allegro 开发平台设计名称和工作路径2 菜单栏设计所需要的Allegro 功能命令大部分都可以在菜单里找到3 工具栏如下图所示可以分为图中的几个区块File Edit View Setup DisplayAppmode Shape Dimension ManufacturePlace Route Add Misc6 90Shanghai Winnet Electronic Co Ltd用户可以根据自己需要自行定制工具菜单点击View 〉Customization 〉Toolbar弹出如下窗体用户可以点击选择需要的工具块如打勾 File 左边的方框就在工具栏出现 File 工具块如下图取消打勾 File 工具块就在工具栏消失其它的也一样设置如果需要添加某个命令的图标只要在右边窗体的Commands 下面的Buttons的工具图标往工具栏上拉就可以用户也可以通过 New 新建自己的工具块然后通过上面的拖拉方式把自己想要的拉到那工具块里就可以了7 90Shanghai Winnet Electronic Co Ltd4 控制面板对于控制面板在 160 版本中进行了较大的改进控制面板在平时不用时会自动收缩使工作区域最大化Options Folder Tab 根据使用命令的不同而显示不同细节设定执行命令后Options的相关参数就显示当前命令的有关设置下面图示了几个常用功能的 Options 窗体具体每个功能的使用可以参考目录Copy Z-Copy8 90Shanghai Winnet Electronic Co LtdAdd Connect Add TextFind Folder Tab Find Filter 寻找或者选择的物件Find 也是体现 Allegro 功能强大的地方通过 Find 可以更容易选中你想要选择的东西整个Find 窗体可以分为上下两部分上面是一个Filter 滤镜作用是在点选板子上的 Element 板子上的所有成份物件时可以过滤你不想要的类型使更容易选中想要的 Element 下面按Element 名称查找Design Object Find Filter上面的 All On 是选中所有复选框All Off 是取消所有选中Find By Name查找类型按Name 查找还是从文件中查找输入 Name 或文件名下面详细介绍◆ Visibility9 90Shanghai Winnet Electronic Co LtdVisibility层面开关控制Views快速切换层面通过下拉菜单可以快速切换想要打开个关闭的层面下拉菜单可分为三部分1Last View Show 最后一次执行的层面2File Show 自己保存的color文件操作步骤首先通过点击自己选择要打开的层面然后执行菜单View Color View Save出现左边的窗体在 Save view 右边文本框中输入保存的文件名在下面选择 Complete 点击 save 就可以了所存文档为color目录为当前工作目录在 Views 的下拉菜单里就多了个 top 以后就可以直接点击 top 快速切换了5 工作区创建和编辑PCB 的工作区域6 命令窗口显示目前使用的命令的相关信息并可以输入命令并执行如下图所示10 90Shanghai Winnet Electronic Co Ltd7 状态栏显示正在执行的命令的名称鼠标的位置17 鼠标按钮鼠标按键的主要功能可以见下表两键鼠标三键鼠标按键功能左键LMB 左键LMB 选取命令或区域右键RMB 右键RMB 下拉目前命令的Pop-Up Menu显示右键相关命令或者执行stork 动作Shift+右键中滚轮键移动和缩放画面ShiftRMB CMB18 控制画面的缩放菜单 View Zoom 也可以直接点击工具栏上小相应图标Zoom In放大Zoom Out缩小Zoom Points放大两点之间的工作区Zoom Fit以board outline为界放大于整个工作区但不超出工作区Zoom Previous工作区域跳回之前的大小Refresh刷新工作区域Zoom World以Drawing Extents的size至于工作区内Zoom Center工作区域依一个xy值至于中央11 90Shanghai Winnet Electronic Co Ltd19 Getting Help 另外按住中键滚轮不放然后移动鼠标可以移动画面滚动鼠标滚轮可以实现显示区域的缩放19 Getting Help在使用 Allegro 如果遇到问题可以有以下几个方式得到帮助WinHelp使用过程中按F1 或查找手册电话咨询Source Line servicehttpsourcecomhttpcomCRC 0800-241-25612 90Shanghai Winnet Electronic Co Ltd第二章设定 Allegro 的工作环境本章主要内容介绍 Allegro 工作环境的设定21 设定绘图参数Cadence Allegro 160 版本将设计参数设置做了较大幅度的调整常用的设计参数集中在同一个控制界面新的参数设定界面包含 DisplayDesignTextShapeRoute 和 Manufacturing Applications1 点击菜单 Setup Design Parameter出现下面窗体点击 Design 选项Size定义设计单位-3User Units 设定单位Mils 10 英寸Inch 英寸Microns 微米Millimeter 毫米Centimeter 厘米Size设定工作区的大小标准 A 11x85B 17x11C 22x17 D 34x22 Other 用户自定义13 90Shanghai Winnet Electronic Co LtdAccuracy 精确度小数点后保留的位数必须在设计的全过程保持一致设置如果使用 Mil 为单位小数点后面位数为0EXTENS 定义工作区域LeftX Lower Y 工作区域左下角的坐标Width Height 工作区域的宽和高MOVE ORIGIN 把当前原点移动到新的坐标若不更改坐标原点的话对于那些以原点为中心的器件封装只能显示一部分与工作区域X Y 分别为移动的相对坐标输入好后系统会自动更改 LeftX Lower Y 的值以达到移动原点的目的Drawing Type 设计类型Type 显示当前文件的类型不能修改Line Lock 走线设置Lock direction走线角度的选择Off 拐角度数任意45 自动拐角45 度90自动拐角90 度Lock mode走线类型的选择Line 直线Arc 圆弧Minimum radius设定走圆弧线时的最小半径Fixed 45 length设定走 45 度线时斜边的固定长度Fixed radius 设定走圆弧线时半径值固定Tangent 设定走圆弧线时以切线方式走弧线Symbol 元件设置Angle 设定旋转角度0360 度Mirror 设定是否旋转至背面Default symbol height 元件的默认高度14 90Shanghai Winnet Electronic Co Ltd2 点击 Display 出现如下窗体设定显示属性Connect point size设定 T 型连接点的尺寸DRC marker size设定 DRC 的显示尺寸Rat T Virtual pin size设定 T 型飞线的尺寸rband count 当放置移动元件时允许显示的网格飞线数目零件 Pin156设 500 效果设 100 效果Ratsnest geometry飞线的走线模式15 90Shanghai Winnet Electronic Co LtdJogged当飞线呈水平或垂直时自动显示有拐角的线段Straight最短的线段Ratsnest Point 设定飞线的点距Closest endpoint显示 EtchPinVia 的最近两点间的距离Pin to pin显示管脚之间最近的距离Display drill holes 显示上锡的孔Display drill hole NormalDisplay non-plated holes显示不上锡的孔Filled pads系统会将 Pin 和 Via 由中空改为填满模式 Filled pads NormalConnect line endcaps显示拐角处的平滑选中不选中Thermal pads显示 NegativeLayer 的PinVia 的散热十字孔Bus rats 如果设定 Bus name 的话它会用特别的方式显示这一组 rats下图所示Bus ratsWaived DRCs设置 DRC 为可接受的16 90Shanghai Winnet Electronic Co LtdGrid On 显示格点SetupGrid设置格点如下图所示Grid On 显示格点Non-Etch 设置非走线层的格点参数All Etch 设置走线层的格点参数Top 设置顶层的格点参数GND 设置地层的格点参数VCC 设置电源层的格点参数Bottom 设置底层的格点参数如果添加一些其他层面还应设置该层的格点参数参数设置说明Spacing x x 轴的格点间距大小Spacing x y 轴的格点间距大小Offset x x 轴的偏移量Offset y y 轴的偏移量3 点击 Text出现如下窗体Justification加 text 时光标所在字体的那边的选择Parameter block 光标大小的设定Markersize所加的 text 的大小的设定Setup Text Sizes设定 Text 大小17 90Shanghai Winnet Electronic Co Ltd22 定义快捷键Cadence 系统是一个比较开放的系统它给用户留了比较多的定制空间为了使用软件更为方便快捷在Allegro中我们可以用alias 或funckey 命令来自行设定快捷键以代替常用的设计命令下面将介绍怎么去设定快捷键以及列出默认的快捷方式1系统默认的快捷方式系统默认的快捷方式见下表Key Command Key CommandF1 Help SF1 Add ConnectF2 Done SF2 GridF3 Oop SF3 Hilite PickF4 Cancel SF4 Dehilite AllF5 Show Element SF5 RedisplayF6 Property Nets SF6SlideF7 Edit Vertex SF7 MoveF8 Zoom Points SF8 availableF9 Zoom Fit SF9 Write tempF10 Zoom In SF10 availableF11 Zoom Out SF11 availableF12 available SF12 available注SF1 为 Shift+F1 其它类推2 快捷键格式alias 然后空格然后按你想定义的快捷键或直接输入然后输入你定义的功能的命令如右图定义 F2 为 Add connect 命令的快捷键快捷键定义可以分为右图 ab c 三部分a 为命令 aliasb 为预定义的快捷键建议大家直接按键取得c 为预定义功能能定义快捷键的功能键为F2~F12 键盘右边的上下左右InsertHome Page Up Delete End Page Down18 90Shanghai Winnet Electronic Co Ltd还有这些功能加上 CtrlAlt ShiftCtrl +Alt Ctrl +ShiftShift+Alt Ctrl+Alt +Shift 切换键的单独和共同的七种组合还有 Ctrl +键盘上的除功能键外的其它键都能设快捷键定义快捷键的 b 部分的具体写法见下表F2~Page PageInsert Delete Home EndF12 up DownF Insert Delter Home End Pgup Pgdown Up Down Left RightCtrl CF CInsert CDelete CHome CEnd CPgup CPgdown CUp CDown CLeft CRightAlt AF AInsertShift SF SInsertCtrl Alt CAF CAInsertCtrlCSF CSInsertShiftShiftASF ASInsertAltCtrlAltShif CASF CASInsertt注意1F1 为系统预定 Help 功能不能定义其它功能2 字母的大小写3定义快捷键步骤要使定义的快捷键产生作用我们有两种方式来定义A 在命令窗口直接定义但这样定义的快捷键只能在当前设计中使用如果重新启动设计时快捷键将会失效命令格式如下alias shortkey Keyboard Commandsfunckey shortkey Keyboard Commands注意A如果直接键入alias 或funckey 命令然后回车系统将会弹出所有快捷键列表这相当于执行Tools- Utilities- AliasesFunction keys 命令Balias 命令不能用来定义字母原因是字母键要用来输入命令行但是funckey 命令可以用来定义单个字母为快捷键它比alias 命令更为强大alias能定义的它都能定义但是字母被定义成某快捷键后该字母就不能用来输入键盘命令了C Allegro 中的所有键盘命令 Keyboard Commands 列表可以通过执行Tools- Utilities- Keyboard Commands 命令来查看这些命令都可以设置成快捷键19 90Shanghai Winnet Electronic Co LtdB 在本地环境变量文件evn 文件中定义这样定义的命令将长期有效例如我们以前在Protel 或PowerPCB 中常用的放大缩小命令就可以如下定义alias Pgdown zoom outalias Pgup zoom in具体步骤如下单击我的电脑单击右键打开系统属性点击高级标签页如下图所示点击环境变量在用户变量查看HOME路径如下图所示20 90Shanghai Winnet Electronic Co Ltd双击我的电脑打开HOME路径找到Pcbenv文件夹如下图注意Pcbenv 文件夹会在设定 User Preference File 后自动产生也就是记录个人修改设定参数的信息文件双击打开Pcbenv文件夹找到env文件如下图所示21 90Shanghai Winnet Electronic Co Ltd用记事本格式打开env文件按照快捷键的格式定义快捷键并保存注意设定的快捷键内容从第二行开始写第一行是source TELENV 要加在的上面否则在下次修改 UserPreference 时系统自动会把下面的内容更新所以定义的快捷键也没了下面是正确的重新启动 Allegro 所自定义的快捷键功能即可使用22 90Shanghai Winnet Electronic Co Ltd23 使用 StrokesStrokes 功能是通过滑动鼠标来产生功能省去了选取菜单或点击工具栏命令的时间使Layout 更快捷使用方法是按住 Ctrl 键然后按住鼠标右键在工作区域内滑动通过划不同路径就可以产生右边表格中的几个不同功能技巧按住 Ctrl 再去按右键滑动鼠标会显得很麻烦可以在User Preferences下设定后直接按右键划鼠标就可以具体操作如下执行菜单 Setup User Preferences 出现窗体在左边的Categories 中选择Input 然后打勾no_dragpopup 右边的方框点击 OK 完成23 90Shanghai Winnet Electronic Co Ltd除了使用系统自带的 Strokes 见右表用户还可以自定义 Strokes Stroke 功能快捷键Copy CtrlCMove ShiftF7Zoom In F10Opps UndoF3Zoom World-Delete -设置 Stroke 的方法如下选择Tools Utilities Stroke Editor弹出如下图所示Stroke 编辑窗口右边一栏为系统已经定义好的 Stroke左边一栏为 Stroke 绘制窗口在左边一栏滑动鼠标右键绘制所需要的图形在下方 Command 栏输入其所代表的命令点击 Add则新设置的 Stroke 出现在右边一栏中如果需要删除先选中右边一栏中不要的Stroke单击鼠标右键选择Delete24 ScriptScript 的功能就像一个录像机可以把你做的动作录制下来然后在你需要重复做录制好动作的时只要回放已录制的动画就可以了合理使用 Script 功能可以省去你不少做重复动作的时间从而提高效率下面介绍 Script 的基本操作24 90Shanghai Winnet Electronic Co Ltd执行菜单 File Script 出现下面窗体Name 输入录制或回放的文件名默认路径为当前的工作路径如果想更改路径的话只要点击 Browse就可以了Macro Record Mode 选择是否要用宏模式录制 Script Library List 出来当前工作目录下和工作环境设置的 Script 目录下的Script点选按 OK 就可以了Record 开始录制 ScriptStop结算录制 ScriptReplay 回放 Script要录制 Script 只要在 Name 框里输入文件名然后点击即可开始录制然后去做想做的动作结束时再次在执行菜单File Script点击就可以了。

Allegro 使用培训手册

Allegro 使用培训手册本部EDA设计室2004 年3月目录概述 (4)第一章原理图打包和Allegro界面概述 (5)1.1 使用Cadence的条件 (5)1.2 打开Project Manager (6)1.3 原理图打包 (8)1.4 Allegro的使用界面说明 (9)1.4.1工具栏说明 (10)1.4.2调整工具栏 (10)1.4.3控制栏说明 (11)1.4.4略缩图和状态栏说明 (12)1.4.5命令输入窗口说明 (12)1.4.6颜色设置窗口说明 (13)1.4.7记录和回放 (13)1.5 Allegro目录结构 (14)1.5.1 Allegro文件目录结构 (14)1.5.2 环境目录 (14)第二章制作板外框、颜色设置、叠层设置、元件布局和尺寸标注 (16)2.1制作板外框 (16)2.2放置定位孔 (17)2.3颜色层的设置 (19)2.4添加叠层 (19)2.5元件布局 (20)2.5.1第一种方式布局 (20)2.5.2第二种方式布局 (21)2.6移动元件 (22)2.7边框倒角和尺寸标注 (22)2.7.1边框倒角 (22)2.7.2边框倒角尺寸标注 (23)第三章布局之后的各项设置 (26)3.1填写技术说明和叠层说明 (26)3.1.1逐个字符输入法 (26)3.1.2复制技术说明法 (27)3.2添加归档文件外框 (28)3.3高亮显示电源和地网络 (29)3.4约束管理器的设置 (29)3.4.1普通线宽和线距设置 (31)3.4.2电源线宽设置 (32)3.4.3差分线宽和线距设置 (34)3.4.3.1与Cadence 14.x版本兼容的设置方案 (34)3.4.3.2 Cadence 15.0差分信号属性的设置方案 (38)3.5电源和GND的大致划分区域 (40)3.6 光绘的输出设置 (43)第四章布线、修线、加测试点和DRC检查 (48)4.1 走线 (48)4.2 移动线 (49)4.3 修线 (50)4.4 查看走线布通率 (50)4.5 加在线测试点 (52)4.6 DRC检查 (53)第五章调整丝印、Valor检查和铺铜 (55)5.1 丝印调整 (55)5.2 添加板名、条目和防静电标识符 (55)5.3 Valor检查 (57)5.4 铺铜 (57)第六章光绘输出和检查 (61)附录 1 Allegro菜单对应的command命令 (65)概述作为流行的EDA 工具之一,Cadence 一直以来都受到了广大EDA和电路设计工程师的青睐,然而Cadence 的使用之繁琐又给广大初学者带来了不少麻烦,对于部分自己做PCB的硬件研发工程师和公司新招募的EDA工程师,许多人都对Cadence软件不熟悉,不知到怎样由原理图打包并转到Allegro的PCB中、不知怎么对Allegro的环境变量进行设置、不知如何进行布局和布线、不知布线之后如何检查和输出光绘等等。

培训教材-allegro基本操作

图12

②.设置PCB元件库路径。菜单Steup—User Preferences,弹出对话框,按图13步 骤操作:

完成以上步骤后,在分别设置 padpath和psmpath,这两个设置 的路径和图13中的第3步一样

PCB元件库路径

图13

.打开原理图,生成Netlist,导入PCB。生成Netlist的操作如下图:

图7

图8

Visibility:快速、直接地代开或者关掉与走线相关层面的颜色。需要换层,查 看不同层面的走线的时候,要先选择在这个选项内 例如:想看Bottom层走线信息,先点到Visibility界面,在Views选择File: ETCH_BOT(如图7),就可以看到Bottom层的信息了。在图8,红圈内,同样可以选 择所需了解的信息。(需要看哪个层面就在方框内打勾,不需要看的就不要勾上。)

图9

按照图9填写完成后,点击Edit/View layers,出现以下对话框:

图10

按照图上步骤操作,第5步OK完成后,会转到图五,最后在图五左下角点击 “Improt”。整个结构的导入就完成了

要查看结构图的时候,请注意做以下的选择,点击菜单

,按照图11进行操作

图11

2.导入网表

①根据所导入的结构图,给PCB增加板框。板框绘制步骤如下:点击增加线段图 标 ;在控制面板Opitions,按照图12进行操作:上面的红框内,显示的是要操作 的层面,在Board Geometry层的Outline子层,Line width(线宽)是6mil

图5

图6

Find:选择可以被作用的对象;此选项主要是配合其他指令来执行的 例如,查找元件R1,先在图一菜单快捷键行,选择第4组第1个按键 然后在图6的find栏里如下操作:选择All Off,然后在Symbols方框处,打勾,在 Find By Name里,选择Symbol(or Pin),在最下面一个框里输入“R1”,回车, R1则会被高亮出来。查找元件pin脚,则在Pins框内打勾,在最下面的方框内输入 “R1.1”,回车,R1的1脚就会被高亮出来。如果需要查找网络,则在Net方框内打 勾,在第二个红圈内选择NET,在最后一个红圈内输入网络名称即可。高亮的步骤与 查找的步骤相同,高亮先点击 ,然后再Find里面勾上Symbols或者Nets,最后选 择要高亮的信息。取消高亮点击 ,步骤同上。

Cadence Allegro SI培训课件Lesson.ppt

Solution Space Analysis Step 5

The solution found thus far is a single-line solution. Crosstalk timing shifts must be within crosstalk budget. Single-line topology is modified to model coupling where appropriate. Different line width / spacing rules are evaluated for timing impact. Result is line width / spacing rules for layout.

Measurement Expression Editor

Partially complete expression

Expand and Collapse: The [+] and [-] controls are used to expand and collapse any item in the treeview.

be implemented. Traces on the same layer have identical characteristics. Resistors in the same RPAK match closely. Develop a simulation strategy based on combinations to be analyzed.

Point-to-point device connection

Terminators at the end of the net on short stubs.

Allegro中文教程

Allegro中⽂教程Allegro培训教材⽬录第⼀章焊盘制作-------------------------------------------------------21.1 ⽤Pad Designer 制作焊盘---------------------------------------21.2 制作圆形热风焊盘----------------------------------------------7 第⼆章建⽴封装------------------------------------------------------102.1 新建封装⽂件-------------------------------------------------102.2 设置库路径---------------------------------------------------112.3 画元件封装---------------------------------------------------12 第三章元器件布局----------------------------------------------------223.1 建⽴电路板(PCB)----------------------------------------------223.2 导⼊⽹络表---------------------------------------------------233.3 摆放元器件---------------------------------------------------26 第四章 PCB布线------------------------------------------------------314.1 PCB 层叠结构-------------------------------------------------314.2 布线规则设置-------------------------------------------------344.2.1 对象(object)--------------------------------------------354.2.2 建⽴差分对----------------------------------------------374.2.3 差分对规则设置------------------------------------------384.2.4 CPU与DDR内存芯⽚⾛线约束规则--------------------------404.2.5 设置物理线宽和过孔--------------------------------------464.2.6 设置间距约束规则----------------------------------------524.2.7 设置相同⽹络间距规则------------------------------------564.3 Allegro PCB布线----------------------------------------------564.3.1 ⼿⼯拉线------------------------------------------------564.3.2 应⽤区域规则--------------------------------------------604.3.3 扇出布线------------------------------------------------614.3.4 差分布线------------------------------------------------634.3.5 等长绕线------------------------------------------------654.3.6 分割平⾯------------------------------------------------66 第五章光绘⽂件输出--------------------------------------------------695.1 Artwork 参数设置---------------------------------------------695.2 ⽣成钻孔⽂件-------------------------------------------------755.3 输出底⽚⽂件-------------------------------------------------79第⼀章焊盘制作1.1 ⽤Pad Designer 制作焊盘Allegro 中制作焊盘的⼯作叫Pad Designer ,所有SMD 焊盘、通孔焊盘以及过孔都⽤该⼯具来制作。

allegro学习基础 第一章 焊盘的建立

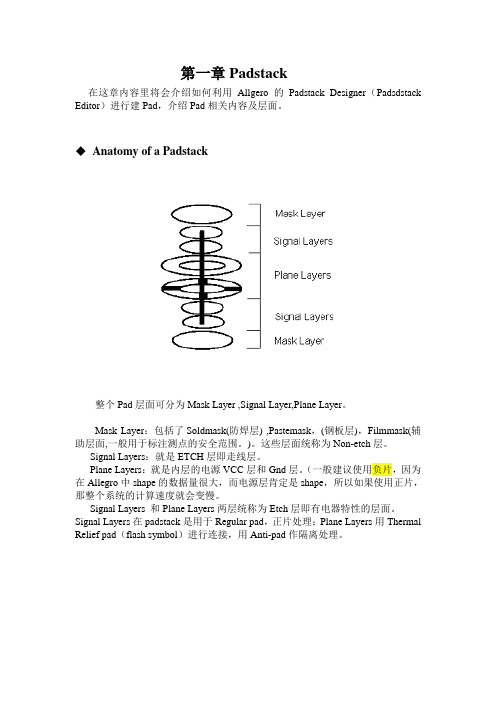

第一章Padstack在这章内容里将会介绍如何利用Allgero 的Padstack Designer(Padsdstack Editor)进行建Pad,介绍Pad相关内容及层面。

Anatomy of a Padstack整个Pad层面可分为Mask Layer ,Signal Layer,Plane Layer。

Mask Layer:包括了Soldmask(防焊层) ,Pastemask,(钢板层),Filmmask(辅助层面,一般用于标注测点的安全范围。

)。

这些层面统称为Non-etch层。

Signal Layers:就是ETCH层即走线层。

Plane Layers:就是内层的电源VCC层和Gnd层。

(一般建议使用负片,因为在Allegro中shape的数据量很大,而电源层肯定是shape,所以如果使用正片,那整个系统的计算速度就会变慢。

Signal Layers 和Plane Layers两层统称为Etch层即有电器特性的层面。

Signal Layers在padstack是用于Regular pad,正片处理;Plane Layers用Thermal Relief pad(flash symbol)进行连接,用Anti-pad作隔离处理。

Pad的种类Pad的建立当大家了解了Pad的一些相关内容后,开始进入建Pad的部分。

在建Pad以前需要先介绍两个与建Pad相关的零件shape symbol及flash symbol 的概念及建立。

Shape Symbol为什么要引进shape symbol呢?原因是在于建pad时有可能要建一些形状比较特殊的Pad(例如一些金手指pad的外形),它又不能用单纯的方形,圆形,椭圆等标示,那没有其他办法的时候,就可以利用建一个特殊形状的shape symbol来描述它的外形。

如何建立一个shape symbol?步骤:1,设定作图的参数,这是一个在新建一个物件时都需要进行设定的一个步骤。

Allegro15.7基础教程

預覽工作檔的大概架構

預覽工作檔的一些參數

1-5

G. Allegro 的工作介面

下圖描述的 Allegro 的工作介面,從圖中就可以瞭解 Allegro 的整個工作介面和環境。

工作選單

標題列

工具列

工作區

控制列

命令列

狀態區

標題列:顯示當前 Allegro 版本和工作路徑

工作選單:Allegro 的功能命令都可以在功能表裏找到

第十章 Rename------------------------------------------------------------------------------------------------------------------ P10-1

第十一章 AutoSilk & Report--------------------------------------------------------------------------------------------------- P11-1

•Visibility Folder Tab 層面開關控制

•World View Window 做圖畫面的範圍將滑鼠置於 #World View Window 按滑鼠右鍵才可以

板子外框

Move Display 的功能就是移動當左圖中前顯示視 窗在整個工作區域的位子 Resize Disply 是修改當左圖中前顯示視的大小 Find Next 下個畫面 Find Previous 前一個畫面

第八章 Routing and Glossing--------------------------------------------------------------------------------------------------P08-1

CadenceAllegro16.5培训教程

注意:用这种方法创建的快捷键是不能保存的,可以在创建时 同时录制脚本,以脚本方式保存快捷键。

Lesson3 焊盘制作

• 学习要点:

• 创建热风焊盘 • 使用Pad Designer创建通孔类和表贴类焊盘

drawings fabrications

drawings reports Autorename backannotation

Physical design analysis

Generate manufacturing

output

Define Power/ GND planes

Arrange/place components

还可以通过“Setup->Change Drawing Origin”改变坐标原点的位 置。

Design标签页

90 45

Off

Line Arc

(Mirror)

0

90

Allegro中的层面设置

• Allegro中所有的元素都通过Class和Subclass来进行管理 • Class是定义好的,用户可以通过 “Setup->Subclass”来建立新的Subclass

Interactive and automatic

route signals

Gloss/auto cleanup for manufacturing

主要产品介绍

• 为了适应不同用户的需要,Cadence软件包中提供了Allegro PCB Designer、OrCAD PCB Designer Standard和OrCAD PCB Designer Professional 3种PCB设计软件版本。

• (1)Allegro PCB Designer:是应用最广泛的一种版本。产品由Base模 块和Option附加模块组成,通过一个完全集成式的设计流程进行PCB Layout设计。

科通集团_Cadence_Allegro_基础培训_第四期

12

科通集团

/

PCB布线基本原则与操作

• 布线规划

– 约束设置

• 物理规则设置 • 间距规则设置 • 电气规则设置

– Fanout

• • • • 对BGA封装器件的Fanout,最好成十字通道 十字通道上不能有过孔 所有的过孔都放在临近的4个焊盘中间 如果不是所有的BGA引脚都有网络,根据实际情况来定

38

科通集团

/

PCB布线基本原则与操作

• 手动布线

– 时序等长控制

• 延迟调整(Delay Tuning)

39

科通集团

/

PCB布线基本原则与操作

• 各类信号布线注意事项及布线技巧

– 差分信号

40

科通集团

– 添加Anti Etch

47

科通集团

/

Allegro电源地处理

• 电源地平面分割(Negative)

– 添加Anti Etch

48

科通集团

/

Allegro电源地处理

• 电源地平面分割(Negative)

– 接口信号(RJ-45、USB、HDMI等)

• 遵循差分布线原则 • 注意隔离器件(变压器、光耦等)下面不要布线 • 保护地(机壳地)的恰当处理

45

科通集团

/

Allegro电源地处理

• 电源地处理的基本原则

– – – – 载流能力 电源通道和滤波 直流压降参考平面 其他要求(20H、分隔带宽度、电气安全间距)

电源地处理的基本原则 电源地平面分割(Negative) 电源地正片铜皮处理 电源地处理的其他注意事项

• Allegro电源地处理(Shape)

2

科通集团

/

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

allegro初级培训教材培训对象:PCB工艺、中试、标准化等部门需要评审PCB和看PCB图的工程师。

培训目标:通过培训,能够把握在Allegro中审PCB图的方法和技巧。

培训内容:➢CADENCE板级设计流程及各模块功能介绍➢板级设计的文件结构及工程的设置➢Allegro中的差不多操作➢Allegro中的PCB可生产性评审➢Allegro中的PCB可测试性评审➢Allegro中的PCB文件打印和文件的输出CADENCE板级设计流程及各模块功能介绍1.1概述CADENCE Design Systems Inc. 公司是全球最大的EDA厂商之一。

具有EDA全线产品,包括系统顶层设计及仿真、信号处理、电路设计及仿真、PCB设计及分析、FPGA 及ASIC设计以及深亚微米IC设计等。

其中:电路设计及仿真、PCB设计及分析属于板级设计范畴。

板级设计初始界面- Project Manager,如图1。

图1:Project Manager界面1.2差不多模块功能介绍1.2.1Project Manager - 工程(项目)治理工具Project Manager 是CADENCE板级设计工具治理器,是板级设计工具的整合环境。

由此能够启动板级设计的所有模块。

如:Concept HDL - 原理图设计输入工具Allegro - PCB设计系统SpectraQuest SI Expert - 高速电路板系统设计和分析Part Developer - 原理图库建库工具(从Tools – Library Tools -- Part Developer 进入)1.2.2Concept HDL - 原理图设计输入工具Concept HDL 是一个完整的混合级设计输入工具,能够用多种方式输入设计信息。

支持行为级和结构级的输入方式;支持Top-Down 设计;Concept HDL 与Allegro 紧密集成。

图2为Concept HDL界面。

图2:Concept HDL界面1.2.3Allegro - PCB设计系统Allegro 依照价格有多种配置。

如:Allegro Expert -- PCB设计专家系统;Allegro Designer - PCB设计系统;PCB Design Studio -- PCB设计工具Allegro Expert -- PCB设计专家系统的功能:➢能够同时处理48个信号层,无限制绘图层。

➢能够进行SI、EMC、可测试性、可生产性等的在线分析。

➢对预先设置的规则进行自动检查。

➢有效的自动交互布局。

➢与Spectra 自动布线器无缝连接,实现基于形状的无网格布线功能。

➢能够输出多种生产加工数据,包括标准Gerber 文件,多种光绘机文件,D码表,装配图,测试针床数据,帖片机数据等等。

➢具有其它通用PCB设计工具,以及CAD设计工具的接口。

图3为Allegro Expert的界面。

图3:Allegro界面1.2.4Part Developer - 原理图库建库工具Part Developer是原理图库建库工具。

界面见图4。

图4:Part Developer界面2.板级设计的文件结构及工程的设置CADENCE的板级设计采纳工程或项目(Project)式的文件结构。

名目及设置文件的构成如图5。

图5:板级设计名目及设置文件的构成当工程名目位置发生改变时,如设计从资料室转移到中试人员机器上,第一应该复原或者修改设置文件,还原设计环境,否则,无法读到完整的原理图。

由于公司的PCB文件包单独归档,只需看PCB文件(*.brd)时,直截了当用Allegro 打开*.brd文件即可,不存在还原设计环境问题。

(不需要启Project Manager。

)3. Allegro中的差不多操作在Allegro中进行PCB的评审时,需要把握以下的差不多操作:3.1界面设置为了能够快捷地操作,应该有效地设置工具条。

举荐的设置如图6:图6:举荐的工具条设置3.2可视性及颜色设置可视性及颜色设置通过进入。

如图7。

图7:可视性及颜色设置Allegro 按照项目的属性分为7个Group。

看图常用以下4个Group:Geometry -- 器件外型的显示及丝印等Manufacturing -- 测试点标识(Probe-Bottom),孔径标识(Ncdrill-Figure),孔径表(Ncdrill-Legend)等等Stack-up -- 电路层、焊盘、过孔等等Component -- 器件位号的显示及丝印等3.3屏幕操作图形的缩放用以下图标:系统定义功能键:F9 -- 缩小F10 -- 放大滑屏操作:三键鼠标:按住中键,拖动鼠标。

双键鼠标:同时按住两个键,拖动鼠标。

点鼠标右键,可分别选Done、Oops、Cancel ,完成操作、取消上一步操作、取消全部操作。

3.4操纵板如图8,在操纵板中能够:➢对电路层的可视性进行操纵。

➢对过滤器进行操纵。

看图在过过滤器中常用的项为:Comps、Symbols 和Nets。

➢利用全局小窗口,进行导航。

快速定位要查找的项目。

图8:操纵板的使用3.5项目的高亮查找与查询项目的高亮查找:1.图形中,将所有的项目去高亮。

2.点击高亮图标。

3.在过滤器中选需要查找的项目,“>”处键入需查找的内容。

4.利用全局小窗口,进行导航。

能够快速定位要查找的项目。

项目的属性及内容查询:1.点击图标,或按“F5”功能键。

2.在过滤器中选需要查询的项目,“>”处键入需查找的内容,或者直截了当点击项目。

3.在弹出的窗口中显示了内容。

如图9。

图9:项目的属性及内容查询3.6测距利用Allegro中的Display --〉Measure 的功能,结合过滤器中,并合理设置Grid 能够对图进行距离的测量。

图10为对Pin 中心距的测量。

图10:对Pin 中心距的测量4.Allegro中的PCB可生产性评审依照公司的PCB工艺要求和Allegro中功能,能够进行差不多的PCB可生产性评审。

Allegro 无法将实际的器件与PCB封装进行比较来判定焊盘的尺寸与孔径的正确性。

器件封装库由正确的原理图库和封装库保证。

4.1检查设计规则和运行DRC设计规则检查程序4.1.1 检查PCB中的设计规则(Constrain)是否符合公司的工艺要求。

与PCB可生产性有关的规则集要紧是间距,Spacing Rule Set。

从Setup –Constrains 或点击图标进入Constrains System Master。

图11。

图11:Constrains System MasterSet Standards Values…进入板的缺省间距的设置。

当表中显示xx时,表示规则集中有不同的值。

图12。

图12:Default Value Form从图11所示Spacing rule set 的Set values …可进入图13 规则集的设置表。

扫瞄规则集,若设置符合公司的工艺要求,不要改动规则的操纵值。

若有小于公司规定值的项目,将其改为公司的规定值。

图13 :规则集的设置表4.1.2运行DRC设计规则检查程序Tools – Update DRC 运行DRC设计规则检查程序。

在可视性及颜色设置中打开相关的DRC项目,如图14 。

由于电源和地层光绘有专门的处理,其与可生产性评审的关系不大,应将电源和地层的DRC关掉。

图14:DRC的可视性及颜色设置4.1.3解读DRC内容Allegro 检查出PCB与设计规则冲突时,图上会显现DRC错误标记,如图15。

图15:解读DRC需要了解实际值和规则确定的值时,按图16 操作,自动弹出所需了解的信息。

图16:了解实际值和规则确定的值在评审时,应该注意确定那些是真正阻碍PCB可生产性的DRC错误。

4.2回流焊面的布局检查为了高效而准确地检查回流焊面的布局,在PCB图中打开以下颜色:回流焊面的丝印和Place-Bound-top/bottom、焊盘、Package-top DRC (或Package-bottom DRC)。

成效如图17 。

图17:回流焊面的布局检查当有器件间距冲突时,图中有以下标志。

由于PCB上常有预留的调试用测试点,如焊示波器探头夹针等,或者有备用器件,评审时注意判别问题的真伪。

由于公司不是所有的事业部在设计PCB封装时,就差不多将公司工艺对器件的间距要求设计到了封装库的Place-Bound-Top 层。

(如图18:CDMA事业部的PBGA封装,Place-Bound-Top 比器件体外扩了5毫米。

)因此,该项DRC检查只能依照库的准确情形作为参考。

随着公司的设计规范不断完善,依靠软件操纵设计的可生产性将能够实现。

图18:考虑了间距要求的PBGA封装库4.3波峰焊面的布局检查在PCB图中打开以下颜色:波峰焊面的丝印和Place-Bound-top/bottom、焊盘、Package-top DRC (或Package-bottom DRC)。

成效如图19 。

图19:波峰焊面的布局检查除依照上一条的方法检查间距之外,波峰焊面还应该检查器件的方向,器件较少时能够采纳目测的方法。

器件较多时能够用DFA Check 中的Component-orientation-layer-audit 来检查。

方法及设置见图20 。

(要依照板的实际情形设置。

)运行Run Audit 即可图20 :器件的方向检查4.4器件位号、极性标识、第1脚标识在PCB图中打开以下颜色:元件面或焊接面丝印、焊盘、过孔的绿油层。

高亮所有器件的第1脚。

操纵板的设置和显示成效如图21 。

图21:目测检查器件位号、极性标识、第1脚标识在图形中目测检查器件位号、极性标识、第1脚标识是否符合公司的要求。

4.5布线间距检查方法差不多在4.1 中介绍。

4.6绿油开窗在PCB图中打开以下颜色:焊盘、过孔、相应的焊盘和过孔绿油层(Sold层)、丝印层。

在Setup – Drawing Options – Display 中关闭Filled pads and cline endcaps ,显示成效如图22 。

目测绿油的开窗是否和符公司要求。

图22:绿油开窗的检查4.7光学定位标识快速检查光学定位标识的方法:➢打开元件面或焊接面丝印、焊盘、焊盘的绿油开窗。

在Setup – Drawing Options –Display 中关闭Filled pads and cline endcaps ;➢高亮光学定位标识的封装(如:CMAD 用MR*)显示成效如图23 。

图23:快速检查光学定位标识➢目测光学定位标识的数量和位置。

4.8条码框及板名/编号打开元件面丝印和元件面的Etch ,目测条码框及板名/编号是否符合公司要求。