大容量FlashROM存储器使用说明

ATmega16 的EEPROM的使用

ATmega16 包含512 字节的EEPROM 数据存储器。

它是作为一个独立的数据空间而存在的,可以按字节读写。

EEPROM 的寿命至少为100,000 次擦除周期。

EEPROM 的访问由地址寄存器、数据寄存器和控制寄存器决定。

通过SPI和JTAG及并行电缆下载EEPROM数据的操作请分别参见P260、P265及P250。

EEPROM 读/ 写访问EEPROM 读/ 写访问EEPROM 的访问寄存器位于I/O 空间。

EEPROM的写访问时间由Table 1给出。

自定时功能可以让用户软件监测何时可以开始写下一字节。

用户操作EEPROM 需要注意如下问题:在电源滤波时间常数比较大的电路中,上电/ 下电时VCC 上升/ 下降速度会比较慢。

此时CPU 可能工作于低于晶振所要求的电源电压。

请参见P20“ 防止EEPROM 数据丢失” 以避免出现EEPROM 数据丢失的问题。

为了防止无意识的EEPROM 写操作,需要执行一个特定的写时序。

具体参看EEPROM控制寄存器的内容。

执行EEPROM 读操作时,CPU 会停止工作4 个周期,然后再执行后续指令;执行EEPROM 写操作时,CPU 会停止工作2 个周期,然后再执行后续指令。

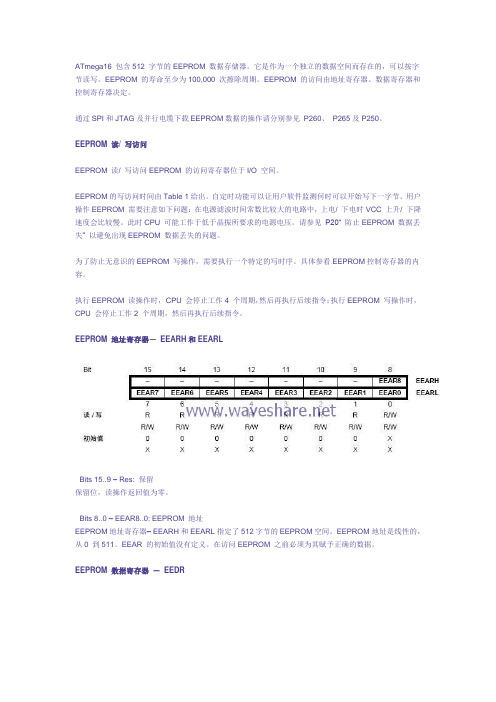

EEPROM 地址寄存器-EEARH和EEARL· Bits 15..9 – Res: 保留保留位,读操作返回值为零。

· Bits 8..0 – EEAR8..0: EEPROM 地址EEPROM地址寄存器– EEARH和EEARL指定了512字节的EEPROM空间。

EEPROM地址是线性的,从0 到511。

EEAR 的初始值没有定义。

在访问EEPROM 之前必须为其赋予正确的数据。

EEPROM 数据寄存器-EEDR· Bits 7..0 – EEDR7.0: EEPROM 数据对于EEPROM 写操作,EEDR 是需要写到EEAR 单元的数据;对于读操作,EEDR 是从地址EEAR 读取的数据。

内部存储器RAM和ROM使用说明

内部存储器RAM和ROM用户指南

1、介绍内部存储器模块

本用户指南介绍了实现以下内存模式的宏功能:

■RAM:1-Port—Single-port RAM 单口RAM

■RAM:2-Port—Dual-port RAM 双口RAM

■ROM:1-Port—Single-port ROM 单口ROM

■ROM:2-Port—Dual-port ROM 双口ROM

Altera公司提供了两种宏功能来实现内存模式:ALTSYNCRAM和ALTDPRAM 宏功能。

QuartusII软件会自动选择其中一个宏功能来实现内存模式。

选择那种宏功能模式取决于目标器件,存储器模式和RAM和ROM的功能。

本用户指南会让您熟悉宏功能,以及如何创建它们。

如果您不熟悉的Altera 宏功能或“the MegaWizard™ Plug-In Manager”,请参阅介绍宏功能用户指南。

内部存储器具有如下功能:

■内存模式配置

■存储模块类型

■端口宽度设置

■存储器最大深度设置

■时钟模式和时钟使能

■地址时钟使能

■字使能

■异步清零

■读使能

■同时读写

■存储器初始化

■错误校正码

2、参数设置

Altera建议您使用参数编辑器来配置来构建您的RAM和ROM内存块,以确保您所选择的选项组合是有效的。

下表是双口RAM参数设置。

flash otp区域使用方法

flash otp区域使用方法Flash OTP(一次性可编程只读存储器)区域在现代电子设备中起着重要作用,尤其在安全领域。

本文将详细介绍Flash OTP区域的使用方法,帮助读者更好地理解并应用这一技术。

一、Flash OTP简介Flash OTP是一种一次性可编程只读存储器,其特点是在编程后数据不可更改,具有很高的安全性。

Flash OTP广泛应用于各类安全认证场景,如智能卡、加密狗、安全芯片等。

二、Flash OTP区域使用方法1.初始化在使用Flash OTP区域之前,首先需要对其进行初始化。

初始化过程通常包括以下步骤:a.设置编程电压:根据Flash OTP器件的规格,调整编程电压。

b.提供编程指令:向Flash OTP发送特定的编程指令,使其进入编程模式。

c.擦除操作:在编程前,需要先擦除Flash OTP区域,使其全部位变为1。

2.编程初始化完成后,可以对Flash OTP区域进行编程。

编程过程如下:a.写入数据:将需要存储的数据写入Flash OTP区域。

b.校验数据:在写入数据后,对数据进行校验,确保数据正确无误。

c.确认编程:在数据校验无误后,发送确认编程的指令,完成编程过程。

3.使用数据编程完成后,Flash OTP区域中的数据不可更改,可以用于以下场景:a.安全认证:利用Flash OTP存储密钥、证书等敏感信息,实现设备或系统的安全认证。

b.唯一标识:将Flash OTP作为设备的唯一标识,防止非法复制和篡改。

c.参数存储:存储设备运行所需的参数,如生产日期、序列号等。

4.注意事项在使用Flash OTP区域时,需要注意以下几点:a.一次性编程:Flash OTP区域只能编程一次,因此在编程前需确保数据无误。

b.数据安全:保护Flash OTP区域中的数据安全,防止泄露或被非法读取。

c.电压控制:编程过程中,要严格控制编程电压,防止过压或欠压导致编程失败。

三、总结Flash OTP区域的使用方法包括初始化、编程和使用数据等步骤。

rom的使用方法

rom的使用方法ROM(Read-Only Memory)是一种用于存储程序和数据的硬件设备,其内容在制造过程中被写入,因此不可修改。

ROM广泛应用于计算机、手机、游戏机等设备中,它的使用方法如下。

一、ROM的分类ROM可以根据其工作原理和特点进行分类。

常见的ROM类型包括:1. PROM(Programmable Read-Only Memory):可编程只读存储器,用户可以通过特殊设备将数据写入ROM中,但一旦写入后就无法修改。

2. EPROM(Erasable Programmable Read-Only Memory):可擦写可编程只读存储器,用户可以使用紫外线照射来擦除其中的数据,并重新编程。

3. EEPROM(Electrically Erasable Programmable Read-Only Memory):可电擦写可编程只读存储器,用户可以通过电信号来擦除其中的数据,并进行重新编程。

4. Flash ROM:一种非易失性存储器,可通过电信号进行擦写和编程,广泛应用于各种移动设备。

二、ROM的使用方法1. 存储固件:ROM常用于存储设备的固件,如计算机的BIOS(基本输入输出系统),手机的操作系统等。

用户无法直接修改其中的数据,但可以通过更新固件的方式来升级设备的功能和性能。

2. 存储引导程序:ROM中还可以存储设备的引导程序,用于在设备启动时加载操作系统或其他应用程序。

引导程序的作用是初始化设备的硬件环境,并将控制权交给操作系统。

3. 存储数据表:某些设备需要预先存储一些常用的数据表,例如显卡中的字符显示表、颜色表等。

这些数据表通常存储在ROM中,以提高设备的运行效率。

4. 存储嵌入式系统:许多嵌入式系统需要存储一些固定的程序和数据,ROM是一种理想的存储介质。

嵌入式系统通常具有高度稳定性和安全性要求,ROM的只读特性可以确保数据的完整性和安全性。

5. 存储游戏软件:ROM还广泛用于游戏机和电脑游戏软件中。

flash otp区域使用方法

flash otp区域使用方法Flash OTP(一次性可编程只读存储器)区域使用方法Flash OTP区域作为可编程存储器的一种,广泛应用于各类嵌入式系统中。

了解其使用方法,对于开发人员来说具有重要意义。

本文将详细介绍Flash OTP区域的使用方法,帮助您更好地应用这一技术。

一、Flash OTP概述Flash OTP是一种一次性可编程只读存储器,具有可编程、非易失性的特点。

在嵌入式系统中,Flash OTP常用于存储固件、配置信息等。

与普通Flash 存储器相比,OTP具有更高的安全性,因为一旦编程后,数据将无法被修改或擦除。

二、Flash OTP区域使用方法1.选择合适的Flash OTP器件在使用Flash OTP之前,首先要选择合适的器件。

根据项目需求,考虑器件的容量、编程电压、接口类型等因素。

确保所选器件满足系统性能要求。

2.集成开发环境(IDE)配置为了对Flash OTP进行编程,需要使用集成开发环境(IDE)。

以下是配置步骤:(1)安装IDE:根据所选Flash OTP器件,下载并安装相应的集成开发环境。

(2)创建项目:在IDE中创建一个新项目,并选择对应的硬件平台。

(3)导入固件:将需要烧录到Flash OTP区域的固件文件导入到项目中。

3.编程Flash OTP在IDE中完成以下步骤,对Flash OTP进行编程:(1)配置编程器:在IDE中设置编程器参数,如编程电压、擦除方式等。

(2)连接目标板:将编程器与目标板连接,确保连接正确无误。

(3)编程操作:在IDE中执行编程操作,将固件烧录到Flash OTP区域。

4.验证编程结果编程完成后,需要对Flash OTP区域进行验证,确保数据正确烧录。

以下是验证步骤:(1)读取数据:使用IDE或专用工具,读取Flash OTP区域的数据。

(2)比对数据:将读取到的数据与原始固件进行比对,确认数据一致性。

(3)功能测试:对目标板进行功能测试,确保烧录的数据能够正常工作。

什么是ROM,RAM,EPROM,EEPROM,DRAM,Flash,MRAM,RDRAM,各有什么作用

一、什么是ROM,RAM,EPROM,EEPROM,DRAM,Flash,MRAM,RDRAM,各有什么作用什么是ROM,有什么作用简称:ROM 标准:Read Only Memory 中文:只读存储器只读存储器,这种内存 (Memory ) 的内容任何情况下都不会改变,计算机与使用者只能读取保存在这里的指令,和使用储存在ROM的数据,但不能变更或存入资料。

ROM被储存在一个非挥发性芯片上,也就是说,即使.Yco688 { display:none; } 简称:ROM标准:Read Only Memory中文:只读存储器只读存储器,这种内存 (Memory ) 的内容任何情况下都不会改变,计算机与使用者只能读取保存在这里的指令,和使用储存在ROM的数据,但不能变更或存入资料。

ROM被储存在一个非挥发性芯片上,也就是说,即使在关机之后记忆的内容仍可以被保存,所以这种内存多用来储存特定功能的程序或系统程序。

ROM储存用来激活计算机的指令,开机的时候ROM提供一连串的指令给中央处理单元进行测试,在最初的测试中,检查RAM位置(location)以确认其储存数据的能力。

此外其它电子组件包括键盘 (Keyboard ) 、计时回路(timer circuit)以及CPU本身也被纳入CPU的测试中。

什么是RAM,有什么作用简称:RAM标准:Random Access Memory中文:随机存储器随机存取内存,是内存(Memory)的一种,由计算机CPU控制,是计算机主要的储存区域,指令和资料暂时存在这里。

RAM是可读可写的内存,它帮助中央处理器 (CPU ) 工作,从键盘 (Keyboard ) 或鼠标之类的来源读取指令,帮助CPU 把资料 (Data) 写到一样可读可写的辅助内存 (Auxiliary Memory) ,以便日后仍可取用,也能主动把资料送到输出装置,例如打印机、显示器。

RAM的大小会影响计算的速度,RAM越大,所能容纳的资料越多,CPU读取的速度越快。

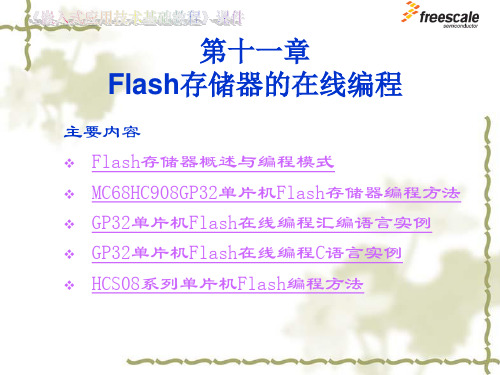

Flash存储器概述与编程模式.

② 擦除及写入子程序中要调用的延时子程序均随其后,以便同时 复制到RAM中,最后一个标号是为复制方便而加入.

③ 擦除及写入子程序中对延时子程序的调用必需使用“BSR 子程 序名”,而不能使用 “JSR 子程序名”,因为这里的子程序是复制 到RAM中执行,程序地址已经发生了变化,只能用相对调用。

11.1.2 M68HC08系列单片机Flash存储器的特点 与编程模式

(1)M68HC08系列单片机Flash存储器的特点

第一,编程速度快及可靠性高。 第二,单一电源电压供电。 第三,支持在线编程。

11.1 Flash存储器概述与编程模式

(2)M68HC08系列单片机Flash存储器的编程模式

11.2 GP32 Flash存储器编程方法

(3)编程操作

MC68HC908GP32的Flash编程操作以行(64字节)为单位进行的。写入 过程如下:

⑴ $1→FLCR(1→PGM位); ⑵ 读Flash块保护寄存器FLBPR; ⑶ 向将要写入的Flash行内任意一个地址写入任意值,为方便起见,一般向 行首地址写入0,这一步选定了所要编程的行,以下的目标地址必需在这一行中; ⑷ 延时tnvs(>10μs); ⑸ $9→FLCR(1→HVEN位); ⑹ 延时tpgs(>5μs); ⑺ 待写数据写入对应的Flash地址; ⑻ 延时tprog(>30μs),完成一个字节的写入(编程)工作; ⑼ 重复⑺、⑻,直至同一行内各字节写入完毕; ⑽ $8→FLCR(0→PGM位); ⑾ 延时tnvh(>5μs); ⑿ $0→FLCR(0→HVEN位); ⒀ 延时trcv(>1μs)以后,完成本行写入工作,可以读出校验。

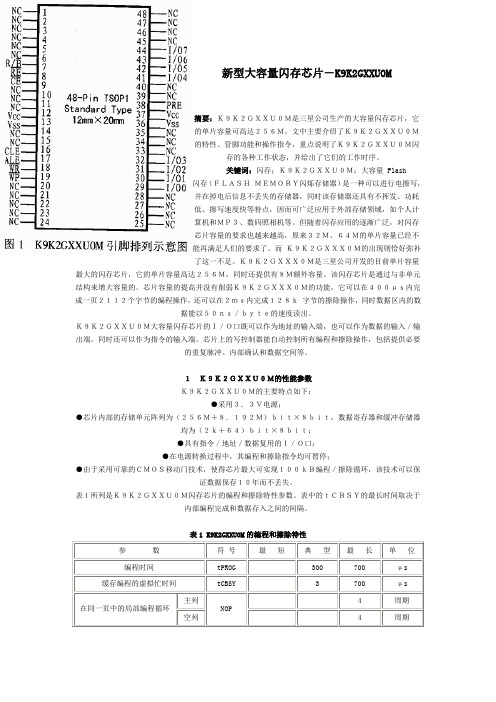

新型大容量闪存芯片K9K2GXXU0M

新型大容量闪存芯片-K9K2GXXU0M摘要:K9K2GXXU0M是三星公司生产的大容量闪存芯片,它的单片容量可高达256M。

文中主要介绍了K9K2GXXU0M的特性、管脚功能和操作指令,重点说明了K9K2GXXU0M闪存的各种工作状态,并给出了它们的工作时序。

关键词:闪存;K9K2GXXU0M;大容量 Flash闪存(FLASHMEMORY闪烁存储器)是一种可以进行电擦写,并在掉电后信息不丢失的存储器,同时该存储器还具有不挥发、功耗低、擦写速度快等特点,因而可广泛应用于外部存储领域,如个人计算机和MP3、数码照相机等。

但随着闪存应用的逐渐广泛,对闪存芯片容量的要求也越来越高,原来32M、64M的单片容量已经不能再满足人们的要求了。

而K9K2GXXX0M的出现则恰好弥补了这一不足。

K9K2GXXX0M是三星公司开发的目前单片容量最大的闪存芯片,它的单片容量高达256M,同时还提供有8M额外容量。

该闪存芯片是通过与非单元结构来增大容量的。

芯片容量的提高并没有削弱K9K2GXXX0M的功能,它可以在400μs内完成一页2112个字节的编程操作,还可以在2ms内完成128k字节的擦除操作,同时数据区内的数据能以50ns/byte的速度读出。

K9K2GXXU0M大容量闪存芯片的I/O口既可以作为地址的输入端,也可以作为数据的输入/输出端,同时还可以作为指令的输入端。

芯片上的写控制器能自动控制所有编程和擦除操作,包括提供必要的重复脉冲、内部确认和数据空间等。

1K9K2GXXU0M的性能参数K9K2GXXU0M的主要特点如下:●采用3.3V电源;●芯片内部的存储单元阵列为(256M+8.192M)bit×8bit,数据寄存器和缓冲存储器均为(2k+64)bit×8bit;●具有指令/地址/数据复用的I/O口;●在电源转换过程中,其编程和擦除指令均可暂停;●由于采用可靠的CMOS移动门技术,使得芯片最大可实现100kB编程/擦除循环,该技术可以保证数据保存10年而不丢失。

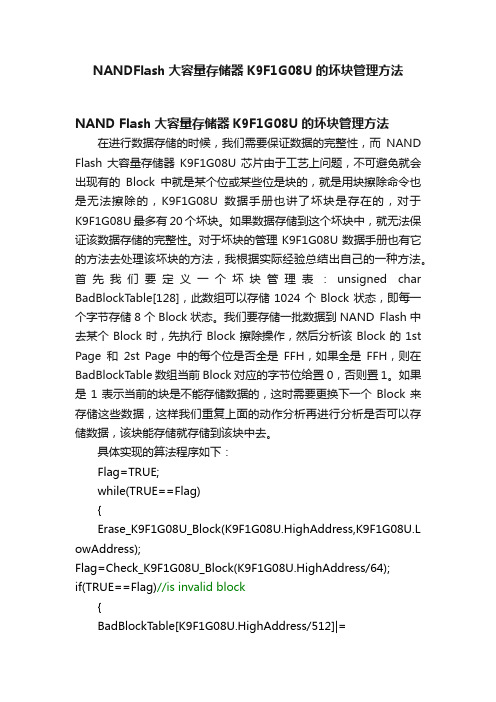

NANDFlash大容量存储器K9F1G08U的坏块管理方法

NANDFlash大容量存储器K9F1G08U的坏块管理方法NAND Flash大容量存储器K9F1G08U的坏块管理方法在进行数据存储的时候,我们需要保证数据的完整性,而NAND Flash大容量存储器K9F1G08U芯片由于工艺上问题,不可避免就会出现有的Block中就是某个位或某些位是块的,就是用块擦除命令也是无法擦除的,K9F1G08U数据手册也讲了坏块是存在的,对于K9F1G08U最多有20个坏块。

如果数据存储到这个坏块中,就无法保证该数据存储的完整性。

对于坏块的管理K9F1G08U数据手册也有它的方法去处理该坏块的方法,我根据实际经验总结出自己的一种方法。

首先我们要定义一个坏块管理表:unsigned char BadBlockTable[128],此数组可以存储1024个Block状态,即每一个字节存储8个Block状态。

我们要存储一批数据到NAND Flash中去某个Block时,先执行Block擦除操作,然后分析该Block的1st Page和2st Page中的每个位是否全是FFH,如果全是FFH,则在BadBlockTable数组当前Block对应的字节位给置0,否则置1。

如果是1表示当前的块是不能存储数据的,这时需要更换下一个Block来存储这些数据,这样我们重复上面的动作分析再进行分析是否可以存储数据,该块能存储就存储到该块中去。

具体实现的算法程序如下:Flag=TRUE;while(TRUE==Flag){Erase_K9F1G08U_Block(K9F1G08U.HighAddress,K9F1G08U.L owAddress);Flag=Check_K9F1G08U_Block(K9F1G08U.HighAddress/64);if(TRUE==Flag)//is invalid block{BadBlockTable[K9F1G08U.HighAddress/512]|=(1<<(K9F1G08U.HighAddress%8));K9F1G08U.HighAddress+=64;//Point to Next Block}else// is valid block ,record to BadBlockTable{BadBlockTable[K9F1G08U.HighAddress/512]&=~(1<<(K9F1G08U.HighAddress%8));}}for(i=0;i<sizeof(BadBlockTable);i++)Write_RAM(RAM_BANK_0,K9F1G08U_BAD_BLOCK+i,BadBlo ckTable[i]);。

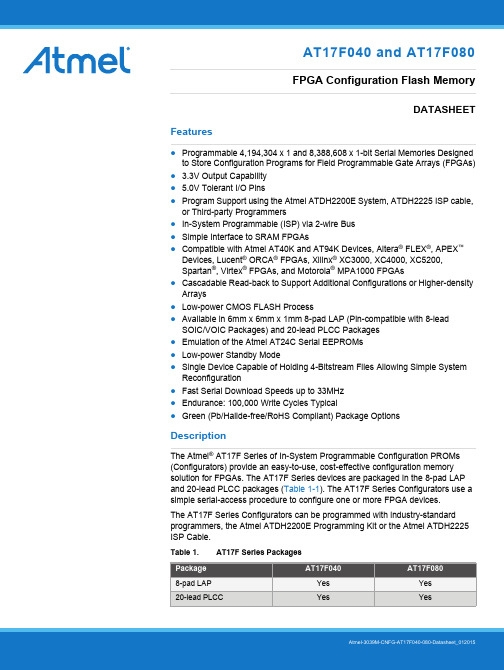

Atmel 3039M-CNFG AT17F040-080 配置FLASH存储器数据手册说明书

AT17F040 and AT17F080FPGA Configuration Flash MemoryDATASHEET Features●Programmable 4,194,304 x 1 and 8,388,608 x 1-bit Serial Memories Designedto Store Configuration Programs for Field Programmable Gate Arrays (FPGAs)● 3.3V Output Capability● 5.0V Tolerant I/O Pins●Program Support using the Atmel ATDH2200E System, ATDH2225 ISP cable,or Third-party Programmers●In-System Programmable (ISP) via 2-wire Bus●Simple Interface to SRAM FPGAs●Compatible with Atmel AT40K and AT94K Devices, Altera® FLEX®, APEX™Devices, Lucent® ORCA® FPGAs, Xilinx® XC3000, XC4000, XC5200,Spartan®, Virtex® FPGAs, and Motorola® MPA1000 FPGAs●Cascadable Read-back to Support Additional Configurations or Higher-densityArrays●Low-power CMOS FLASH Process●Available in 6mm x 6mm x 1mm 8-pad LAP (Pin-compatible with 8-leadSOIC/VOIC Packages) and 20-lead PLCC Packages●Emulation of the Atmel AT24C Serial EEPROMs●Low-power Standby Mode●Single Device Capable of Holding 4-Bitstream Files Allowing Simple SystemReconfiguration●Fast Serial Download Speeds up to 33MHz●Endurance: 100,000 Write Cycles Typical●Green (Pb/Halide-free/RoHS Compliant) Package OptionsDescriptionThe Atmel® AT17F Series of In-System Programmable Configuration PROMs (Configurators) provide an easy-to-use, cost-effective configuration memory solution for FPGAs. The AT17F Series devices are packaged in the 8-pad LAP and 20-lead PLCC packages (Table 1-1). The AT17F Series Configurators use a simple serial-access procedure to configure one or more FPGA devices.The AT17F Series Configurators can be programmed with industry-standard programmers, the Atmel ATDH2200E Programming Kit or the Atmel ATDH2225 ISP Cable.Table 1.AT17F Series PackagesAT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_01201521.Pin ConfigurationsTable 1-1.Pin DescriptionsNotes:1.Internal 20K Ω pull-up resistor2.Internal 30K Ω pull-up resistor3AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_012015Table 1-2.Address Space PAGESEL[1:0]Table 1-3.Pin ConfigurationsFigure 1-1.PinoutsNote: Drawings are not to scale.43215678DATA CLKRESET/OECEV CCSER_EN CEO (A2)GND8-pad LAP(Top View)20-lead PLCC(Top View)CLK NCRESET/OE PAGESEL1CE456781817161514N CG N DP A G E S E L 0N CN CN CD A T AN CV C CN C3212019910111213NC SER_EN PAGE_EN READY CEO (A2)AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_01201542.Block DiagramFigure 2-1.Block DiagramCLKCEO(A2)DATAREADYPAGE_EN PAGESEL0PAGESEL1CERESET/OE SER_EN5AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_0120153.Device DescriptionThe control signals for the configuration memory device (CE, RESET/OE and CLK) interface directly with the FPGA device control signals. All FPGA devices can control the entire configuration process and retrieve data from the configuration device without requiring an external intelligent controller.The RESET/OE and CE pins control the tri-state buffer on the DATA output pin and enable the address counter. When RESET/OE is driven Low, the configuration device resets its address counter and tri-states its DATA pin. The CE pin also controls the output of the AT17F Series Configurator. If CE is held High after the RESET/OE reset pulse, the counter is disabled and the DATA output pin is tri-stated. When OE is subsequently driven High, the counter and the DATA output pin are enabled. When RESET/OE is driven Low again, the address counter is reset and the DATA output pin is tri-stated, regardless of the state of CE.When the configurator has driven out all of its data and CEO is driven Low, the device tri-states the DATA pin to avoid contention with other configurators. Upon power-up, the address counter is automatically reset.4.FPGA Master Serial Mode SummaryThe I/O and logic functions of any SRAM-based FPGA are established by a configuration program. The program is loaded either automatically upon power-up or on command, depending on the state of the FPGA mode pins. In Master mode, the FPGA automatically loads the configuration program from an external memory. The AT17F Serial Configuration PROM has been designed for compatibility with the Master Serial mode.This document discusses the Atmel AT40K, AT40KAL and AT94KAL applications as well as Xilinx applications.5.Control of ConfigurationMost connections between the FPGA device and the AT17F Serial Configurator PROM are simple and self-explanatory.●The DATA output of the AT17F Series Configurator drives DIN of the FPGA devices.●The master FPGA CCLK output drives the CLK input of the AT17F Series Configurator.●The CEO output of any AT17F Series Configurator drives the CE input of the next Configurator in a cascade chain of configurator devices.●SER_EN must be connected to V CC (except during ISP).●The READY pin is available as an open-collector indicator of the device’s reset status; it is driven Low while the device is in its power-on reset cycle and released (tri-stated) when the cycle is complete.●PAGE_EN must be held Low if download paging is not desired. The PAGESEL[1:0] inputs must be tied off High or Low. If paging is desired, PAGE_EN must be High and the PAGESEL pins must be set to High or Low such that the desired page is selected (Table 1-2).6.Cascading Serial Configuration DevicesFor multiple FPGAs configured as a daisy-chain or for FPGAs requiring larger configuration memories, cascaded configurators provide additional memory.After the last bit from the first configurator is read, the clock signal to the configurator asserts its CEO output Low and disables its DATA line driver. The second configurator recognizes the Low level on its CE input and enables its DATA output.After configuration is complete, the address counters of all cascaded configurators are reset if the RESET/OE on each configurator is driven to its active (Low) level.If the address counters are not to be reset upon completion, then the RESET/OE input can be tied to its inactive (High) level.AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_01201567.Programming ModeThe programming mode is entered by bringing SER_EN Low. In this mode, the chip can be programmed by the 2-wire serial bus. The programming is done at V CC supply only. Programming super voltages are generated inside the chip. The AT17F parts are read/write at 3.3V nominal. Refer to the AT17F Programming Specification available on for more programming details. AT17F devices are supported by the ATDH2200 programming system along with many third party programmers.8.Standby ModeThe AT17F Series Configurators enter a low-power standby mode whenever SER_EN is High and CE is asserted High. In this mode, the AT17F Configurator consumes less than 1mA of current at 3.3V. The output remains in a high-impedance state regardless of the state of the OE input.7AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_0120159.Electrical Characteristics9.1Absolute Maximum Ratings*9.2Operating ConditionsTable 9-1.Operating Conditions 9.3DC CharacteristicsTable 9-2.DC CharacteristicsOperating Temperature . . . . . . . . . . . . . . . . . . . -40︒C to +85︒C Storage Temperature. . . . . . . . . . . . . . . . . . . . -65︒C to +150︒C Voltage on Any Pinwith Respect to Ground . . . . . . . . . . . . . . . . .-0.1V to V CC +0.5V Supply Voltage (V CC ) . . . . . . . . . . . . . . . . . . . . . . -0.5V to +4.0V Maximum Soldering Temp. (10 sec. @ 1/16in.). . . . . . . . .260︒C ESD (R ZAP = 1.5K, C ZAP = 100pF) . . . . . . . . . . . . . . . . . . 2000V*Notice:Stresses beyond those listed underAbsolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those listed under operating conditions is not implied. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect device reliability.AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_01201589.4AC CharacteristicsTable 9-3.AC CharacteristicsNotes:1.AC test load = 50pF2.Float delays are measured with 5pF AC loads. Transition is measured ± 200mV from steady-state active levels.3.See the Atmel AT17F Programming Specification for procedural information.Table 9-4.AC Characteristics When Cascading2.Float delays are measured with 5pF AC loads. Transition is measured ± 200mV from steady-state active levels.9AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_012015Figure 9-1.AC WaveformsFigure 9-2.AC Waveforms when CascadingCERESET/OECLKDATACERESET/OECLKDATACEOAT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_0120151010.Ordering Information10.1Ordering Code Detail10.2Ordering InformationA T 17F 040-30C UAtmel DesignatorProduct FamilyDevice DensityPackage OptionProduct Variation040 = 4 megabit 080 = 8 megabit17F = FPGA Flash Configuration MemoryPackage Device GradeC = 8-pad LAP J = 20-lead PLCCU = Green, Sn Lead FinishIndustrial Temperature Range (-40°C to +85°C)30 = Default Value11AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_01201511.Packaging Information11.18CN4 — 8-pad LAPAT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_0120151211.220J — 20-lead PLCC13AT17F040/080 [DATASHEET]Atmel-3039M-CNFG-AT17F040-080-Datasheet_01201512.Revision HistoryX X X X X XAtmel Corporation1600 Technology Drive, San Jose, CA 95110 USAT: (+1)(408) 441.0311F: (+1)(408) 436.4200|© 2015 Atmel Corporation. / Rev.: Atmel-3039M-CNFG-AT17F040-080-Datasheet_012015.Atmel ®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities ®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended,authorized, or warranted for use as components in applications intended to support or sustain life.SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems.Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.。

flashrom用法

flashrom用法Flashrom是一款用于闪存芯片擦除、写入和读取的工具。

以下是Flashrom的主要用法:1. 确定芯片类型和接口类型:在选择编程器和工具时,需要先确定芯片类型和接口类型。

2. 闪存芯片操作:Flashrom支持擦除、写入和读取操作。

在写入之前,需要先擦除芯片,然后再将新内容写入芯片中。

读取芯片中的内容可以帮助用户备份和恢复固件。

3. 内存映射:Flashrom还支持内存映射,可以将闪存芯片的部分或全部区域映射到系统内存中,然后进行读写操作。

这种方法允许用户直接访问和修改闪存芯片中的内容,而不必使用编程器。

4. 安装:对于一些流行的Linux发行版,可以通过自身的包管理器来安装Flashrom。

例如,Debian/Ubuntu用户可以使用`sudo apt-get install flashrom`命令进行安装,Fedora用户可以使用`sudo yum install flashrom`命令进行安装。

如果无法通过包管理器安装,可以选择手动编译安装。

5. 检测:除了通过Flashrom官方主页查询是否支持当前的主板和芯片之外,还可以直接使用Flashrom工具进行检测。

执行`flashrom`指令后,Flashrom将输出类似下面的信息,以表明检测结果。

6. 备份和刷写:如果想把当前的BIOS映像备份下来,可以使用`flashrom -r bios_`命令进行备份。

同样地,Flashrom也提供读取操作,帮助用户备份和恢复固件。

如果需要刷写新的BIOS,可以执行相应的命令进行操作。

以上信息仅供参考,如需了解更多关于Flashrom的用法,建议咨询专业人士或查阅相关论坛教学资料。

C8051F的超大容量Flash存储器扩展

C8051F的超大容量Flash存储器扩展摘要:NAND结构Flash数据存储器件是超大容量数据存储的理想选择,当前被广泛应用于U 盘、MP3和数码相机的数据存储。

本文对该类型Flash的基本操作进行研究并对实际应用系统给予验证,揭示了NAND结构Flash的操作规律。

引言大容量数据存储是单片机应用系统的瓶颈,受到容量、功耗、寻址方式的约束。

突破容量限制,可以很大程度上扩展和提高应用系统的总体功能。

Sumsung公司的NAND结构Flash 存储器件是一款性价比很高的超大容量数据存储器件,在MP3、U盘、数码相机和PDA中有广泛的应用,且市场占有份额逐年加大。

用该器件作为各种单片机尤其是嵌入式系统的数据存储器,可以完美地解决容量限制,实现灵活操作,势必成为数据存储的主流方向。

1 器件介绍NAND结构Flash是Sumsung公司隆重推出并着力开发的新一代数据存储器件,电源电压1.7~3.6V,体积小,功耗低,容量最大可达1GB,按页进行读写,按块擦除,通过I/O口分时复用作为命令/地址/数据。

本次应用开发的是NAND结构16MB的K9F2808UOB,其它大容量的器件只比该型号送出的地址多了几字节,操作指令和时序相同。

具体结构说明。

由图1可知,该器件由1K个块(block)组成,每个块有32页,每页有528字节,这528字节分成A、B、C三个区。

对每一页的寻址需要通过I/O口送出三个地址,第二、三行地址(A9~A23)指明寻址到某一页,第一列地址指明寻址到页的指定区中某一字节。

对页的分区命令如表1所列。

表1 起始指针位置与区域关系对照表命令指针位置/字节区域 00H 0~255 阵列第一伴(A) 01H 256~511 阵列第二半(B) 50H 512~527 剩余阵列(C)由表1可以看出,00H、01H、50H只是选区指针。

选定区的内部寻址是由第一个列地址完成的,A0~A7可以最大寻址256字节。

flash memory分类以及使用方法。

Flash Memory分类及使用方法一、引言在数字化时代,我们所使用的各种电子设备中,都离不开存储设备,其中一种常见的存储设备就是Flash Memory。

Flash Memory因其高速读写、便携性和高存储密度而备受青睐,广泛应用于闪存卡、固态硬盘、移动设备等领域。

本文将对Flash Memory进行全面评估,并探讨其分类和使用方法,以便读者能全面、深刻、灵活地理解这一主题。

二、Flash Memory分类1. 按照存储介质分类Flash Memory根据其存储介质不同可分为两类:NAND Flash和NOR Flash。

NAND Flash主要用于大容量数据存储,如固态硬盘;而NOR Flash则用于小容量数据存储,如闪存卡。

2. 按照接口分类根据接口的不同,Flash Memory可分为SATA接口、PCIe接口和USB接口。

其中,SATA接口适用于固态硬盘,PCIe接口适用于高性能存储设备,USB接口适用于便携性较强的闪存盘和移动设备。

3. 按照存储类型分类根据存储类型的不同,Flash Memory可分为SLC(Single-LevelCell)、MLC(Multi-Level Cell)和TLC(Triple-Level Cell)。

SLC 存储密度低,但读写速度快,寿命长;MLC存储密度中等,价格适中;TLC存储密度高,价格低廉,但寿命相对较短。

三、Flash Memory的使用方法1. 选择适合的存储介质根据实际需求,选择NAND Flash或NOR Flash,以满足不同的存储需求。

2. 根据设备接口选择Flash Memory在选购Flash Memory时,要根据设备的接口来选购,确保Flash Memory能够与设备兼容并发挥最佳性能。

3. 注意数据传输速度和读写次数在使用过程中,要注意Flash Memory的数据传输速度和读写次数,避免因频繁读写导致存储器老化。

4. 合理使用存储空间在使用Flash Memory时,要合理利用存储空间,避免存储碎片和浪费存储资源。

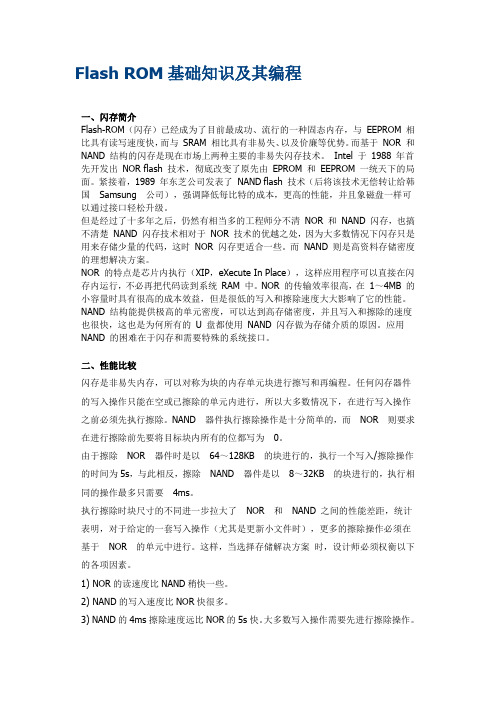

Flash ROM基础知识及其编程

Flash ROM基础知识及其编程一、闪存简介Flash-ROM(闪存)已经成为了目前最成功、流行的一种固态内存,与EEPROM 相比具有读写速度快,而与SRAM 相比具有非易失、以及价廉等优势。

而基于NOR 和NAND 结构的闪存是现在市场上两种主要的非易失闪存技术。

Intel 于1988 年首先开发出NOR flash 技术,彻底改变了原先由EPROM 和EEPROM 一统天下的局面。

紧接着,1989 年东芝公司发表了NAND flash 技术(后将该技术无偿转让给韩国Samsung公司),强调降低每比特的成本,更高的性能,并且象磁盘一样可以通过接口轻松升级。

但是经过了十多年之后,仍然有相当多的工程师分不清NOR 和NAND 闪存,也搞不清楚NAND 闪存技术相对于NOR 技术的优越之处,因为大多数情况下闪存只是用来存储少量的代码,这时NOR 闪存更适合一些。

而NAND 则是高资料存储密度的理想解决方案。

NOR 的特点是芯片内执行(XIP,eXecute In Place),这样应用程序可以直接在闪存内运行,不必再把代码读到系统RAM 中。

NOR 的传输效率很高,在1~4MB 的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。

NAND 结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快,这也是为何所有的U 盘都使用NAND 闪存做为存储介质的原因。

应用NAND 的困难在于闪存和需要特殊的系统接口。

二、性能比较闪存是非易失内存,可以对称为块的内存单元块进行擦写和再编程。

任何闪存器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。

NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。

由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。

存储器-RAM、ROM、PROM、EPROM、EEPROM、FLASH

存储器-RAM、ROM、PROM、EPROM、EEPROM、FLASH1. RAMRAM: Random Access Memroy,随机访问存储器,典型代表:内存条。

特点:要是做运⾏时数据存储器,在掉电之后丢失数据。

分类:SRAM,DRAM.2. ROMROM: Read-Only Memory, 只读存储器特点:ROM数据不能随意更新,但是在任何时候都可以读取,断电之后仍保存数据。

往ROM中注⼊数据需要另外的编译器,PC上⾯没有这个功能,⼀般在ROM出⼚前注⼊信息,依次写⼊,永久保存,不能进⾏修改。

在微机发展初期,BIOS都存放在ROM中。

3.PROMPROM: Programmable Read-Only Memory 可编程只读存储器PROM只允许写⼊⼀次,所以也被称为:“⼀次可编程只读存储器”,出⼚时存储器的内容全为1,⽤户可以⾃⼰往⾥写数据,但只能写⼊⼀次,写错了也就废了。

4. EPROMEPROM: Erasable Programmable Read-Only Memroy 可擦写可编程只读存储器⽤户可以⾃⼰往⾥写数据,写错了可以可擦除然后重新写⼊。

但是写⼊⽐较费劲,需要使⽤紫外线照射⼀段时间。

5. EEPROMEEPROM: Electricall Erasable Programmable Read-Only Memory 带电可擦除可编程只读存储器最⼤的优点是直接⽤电信号擦除,写⼊⽅便,写⼊时以byte为最⼩修改单位,也不必全部擦除重写。

6. Flash ROM具备 RAM 和 ROM 的优点,⼜称闪存,是在EEPROM基础上的改进产品,与EEPROM不同的是,最⼩修改单位不是byte,⽽是块(block),block⼤⼩是⼚家定的。

近些年已逐步取代EEPROM,⼴泛⽤于主板的BIOS ROM。

另外还主要⽤于U盘,MP3等需要⼤容量且断电后不丢失数据的设备。

分类:Nor Flash,Nand Flash.NOR Flash 的读取和我们常见的SDRAM 的读取是⼀样,⽤户可以直接运⾏装载在NOR FLASH ⾥⾯的代码,这样可以减少SRAM 的容量从⽽节约了成本。

Flash EPROM AT29C040A的性能及其使用

*(# *($

器件数据保护的进入和退出算法( 见图 * ) 自举模块编程锁定激活算法( 见图 * )

将数据 @@D 装入地址 $$$D 将数据 A+D 装入地址 $$$D

将数据 $$D 装入地址 *@@@D

将数据 @@D 装入地址 $$$D

( 软件保护。 $) # 器件操作 *(: 功能表 功能表如表 :。 表 : @>*";+#+@ 的功能表

:(!

@>*";+#+@ 具 有 硬 件 和 软 件 两 方 面 的 数 据 保

护, 防止其内容免遭意外改写, 数据保护采取如下 措施。 所有的控制线输入都有滤波电路, 以滤除 ( :) 脉宽在 :$74 以下的噪声尖峰; ( 如果电源跌到 !(A% 以下, 编程操作被封锁; *) ( 当 ! "" 高于检测电平时, 要延时 $64 方可编 !) 程操作; 要进入写周期, 只有当;,、 ( #) <,、 B,同时满足 要求才能进入编程状态;

摘要:介绍了 &’()* 公司的新一代 +*,-. /0123 &4567%8%& 的硬件结构和性能特点, 讨论了这种大容量( 快速擦写存储器和 $%#" 系列单片机的接口, 以及应用中应注 839) 意的事项。 关键词: 单片机 +*,-. /0123; &4567%8%&; 文献标识码: 中图分类号: 40### 9 文章编号: "%%":"#6%( 5%%5) %#:%%;":%#

*++* 年 第 ! 期

,’-./01.2’ 3-2450-6-7/ 8 974/056-7/2/1&7

金士顿闪存指南(中文)说明书

闪存指南金士顿® 是全球领先的独立内存产品制造商,提供各种利用闪存芯片存储数据的闪存卡、USB 闪存盘和固态硬盘 (SSD)(统称为闪存设备)。

本指南旨在介绍现有的各种技术和闪存产品。

注意:由于闪存技术不断变化,本文档所述规格可能随时更改,恕不另行通知。

1.0 闪存:助力新一代闪存设备东芝于 20 世纪 80 年代发明了闪存,这项新存储器技术让存储器设备在断开电源时也能保留已存储的数据。

从那时起,闪存技术逐步发展成为各种消费类及工业设备的首选存储介质。

在消费类设备领域,闪存广泛应用于:••笔记本电脑••个人电脑••平板电脑••数码相机••全球定位系统•(GPS)••手机••固态音乐播放器,例如•••电子乐器•MP3•播放器••电视•••便携式和家庭视频游戏机闪存还应用于许多工业应用领域,其中断电情形中的可靠性和数据保持性是两项关键要求。

这些领域包括:••安保系统/网路摄影机••军事系统••嵌入式计算机••机顶盒••网络和通信产品••无线通信设备••零售管理产品••销售点设备•((例如手持扫描器))请注意:大多数金士顿闪存产品经过精心设计和严格测试,可兼容消费类设备。

对于超出标准日常消费类用途的工业应用或特殊用途应用,建议您直接联系金士顿。

这可能需要特殊配置,特别是对于严重影响闪存单元耐久性的应用(参见第•3.0•章)。

2.0 SSD、闪存卡和 USB 闪存盘容量闪存设备上所列容量有部分会用于格式化及其他功能,并非全部用于数据存储。

在设计和生产闪存设备时,需要采取相应的步骤,以确保设备能够可靠地工作并允许主机设备(计算机、数码相机、平板电脑、手机等)访问存储器单元,即存储和检索位于闪存设备上的数据。

格式化包括以下操作:1.•测试闪存设备中的每个存储器单元。

2.•找出所有有问题的单元,并采取相应的步骤确保不会对有故障的单元进行数据写入或读取。

3.•保留部分单元作为“备用”。

闪存单元拥有很长的寿命,但也是有限的。

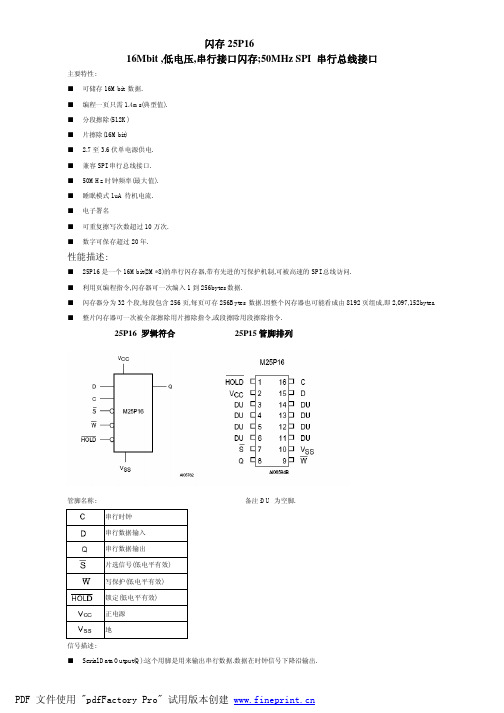

Flash ROM ST25P16中文资料

■ 闪存器可被外围带 SPI 的控制器驱动并工作在下面两种模式下: CPOL=0 , CPHA=0 CPOL=1 , CPHA=1 在这两种模式下,输入数据都是在时钟信号上升沿锁入闪存器,输出数据是利用时钟信号的下降沿输出. 这两种模式的区如图 6 所示,时钟极性是在总线控制器在标准模式下不传输数据的极性: ------- C remains at 0 for (CPOL=0,CPHA=0) ------- C remains at 0 for(CPOL=1,CPHA=0)

串行数据输入

串行数据输出

片选信号(低电平有效)

写保护(低电平有效)

锁定(低电平有效)

正电源

地

信号描述: ■ Serial Data Output(Q):这个用脚是用来输出串行数据.数据在时钟信号下降沿输出.

PDF 文件使用 "pdfFactory Pro" 试用版本创建

时: ◇ 上电重启 ◇ 写取消指令(WRDI)完成 ◇ 写状态寄存器指令(WRSR)完成 ◇ 页编程指令(PP)完成 ◇ 段擦除指令(SE)完成 ◇ 片擦除指令(BE)完成

■ 块保护位(BP2,BP1,BP0)可设置闪存器部分区域只能被读,不能写入,这就是软件保护模式(SPM) ■ 写保护信号(W)允许块保护位(BP2,BP1,BP0)和状太寄存器写保护位(SRWD)位被保护.这就是硬件保护模式(HPM). ■ 除低功耗之外,掉电模式提供了额外软件保护,此时所有的写入,编程,擦除指令都不被处理.

■ 如果锁定信号不是在时钟信为低电平时产生,锁定状态将在下一个时钟信号为低时生效.同样地如果取消锁定信号不是 在时钟信号为低时产生,锁定取消将在下一个时钟信号为低时生效.

■ 在锁定状态中,串行输出端(Q)为高阻抗,串行输入数据(D)和串行时钟信号都不被处理. ■ 通常,在整个锁定过程中都被处选中状态,即片选信号(S)为低.这是为了确保进入锁定状态的储存器内部逻辑数据不变. ■ 如果片选信号(S)在锁定过程中变为高电平,这将对闪存器内部逻辑的重新编排有影响.重启闪存器的通信,这必须使锁定信

FLASH的操作

FLASH的操作所谓Flash,是内存(Memory)的一种,但兼有RAM和ROM 的优点,是一种可在系统(In-System)进行电擦写,掉电后信息不丢失的存储器,同时它的高集成度和低成本使它成为市场主流。

Flash 芯片是由内部成千上万个存储单元组成的,每个单元存储一个bit。

具有低功耗、大容量、擦写速度快、可整片或分扇区在系统编程(烧写)、擦除等特点,并且可由内部嵌入的算法完成对芯片的操作,因而在各种嵌入式系统中得到了广泛的应用。

作为一种非易失性存储器,Flash在系统中通常用于存放程序代码、常量表以及一些在系统掉电后需要保存的用户数据等。

常用的Flash为8位或16位的数据宽度,编程电压为单3.3V。

主要的生产厂商为INTEL、ATMEL、AMD、HYUNDAI等。

Flash 技术根据不同的应用场合也分为不同的发展方向,有擅长存储代码的NOR Flash和擅长存储数据的NAND Flash。

一下对NOR Flash和NAND Flash的技术分别作了相应的介绍。

一.NOR Flash1.市场介绍随着技术的发展,愈来愈多的电子产品需要更多的智能化,这也对这些产品的程序存储提出了更高的要求。

Flash 作为一种低成本、高集成度的存储技术在电子产品领域的应用非常广泛。

今天90%的PC、超过90%的手机、超过50%的Modem,都是用了Flash,如今Flash市场规模已经超过了100亿美元。

如此巨大的市场规模,也导致市场上的Flash 品牌层出不穷。

在NOR Flash市场中,Intel公司是非常重要的一家生产厂商。

Intel公司生产的Flash芯片多年来占据着市场的很大份额,而它的芯片封装形式和接口也成为业界标准,从而为不同品牌的Flash带来了兼容的方便。

2.NOR Flash 的硬件设计和调试首先,Flash 要通过系统总线接在处理器上,即保持一个高速的数据交换的通道。

那么就必须了解一下Flash在系统总线上的基本操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

�

FM FLASHROM 块写函数: DMto MtoF

函数定义:

FUN I, FM_addr As LDM256, DM_addr As D1, Len As D2

函数功能:

把数据存储器 DM 中某个块的数据按字写入到 FROM 中。

输入参数:

FM_addr:FROM 中数据块的起始地址(必须为偶数) 。 DM_addr:数据存储器 DM 块的起始地址。 Len :数据块的长度(按字算) 。 FM(10000, #DM300, 10) 例如: D Mto MtoF 中地址 10000 开始的数据块中。 , #DM300, 10 00 ) 为扇区写操作, DMtoFM (DM280*4096 DM280*4096, 1000 00) 表示把从 DM300 开始的 1000 个字的数据写入到 FROM 的某个扇区(从起始位置开始)中,该扇区号在 DM280 中。注:执行扇区写操作前必须要先擦除该扇区。 把从 DM300 开始的 10 个字的数据写入到 FROM

大容量 FlashROM 存储器应用说明

说明: 大容量 FlashROM 存储器容量为 4M 个字节( 2M 个字) ,分为 1024 个扇区,每个扇区 有 4K 字节( 2K 个字) ,各个扇区可单独擦除。若某个位置已经写过数据,那么往该位置再 写其他数据时,必须要先擦除该位置所在的扇区。扇区号( 0~1023 )和字节存储地址的对 应关系为:字节存储地址 = 扇区号*4096。 函数库文件名: FROM.yf。 函数库内的函数如下: � FLASHROM 扇区擦除数:ROMERC

函数定义:

FUN I, Void As D0

函数功能:

擦除 FLASHROM 中的所有数据。

输入参数:

Void:固定为 0。

说明:

写数据前必须先擦除。整片擦除时间为 3 秒。

例如: ROMERC(0)

擦除所有数据。

�

FLASHROM 块读函数: FMtoDM

函数定义:

FUN I, Sector As D0

函数功能:

擦除 FLASHROM 中的某个扇区( 0~1023 ) 。

输入参数:

Sector:要擦除的扇区号( 0~ 1023 ) 。

说明:

FLASHROM 中分成 1024 个扇区 0~ 1023 ,每个扇区 4K 字节,写数据前必须先擦除。 扇区擦除时间为 0.3 秒。 例如: ROMERS(1) 擦除第 1 个扇区(地址 4096 ~8191 ) 。

函数定义:

FUN I, FM_addr As LDM256, DM_addr As D1, Len As D2

函数功能:

把 FROM 中某个块的数据按字读入到数据存储器 DM 中。

输入参数:

FM_addr:FROM 中数据块的起始地址(必须为偶数) 。 DM_addr:数据存储器 DM 块的起始地址。 Len :数据块的长度(按字算) 。 例如:FMtoDM(10000, #DM300, 10) 把 FROM 中从地址 10000 开始的 10 个字的数据 读入到 DM300 开始的数据块中。 DM280*4096 , #DM300, 10 00 ) 为扇区读操作,表示从 FROM 中某个扇 FMtoDM( FMtoDM(DM280*4096 DM280*4096, 1000 00) 区起始位置开始读 1000 个字放到 DM300 开始的数据块中, 该扇区号在 DM280 中 。