cadence 实验指导书

Cadence数字集成电路版图设计与验证 实验指导书 (电子科技大学)

数字集成电路版图设计与验证实验指导书电子科技大学微电子与固体电子学院实验名称数字集成电路版图设计与验证一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。

该实验是正向设计中电路仿真完成之后、工艺制版之前的必须环节,与其他实验相结合,可以使学生对当前国际主流的IC设计技术流程有较完整的认识。

本实验是基于微电子技术应用背景和《微电子集成电路》课程设置及其特点而设置,为IC设计性实验。

其目的在于:•根据实验任务要求,综合运用课程所学知识自主完成相应的数字集成电路版图设计,掌握基本的IC版图布局布线技巧。

•学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的自动布局布线设计与验证。

通过该实验,使学生掌握数字专用集成电路版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力,掌握自主进行数字集成电路版图设计与验证的基本方法,进而为今后从事科研、开发工作打下良好基础。

二、实验原理2. 1 Cadence 环境的调入1、在UNIX 操作系统的Terminal窗口下→ cd user/userxxx/studname/Project→ icms& 或icfb&2、出现CIW(command Interpreter window)命令解释画面3、点选在CIW窗口的上面工具列Tools→Library Manager,会出现LM窗口LM(Library Manager)2. 2 建立新的Library1.点选LM窗口上面的工具列File→New→Library2.会产生New Library画面3.出现下图画面1.在name填上Library名称2.点选下面的OK4.出现Load Technology File窗口,添加工艺文件2.3 电路版图的自动布局布线2.3.1 启动Automatic Layout Tool1.打开已经设计完成的电路图Schemic2.点选 Tools --> Design Synthesis --> Device-Level Editor ,将弹出对话框,定义版图名,最好取与前面cell view 相同的名字。

cadence实验报告三实验报告

实验报告三:Cadence实验报告

1. 实验目的

本实验旨在熟悉Cadence软件的使用,并通过设计和仿真一个简单的2输入AND门,学习使用更多的Cadence工具。

2. 实验步骤及结果

2.1 绘制原理图

首先使用Cadence软件新建一个库文件,命名为“And2_lib”,并打开Library Manager工具,如下图所示:

Library Manager

Library Manager

在Library Manager工具中,我们可以进行各种管理操作,包括新建、删除、重命名库文件等操作,还可以查看库文件中的各种信息。

接下来,我们使用Schematic Composer工具绘制2输入AND门的原理图,如下图所示:2-input AND Gate Schematic

2-input AND Gate Schematic

其中,我们使用了以下基本元件:

•Pmosa:NMOS器件

•Nmosa:PMOS器件

•Resistor:电阻器件

•Vdc:直流电源

•Vground:地电源

绘制完成后,使用“Save As”命令将原理图保存为“And2”即可。

2.2 设计Layout布局

在完成原理图设计后,接下来需要对其进行布局设计。

我们首先在Design Manager工具中打开“And2”原理图文件,并使用Create Cell View工具为该原理图新建一个Layout布局,如下图所示:

Create Cell View

Create Cell View

然后,我们进入Virtuoso Layout Editor工具,选中。

实验报告cadence实验报告三篇_082文档

2020实验报告cadence实验报告三篇_082文档EDUCATION WORD实验报告cadence实验报告三篇_082文档前言语料:温馨提醒,教育,就是实现上述社会功能的最重要的一个独立出来的过程。

其目的,就是把之前无数个人有价值的观察、体验、思考中的精华,以浓缩、系统化、易于理解记忆掌握的方式,传递给当下的无数个人,让个人从中获益,丰富自己的人生体验,也支撑整个社会的运作和发展。

本文内容如下:【下载该文档后使用Word打开】PSpiceSimulationExperience620xx0xx21236张双林Workrequirement:pleasereadtheexerciseofpage117fromthespicebook,butsimulat ethedevicemodelparametersandoperationalpointat30degreeand100degree.PleaseRuntheTEMPanalysiswithPspiceandanswerthequestionoft heexercisePleasehandoutae-reportaboutyourworkI.Net-listsandcircuitfigure:Andthenet-listfilegoes:EX3DCAnalysysexapal1.2.MODELMELQNPNBF=100IS=1E-16Q1210MELQRB31200KRC321KVCC30DC5.temp30100.OP.ENDII.Simulationresult:Accordingtotheoutputfile,wecandrawatabletocontrastthediff erence:a.b.III.Conclusion:Withaninspectionofthecircuitparametersindifferenttemperat ures,wecanfindthatthevalueofISchangeslargely,about1000tim es,andGM,about16percent,whileabout500mvdecreasingonVCEcau sed.SothebehaviorofTransistorscanbeaffectedbytemperatures largely.。

cadence 实验

• 接下来出现如下图对话框,点击OK

• 删除绿线框,但红线框要保留。

• Add-shape;利用下面的形状把symbol修改成你所需要的形状,在 修改形状之前,先把红线框拉大点。

• 画图方法,选中所需要的图形,鼠标左键 点一下,然后移动鼠标,不用按住鼠标左 键不放移动鼠标来画图。

• 画完后如图所示,@instanceName与@partName可以保留,也可以 删除。

• simulation: spectre & hspice (旧版hspice需要手动改网表,新版可以集 成到ADE环境中) • layout: virtuoso • verification: diva (on-line) dracula & calibre (off-line)

Байду номын сангаас

工艺库选择

完整为主: 必须包含: spectre & hspice 库、 diva规则文件、dracula & Calibre规则文件 最好能包含: assura规则文件 台湾教学大多用 CIC TSMC035,pad信息不全,流片时由 CIC负责替换 //拼凑了一个,仅用于教学 所用的工艺为TSMC035

Cadence 实验

实验流程:

一、实验环境搭建

二、 Schematic (原理图设计与生成符号图) 三 、Pre-simulation(前仿真) 四 、Layout(版图设计) 五、Verification(验证) 六、Post-simulation(后仿真)

工具选择

• schematic: virtuoso

2、编辑(绘制)原理图

• 使用前说明:

• 每做一步按一次esc 退出键,要不然会经常 重复操作,带来一定的麻烦。 • Schematic Editing 编辑窗口如下图所示:

Cadence实验指导书

% pwd /home/dong/work % cd/ % pwd / % /cd/home/dong/work % pwd /home/dong/work % cd ~ % pwd /dong/work 3. 查阅目录 查找文本信息使用 Is 命令,基本的显示格式中只包含文件名。例如: % pwd / % Is work group homework 若要显示更多的信息,可以用 Is 的-1(长格式)选项, 显示信息包括 7 项,从左至右分别 为:目录内容和显示权限、链接数、文件所有者、文件大小(字节数) 、最后一次的修改日期和时 间、文件名称等,如下所示。 -rwxr----1 bill 6784 Feb 3 10:54 addendum Drw--x--1 bill 367 Mar 15 08:37 balance -rw-r--r-2 bill 9285 Apr 22 15:21 call-125 drwx-----1 bill 294 Jan 18 11:46 deadline -rwxrw---1 bill 8349 Dec 17 08:59 end.odd -rw-rw-rw5 bill 7956 May 24 10:03 first 长格式显示中的每一行字符用于确定此文件是普通文件(-)还是目录(d) 。 4. 创建目录 UNIX 中创建目录的命令是 mkdir(make directory)。例如: % pwd /usr/paul % mkdir news %_ 该命令在/usr/paul 下创建了一个名为 news 的子目录,即/usr/paul/news。 5. 删除目录 删除目录的命令是 rmdir(remove directory)。在删除目录之前必须删除该目录下的所有文 件,然后移到父目录下去,在删除此目录。下面的例子说明如何删除/usr/paul/letters: % cd.. % pwd /usr/paul % rmdir letters %_

基于Cadence的模拟集成电路设计

2.1

Cadence初次启动之前需要如下一些配置文件:

.cshrc文件:有关一些Cadence必需的环境变量,如Cadence软件的路径及license。

.cdsenv文件:包含Cadence各种工具的一些初始设置。

.cds.lib文件:用户库的管理文件,在第一次运行Cadence时自动生成。

.cdsinit文件:包含Cadence的一些初始化设置以及快捷键设置。

进入连线命令后,于起点单击左键,再于终点单击左键。画完一段导线后,此时并没有退出画线命令,可以继续画连接线,直到画完所所有的连接线后,按ESC退出画线命令。连好线的电路图如图3.7所示,其中左右两条水平导线是后在连连接端口用的。

还可以对画好的线进行命名,键入快捷键L(小写),在弹出的对话框中输入线名,比如a,点击Hide,然后将字母a移动到要命令的线附近点击左键放下,如果名字离线较远,则要求再单击所要命名的线。

如图1.1Cadence模拟集成电路设计流程

本实验指导书针对以上流程,通过设计一个简单的缓冲器的原理图到最终的版图,对Cadence的Composer,Analog Desing Environment,Virtuoso,Assura等各大功能模块逐一做个简单介绍。此外还包括一些Cadence平台的知识介绍。Cadence开发了自己的编程语言skill以及相应的编译器,整个Cadence可以理解为一个搭建在skill语言平台上的可执行文件集。初学者对此可以不用理会,当用户深入后,可以用skill语言对Cadence设计工具进行扩展。

图3.5选择了元件后的添加器件窗口

可以发现Library,Cell,View等都自动填上了相应的信息。同时多出了一些参数列表(拖动滚动条可以看到更多)。点击Hide隐藏当前窗口,此时鼠标对应有一个PMOS的symbol,此时按r键,可以旋转PMOS,继续点击鼠标左键,否则按ESC取消当前的放置器件命令。

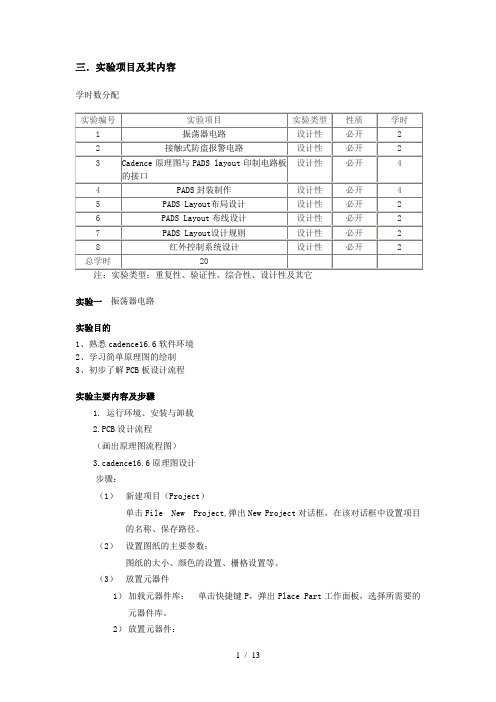

cadence16.3、PADS9.5实验讲义

三.实验项目及其内容学时数分配注:实验类型:重复性、验证性、综合性、设计性及其它实验一振荡器电路实验目的1、熟悉cadence16.6软件环境2、学习简单原理图的绘制3、初步了解PCB板设计流程实验主要内容及步骤1. 运行环境、安装与卸载2.PCB设计流程(画出原理图流程图)3.cadence16.6原理图设计步骤:(1)新建项目(Project)单击File New Project,弹出New Project对话框,在该对话框中设置项目的名称、保存路径。

(2)设置图纸的主要参数:图纸的大小、颜色的设置、栅格设置等。

(3)放置元器件1)加载元器件库:单击快捷键P,弹出Place Part工作面板,选择所需要的元器件库。

2)放置元器件:3) 编辑原理图:元器件的复制、粘贴、删除;旋转 4) 放置电源和接地符号 5) 连接导线实验二 接触式防盗报警电路实验目的:1、进一步熟悉cadence16.6软件环境2、熟悉cadence16.6各种菜单和工具的使用3、理解画PCB 板前的准备工作实验主要内容及步骤1. 新建接触式防盗报警电路项目和接触式防盗报警电路原理图2. 原理图绘制的后续处理(1) 对绘制后的原理图重新编号 (2) DRC 检查(3) 在原理图中为每个元器件定义PADS Layout 封装 (4) 生成网络表R4RJ1HEADER 212VCCR2RR1RR3RR4RR5RR6RR7RR8RR9R+C2CAP POL+C5CAP POL+C1CAP POLD1DIODE Q2NPN BCEQ1PNP BCE J2HEADER 212+C3CAP POLLS1SPEAKERVCCVCC-+U1LF356/DIP832671458U2NE555OUT3R S T4V C C8G N D1C V5TR2TH 6DIS 7J1AM1A V C CC4CVCC实验三 Cadence 原理图与PADS layout 印制电路板的接口 实验目的掌握在PADS layout 中导入网络表的方法 实验主要内容及步骤1、 在cadence allegro design CIS 系统中给每个元器件赋予PCB 封装(这里的PCB 封装指的是PADS layout 中的封装)。

cadence 实验3

•

修改后:

• 将修改好的list 拷贝到calibre_lvs文件夹下面。 • 同时将inv.gds拷贝到calibre_lvs文件夹下面。inv.gds 是 在版图DRC验证时产生的文件。 • 打开inv 的版图窗口 • 点击窗口工具栏的Caliber—Run LVS • 先关掉Load Runset File 窗口,不要配置Load Runset File 对话框。

• 最后的INV版图

• 加上引脚 in: • 先在左面的LSW 窗口选择METAL1 -pin ,不是METAL1drw

• 然后在版图窗口creat -----pin或使用快捷键ctrl+p ,在 Terminal Names 中输入名字 in,然后选中shape pin,会 弹出另外一个对话框,选中Display Pin Name 再点击 Display Pin Name Options… ,在弹出的对话框中的 Layer项选择 METAL1 pn ,然后OK,同时确定I/O Type 的类型 input,点击Hide 之后,需要通过鼠标拉出一个矩 形,然后出现in 字样,如图所示:

• 通过Library Browser 选中inv 的schematic 之后关掉左面 的窗口即可,改一下output file 的名字,点击右面的窗口 的OK

• • •

手动修改网表,PMOS模型应由PM改为P,NMOS模型 应由NM改为N 。 在自己的工作目录下,会有list 文件,通过命令 vi list 修改,对第33行与第34行修改。 修改前:

INV(反相器)版图

• 在自己的库下新建一个inv 版图 • 通过i 快捷键将PMOS ,NMOS 版图添加进来。 有可能出现如图的情况,只要通过shift +f 就可以 显示详细的版图,ctrl +f 缩略的版图。

Cadence教程(D422)PDF.pdf

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为键盘功能键;“单击”指鼠标左键按下一次。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

[1]启动IC Design 软件:首先,登陆Linux,在username文件夹中建立一个你命名的文件夹,然后在Terminal窗口中进入这个文件夹,在该文件夹目录下输入:icfb&,(这样,你在cadence中做的一切工作都会自动保存在这个文件夹中,如果直接icfb&的话,会导致你的工作成果,例如:电路图、仿真结果等,会在/home中保存,影响其他人的使用)[2]建立新库、新单元以及新视图(view):首先,输入icfb&后,出现下图窗口在图中CIW窗口中依次打开:Tools->Library Manager,出现下图窗口:在图中窗口中依次打开:File->New->Library,出现下图窗口:输入Library Name:test,然后点OK。

(注意下面的保存路径就是你第一步建立的文件夹)出现下一个窗口:选中Attach to an existing techfile,然后OK。

出现下一个窗口:选中右下方Technology Library:chrt35dg_SiGe,然后OK。

下面我们来画一个nand2电路。

选中左侧的test,在Library Manager 窗口,File->New->Cellview,如下图:在弹出的“Create New File”窗口Cell Name栏中,nand2 Tool栏中,选Composer-SchematicOK,如下图[3]添加元件(实例instance)在弹出的“Virtuos o Schematic Editing:…”窗口中,左边为工具栏,选instance 图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser-…”窗口,Library选chrt35dg_SiGe,Cell选nmos_3p3, View选symbol鼠标回到“Add instance”窗口,Model name栏:nmos_3p3, width(Total Width): 3.0u , Length: 0.5u,Hide 如下图在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,这样就增加了2个nmos元件,ESC(试一试:先选中一个元件,再q ,查看/改变属性)。

课程实验一 Cadence使用基础

IC工艺及版图设计课程实验一一、实验目的:1 掌握Cadence软件的启动方法2 了解原理图编辑器使用方法3 掌握Cadence版图编辑软件的使用方法二、实验软件:Cadence IC 5141 Virtuoso Layout Editor三、实验要求:实验前请做好预习工作,实验后请做好练习,较熟练的使用Cadence软件。

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)实验内容:项目一、Linux系统与Cadence软件介绍1.Cadence软件介绍◎全球最大的EDA公司,产品涵盖电子设计的整个流程,自1991年以来,连续在EDA市场中销售额稳居第一。

◎提供系统级至版图级的全线解决方案,产品包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制IC设计,IC物理验证,PCB设计和硬件仿真建模等。

◎系统庞杂,工具众多,不易入手◎具有广泛的应用支持,全球知名半导体公司与电子系统公司均将Cadence软件作为其全球设计的标准。

2.Cadence 全定制IC设计软件◎Virtuoso Schematic Composer◎Analog Design Environment◎Spectre◎Virtuoso Layout Editor◎Assura◎Dracula & Diva◎Virtuoso Layout Synthesizer自动版图◎ICCragtsman布局工具3.系统环境◎.cshrc:指定Cadence软件和License文件所在路径(用户目录下,隐藏文件)◎.cdsenv:包含Cadence软件的一些环境设置(用户目录下,隐藏文件)◎.cdsinit:Cadence初始化设置(用户目录下,隐藏文件)◎ cds.lib:Cadence调用的设计库文件◎ techfile:工艺文件包含了设计必须的信息,版图设计时必须包含该文件。

Cadence 实验

实验说明

212实验室的电脑,只有F盘能够保存数据,因此要把cadence的工作目 录转移到F盘中的文件夹。具体方法: 在F盘的RedHat_Share中,以自己的学号名建文件夹,如12120036. 然后启动cadence,右键>打开终端,输入如下命令, cd .. cd .. cd mnt cd hgfs cd Redhat_Share cd 14120024 icfb& 注意:一次输一行命令,每输完一行命令之后要敲回车键。以后每次实验 都在该路径下打开icfb&。

2.File>Open…

1.1启动VMware

3.找到redhat所在目录(E:\Redhat),导入redhat

4.单击绿色三角形,启动VMware

1.1启动VMware

5.用户登陆 User:cadence Passward:cadence

1.2启动&退出 IC5141

在桌面点击右键>打开终端>输入:icfb& 出现如图所示的CIW(Command Interpreter Window)窗口。从CIW窗口就可以调用许多工具并完 成许多任务。 CIW>File>Exit.. 可以退出IC5141

2.3复制库

2.4重命名库

选中所要复制的Library Library Manager>Edit>Rename… 右键>Rename… To Library 填入新的Library Name

2.5新建Cell View

选中所要添加Cell View的Library (Category) 输入Cell Name 选择Tools>Ok 不同的Tools对应不同的View Name

Cadence实验

实验报告要求:1、封面要求:集成电路设计技术实验报告专业、学号、姓名2、正文要求:要求有以下几项:A、实验名称B、实验目的C、实验步骤D、出现问题及解决方法E 时间试验1名称:Candence软件操作准备试验目的:了解熟悉虚拟机的概念、linux常用命令;熟练操作文件的挂载,虚拟机以及Candence 的启动。

试验步骤:熟悉相关概念,启动虚拟机,建立自己的文件夹,挂载库“csmc06lib_ver4”以及文件夹“models”并拷贝到自己建立的文件夹中;在自己建立文件夹的路径下启动Candence。

出现问题及解决:虚拟机:虚拟机(VM)是支持多操作系统并行运行在单个物理服务器上的一种系统,能够提供更加有效的底层硬件使用。

在虚拟机中,中央处理器芯片从系统其它部分划分出一段存储区域,操作系统和应用程序运行在“保护模式”环境下。

在一台电脑上将硬盘和内存的一部分拿出来虚拟出若干台机器,每台机器可以运行单独的操作系统而互不干扰,这些“新”机器各自拥有自己独立的CMOS、硬盘和操作系统,你可以像使用普通机器一样对它们进行分区、格式化、安装系统和应用软件等操作,还可以将这几个操作系统联成一个网络。

在虚拟系统崩溃之后可直接删除不影响本机系统,同样本机系统崩溃后也不影响虚拟系统,可以下次重装后再加入以前做的虚拟系统。

虚拟机以及Candence的启动见计算机中拷贝的相关资料。

文件的挂载:就是将windows操作系统下的文件共享到linux操作系统中,见计算机中拷贝的相关资料。

本实验将windows下的库“csmc06lib_ver4”共享到linux中,并拷贝到自己建立的目录中。

实验一虚拟机以及Candence的启动1、点击桌面“VMare Workstation”的图标,进入VMare Workstation工作界面。

2、点击菜单“file”中的子菜单“open”,找到虚拟机的安装路径。

3、路径找到后,点击文件名为“red hat linux”的虚拟机文件,然后点击“打开”。

2 Cadence IC实验一、二、三

2、输入特性

三极管的输入特性是指当集电极电压Vce为常数时,基极与发射极间电压Veb与基极电流ib之间的关系。

如同前一个实验介绍的方法,打开仿真窗口,先设置好model路径,模型文件依然选择/cad/smic018_tech/Process_technology/Mixed-Signal/SPICE_Model/ms018_v1p6_spe.lib,注意section设为bjt_tt。然后添加变量vbe和vce。再按图2.3对话框设置好DC分析。其中DC分析是对vbe进行扫描,扫描范围从0到1.8V。vce的初始值设为1.5V。最后设置输出,这里我们要看的是基极电流,所以点击三极管的基极pin脚。

然后点“Netlist and Run”进行仿真。得到的输入特性曲线如图2.4所示。横坐标是基极-射极电压vbe的变化,纵坐标是基极电流ib的变化。

3、输出特性

三极管的输出特性是指以iB为参变量的共射极电流iC与UCE之间的关系。

先设置好Analog Design Enviroment对话框,注意这次DC分析所扫描的变量是vce,扫描范围为-0.3到1.8V。如图2.5所示:

如同前面的方法,打开仿真窗口,先设置好model路径,库文件与上面的相同,但工艺角(section)填入tt。然后添加变量vds和vgs。接着设置DC分析。其中DC分析是对vds进行扫描,扫描范围从0到1.8V。vgs的初始值设为0V。最后设置输出,这里我们要观察的是MOS管的漏电流,所以点击MOS管的漏极。设置好后的仿真窗口如图2.11所示。

电压源的参数设置图1.3所示,在DC voltage处填入vin(填入变量是为了要做直流扫描)

实验一、Cadence软件操作步骤

实验一基本门电路设计——电路仿真一、实验内容:完成CMOS 反相器的电路设计完成CMOS 反相器的电路设计实验目的掌握基本门电路的设计方法掌握基本门电路的设计方法熟悉Cadence 的设计数据管理结构,以及定制设计的原理图输入、电路仿真、版图设计、版图验证工具的使用二、实验目的:基于csmc05工艺,完成一个具有逻辑反相功能的电路设计要求:设计要求:1.反相器的逻辑阈值在Vdd/2附近,即噪声容限最大2.反相器的版图高度限制为24微米,电源和地线宽度各为2微米3.反相器宽度限制为mos 器件不折栅4.为了给顶层设计留出更多的布线资源,版图中只能使用金属1和多晶硅作为互连线,输入,输出和电源、地线等pin脚必须使用金属15.版图满足设计规则要求,并通过LVS 检查三、设计过程:启动icfb1.建立自己的设计库2.用Virtuoso Schematic Composer 画电路图3. 在Analog Design Environment中进行电路仿真4. 用Virtuoso (XL)Layout Editer 画版图5. 利用diva 工具进行DRC检查,用dracula进行DRC和LVS验证。

四、实验步骤1.Cadence软件操作步骤:(1).点击桌面虚拟机快捷方式图标;(2).打开虚拟机(存放路径:F:\cadence);(3).启动虚拟机(4).单击右键,Open Teminal,弹出终端对话框,输入Cadence启动命令icfb&(&是后台运行的意思)。

2.. 新建一个库建立自己的Design Lib第一步:CIW-> Tools-Library manager第二步:File-New弹出“New Library ”对话框,在“Name”项填写要建的design lib的名字,这里是“lesson1”,选择“Attach to an existing techfile”第三步:弹出”Attach Design Library to Technology File”对话框,在“Technology Library”中选择st023.新建一个电路图(1)File->New->Cellview(2)弹出“Create New File”对话框,“Library Name”项选择“lesson1”“Cell Name”项填入”inv”,“Tool”项选择”Composer-Schematic”“Tool”项确定后, 相应的“View Name”项会出现内容因而无需输入”,点击“OK”后就进入Virtuso Schematic。

集成电路版图设计实验指导书

集成电路版图设计实验指导书实验一绘制标准逻辑单元版图实验目的:了解集成电路版图设计基本原理;熟悉版图设计软件cadence virtuoso的使用。

实验内容:学习集成电路版图设计基础;学习cadence virtuoso基本操作;绘制完成标准逻辑单元版图。

实验原理:集成电路版图设计是电路系统设计与集成电路工艺之间的中间环节。

通过集成电路版图设计,将立体的电路系统转变为二维平面图形。

利用版图制作掩模板,就可以由这些图形限定工艺加工过程,最终还原为基于半导体材料的立体结构。

以最基本的MOS器件为例,工艺生产出的器件应该包含源漏扩散区、栅极以及金属线等结构层。

按照电路设计的要求,在版图中用不同图层分别表示这些结构层,画好各个图层所需的图形,图形的大小等于工艺生产得到的器件尺寸。

正确摆放各图层图形之间的位置关系,绘制完成的版图基本就是工艺生产出的器件俯视图。

器件参数如MOS管的沟道尺寸,由电路设计决定,等于有源区与栅极重叠部分的尺寸,如图1。

其他尺寸由生产工艺条件决定,不能随意设定。

图1在工艺生产中,相同结构层相连即可导电,而不同结构层之间是由氧化层隔绝的,相互没有连接关系,只有制作通孔才能在不同结构层之间导电。

与工艺生产相对应的版图中默认不同图层之间的绝缘关系,因此可以不必画氧化层,却必须画各层之间的通孔。

另外,衬底在版图设计过程中默认存在,不必画出。

而各个N阱、P阱均由工艺生产过程中杂质掺杂形成,版图中必须画出相应图形。

实验步骤:打开指定电路图,浏览并简单分析电路结构;为电路新建版图文件;根据版图基本原理,为电路绘制版图。

(详细内容参考《Cadence virtuoso 使用简介》)实验报告要求:应包含对电路功能的简单分析,以及绘制完成的版图图片。

思考题:观察《Cadence virtuoso 使用简介》中给出的反相器版图,思考为什么把两MOS管栅极放在一条直线上,而不是并排放置。

实验二简单数字逻辑模块版图设计实验目的:了解集成电路版图设计规则;熟悉版图设计技巧;掌握基于DIV A的版图验证方法。

Cadence实验教程

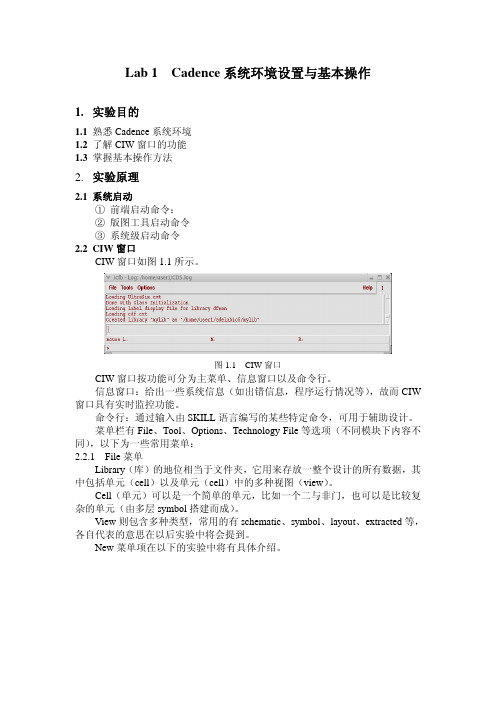

Lab 1 Cadence系统环境设置与基本操作1.实验目的1.1熟悉Cadence系统环境1.2了解CIW窗口的功能1.3掌握基本操作方法2.实验原理2.1系统启动① 前端启动命令:② 版图工具启动命令③ 系统级启动命令2.2CIW窗口CIW窗口如图1.1所示。

图1.1 CIW窗口CIW窗口按功能可分为主菜单、信息窗口以及命令行。

信息窗口:给出一些系统信息(如出错信息,程序运行情况等),故而CIW 窗口具有实时监控功能。

命令行:通过输入由SKILL语言编写的某些特定命令,可用于辅助设计。

菜单栏有File、Tool、Options、Technology File等选项(不同模块下内容不同),以下为一些常用菜单:2.2.1File菜单Library(库)的地位相当于文件夹,它用来存放一整个设计的所有数据,其中包括单元(cell)以及单元(cell)中的多种视图(view)。

Cell(单元)可以是一个简单的单元,比如一个二与非门,也可以是比较复杂的单元(由多层symbol搭建而成)。

View则包含多种类型,常用的有schematic、symbol、layout、extracted等,各自代表的意思在以后实验中将会提到。

New菜单项在以下的实验中将有具体介绍。

图1.2 New Library窗口图1.3 Create New File Library窗口分为Library和Technology File两部分。

Library部分有Name和Directory两项,分别对应要建立的Library名称和路径,Library名称可以自定义。

一般Technology部分选择Don’t need a techfile选项。

如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的工艺文件)或Attach to an existing techfile(使用原有的工艺文件)。

Cadence教程(D422)

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为键盘功能键;“单击”指鼠标左键按下一次。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

[1]启动IC Design 软件:首先,登陆Linux,在username文件夹中建立一个你命名的文件夹,然后在Terminal窗口中进入这个文件夹,在该文件夹目录下输入:icfb&,(这样,你在cadence中做的一切工作都会自动保存在这个文件夹中,如果直接icfb&的话,会导致你的工作成果,例如:电路图、仿真结果等,会在/home中保存,影响其他人的使用)[2]建立新库、新单元以及新视图(view):首先,输入icfb&后,出现下图窗口在图中CIW窗口中依次打开:Tools->Library Manager,出现下图窗口:在图中窗口中依次打开:File->New->Library,出现下图窗口:输入Library Name:test,然后点OK。

(注意下面的保存路径就是你第一步建立的文件夹)出现下一个窗口:选中Attach to an existing techfile,然后OK。

出现下一个窗口:选中右下方Technology Library:chrt35dg_SiGe,然后OK。

下面我们来画一个nand2电路。

选中左侧的test,在Library Manager 窗口,File->New->Cellview,如下图:在弹出的“Create New File”窗口Cell Name栏中,nand2 Tool栏中,选Composer-SchematicOK,如下图[3]添加元件(实例instance)在弹出的“Virtuos o Schematic Editing:…”窗口中,左边为工具栏,选instance 图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser-…”窗口,Library选chrt35dg_SiGe,Cell选nmos_3p3, View选symbol鼠标回到“Add instance”窗口,Model name栏:nmos_3p3, width(Total Width): 3.0u , Length: 0.5u,Hide 如下图在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,这样就增加了2个nmos元件,ESC(试一试:先选中一个元件,再q ,查看/改变属性)。

Cadence教程IC50-1

第一章启动IC50IC50是Cadence全定制IC设计工具包,其中包括原理图设计工具Composer,版图设计工具Virtuso,版图验证工具Diva、Dracula等。

这些工具集成在一个统一的设计环境中,称为Design Frame II。

Cadence IC50是一种通用的设计工具,其使用方法很灵活,许多操作取决于用户的设置,这些设置文件存放在用户的工作目录下,在启动时,系统自动寻找这些文件,因此在不同的目录下启动IC50时,操作方法可能有很大区别。

在ASIC EDA课程中,我们主要使用由美国北卡罗来纳大学(NCSU)编写的操作环境,使用该环境时,你需要在/etc/bashrc中设置环境变量CDS_SITE=/tools/cds5/。

本机安装时,该环境变量已设置,在不使用NCSU环境时,应在该句前面加#使其不起作用,但不要删掉,这样在需要使用该环境变量时,只要去掉#,重新启动即可。

本机的Cadence工具软件使用Linux Redhat7.2操作系统,所有Linux Redhat7.2操作系统都安装在虚拟机下,首次使用Linux Redhat7.2下的工具软件时需阅读本章的第1、2节。

1、启动虚拟机(1) 双击桌面上Vmware Workstation图标。

(2) 点击窗口中的“Start this virtual machine”(3) 在弹出的对话框中,点“OK”。

(4) 这时将出现Linux RedHat7.2的启动画面,用鼠标在Linux画面范围内点击一下,则鼠标可控制Linux,然后敲回车键启动Linux。

(5) 当Linux窗口内的信息不再变化时,敲回车键,应出现登陆信息(如敲回车键无效,先用鼠标在Linux窗口内点一下,进入控制虚拟机状态)。

(6) 在login:后面键入 root,然后回车(7) 在Password:后输入123456回车(8) 在出现[root xxn root]# 后输入 startx 回车(9) 这时将启动Linux的图形操作界面。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

cadence 实验指导书哈尔滨理工大学开放性实验指导书Virtuoso Analog Design Environment中文实验手册Version 5.1.41哈尔滨理工大学开放性实验指导书实验一、熟悉Virtuoso Analog Design Environment............................................................. (2)实验二、SchematicEntry .................................................................. . (6)实验三、模拟仿真 ..................................................................... . (13)实验四、显示仿真结果 ..................................................................... .. (22)实验五、仿真结果分析 ..................................................................... .. (31)实验六、参数分析 ..................................................................... . (43)实验七、使用OCEAN 和SKILL语言(略) ................................................................. .......... 46 实验八、使用Corner分析工具 ..................................................................... . (47)实验九、Monte Carlo 分析 ..................................................................... . (50)实验十、优化分析 ..................................................................... . (59)实验十一、Component Description Format(CDF)参数 .......................................................... 64 实验十二、Macromodels、Subcircuits和InlineSubcircuits (67)实验十三、HierarchyEditor ................................................................. .. (73)实验十四、继承连接 ..................................................................... (77)哈尔滨理工大学开放性实验指导书Virtuoso Analog Design Environment 实验步骤:一、登录Linux操作系统,用安装软件的用户登录,最好不要用root用户。

二、打开Linux的终端,进入软件所在文件夹,比如我的是/home/chengtao/adelabic5,输入 cd /home/chengtao/adelabic5,即可进入,注意在安装时有一个lnx86.cshrc的文件,在每次进入Cadence之前都应该先运行以下命令:source lnx86.cshrc ,然后再终端中输入 icms & ,稍等片刻,即可进入Cadence图形界面CIW,如下图所示(会弹出一个Cadence的介绍窗口,关闭即可)。

三、打开一个尖峰检测电路。

1、选择Tool下的Library Manager ,即可弹出Library Manager对话框,总共有三栏分别为:Library、Cell、View,只有在Library下有目录,另外两个是空的,点traning,在Cell下便会显示很多目录,我们选择点击peakTestv,在View 下会出现一个schematic,双击便会弹出一个对话框,如下图所示:哈尔滨理工大学开放性实验指导书2、选中peakDetectv ,peakDetectv会被白色的正方形线包围,然后依次执行 Design—Hierarchy—Descend Edit (可以使用快捷键E),会蹦出一个小对话框,在View Name中选择schematic,点击Ok,则会弹出一个电路图,如下图所示:3、用鼠标选中一个Ampv,按下E键,将ViewName设置为Veriloga,点击OK,即可弹出这个器件的Verilog-a语言描述,可以仔细参考一下,先不要关闭。

四、运行仿真。

1、在VerilogA-Editor对话框中,选中Design下的Return,即可回到原来的Schematic Editor对话框,依次选择Tool-Analog Environment,弹出一个对话框,如下图所示:哈尔滨理工大学开放性实验指导书2、依次选择Setup-Simulator/Directory/Host,确认Simulator设置为specture,点击Ok。

3、依次选择Setup-Model Libraries,在弹出的对话框中点击右下角的Browser,将目录设置为/home/chengtao/adeabic5/Models/myModels.scs,点击Add,点击OK。

4、依次选择Analysis-Choose,(也可点击对话框右侧的Choose Analysis),弹出一个对话框,如下图所示设置,点击OK。

5、重新选中peakTestv 块,按E键打开尖峰检测电路,然后再Analog Design Environment对话框中依次选择Outputs-To Be Plotted-Select On Schematic,在尖峰检测电路中选择vinput、vcap、vcontrol附近的线路,然后按下Esc键,重新返回到Analog Design Environment 对话框,得到如下图所示:哈尔滨理工大学开放性实验指导书6、依次执行Simulation-Nestlist and Run,也可点击对话框右侧的Nestlist and Run,(若这时弹出一个文本窗口,点击OK即可)稍等片刻,会弹出两个窗口,其中有一个波形窗口,波形应该是如下图所示:7、关闭所有窗口,不必保存。

哈尔滨理工大学开放性实验指导书Schematic Entry实验步骤:一、创建Library和Schematic Cellview。

1、进入CIW窗口,依次执行File-New-Library,在Name一栏里输入mylib,在右边的Technology File中选中Don’t need a techfile,点击Ok。

2、继续在CIW窗口中执行 File-New-Cellview,将Library Name 设置为mylib,Cell Name 中输入 amplifier,View Name设为schematic,Tool设为Composer-Schematic,点击OK,弹出一个空白的Schematic Editor窗口。

3、在Schematic Editor 窗口中,我们要画一个如下图所示的电路。

添加元件,可以选择Add-Instance ,或者按下键盘上的I 键,要添加的元件列表如下:Library Name Properties/Comments Cell Namepnp analogLib For Q2, Q3, Q4: Model Name=trpnp (no quotes)npn F or Q0, Q1: Model Name=trnpn (no quotes) analogLibpmos4 analogLib For M1: Model Name=trpmos (no quotes)Length=8u, Width=iPar(“l”)*16pmos4 analogLib For M3: Model Name=trpmos (no quotes)Length=iPar(“w”)/16, Width=128unmos4 analogLib For M2, M5: Model Name=trnmos, Width=100u,Length=10u哈尔滨理工大学开放性实验指导书res analogLib Resistance=2.5Kcap analogLib Capacitance=CAP (Design Variable)Vdd vss analogLib一个添加的例子如下图所示:注意:点击Browser即可进行选择,要注意器件的方向要与上图电路所示的方向一致,可以使用 Rotate和Sideways进行改变器件方向,将鼠标移入Schematic Editor窗口,单击即可添加,按下Esc键即可结束添加。

4、添加节点,执行Add-Pin,或者直接按P键,Pin Name中输入节点名称,如下所示:Pin Names iref inp inm out各节点名称要用空格隔开,Direction 设为input ,Usage设为schematic,将鼠标移入Schematic Editor窗口,会有一个图形跟着鼠标,选择好iref的方向(使用Add Pin窗口下面的Rotate和Sideways按钮),单击即可将iref放入,再回到Add Pin窗口,选择好inp的方向,依次类推,鼠标每点一下,将放入一个,注意再放入out之前,要将Direction改为output。

Tips:, 当器件已经放入时,仍然可以更改其方向,选择Edit—Rotate时,单击某个器件即可旋转,Esc可以退出,还可以更改期间的属性,选中某个器件,Edit —Properties—Object即可更改部分属性。

哈尔滨理工大学开放性实验指导书, Schematic Editor窗口左边有一排快捷键,使用时可提高效率。

, 器件的旋转方向只有一个,要想改变只能通过Sideways来改变的,在添加时就要使用Sideways按钮,再添加完之后,无法改变。

, 有很多键盘的字母代表快捷键,在你使用工具栏时,会看到他们各代表什么。