基于EDA技术的流水线CPU创新设计

EDA流水灯论文(VHDL)

滨江学院课程论文(可编程器件原理与应用)题目基于VHDL语言的流水灯设计学生姓名王秋阳学号20082305047院系滨江学院专业电子与信息工程指导教师刘建成二零一零年十二月三十日一、任务:采用ALTERA 公司的EPM7128SLC84-10芯片,通过VHDL 语言设计一个流水灯电路。

流水灯样式必须大于3种,且可以通过按键调节显示样式;可以通过按键调节流水灯变化快慢;当前流水灯样式和变化速度能够通过数码管显示出来;(附加:具有按键声)二、设计框图(框图说明)1MHZ 周期信号经过2个100分频,得到100HZ ,再经过1个10分频得到10HZ 信号,传给速度控制模块,得到需要的速度周期信号,然后传给样式选择模块,样式选择模块直接输出彩灯样式;控制模块通过接受两个按键信号,同时控制速度控制模块和样式选择模块;译码扫描模块通过判断控制模块,扫描数码管显示当前彩灯样式和彩灯变化速度;按键信号通过延时模块输出按键发生信号。

速度按键 样式按键控制模块速度控制样式选择译码和扫描数码显示彩灯显示1000HZ 信号100HZ 信号蜂鸣器三、原理图(CPLD内部原理说明)从原理图中可以看到,一共有8种模块,D触发器的作用是对按钮进行消抖,除D触发器之外的7个模块功能及作用如下:f100和f10分别是100和10的分频器,speed模块的作用是对彩灯变化速度进行控制,而style_switch模块的作用是对彩灯样式进行调节。

Control 模块接收按键信号对样式和速度进行总的控制。

Show模块是对速度值和样式值进行译码并进行扫描数码管,将当前样式和速度状态显示出来。

Delay模块则是对按键声的延时。

四、各个模块设计(波形仿真)1.f100模块功能:100分频波形仿真:VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity f100 is --100分频port(clk:in std_logic;sec:out std_logic);end entity f100;architecture getsec of f100 issignal secout : std_logic :='1';beginprocess(clk) isvariable count100: integer range 0 to 50;beginif clk'event and clk='1' thencount100:=count100+1;if count100=50 thensecout<=not secout;count100:=0;end if;end if;end process;sec<=secout;end architecture getsec;2.f10模块功能:10分频波形仿真:VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity f10 is –-10分频port(clk:in std_logic;sec:out std_logic);end entity f10;architecture getsec of f10 issignal secout : std_logic :='1';beginprocess(clk) isvariable count10: integer range 0 to 5;beginif clk'event and clk='1' thencount10:=count10+1;if count10=5 thensecout<=not secout;count10:=0;end if;end if;end process;sec<=secout;end architecture getsec;3.speed模块功能:根据DATE输入端的数值大小,产生不同频率的周期信号,从而达到控制彩灯变化速率的目的。

基于RISC-V指令集的六级流水线CPU[发明专利]

![基于RISC-V指令集的六级流水线CPU[发明专利]](https://img.taocdn.com/s3/m/d1bf7b1766ec102de2bd960590c69ec3d4bbdb54.png)

专利名称:基于RISC-V指令集的六级流水线CPU 专利类型:发明专利

发明人:康明才,顾佳浩

申请号:CN202111267138.4

申请日:20211028

公开号:CN113986354A

公开日:

20220128

专利内容由知识产权出版社提供

摘要:本发明公开了一种基于RISC‑V指令集的六级流水线CPU,该CPU能够实现RV32I基本指令集、乘法指令、CSR读写指令,并设置中断寄存器可以暂停流水线;CPU的显著特点是有六级流水线结构,分别是IF级、FD级、CSG级、EXE级、MEM级、WB级,具有较高的主频;对流水线中的冒险问题都设计了相关电路解决;利用内部前推解决了数据冒险,利用暂停流水线的方法解决了load_use 冒险,利用静态预测的方法解决了控制冒险。

该CPU具有小面积、低功耗、多功能的特点,可以在物联网和嵌入式领域广泛的应用。

申请人:南京理工大学

地址:210094 江苏省南京市孝陵卫200号

国籍:CN

代理机构:南京理工大学专利中心

代理人:陈鹏

更多信息请下载全文后查看。

基于流水线结构的DDS多功能信号发生器设计

基于流水线结构的DDS多功能信号发生器设计原华;单长虹;蒋小军【摘要】在应用FPGA进行DDS系统设计过程中,选择芯片的运行速度优化和资源利用优化常常是相互矛盾的,从发展趋势和运算要求看,系统速度指标的意义比面积指标更趋重要.基于此,介绍了一种流水线结构来优化传统的相位累加器,在QuartusⅡ开发环境下搭建系统模型、仿真及下载,并采用嵌入式逻辑分析仪分析和验证了实验结果.该系统可以完成多位频率控制字的累加,能够产生正弦波、方波和三角波,具有良好的实时性.%In the process of DDS system design by using FPGA, the chip selection for its speed optimization and resource utilization optimization is often contradictory. As for trends and operational requirements, the significance of system speed index is more important than the area index. In the light of this, a pipeline architecture is adopted to optimize the conventional phase accumulator. The system model was built, simulated and downloaded in quartus Ⅱ development environment. The experimental results were verified with an embedded logic analyzer. The results indicate that the system can complete the summation of frequency control word, produce sine, square and triangular waves, and has a good real-time performance.【期刊名称】《现代电子技术》【年(卷),期】2012(035)008【总页数】4页(P15-17,20)【关键词】流水线技术;超高速集成电路硬件描述语言;现场可编程门阵列;相位累加器【作者】原华;单长虹;蒋小军【作者单位】南华大学电气工程学院,湖南衡阳421000;南华大学电气工程学院,湖南衡阳421000;南华大学电气工程学院,湖南衡阳421000【正文语种】中文【中图分类】TN919-34随着现代电子技术的不断发展,在通信系统中往往需要在一定频率范围内提供一系列稳定和准确的频率信号,一般的振荡器已不能满足要求,这就需要频率合成技术。

关于EDA技术课程实验组织的研究

关于EDA技术课程实验组织的研究作者:方琼来源:《现代电子技术》2010年第06期摘要:在EDA课程实验组织中,这里一改传统的广播操式实验模式,取而代之的是让学生从头开始做一个实验专题“基于FPGA的流水线RISC_CPU实现”的研究。

自顶向下的设计方法和模块化的设计思想,使电子专业的学生较系统地掌握电子系统的设计技能。

通过一个实验专题项目,将电子电路、计算机硬件描述语言和EDA开发软件与仿真软件等知识综合起来,架构较宽的知识体系。

关键词:EDA技术;流水线;实验模式;架构中图分类号:G642.0文献标识码:A文章编号:1004-373X(2010)06-075-03Research of EDA Technique Course Experimental OrganizationFANG Qiong(Hangzhou Professional and Technical College,Hangzhou,310012,China)Abstract: In the EDA course experimental organization,the traditional broadcasting hold type experimental mode is unused,making the students from research of special subject experiment "Realization of FPGA Pipeline RISC_CPU" Means of top-down method and modular design make electronics professional students systematically control technical ability of electronics system.Through an experimental special subject item,electronic circuit,computer hardware description language and EDA development software with simulation software etc.The knowledge system is built.Keywords:EDA technology;pipeline;experimental mode;structure0 引言随着半导体技术和计算机技术的高速发展,现代电子系统的设计思路和方法发生着深刻的变化,电子系统设计的复杂程度也越来越高。

基于FPGA的CPU设计

基于FPGA的CPU设计FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种集成电路,可以重新配置其数字电路开关来执行不同的任务。

在FPGA 上设计CPU(中央处理器)可以提供灵活性和性能优势。

本文将介绍基于FPGA的CPU设计,并讨论其应用和优点。

基于FPGA的CPU设计的主要目标是实现一个可编程的、高性能的处理器。

设计一个CPU需要考虑多个因素,包括指令集架构、流水线设计、内存架构等。

在FPGA上设计CPU可以通过硬件定义语言(HDL)如VHDL 或Verilog来实现。

首先,需要确定CPU的指令集架构。

指令集架构定义了处理器所支持的指令和寻址模式。

常见的指令集架构有RISC(精简指令集计算机)和CISC(复杂指令集计算机)。

在设计基于FPGA的CPU时,通常选择RISC 架构,因为它有简单的指令集和流水线设计,适合在FPGA上实现。

接下来,需要设计CPU的流水线结构。

流水线是指将指令的执行过程划分为多个阶段,并行处理不同的指令。

常见的流水线阶段包括取指、译码、执行、存储和写回。

在FPGA上设计流水线需要考虑时钟频率、延迟和资源约束。

通过合理的流水线设计可以提高CPU的吞吐量和性能。

另一个重要的设计考虑因素是内存架构。

内存是CPU用来存储指令和数据的地方。

在FPGA上设计CPU时,可以使用各种类型的内存,包括寄存器、缓存和外部存储器。

选择合适的内存架构可以提高CPU的效率和性能。

此外,基于FPGA的CPU设计还可以提供高性能。

由于FPGA的并行计算能力,可以实现多个运算单元和流水线来同时执行指令,从而提高CPU的性能。

此外,FPGA上的CPU还可以与其他外部设备(如硬件加速器)集成,以提供更高的计算能力和灵活性。

基于FPGA的CPU设计在嵌入式系统、高性能计算和通信设备等多个领域具有广泛的应用。

在嵌入式系统中,FPGA上的CPU可以用于控制和处理实时数据,如机器人和工业自动化。

简述用eda技术设计电路的设计流程

EDA技术设计电路的设计流程EDA(Electronic Design Automation)是电子设计自动化的缩写,是一种利用计算机和软件工具来辅助电子电路设计的技术。

EDA技术的应用可以大大提高电路设计的效率和准确性。

本文将详细描述使用EDA技术进行电路设计的步骤和流程,以确保流程清晰且实用。

第一步:需求分析在进行任何一项工程之前,都需要明确需求。

在电路设计中也不例外。

在需求分析阶段,需要明确设计目标、功能要求、性能指标、输入输出要求等。

同时还需要考虑到实际应用环境、成本限制以及市场需求等因素。

第二步:原理设计原理设计是整个电路设计过程中最为关键的一步。

在原理设计阶段,需要根据需求分析的结果开始进行电路拓扑结构的选择和优化。

这包括选择合适的器件、元件、电源等,并确定它们之间的连接方式。

在这一阶段,可以使用EDA软件中提供的原理图绘制工具进行设计。

第三步:参数设定在进行参数设定之前,需要对所选器件和元件进行详细的调研和了解。

根据器件的数据手册,设定合适的参数。

这些参数包括电源电压、电流、频率范围、工作温度等。

还需要进行一些特殊参数的设定,如滤波器的截止频率、放大器的增益等。

第四步:电路仿真在进行实际电路设计之前,需要进行电路仿真。

通过仿真可以验证原理设计的正确性和稳定性,并对其性能进行评估。

常用的仿真工具有SPICE软件(如LTspice、Pspice)和EDA软件中提供的仿真模块。

第五步:PCB布局设计在完成原理设计和仿真之后,需要将电路转换为PCB(Printed Circuit Board)布局。

在这一阶段,需要根据原理图进行元件位置布置、走线规划以及地线和电源线的布局等。

同时还需要考虑到信号完整性、EMC(Electromagnetic Compatibility)和热管理等因素。

第六步:PCB布线设计在完成PCB布局之后,需要进行具体的PCB布线设计。

在这一阶段,需要根据信号传输特性、电磁干扰抑制等要求进行走线规划。

(完整)《EDA技术与应用》期末试卷

EDA試卷答案一、单项选择题1、2. 基于EDA软件的FPGA/CPLD设计流程为:原理图/HDL文本输入→__A__→综合→适配→____B____→编程下载→硬件测试。

P14A. 功能仿真B. 时序仿真C。

逻辑综合D。

配置3. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__A___.P25A. 软IPB. 固IPC。

硬IP D。

全对4。

综合是EDA设计流程的关键步骤,在下面对综合的描述中,_____D____是错误的。

P15A。

综合就是把抽象设计层次中的一种表示转化成另一种表示的过程。

B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件。

C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束。

D. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

5. 大规模可编程器件主要有FPGA、CPLD两类,其中CPLD通过___A__实现其逻辑功能。

P42A. 可编程乘积项逻辑B. 查找表(LUT)C。

输入缓冲 D. 输出缓冲6。

VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述_____B___.P274A. 器件外部特性B。

器件的内部功能C. 器件外部特性与内部功能D. 器件的综合约束7. 电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);下列方法中___A___不属于面积优化.P238A。

流水线设计B。

资源共享C。

逻辑优化 D. 串行化8. 进程中的信号赋值语句,其信号更新是___B____。

P134A. 立即完成B。

在进程的最后完成C。

按顺序完成 D. 都不对9。

不完整的IF语句,其综合结果可实现__A__。

《步步惊“芯”——软核处理器内部设计分析》【迷你书】

了 RISC。1979 年美国加州大学伯克利分校提出了 RISC 的概念,RISC 并不只是简单地减少

指令,更主要的目的是研究如何使计算机的结构更加简单合理以提高运算速度。其特点是指

令长度固定、指令格式种类少、寻址方式种类少、大量使用寄存器。由于在 RISC 中使用的指

令大多数是简单指令且都能在一个时钟周期内完成,因而处理器的频率得以大幅提升,同时

只限于 XILINX 芯片

MicroBlaze 的开源版本

Nios II/f

Nios II

32 Proprietary 6 1 有 有 可选

Nios II/s

Nios II

32 Proprietary 5 1 无 有 可选

Nios II/e

Nios II

32 Proprietary 无 6 无 无 可选

示。值得注意的是表 1.1 中所列出的软核处理器都是 RISC 处理器。RISC 是精简指令集计算

机(Reduced Instruction Set Computer),与之相对的是 CISC,即复杂指令集计算机(Complex

Instruction Set Computer)。在计算机的发展早期,人们使用汇编语言编程,偏好强大好用的

IP 核有 3 种:软核、固核和硬核。软核指的是在寄存器级或者门级对电路功能用 HDL (Hardware Description Language)进行描述,表现为 VHDL 或 Verilog HDL 代码。软核与生产工 艺无关,不涉及物理实现,为后续设计留有很大的空间,增大了 IP 的灵活性和适应性。用户可 以对软核的功能加以裁剪以符合特定的应用,也可以对软核的参数进行设置,包括总线宽度、 存储器容量、使能或禁止某些功能块等。固核是完成了综合的功能块,通常以网表的形式提交 给用户使用。硬核指的是以版图的形式实现的设计模块,它基于一定的设计工艺,不同的用户 可以根据自己的需要选用特定生产工艺下的硬核。软核使用灵活,但其可预测性差,延时不一 定能达到要求;硬核可靠性高,能确保性能,如速度、功耗等,可以很快投入使用。

EDA技术实用教程第6章NIOS软核SOPC系统设计

寄存器 CTL0 CTL1 CTL2 CTL3 CTL4 CTL5 名称 status estatus bstatus ienable ipending cpuid B31 ... B2 B1 保留 U 保留 EU 保留 BU 中断使能位 中断挂起位 处理器的唯一标识 B0 PIE EPIE BPIE

. . .

异常临时寄存器(1) 断点临时寄存器(2) 全局指针寄存器 堆栈指针寄存器 帧指针寄存器 异常返回地址(1) 断点返回地址(2) 返回地址寄存器

(1)寄存器R0作为0寄存器。它通常包含常数0。 因此,写它时无效,读这个寄存器的返回值为0。 (2)寄存器R1被汇编器作为临时寄存器使用,用 户程序中不能使用。 (3)寄存器R24和R29用于处理表达式;它们在用 户模式不可用。 (4)寄存器R25和R30是JTAG调试模式专用。 (5)寄存器R27和R28用于控制NiosII处理器使用 的栈。 (6)寄存器R31用于保存子程序调用的返回地址。

6.2 NiosII指令系统

NiosII处理器是精简指令架构(RISC)。其 算术和逻辑运算的操作数在通用寄存器执 行。 通过Load和Store指令在内存和寄存器 之间传送数据。 NiosII处理器的字长为32 bits。所有的寄存器都是32 bits。32-bit的 字节地址可用从小到大或从大到小的风格 赋值。在配置时,用户可能会选择一种赋 值风格。本文使用从小到大的风格。 NiosII 架构使用单独的指令和数据总线,通常叫 做哈佛架构。

NiosII CPU内部结构示意图

CPU复位信号 时钟信号 JTAG 调试模块 程序控制器和 地址生成器

指令存储器

简述用eda技术设计电路的设计流程

EDA技术设计电路的设计流程EDA(Electronic Design Automation)技术是指通过计算机软件工具辅助进行电子电路设计、分析和验证的技术。

它可以提高设计师的效率和设计质量,并减少设计周期。

本文将详细描述使用EDA技术设计电路的设计流程,包括以下步骤:1. 需求分析在进行电路设计之前,首先需要明确电路的需求和要求。

这包括功能需求、性能指标、电源和环境条件等。

设计人员需要与客户或系统工程师进行充分的沟通和交流,确保对电路设计目标的共识。

2. 架构设计在需求分析的基础上,设计人员需要进行电路的架构设计。

在这一阶段,设计人员需要选择合适的电路拓扑结构、制定电路通信方式、确定信号处理算法等。

架构设计的目标是在满足需求的前提下,最大程度地降低功耗、电路面积和成本。

3. 电路原理图设计电路原理图是电路设计的基础,它描述了各个元件和电子器件之间的连接关系。

在EDA工具中,设计人员可以通过拖拽符号、连接引脚等方式来完成电路原理图的设计。

在这一阶段,设计人员需要根据架构设计的要求选择合适的元件,并进行连接。

此外,还需要进行信号的调节和滤波等处理。

4. 电路仿真电路仿真是验证电路设计的关键步骤之一。

通过仿真,设计人员可以预测电路的性能、稳定性和可靠性。

在EDA工具中,设计人员可以通过输入电路的参数和信号来进行仿真,并通过仿真结果进行分析。

常用的电路仿真工具有SPICE、Verilog等。

4.1 直流分析直流分析可以得到电路的稳态工作状态,包括电流、电压和功率等。

设计人员需要根据设计要求设置电路的直流电源和参数,并进行仿真分析。

4.2 交流分析交流分析可以得到电路在不同频率下的频率响应和滤波效果。

设计人员需要设置交流源和参数,并进行交流仿真分析。

4.3 时序分析时序分析可以得到电路在不同时钟频率下的时序性能,包括时钟延迟、数据到达时间和时序安全裕度等。

设计人员需要设置时钟源和时钟参数,并进行时序仿真分析。

校企协同合作 促进EDA课程建设

Science &Technology Vision科技视界0引言20172,,10,“”“”,,;,,,,。

EDA ,FPGA 。

FPGA 、、,,5G、、、、。

EDA ,、、、,EDA 。

1注重课堂基础建设,EDA [1]。

,,、、、。

EDA ,EDA ,EDA 。

,A/D 、,,EDA ,EDA ,。

,FFT、FIR、,,,EDA ,EDA 。

EDA 。

,。

4:7、、DDS 、ADC 。

,,、、、FIR 、。

,EDA ,。

2师资继续教育培训《※基金项目:中国石油大学(北京)本科教学改革项目。

作者简介:薛亚茹,中国石油大学(北京)信息科学与工程学院电子信息工程系,副教授。

校企协同合作促进EDA 课程建设薛亚茹闫景富陈冲(中国石油大学(北京)信息工程学院电子信息工程系,北京102249)【摘要】EDA 是一门实践性强的课程。

为提高课程建设水平,通过加强课堂基础建设、师资继续教育培训、企业进校提升综合实践能力、校企合作培养创新能力四个层次,循序渐进提升EDA 课程质量。

通过2年的实践证明,上述建设思路提高了专业教师教学水平、学生实践能力,并建立了良好的校企合作机制。

【关键词】EDA 课程建设;校企合作;实践能力中图分类号:TN702;G642文献标识码:ADOI:10.19694/ki.issn2095-2457.2021.35.0512. All Rights Reserved.》(〔2017〕95)《2.0》,, 16。

,,、、,,,。

FPGA,。

,/RAM、FIR,EDA。

,、。

,,。

3企业进校提升综合实践能力,,。

,FPGA,,,FPGA,,。

EDA。

,,mini,,。

,MIPS CPU, ,,,,,、CPU。

,、,RFID,WIFI。

,,[2]。

4校企合作培养创新能力,,,。

,。

,,,。

,FPGA KVM,、、、、。

1080P@60Hz;IIS;;;,,NEC,。

FPGA KVM、、、,、,,。

基于龙芯开源CPU的计算机组成原理实验课程改革

摘 要:以基于龙芯开源 CPU 的计算机组成原理实验平台为载体,结合该实验平台在高校的试点使用 成果,详细探讨新一代实验平台在教学中的利弊以及可改进的方向,并对存在的问题提出建议和思考。 关键词:计算机组成原理;龙芯开源 CPU;教学实验

0 引 言

计算机组成原理是一门偏硬件的计算机基础 核心课程,பைடு நூலகம்课程对学生了解计算机各组成部件 及其内部运行机制具有重要意义。目前,国内高 校普遍采用的教材介绍了计算机指令集、CPU 设 计、存储器层次结构、I/O 系统、总线系统等计 算机核心组成部件 。 [1-2] 该课程涉及计算机的多 个部件,概念较为抽象,因此其实验环节尤为重 要。只有通过动手充分了解计算机各部件的内部 运行机制,才能加深学生对计算机组成知识的理 解,提升学生的实践动手能力,并为其今后的学 习和深造打好坚实的基础。

实验用到的龙芯实验箱型号为 LS-CPU-EXB002,主要由以下部件组成:Spartan6-XC6SLX150FGG676 FPGA 芯片、双色 LED 灯、单色 LED 灯、 LED 点阵、数码管、下载 JTAG 接口、UART 接 口、VGA 接口、LAN 接口、USB 接口、PS2 接口、 电源开关、拨码开关、脉冲开关、4×4 键盘、复 位键、LCD 显示屏。实验箱 LS-CPU-EXB-002 见 图 1。

硬件实验平台对于计算机组成原理课程的教 学效果具有重要意义,因此,如何选定合适的实 验平台是计算机组成原理课程教学改革的重点和 难点问题。为此,笔者基于龙芯开源 CPU 的教 学实验平台 [7],就计算机组成原理课程开展了一 系列教学改革尝试,并取得了较好的效果。

基金项目:国家自然科学基金项目(61602264);国家博士后自然科学基金项目(2017M611882);南京邮电大学 引进人才科研启动基金资助项目(NY215044)。 第一作者简介:王俊昌,男,讲师,研究方向为计算机系统结构,wangjc@。

EDA技术进行数字电路设计

EDA技术进行数字电路设计EDA技术进行数字电路设计EDA(ElectronicsDesignAutomation)技术是随着集成电路和计算机技术飞速发展应运而生一种高级、快速、有效电子设计自动化工具。

本文介绍了EDA技术主要特点和功能,并对将EDA技术引入到数字电路设计工作方案进行了探讨。

1EDA技术EDA(电子线路设计座自动化)是以计算机为工作平台、以硬件描述语言(VHDL)为设计语言、以可编程器件(CPLD/FPGA)为实验载体、以ASIC/SOC芯片为目标器件、进行必要元件建模和系统仿真电子产品自动化设计过程。

EDA是电子设计领域一场革命,它源于计算机辅助设计,计算机辅助制造、计算机辅助测试和计算机辅助工程。

利用EDA工具,电子设计师从概念,算法、协议开始设计电子系统,从电路设计,性能分析直到IC版图或PCB版图生成全过程均可在计算机上自动完成。

EDA代表了当今电子设计技术最新发展方向,其基本特征是设计人员以计算机为工具,按照自顶向下设计方法,对整个系统进行方案设计和功能划分,由硬件描述语言完成系统行为级设计,利用先进开发工具自动完成逻辑编译、化简、分割、综合、优化、布局布线、仿真及特定目标芯片适配编译和编程下载,这被称为数字逻辑电路高层次设计方法。

1.1EDA软件简介“EDA”就是ElectronicDesignAutomation(电子设计自动化),也就是能够帮助人们设计电子电路或系统软件工具,该工具可以使设计更复杂电路和系统成为可能。

目前进入我国并具有广泛影响EDA软件有:muhisim7、OW_AD、Protel、Viewlogio、Mentor、Synopsys、PCBWId、Cadence、MicmSim等等,这些软件各具特色,大体分为芯片级设计工具、电路板级设计工具、可编程逻辑器件开发工具和电路仿真工具等几类;其中Protel是国内最流行、使用最广泛一种印制电路板设计首选软件,由澳大利亚protdTechnology 公司出品,过去只是用来进行原理图输入和PCB版图设计,从Protel98开始,加入了模拟数字混合电路仿真模块和可编程逻辑器件设计模块,1999年Protel推出了功能更加强大EDA综合设计环境Protel99,它将EDA全部内容整合为一体,成为完整EDA软件,因而该软件发展潜力很大,但它最具特色和最强大功能仍是原理图输人和PCB版图设计。

流水线CPU设计文档(0002)

流水线CPU设计文档流水线CPU 设计文档张路一、 设计结构图:二、 设计概要:该处理器采用5级流水线技术,在处理器中,指令的处理分5阶段完成:取指、译码、执行、访存、写回。

每阶段与前一阶段采用寄存器组暂存指令数据信息和控制信号,完成对指令的流水化处理。

1、 取指阶段:PCImemReg32DMem DecoderExt9NextPC MULT ALUW1R1R2WE BusA BusB BusCBusAALUOPFLAGSResult FLAGSResultMux MuxMultI F /I DImm9ALUOPI D /E XRegW Mux BusBBSrc E X /M EMemWrRegSrcImm32Imm32ASR AddrMemWr EX /M EDataInDataOu tRdRd RdDataInMemOut ALUOutMuxRegSrcRegWRdR3BusCLabelPCFlagsLabelRs2BranOpBranOpBusBMuxASrc MuxASRSrc ForwardRd Ex:RegW RegSrc RdMem:RegW RegSrc RdWB:RegW RegSrc BSrc Asrc RS1RS2RDFwd.B Fwd.A BMux AMuxStallStallClkClkClkClkClkClkClkClkStallResetResetResetReset ResetPCImemNextPC I F /I DPCFlagsLabelRs2BranOpStallClkClkClkResetResetStall通过PC 寄存器中的值在IMem 中取出指令,送入IF/ID 寄存器中。

2、 译码阶段Reg32DecoderExt9W1R1R2WE BusA BusB BusCMultI F /I DImm9ALUOPI D /E XRegW BSrc MemWrRegSrcImm32Imm32RdDataInR3LabelBranOpASrc ASRSrc BSrcAsrc RS1RS2RDClkClkClkReset译码阶段中,根据指令译出相应的控制信号,同时将使用的寄存器和扩展之后的立即数送入ID/EX 寄存器中。

实验报告---流水线cpu(处理器)的实现

本科实验报告实验名称:流水线机制CPU的实现一、实验内容和原理实验内容:1、分析ARM指令集,明确指令功能、指令在CPU中执行各阶段中的行为;2、设计ARM处理器的数据通路和控制通路,画出指令描述表和指令的状态转换图;3、利用Vivado软件,用V erilog硬件描述语言描述处理器中的各个分部件,每个分部件通过功能仿真;4、利用Vivado软件,用V erilog硬件描述语言实现分部件的互连,即实现数据通路和控制通路;5、编写测试用的汇编指令,并将汇编指令转换为二进制的指令编码,并且加载到处理器中的指令存储器中。

6、将ARM处理器编程下载至FPGA实验板,运行测试程序,并通过开发板上的led或数码管显示执行结果。

二、实验步骤与实验结果写出实验操作的总体思路、操作规范和主要注意事项;按顺序记录实验中每一个环节和实验现象。

画出必要的实验装置结构示意图,并配以相应文字说明;(一)说明你所实现的ARM处理器是多周期还是流水线CPU;一共实现了多少条指令?测试通过了多少条指令?我实现的处理器是流水线的,一共实现了10条指令,测试通过了10条指令。

(二)描述你的设计思路,如果你实现了多周期和流水线CPU,请分别描述多周期CPU设计思路:流水线处理器设计思路:由于将多周期的阶段分成五级流水,无法设置统一的控制信号,而是让每一级流水段根据自己输入的指令产生控制信号,即将各个控制信号分属到两级流水之间的寄存器当中。

本想设计一个移位寄存器来将指令分别送入各级寄存器,但是发现不是特别有必要这样做,因为可以将指令一级一级传递下去可以实现同样的功能。

总共分五级流水,取指,译码,执行,存储,写回。

如果指令之间出现相关则设置空指令,如果遇到空指令则所有控制信号为0,不产生任何有影响的操作。

(三)对于实现的多周期处理器,为你所实现的指令画出指令描述表,和指令的状态转换图,一类指令可以画一个表或一个状态转换图(四)画出你设计的处理器(多周期和流水线)的数据通路和控制通路的合成图,要求为viso图或其他可再次修改的图,不能仅用无法修改的图片流水线数据通路(viso图双击用viso打开)(一)如果你设计的是流水线CPU,描述你的设计思路,实现方法,和多周期实现时的异同。

(完整word版)MIPS流水线CPU的verilog实现

(完整word版)MIPS流水线CPU的verilog实现一、实验目的1.了解提高CPU性能的方法。

2.掌握流水线MIPS微处理器的工作原理。

3.理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

4.掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器,具体要求如下:1.至少运行下列MIPS32指令。

(1)算术运算指令:ADD、ADDU、SUB、SUBU、ADDI、ADDIU。

(2)逻辑运算指令:AND、OR、NOR、XOR、ANDI、ORI、XORI、SLT、SLTU、SLTI、SLTIU。

(3)移位指令:SLL、SLLV、SRL、SRLV、SRA。

(4)条件分支指令:BEQ、BNE、BGEZ、BGTZ、BLEZ、BLTZ。

(5)无条件跳转指令:J、JR。

(6)数据传送指令:LW、SW。

(7)空指令:NOP。

2.采用5级流水线技术,对数据冒险实现转发或阻塞功能。

3.在XUP Virtex-Ⅱ Pro 开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz。

三、实验原理1.总体设计流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用于高档CPU的架构中。

根据MIPS处理器的特点,将整体的处理过程分为取指令(IF)、指令译码(ID)、执行(EX)、存储器访问(MEM)和寄存器会写(WB)五级,对应多周期的五个处理阶段。

如图3.1所示,一个指令的执行需要5个时钟周期,每个时钟周期的上升沿来临时,此指令所代表的一系列数据和控制信息将转移到下一级处理。

图3.1 流水线流水作业示意图由于在流水线中,数据和控制信息将在时钟周期的上升沿转移到下一级,所以规定流水线转移变量命名遵守如下格式:名称_流水线级名称例如:在ID级指令译码电路(Decode)产生的寄存器写允许信号RegWrite在ID级、EX级、MEM级和WB级上的命名分别为RegWrite_id、RegWrite_ex、RegWrite_mem和RegWrite_wb。

基于FPGA开放CPU的设计与实现的开题报告

基于FPGA开放CPU的设计与实现的开题报告一、选题背景随着信息技术的不断发展,计算机已经成为现代社会的基本设备,其应用领域也越来越广泛。

同时,开放源代码的操作系统也越来越受到欢迎,这样的开源操作系统使得开发者更加方便地进行软件开发。

而硬件开放性的问题也引起了越来越多的关注,特别是在嵌入式系统领域中。

这些设备通常需要高度定制的硬件,以满足特定的应用需求。

因此,开放的硬件平台也十分重要。

二、选题意义本选题主要是探究一种基于FPGA(Field Programmable Gate Array)的CPU(Central Processing Unit)开放设计与实现。

FPGA作为一种可编程的硬件平台,可以通过编程方式改变其硬件功能,这为CPU的实现提供了一种新的思路。

在此基础上,本选题将重点研究开放CPU的设计和实现方法,探索可编程硬件的学习和应用。

三、研究内容本项目的研究内容主要包括以下三个方面:(1)CPU体系结构设计:设计和实现一个基于FPGA的开放CPU体系结构,包括指令集设计和流水线处理器等模块的设计。

(2)CPU应用开发:开发并测试适用于CPU的应用程序,包括操作系统和应用程序等。

(3)实验验证与分析:通过实验验证和性能分析,评估开放CPU实现的可行性和有效性。

四、预期成果本项目的预期成果主要包括:(1)完成基于FPGA的CPU体系结构设计和实现;(2)开发适用于CPU的应用程序;(3)验证开放CPU实现的可行性和有效性。

五、研究方法本项目采用的研究方法包括:(1)文献调研:通过查阅相关文献,了解目前CPU的设计和实现方法,为本项目的研究提供基础和参考。

(2)硬件设计:根据CPU的体系结构设计,利用Verilog HDL进行硬件设计。

(3)软件开发:开发适用于CPU的应用程序。

(4)实验验证与分析:通过实验验证和性能分析,评估开放CPU 实现的可行性和有效性。

六、研究进度安排本项目的研究进度安排如下:(1)前期准备阶段(2021年4月-2021年5月):调研相关文献,熟悉相关硬件平台和开发工具。

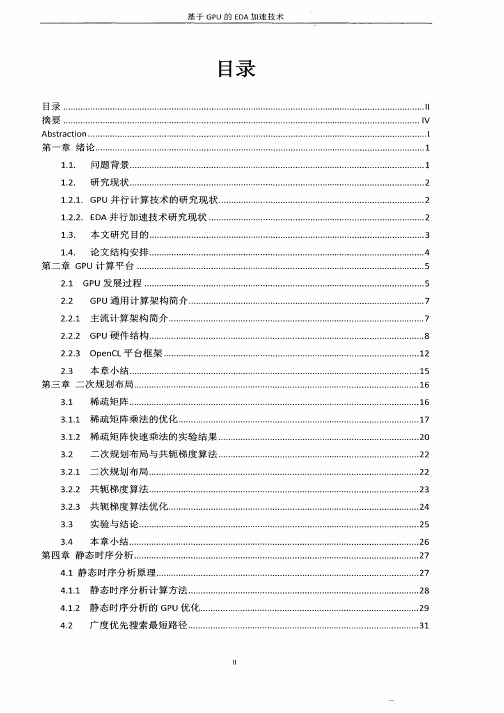

基于GPU的EDA加速技术

供的完全开放性开发工具包,可以让程序开发人员更加充分的利用A M 。

硬件,完成在变化性快速增长的平台与操作系统上,开发出更快速、更节能的应用程序的梦想。

2.2.2 G P u 硬件结构现代G p u 硬件体系结构的组织方式是一种多层次的组织,不同型号的G p u会有不同的参数,如A Lu 的个数,全局内存和局部内存的大小等,但总体来说,结构还是相似的。

流处理器找盆黛熟噩噩图..一.....一.一....︸线程处理器气流核心‘口口口口一图2.1.G p u 核心结构最粗粒度的概念是流处理器,一个G Pu 会拥有一个或者几个流处理器。

一个流处理器里含有数个S IM O 引擎。

每个SIM O 引擎中又包含了很多个线程处理器。

每个线程处理器可以按内核所规定的操作对独立的数据执行。

一个线程处理器里面还包含了一定数量的计算核心,这些核心是最基本处理单元,它们可以进行整数、单精度浮点数、双精度浮点数等操作。

在同一时间内,一个sIM 。

引擎中的所有的线程处理器都执行相同的指令集,不同的sIM 。

引擎是可以执行不同的指令的。

一个线程处理器中可以最多同时处理五条指令。

在图中可知,一个线程处理器中有五个流核心(S treom c ore)。

其中一个是可以计算超越函数的【191,剩下四个可以同时计算单精度浮点数。

双精度浮点数计算是会将两个核心一起使用,来满足双精度的计算要求,所以说一般G pu 双精度浮点数的计算速度是单精度的一半,所以相对来说要稍微慢一些。

除了流核心,每个线程处理器还包含流控制器,流控制器用来处理条件分支转移和命中不命中时结果的保留和抛弃。

S IM D 引擎S IM D引擎S IM D引擎S IM O引擎指令和控制流T流核心图2.2.AT I G p U结构图不同型号的6p u的细节参数都是不同的。

例如,在灯一Rad eo n35706p u这款G p u里面一共包含了4个SIM O引擎,每个SIM O引擎里面有16个线程处理器,并且每个处理器里面有5个St「eam Co re。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于EDA技术的流水线CPU创新设计

基于EDA技术设计的一种五级流水线CPU,它将指令分解为取指令、指令译码、指令执行、访问存储器、数据写回五阶段流水处理。

首先进行结构设计,然后解决流水线CPU的各项相关问题,再进行各模块设计。

最后基于Cyclone Ⅲ系列FPGA硬件平台和QuartusⅡ工具开发平台,利用EP3C40Q240C8型FPGA 芯片进行设计与调试。

标签:EDA;流水线;CPU

引言

CPU是由基本的功能模块和与之相连的数据通路组成,对于CPU的设计,首先必须了解其结构的细节和功能模块的内容。

然后对各模块电路进行编辑设计、逻辑综合、时序仿真和硬件设计,最后组装完成整个硬件系统。

在这个过程中还包括指令系统的设计和软件程序调试等步骤。

在流水线CPU设计过程中重点解决结构冲突、数据冲突、控制冲突三大问题。

1 流水线CPU工作原理

1.1 流水线原理

对于一条具体的指令执行过程,通常可以分成五个部分:取指令,指令译码,取操作数,运算,写结果。

其中前面三个步骤一般由指令控制器完成,后面两步则由运算器完成。

指令控制器完成了对第一条指令的处理后,不等待运算器完成后续的处理直接开始对第二条指令的处理。

1.2 CPU的结构与功能

CPU是负责执行指令的,图1为一个简单指令的CPU结构图。

对于冯·诺依曼结构的计算机来说,一旦程序进入存储器后,就可由计算机自动完成取指令和执行指令的任务,控制器就是专门用于完成此项工作的,它负责协调并控制计算机各个部件执行程序的指令序列,其基本功能是取指令,分析指令和执行指令。

1.3 流水线CPU工作原理

流水线是一个可以提高CPU运行效率的技术,它的核心思想是把多條指令的不同执行阶段重叠,让CPU同时处理多条指令。

在流水线CPU中,每条指令的执行过程被分成多个执行阶段。

只有当某指令的执行阶段都完成后,该指令才算执行完毕。

在每一个指令执行阶段中,当一条指令在该阶段中完成执行后,下一条指令将立即进入到该执行阶段来执行。

当流水线处于饱和状态时,将同时有

流水线级数的指令在同时运行。

如图2所示。

1.4 指令集

指令集是指CPU指令系统所能识别执行的全部指令的集合。

处理器要完成计算任务,需要具备运算、控制、传送等指令。

运算指令是由运算器单元(ALU)实现,包括算术运算指令、逻辑指令和位移指令。

控制指令是由除了做运算外的其他操作指令,如循环、跳转、CPU控制等指令构成,由CPU控制器单元实现。

数据传送指令是完成数据传送的任务,如寄存器、存储器交换数据及自身交换数据的指令等。

2 流水线CPU创新设计

2.1 流水线工作的五个阶段

取指令阶段(IF),从指令存储器中获取指令存入IR寄存器,并更新PC寄存器的值。

该阶段完成计算下一条指令的地址(+1)以及取指操作,加法器完成加1操作,Lpm_Instrom完成取指操作。

指令译码阶段(ID),由IR寄存器中的指令的op和func字段译码出各个阶段需要的控制信号,同时从寄存器组RegSet 中获取EXE阶段所需要的操作数并将指令的立即数进行扩展。

指令执行阶段(EXE),根据操作数计算出结果,算数运算由ALU完成,移位运算由移位器完成,通过控制信号Resultop选择执行结果。

访问存储器阶段(MEM),把EXE 阶段计算的结果作为数据存储器的地址输入端读取数据,若数据存储器写使能信号DMwen为高电平,那么需要把rt寄存器的数据写入数据存储器的对应存储单元。

数据写回阶段(WB),选择写回寄存器组RegSet的数据,根据前面的流水段传递的控制信号REwen和目的寄存器RegDest将数据写回。

在每一个阶段完成一条指令在该阶段的执行任务之后,将进下一条指令的执行。

这样,每两个阶段之间都需要有一组寄存器来保存刚刚执行完成的指令的执行结果。

该执行结果将交给下一个执行阶段,进行下一个阶段的处理任务。

2.2 流水线CPU顶层设计

CPU主要由以ALU为核心的运算器模块、以程序计数器PC和地址寄存器AR为核心的数据通路模块、以微指令控制器为核心的控制器模块、以程序控制器和数据RAM为核心的存储模块四个模块构成。

算数逻辑单元模块主要有ALU运算器,数据寄存器DR等部件,ALU运算器是CPU的核心,它可以执行算数运算,也可以执行逻辑运算。

数据缓冲寄存器DR为ALU提供一个或两个参与运算的操作数,同时作为CPU、外部设备、主存之间的信息中转站,对数据起暂存作用。

数据通路模块主要由程序计数器PC,地址寄存器AR,指令寄存器IR组成。

程序计数器PC的功能是给出在主存中的下一条指令的地址。

PC值的变化分为两种情况,一是指令顺序执行的情况,二是跳转指令的情况。

地址寄存器AR用来保存当前CPU所要访问的主存单元

或I/O端口的地址。

指令寄存器IR用来保存当前CPU正在执行的一条指令。

微程序控制器主要由控制存储器、微指令寄存器和微指令地址形成部件三部分组成。

控制存储器用以存放指令系统所对应的全部微程序。

微程序控制器主要由微指令控制电路、微地址寄存器和微指令存储器三个模块组成。

微地址分支转移控制电路根据来自指令寄存器IR的指令操作码生成一个微地址的控制信号,控制微程序按正确顺序执行微程序和实现分支转移。

微地址寄存器是用来存放从微指令存储器中读出的一条微指令信息,由控制字段和下地址字段组成。

微指令存储器是存取微程序的原件,其原件的生成可直接调用LPM宏模块。

组成的流水线CPU顶层结构图如图3所示。

3 结束语

流水线CPU是现代CPU非常流行的设计方式,它在只需要添加少数硬件的条件下大大提高了CPU的性能。

本设计从了解并研究CPU工作原理开始,到熟悉并运用EDA技术,再到流水线CPU局部器件设计、模块设计、整体设计,最后在FPGA硬件平台和QuartusⅡ工具开发平台进行模拟调试验证了本设计符合设计要求。

但本设计的CPU与实际应用中的CPU还存在较大的差距,在接下来的研究中小组成员仍将不断丰富流水线CPU的知识,将本设计的流水线CPU升级至应用级别。

参考文献

[1]史展,李占宣.基于FPGA的嵌入式CPU的VHDL设计[J].科技创新与应用,2013(9).

[2]潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2013(4).

[3]潘松,潘明,黄继业.现代计算机组成原理[M].北京:科学出版社,2013.。