EDA工具手册约束管理器分册

手册大全--candence使用手册仿真分册

Candence使用手册_仿真分册前言PCB仿真Cadence软件是我们公司统一使用的原理图设计、PCB设计、高速仿真的EDA工具。

进行仿真工作需要有很多方面的知识,须对高速设计的理论有较全面的认识,并对具体的单板原理有一定的了解,还需具备仿真库的相关知识等。

在这个分册中仅对仿真软件的使用进行较详细的阐述,还介绍高速设计的一些相关理论,仿真过程是基于Allegro SPB 15.7的PCB SI模块进行的。

其他知识,如仿真库的知识、约束管理器等请参阅专门的使用手册。

在此非常感谢网络南研 EDA和本部 EDA对此手册的支持。

第一章高速设计与PCB仿真流程本章介绍高速PCB仿真设计的基础知识和重要意义,并介绍基于Cadence 的Allegro SPB15.7的PCB仿真流程。

1.1高速信号与高速设计随着通信系统中逻辑及系统时钟频率的迅速提高和信号边沿不断变陡,PCB的走线和板层特性对系统电气性能的影响也越发显著。

对于低频设计,走线和板层的影响要求不高甚至可以完全忽略不计。

当频率超过 50MHz时,PCB走线则必须以传输线考虑,而在评定系统性能时也必须考虑 PCB 板材的电参数影响。

当系统时钟频率达到120MHz及更高时,就只能使用高速电路设计方法,否则基于传统方法设计的PCB将无法工作。

因此,高速电路设计技术已经成为电子系统设计师必须采取的设计手段,只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性。

高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性问题。

通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路占整个电子系统的一定份量(比如说1/3),就称为高速电路。

实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)引发了信号传输的非预期结果。

因此,通常约定如果线传播延时大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应,见图1-1所示。

集成电路设计EDA工具应用作业指导书

集成电路设计EDA工具应用作业指导书第1章 EDA工具概述 (5)1.1 EDA工具发展历程 (5)1.2 EDA工具在集成电路设计中的作用 (5)1.3 常用EDA工具简介 (6)第2章集成电路设计流程 (6)2.1 设计准备阶段 (6)2.1.1 需求分析 (6)2.1.2 技术选型 (6)2.1.3 设计规划 (6)2.1.4 电路架构设计 (6)2.2 设计实现阶段 (6)2.2.1 电路设计 (7)2.2.2 仿真验证 (7)2.2.3 布局布线 (7)2.2.4 版图设计 (7)2.3 设计验证阶段 (7)2.3.1 功能验证 (7)2.3.2 时序验证 (7)2.3.3 电源完整性分析 (7)2.3.4 热分析 (7)2.4 设计后处理阶段 (7)2.4.1 版图检查 (7)2.4.2 后仿真分析 (7)2.4.3 生产数据 (7)2.4.4 文档编写 (7)第3章数字集成电路设计 (7)3.1 数字电路设计基础 (8)3.1.1 数字逻辑元件 (8)3.1.2 组合逻辑电路设计 (8)3.1.3 硬件描述语言(HDL) (8)3.2 逻辑合成与优化 (8)3.2.1 逻辑合成 (8)3.2.2 逻辑优化 (8)3.2.3 EDA工具在逻辑合成与优化中的应用 (8)3.3 时序分析 (8)3.3.1 时序分析基础 (9)3.3.2 时序约束与优化 (9)3.3.3 EDA工具在时序分析中的应用 (9)3.4 电源网络设计 (9)3.4.1 电源网络设计基础 (9)3.4.2 电源网络设计方法 (9)3.4.3 EDA工具在电源网络设计中的应用 (9)第4章模拟集成电路设计 (9)4.1 模拟电路设计基础 (9)4.1.1 模拟电路概述 (9)4.1.2 模拟电路设计流程 (9)4.1.3 模拟电路设计方法 (9)4.2 模拟电路仿真 (9)4.2.1 仿真概述 (10)4.2.2 仿真工具与流程 (10)4.2.3 仿真参数设置与优化 (10)4.3 模拟电路布局与布线 (10)4.3.1 布局与布线概述 (10)4.3.2 布局设计 (10)4.3.3 布线设计 (10)4.4 模拟电路后处理 (10)4.4.1 后处理概述 (10)4.4.2 版图检查与修正 (10)4.4.3 后仿真与功能验证 (10)4.4.4 生产工艺与封装 (10)第5章混合信号集成电路设计 (10)5.1 混合信号电路设计基础 (10)5.1.1 混合信号电路概述 (11)5.1.2 混合信号电路设计流程 (11)5.1.3 混合信号电路关键功能指标 (11)5.2 混合信号电路仿真 (11)5.2.1 仿真方法 (11)5.2.2 仿真工具 (11)5.2.3 仿真步骤 (12)5.3 混合信号电路布局与布线 (12)5.3.1 布局与布线概述 (12)5.3.2 布局与布线原则 (12)5.3.3 布局与布线工具 (12)5.4 混合信号电路后处理 (12)5.4.1 后处理概述 (12)5.4.2 后处理流程 (12)5.4.3 后处理工具 (13)第6章射频集成电路设计 (13)6.1 射频电路设计基础 (13)6.1.1 射频信号特性 (13)6.1.2 射频电路元件 (13)6.1.3 射频电路拓扑 (13)6.2 射频电路仿真 (13)6.2.1 电路仿真原理 (13)6.2.2 仿真工具及参数设置 (13)6.2.3 仿真结果分析 (14)6.3 射频电路布局与布线 (14)6.3.1 布局原则 (14)6.3.2 布线技巧 (14)6.3.3 射频电路版图设计 (14)6.4 射频电路后处理 (14)6.4.1 参数提取 (14)6.4.2 功能评估 (14)6.4.3 优化策略 (14)第7章系统级集成电路设计 (14)7.1 系统级电路设计基础 (14)7.1.1 设计流程概述 (15)7.1.2 设计规范与要求 (15)7.1.3 顶层模块划分 (15)7.1.4 通信协议与接口设计 (15)7.2 系统级电路仿真 (15)7.2.1 仿真工具与流程 (15)7.2.2 仿真模型与参数设置 (15)7.2.3 功能仿真与功能仿真 (15)7.2.4 仿真结果分析 (15)7.3 系统级电路布局与布线 (15)7.3.1 布局布线概述 (15)7.3.2 布局布线策略与方法 (15)7.3.3 布局布线工具与流程 (16)7.3.4 布局布线优化与后处理 (16)7.4 系统级电路后处理 (16)7.4.1 后处理概述 (16)7.4.2 版图检查与修正 (16)7.4.3 参数提取与后仿真 (16)7.4.4 设计交付与生产 (16)第8章设计验证与测试 (16)8.1 功能验证 (16)8.1.1 验证目的 (16)8.1.2 验证方法 (16)8.1.3 验证步骤 (16)8.2 时序验证 (17)8.2.1 验证目的 (17)8.2.2 验证方法 (17)8.2.3 验证步骤 (17)8.3 功耗验证 (17)8.3.1 验证目的 (17)8.3.2 验证方法 (17)8.3.3 验证步骤 (17)8.4 DFT与测试 (18)8.4.1 DFT(Design for Testability)设计 (18)8.4.2 测试方法 (18)8.4.3 测试步骤 (18)第9章设计收敛与优化 (18)9.1 设计收敛策略 (18)9.1.1 确定设计目标 (18)9.1.2 分阶段收敛 (18)9.1.3 迭代优化 (18)9.1.4 设计收敛监控 (19)9.2 逻辑合成优化 (19)9.2.1 逻辑简化 (19)9.2.2 逻辑层次优化 (19)9.2.3 时序优化 (19)9.2.4 功耗优化 (19)9.3 布局与布线优化 (19)9.3.1 布局优化 (19)9.3.2 布线优化 (19)9.3.3 热点分析与优化 (19)9.4 电源网络优化 (19)9.4.1 电源规划 (19)9.4.2 电源网络分割 (19)9.4.3 电源网络优化算法 (20)9.4.4 电源噪声分析与控制 (20)第10章 EDA工具在特定领域应用 (20)10.1 EDA工具在嵌入式系统设计中的应用 (20)10.1.1 硬件描述语言(HDL)设计 (20)10.1.2 仿真验证 (20)10.1.3 逻辑综合 (20)10.1.4 布局布线 (20)10.2 EDA工具在人工智能芯片设计中的应用 (20)10.2.1 高层次综合 (21)10.2.2 基于FPGA的加速 (21)10.2.3 数据流优化 (21)10.3 EDA工具在物联网芯片设计中的应用 (21)10.3.1 低功耗设计 (21)10.3.2 射频设计 (21)10.3.3 系统集成 (21)10.4 EDA工具在汽车电子设计中的应用 (21)10.4.1 功能安全 (21)10.4.2 硬件在环仿真 (21)10.4.3 系统级设计 (22)第1章 EDA工具概述1.1 EDA工具发展历程电子设计自动化(Electronic Design Automation,EDA)工具起源于20世纪60年代,集成电路(Integrated Circuit,IC)技术的飞速发展,EDA工具逐渐成为集成电路设计领域不可或缺的辅助工具。

EDA工具手册约束管理器分册

EDA工具手册约束管理器分册目录第一章约束管理器介绍 (4)1.1约束管理器简介 (4)1.2约束管理器界面简介 (8)1.2.1worksheet selector (8)1.2.2用户接口 (9)1.2.3View选项 (9)1.3启动约束管理器 (11)第2章OBJECTS介绍 (12)2.1P IN-P AIRS (13)2.1.1Pin-Pair规则 (14)2.2N ETS和X NETS (14)2.3B USES (15)2.4M ATCH G ROUPS (15)2.4.1如何确定target pin pair (16)2.4.2相对/匹配的群组规则 (16)2.5D IFF P AIRS (16)2.5.1差分对工作表 (17)2.5.2差分计算器(Differential Calculator)的使用方法 (19) 2.5.3差分对规则 (19)2.6D ESIGNS AND S YSTEMS (20)第3章设置网络的走线约束 (21)3.1.1设置网络的最大最小传输延迟 (21)3.1.2设置网络相对传输延迟 (24)3.1.3设置差分对约束 (26)3.1.4查看网络规范格式和物理格式 (28)第4章设置网络的时序和信号完整性约束 (30)4.1设置时序约束 (30)4.2设置信号完整性约束 (32)4.2.1设置电气属性约束 (32)4.2.2设置反射属性约束 (33)第5章电子约束创建和应用 (35)5.1创建ECS ET (35)5.2指定ECS ET给网络 (40)5.3不考虑ECS ET的缺省约束值 (41)5.4在原理图中查看ECS ET (41)第6章ECOS实现 (43)6.1在原理图中增加网络 (43)6.2在原理图中修改约束 (45)6.3在约束管理器中修改约束 (46)6.4在约束管理器中删除约束 (46)6.5在原理图中重新命名网络 (47)第7章在原理图和PCB之间同步约束 (50)7.1从原理图中输出约束 (50)7.2在PCB D ESIGN中查看和添加约束 (50)7.3在原理图中导入并查看约束 (51)7.4在PCB和原理图之间同步约束的两种模式 (52) 7.4.1用原理图中的约束重写PCB中的约束 (53) 7.4.2在原理图中导入PCB中变更的约束 (56)第8章约束分析 (58)8.1查看工作表单元格和对象 (58)8.2定制约束、定制测量和定制激励 (59)8.2.1定制约束 (59)8.2.1.1 用户定义的属性 (59)8.2.1.2 约束的定制测量 (59)第9章SCHEDULING NETS (61)9.1S CHEDULING N ETS (61)9.2S CHEDULING N ETS-R EVISITED (65)第10章相对传输延迟 (68)第11章MATCH DELAY (73)第12章解决DRC冲突 (74)第13章约束管理器 (76)13.1层次设计中的电子约束 (76)第一章约束管理器介绍约束管理器是一个交叉的平台,以工作簿和工作表的形式在Cadence PCB设计流程中用于管理所有工具的高速电子约束。

candence使用手册仿真分册实用手册

Candence使用手册_仿真分册前言PCB仿真Cadence软件是我们公司统一使用的原理图设计、PCB设计、高速仿真的EDA工具。

进行仿真工作需要有很多方面的知识,须对高速设计的理论有较全面的认识,并对具体的单板原理有一定的了解,还需具备仿真库的相关知识等。

在这个分册中仅对仿真软件的使用进行较详细的阐述,还介绍高速设计的一些相关理论,仿真过程是基于Allegro SPB 15.7的PCB SI模块进行的。

其他知识,如仿真库的知识、约束管理器等请参阅专门的使用手册。

在此非常感谢网络南研 EDA和本部 EDA对此手册的支持。

第一章高速设计与PCB仿真流程本章介绍高速PCB仿真设计的基础知识和重要意义,并介绍基于Cadence 的Allegro SPB15.7的PCB仿真流程。

1.1高速信号与高速设计随着通信系统中逻辑及系统时钟频率的迅速提高和信号边沿不断变陡,PCB的走线和板层特性对系统电气性能的影响也越发显著。

对于低频设计,走线和板层的影响要求不高甚至可以完全忽略不计。

当频率超过 50MHz时,PCB走线则必须以传输线考虑,而在评定系统性能时也必须考虑 PCB 板材的电参数影响。

当系统时钟频率达到120MHz及更高时,就只能使用高速电路设计方法,否则基于传统方法设计的PCB将无法工作。

因此,高速电路设计技术已经成为电子系统设计师必须采取的设计手段,只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性。

高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性问题。

通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路占整个电子系统的一定份量(比如说1/3),就称为高速电路。

实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)引发了信号传输的非预期结果。

因此,通常约定如果线传播延时大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应,见图1-1所示。

手册大全--candence使用手册仿真分册

Candence使用手册_仿真分册前言PCB仿真Cadence软件是我们公司统一使用的原理图设计、PCB设计、高速仿真的EDA工具。

进行仿真工作需要有很多方面的知识,须对高速设计的理论有较全面的认识,并对具体的单板原理有一定的了解,还需具备仿真库的相关知识等。

在这个分册中仅对仿真软件的使用进行较详细的阐述,还介绍高速设计的一些相关理论,仿真过程是基于Allegro SPB 15.7的PCB SI模块进行的。

其他知识,如仿真库的知识、约束管理器等请参阅专门的使用手册。

在此非常感谢网络南研 EDA和本部 EDA对此手册的支持。

第一章高速设计与PCB仿真流程本章介绍高速PCB仿真设计的基础知识和重要意义,并介绍基于Cadence 的Allegro SPB15.7的PCB仿真流程。

1.1高速信号与高速设计随着通信系统中逻辑及系统时钟频率的迅速提高和信号边沿不断变陡,PCB的走线和板层特性对系统电气性能的影响也越发显著。

对于低频设计,走线和板层的影响要求不高甚至可以完全忽略不计。

当频率超过 50MHz时,PCB走线则必须以传输线考虑,而在评定系统性能时也必须考虑 PCB 板材的电参数影响。

当系统时钟频率达到120MHz及更高时,就只能使用高速电路设计方法,否则基于传统方法设计的PCB将无法工作。

因此,高速电路设计技术已经成为电子系统设计师必须采取的设计手段,只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性。

高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性问题。

通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路占整个电子系统的一定份量(比如说1/3),就称为高速电路。

实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)引发了信号传输的非预期结果。

因此,通常约定如果线传播延时大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应,见图1-1所示。

EDA 软件 说明书

12.安装完成可通过界面配置安装产品,如下:

15

13.出现以下画面,选择 OK 继续: 14.出现以下画面,点击“Select All”,选择 OK 继续:

16

15.根据实际需求选择相关配置信息,若干分钟后完成安装:

16.进入安装目录,建立链接:

17

17.若需要运行安装程序,则运行: 18.若有补丁需要更新,在安装界面选择“Update Installed Products”,后续步骤与安 装类似,具体过程略:

2.进入安装程序,如下;首先,指定安装包文件存放路径:

3.第二步,选择安装版本:

3

4.第三步,指定 ID、管理员名称及管理员联系信息等内容: 5.第四步,选择准备安装的产品内容、产品安装平台: 6.第五步,最后确认安装路径、安装文件大小等相关信息:

4

7.第六步,完成安装:

8.安装完成后修改.cshrc 文件,添加以下内容:

1.将可执行文件 copy 到安装目录: 2.更改文件权限为可执行: 3.运行安装文件:

26

4.选择安装路径: 5.修改配置文件:

27

6.启动程序: $source .cshrc $caliber –gui

7.完成。 六、License 环境变量:

1.Cadence 私有环境变量 DS_LIC_FILE

5

9.激活.cshrc 文件,并运行 dc_shell:

10.完成。 第三阶段:STAR-RCXT 安装

1.创建安装文件夹,将安装文件 copy 到安装文件夹: 2.进入安装文件夹,解压缩:

6

3.进入安装程序:

7

4.完成安装:

5.修改配置文件(打开、激活等步骤略): 完成。 第四阶段:HSPICE 安装

常用EDA工具介绍

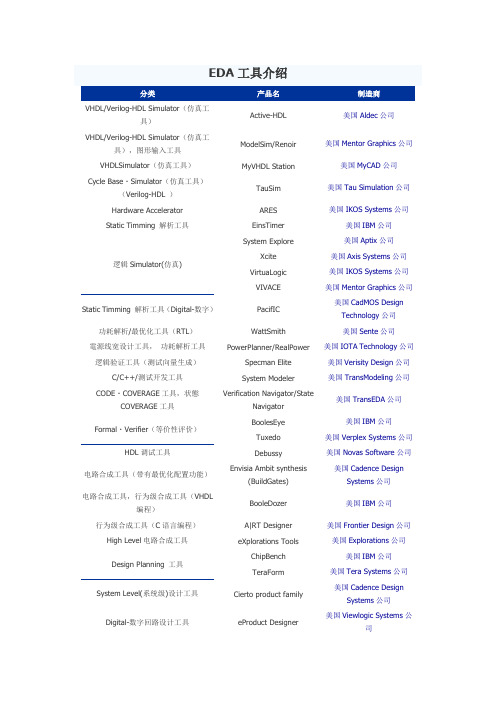

EDA工具介绍VHDL/Verilog-HDL Simulator(仿真工具)Active-HDL 美国Aldec公司VHDL/Verilog-HDL Simulator(仿真工具),图形输入工具ModelSim/Renoir 美国Mentor Graphics公司VHDLSimulator(仿真工具)MyVHDL Station 美国MyCAD公司Cycle Base・Simulator(仿真工具)(Verilog-HDL )TauSim 美国Tau Simulation公司Hardware Accelerator ARES 美国IKOS Systems公司Static Timming 解析工具EinsTimer 美国IBM公司逻辑Simulator(仿真) System Explore 美国Aptix公司Xcite 美国Axis Systems公司VirtuaLogic 美国IKOS Systems公司VIVACE 美国Mentor Graphics公司Static Timming 解析工具(Digital-数字)PacifIC 美国CadMOS Design Technology公司功耗解析/最优化工具(RTL)WattSmith 美国Sente公司電源线宽设计工具,功耗解析工具PowerPlanner/RealPower 美国IOTA Technology公司逻辑验证工具(测试向量生成)Specman Elite 美国Verisity Design公司C/C++/测试开发工具System Modeler 美国TransModeling公司CODE・COVERAGE工具,状態COVERAGE工具Verification Navigator/StateNavigator美国TransEDA公司Formal・Verifier(等价性评价)BoolesEye 美国IBM公司Tuxedo 美国Verplex Systems公司HDL调试工具Debussy 美国Novas Software公司电路合成工具(带有最优化配置功能)Envisia Ambit synthesis(BuildGates)美国Cadence DesignSystems公司电路合成工具,行为级合成工具(VHDL编程)BooleDozer 美国IBM公司行为级合成工具(C语言编程)A|RT Designer 美国Frontier Design公司High Level电路合成工具eXplorations Tools 美国Explorations公司Design Planning 工具ChipBench 美国IBM公司TeraForm 美国Tera Systems公司System Level(系统级)设计工具Cierto product family 美国Cadence Design Systems公司Digital-数字回路设计工具eProduct Designer 美国Viewlogic Systems公司电路图Editor,逻辑Simulator(仿真工具)MyLogic Station 美国MyCAD公司VHDL模拟工具和VCS模拟工具VSS、VCS Synopsys公司电路综合工具Synthesis Synopsys公司模拟/数.模混合信号电路设计EDA工具模拟电路Simulator(仿真工具)T-Spice Pro美国Tanner Research公司SmartSpice美国Silvaco International公司Eldo 美国Mentor Graphics 公司混合信号・Simulator(仿真工具)ICAP/4 美国intusoft 公司混合信号・Simulator(仿真工具),RF电路Simulator (仿真工具),Analog Macro Library ADVance,CommLib美国Mentor Graphics 公司Static Noise 解析工具(混合信号)SeismIC 美国CadMOS Design Technology 公司Model Generator(模拟)NeoCell 美国Neolinear公司模拟电路设计工具MyAnalogStation美国MyCAD 公司电路仿真工具Star-HspiceStar-SimStar-TimeAvanti公司Hard/Soft协调设计EDA工具Hard/Soft协调设计工具Cierto VCC Environment 美国Cadence Design Systems 公司ArchGen 美国CAE Plus 公司eArchitect 美国Viewlogic Systems公司Hard/Soft协调验证工具SeamlessCVE 美国Mentor Graphics 公司LSI Layout设计EDA工具寄生电容/阻抗提取工具DISCOVERY 美国Silvaco International公司寄生电容/寄生阻抗提取工具,延迟计算工具SWIM/InterCal 美国Aspec Technology公司寄生电容/阻抗提取工具,回路Simulator(仿真工具),Layout 变换工具Spicelink,Ansoftlinks 美国Ansoft公司Model Generator CLASSIC-SC 美国Cadabra Design Automation公司Layout设计工具(带有电路合成功能)Blast Fusion 美国Magma Design Automation公司Layout设计工具DOLPHIN美国Monterey DesignSystems公司L-Edit Pro 美国Tanner Research公司MyChip Station 美国MyCAD公司CELEBRITY美国Silvaco International公司相位Shift Mask设计工具,OPC设计工具,Mask测试工具iN-Phase/TROPiC/CheckIt美国Numerical Tecnologies公司版图寄生参数提取工具Star-RC Avanti公司测试设计EDA工具Test - Pattern 变换工具TDS iBlidge/SimValidator 美国Fluence Technology 公司Test 设计工具TestBench 美国IBM 公司TDX 美国Fluence Technology 公司Test 解析工具(混合信号)Test Designer 美国intusoft 公司Designer/Ensemble Systems公司封装(Package)用温度解析工具Hybrid Thermal 美国Ansoft公司封装(Package)用寄生电容/寄生阻抗提取工具Turbo Package Analyzer 美国Ansoft公司其他的工具AC/DC设计・解析工具MotorExpert 韓国jasontech公司工艺・Simulator(仿真工具)ATHENA 美国Silvaco International 公司器件・Simulator(仿真工具)ATLAS 美国Silvaco International 公司器件模拟工具工艺模拟工具MediciDavinciTSUPREMAvanti公司。

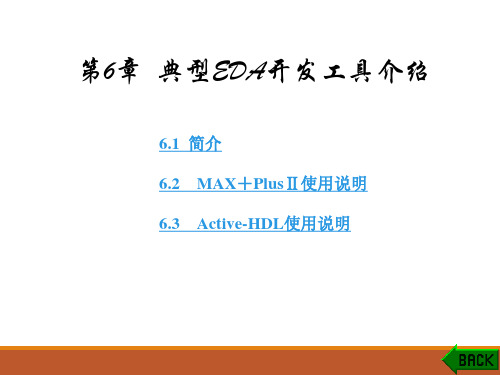

典型EDA开发工具介绍

MAX+plus Ⅱ的编译过程大致如下:

(1) 按前所述步骤,调出现行源程序的编辑窗,将源程序 调入并显示在编辑窗中。

(2) 选择File选项,光标移至子菜单的Project项停留几秒种, 屏幕上又会出现下一级菜单,如图6-11所示。

图6-11 工程文件设置菜单

(3) 选择图6-11所示下一级菜单的Name项,就会出现工程名 (Project name)对话框,输入程序名,如counter或用光标点击左 下角框内的现有工程文件counter,就可以确定当前的工程文件 名,然后点击OK按钮结束工程文件名设置。

(1) 输入工具。一般较常用的输入方式有文本输入、原理图 输入两种,它们在一般的开发软件和芯片制造商提供的集成开 发环境中都有,而有些软件还支持波形输入和状态图输入,有 的编辑器还带有语法模板,支持语法纠错。HDL Turbo Writer 是一款很好的VHDL/Verilog的编辑器,能转换大小写、缩进、 折叠,格式编排很方便。Visual VHDL/Verilog这款编辑器还支 持流程图输入,并能将流程图转换成VHDL/Verilog代码。

目前,在业界中受到好评的综合工具主要由以下几家公司所 开发:Synopsys公司、Mentor Graphics公司和Synplicity公司。 Synopsys公司出品的综合工具较多,如FPGA Express、FPGA Complier、Design Complier等,其综合优化能力也处于领先地位。 Synopsys公司支持的HDL语言子集比较完整,还提供一个设计元 件库,这个库包含许多元件的不同实现方案,可以让用户随意 调用。Mentor Graphics公司的Leonardo Spectrum也是一款非常优 秀的综合器,它不仅支持众多的FPGA/CPLD器件,也支持ASIC 的开发。其各项设置约束功能强大,具备RTL级和门级电路查看 功能并以彩色显示,具备智能分页显示功能,支持多种输出网 表格式,同时也能调用其他FPGA厂家的布线器。

EDA指导书1

一、数字系统设计的概念1、数字系统的电路层次门电路:CMOS门电路组合逻辑电路:以基本逻辑门组成的无反馈的单方向性电路。

对时间而言,只有延迟的概念,没有确定的时间逻辑。

时序逻辑电路:在电路中存在输出到输入的反馈。

具有逻辑时序的概念、即引入了时钟的概念。

时序电路分同步电路和异步电路两类。

同步电路系统以触发器为基本时序电路单元,利用统一的时钟对电路系统进行统一的控制。

异步电路利用专门的协调和仲裁电路进行统一管理。

我们目前使用的数字系统电路都是同步电路,其中也有一些异步的概念,如异步置位和异步复位等。

真正的异步电路系统是没有―时钟‖的。

数字系统电路:以触发器和功能组合电路组成单元电路——寄存器。

在逻辑关系上分成两部分,控制器和处理器。

在较大的系统中又分成―内核‖和―外壳‖。

2、数字系统设计的分类专用集成电路(ASIC :Application Specific Integrated Circuit)设计可编程电路(FPGA:Field Programable Generric Array、CPLD:Complex Programmable Logic Devise)设计电路板设计(PCB:Printed Circuit Board)3、数字电路系统的一般描述方式逻辑代数方法:用逻辑函数、状态方程表示电路。

是一种数学形式的描述,可以对简单的逻辑单元进行化简,具有数学的演绎功能。

在保持电路功能不变的情况下,可以演变出多种形式。

并与具体电路有一定的对应关系。

图表方法:用真值表、状态表、卡诺图、状态图、ASM图、框图等表示数字电路的逻辑功能。

与具体电路无直接对应关系。

图形符号方法:用电路器件符号组成的电路图。

波形时序图方法:用信号对时间的函数曲线表示电路功能,主要用表示电路信号间的时间关系。

上述各种方法与人们理解、设计数字电路的各种需要有关。

如果涉及制造电路,还需要更多的描述方法。

如电路网表、电路制版、布线等。

立创eda操作手册(3篇)

第1篇目录1. 简介2. 系统安装与启动3. 界面介绍4. 基本操作5. 元件库管理6. 布局与布线7. 印制电路板设计8. 生成报表9. 设计文件输出10. 常见问题解答11. 总结1. 简介立创EDA是一款功能强大的电子设计自动化(EDA)软件,适用于电路设计、原理图绘制、PCB设计等领域。

本手册旨在帮助用户快速上手立创EDA,掌握其基本操作和设计流程。

2. 系统安装与启动2.1 系统要求- 操作系统:Windows 7/8/10- 处理器:Intel Core i3 或 AMD Athlon II 或更高- 内存:4GB RAM 或更高- 硬盘空间:1GB 或更高- 显卡:DirectX 9 或更高版本2.2 安装步骤1. 下载立创EDA安装包。

2. 双击安装包,按照提示完成安装。

3. 安装完成后,双击桌面上的立创EDA快捷方式启动软件。

3. 界面介绍立创EDA界面主要由以下部分组成:- 菜单栏:提供各种操作命令。

- 工具栏:提供常用的快捷工具。

- 设计区域:显示电路原理图或PCB布局。

- 元件库:提供各种元件供设计使用。

- 属性栏:显示当前选中元件或图形的属性。

4. 基本操作4.1 新建项目1. 点击“文件”菜单,选择“新建”。

2. 在弹出的对话框中,选择项目类型(原理图或PCB)。

3. 输入项目名称和保存路径,点击“确定”。

4.2 打开项目1. 点击“文件”菜单,选择“打开”。

2. 在弹出的对话框中,选择要打开的项目文件。

3. 点击“打开”按钮。

4.3 保存项目1. 点击“文件”菜单,选择“保存”或“另存为”。

2. 在弹出的对话框中,选择保存路径和文件名。

3. 点击“保存”按钮。

5. 元件库管理5.1 添加元件库1. 点击“元件”菜单,选择“添加元件库”。

2. 在弹出的对话框中,选择要添加的元件库。

3. 点击“确定”。

5.2 搜索元件1. 在元件库中,输入要搜索的元件名称。

2. 按下回车键或点击搜索按钮,搜索结果将显示在元件列表中。

第4章 常用EDA工具软件的操作指南(20170801)

第4章 常用EDA工具软件的操作指南

4.1 常用EDA工具软件安装指南

1.硬件配置的选择 EDA软件随着功能越来越多,性能越来越好,相应地对计 算机的硬件配置越来越高,包括硬盘容量、内存容量、显示器、 通讯接口、操作系统等。如果安装软件的计算机硬件配置低于 软件安装于运行的最低要求,就会使系统无法完成安装或无法 正常运行。因此在安装计算机软件前,先要阅读有关说明,应 满足系统安装与运行的最低配置要求。 虽然现在计算机有包括USB接口在内的很多通讯接口方式, 但是很多EDA实验开发系统仍然需要计算机的并行打印机接口 进行编程下载,因此为了自己的使用方便,购买计算机时选择 含并行打印机接口的主板是必需的。

并将计数结果使用动态扫描的方式进行显示。

图4.6 0-9999计数动态显示电路原理图

第4章 常用EDA工具软件的操作指南

为了简化设计并便于显示,该计数动态扫描显示电路 分为两个层次,其中底层电路包括四个十进制计数器模块 CNT10、动态显示控制信号产生模块CTRLS、数据动态 显示控制模块DISPLAY等三个模块,再由这六个模块按 照图4.6所示的原理图构成顶层电路DTCNT9999。其中底 层的六个模块是用VHDL文本输入,顶层的电路系统则采 用原理图输入。DTCNT9999中的CLK1是计数时钟信号; CLK2是动态扫描控制时钟信号,要求在24Hz以上; CLR为清零信号;ENA为计数时钟信号;COM为数码管 公 共 端 控 制 信 号 ; SEG 为 数 码 管 的 显 示 驱 动 端 , 分 别 接 a~g。十进制计数器模块CNT10的VHDL程序见例题4.1, 其余两个模块的VHDL程序如下:

(S1, CLR, ENA, DOUT(11 DOWNTO 8), S2); U3:CNT10 PORT MAP

数字芯片EDA工具

数字芯片EDA工具1. 简介数字芯片EDA(Electronic Design Automation)工具是一类专门用于数字芯片设计的软件工具。

这些工具通过提供各种功能和功能模块,帮助工程师完成数字芯片的设计、验证和优化工作。

数字芯片EDA工具包括电路设计工具、仿真工具、布局与布线工具等。

2. 电路设计工具2.1 逻辑设计工具逻辑设计工具是数字芯片EDA工具中最基础的部分,其功能是帮助工程师进行数字电路的逻辑设计。

逻辑设计工具提供了一系列的逻辑门、触发器、计数器等基本逻辑元件,以及与、或、非等逻辑运算。

工程师可以使用这些元件和运算进行电路的逻辑设计,然后通过仿真工具进行验证。

2.2 时序设计工具时序设计工具是用于数字芯片的时序设计的工具。

时序设计工具可以根据工程师的输入,生成时序逻辑电路的表达式和状态转换图。

工程师可以根据实际需要,在时序设计工具上进行时序约束的设置,以达到设计的时序要求。

3. 仿真工具仿真工具是用于验证数字芯片设计的重要工具。

工程师可以通过仿真工具,在设计完成之前进行各种测试和验证。

仿真工具可以对设计进行功能仿真、时序仿真等。

通过仿真工具,工程师可以不断调整和优化设计,以满足设计要求。

仿真工具的核心是仿真器。

仿真器可以对设计进行仿真运行,并显示设计的状态和结果。

仿真器可以模拟特定的输入条件,以验证设计在不同输入条件下的行为。

另外,仿真工具还可以提供波形显示,方便工程师观察和分析输出波形。

4. 布局与布线工具布局与布线工具是数字芯片EDA工具中的另一个关键模块。

布局与布线工具将电路设计映射到芯片的物理布局上,通过优化布局和布线,提高芯片的性能和可靠性。

布局工具可以根据设计要求,对芯片进行区域划分、资源分配等操作,生成一个满足约束条件的初始布局。

布线工具则根据布局结果,进行线路的布线规划和优化。

通过布局与布线工具,工程师可以控制电路的物理排列和布线路径,提高芯片的时序性能和功耗。

5. 其他工具除了上述主要功能模块外,数字芯片EDA工具还包括其他辅助工具。

111《EDA工具手册》约束管理器分册2

第1章在原理图和PCB之间同步约束本章学习如何同步从原理图中获取的约束或者从PCB中获取的约束。

主要内容如下:∙传送电子约束从原理图到PCB∙传送电子约束从PCB到原理图∙在原理图中重写电子约束加到板上,或者反过来∙仅传送变更的电子约束从原理图到PCB或者反过来1.1 从原理图中输出约束一旦完成原理图设计并加了所有的约束,可以传送逻辑到PCB Design板,当创建了PCB 板,电子约束也可以传递给PCB。

下面就打包一个设计并创建一个PCB文件,此板文件将包含在原理图中添加的所有的约束。

从原理图中输出约束1.点击Concept HDL窗口,选择【File】/【Export Physical】,出现【Export Physical】对话框。

1.确认选择了【Package Design】选项,注意如果原理图中加了新的约束,一定要打包设计,以便约束传递到相关的板。

2.选择【Update Allegro Board (Netrev)】选项。

3.在【Output Board File】栏输入“my_board”。

4.点击按钮。

5.点击按钮,不查看报告。

1.2 在PCB Design中查看和添加约束约束管理器是与Concept HDL和PCB Design集成在一起的。

PCB工程师可以在PCB Design中启动约束管理器来查看原理图中获取的约束,除了查看,还可以进行以下工作:∙在PCB中获取相关的布局和走线的约束∙万一发现约束与板上的走线情况不一致时,更新原理图中获取的约束∙分析不同约束的值∙输出分析结果,原理图设计者可以在约束管理器中查看有没有冲突下面将在PCB Design中启动约束管理器,查看网络RESETL的约束,编辑此网络的Min First Switch约束,并增加Max Xtalk约束在网络上,并将分析这个约束和输出结果。

在PCB Design中查看和添加约束1.点击【Project Manager】界面,点击Layout图标,进入PCB Design界面。

常见EDA软件的license管理

常见EDA软件的license管理大型工程软件如Ansys、Fluent、Unigraph、ProE等安装需要经过注册程序Flexlm才可以使用,而Flexlm中涉及到很多知识、技巧,也存在许多问题。

本篇文章就是针对上述软件安装中的常见问题作一些探讨与解决。

莱曼特的LMT LicManager可对EDA软件的许可证进行集中监控管理。

Lanmantech公司研发的licManager产品充分研究识别Flexlm及其他主流授权机制并利用LMT核心计算模式在不影响软件许可证本身授权机制的基础上对许可证进行闲置识别、资源调度从而提高许可证的使用率。

它的解决方案已被多家世界500强企业所采用。

并且可以为企业节省30%左右的许可证费用。

当前,在产品设计过程中,需要用到很机械(MDA)和电子(EDA)设计和分析相关的大型应用软件,如Pro/E、nastran、pantran、cadence、synopsys、ansys、fluent、unigraph等。

而这些大型工程软件需要安装许可证才能使用,为了满足不断增长的设计需求,软件许可证的数量也要不断的增多。

对于目前的应用软件,一些大型企业现有的许可证管理模式和使用模式与行政管理体系想对应,即大部分已经存在于各个下级公司,由各个下级子公司分别对本公司的许可证进行管理和使用,部分子公司已经开始在本部门内进行软件的网络浮动使用,但在公司之间软件部能充分共享。

同时也造成部分公司内软件使用效率偏低,同时其他子公司需求迫切却又无软件可以,还需要重复购置的现象。

有些企业通过统一采购、免费升级的方式可以获得位于各个子公司的软件许可证的共享使用方式;同时全新采购的此类软件将不再下发到各个子公司,而采用许可证服务器集中存放、统一管理、网络浮动的方式共享给下属各个公司使用。

通过以上现状可以发现,目前这些大型企业的许可证分布现状是一种既集中又分布的混合结构。

对于这种混合结构,如何更好的管理这些许可证,更高效、更合理的使用这些许可证,是很多企业单位的信息管理部门所面临的一项迫切的任务。

eDAQ中文简明操作手册2013v2.0

ECOM EHLS

ECOM EHLS-B EHLS-AO

EBRG

EBRG-350-B EBRG-350-AO EBRG-120-B EBRG-120-AO

EDIO

EDIO-B EDIO-5HZGPS

ENTB EITB

ENTB EITB-K EITB-J EITB-T EITB-E

ELLB EHLB

N/A N/A

图 1-4 TCE 软件界面示意 TCE 软件有如下功能: 建立设置文件定义和标定传感通道; 软件内置 ISO 文件测试程序; 定义数据类型和计算通道以便进行在线数据计算和分析; 测试数据的采集确定触发条件,可实现手动触发或程序触发等; 采用 TCE 时间运行显示监测测试数据; 监测测试和存储状态;初始化、启动、重启和结束测试等。

eDAQ 中文操作手册

1

目录

第一章 eDAQ 系统概述 ............................................................................................................. 3 1.1 系统组成 ....................................................................................................................... 3 1.2 系统供电 ....................................................................................................................... 4 1.3 系统通讯 ....................................................................................................................... 5 1.4 TCE 试验设置和控制软件 ............................................................................................. 6 第二章 eDAQ 系统操作流程☆ ................................................................................................... 8 2.1 系统准备 ...................................................................................................................... 8 2.2 软件参数设置及数据采集 ............................................................................................. 9 2.3 计算通道 ..................................................................................................................... 22 第三章 常用传感器测试方法 .................................................................................................... 29 3.1 应变片测量示例 ......................................................................................................... 29 3.2 热电偶测量示例 ......................................................................................................... 30 3.3 位移传感器测量示例 .................................................................................................. 32 3.4 压电式传感器测量示例 ............................................................................................... 34 3.5 CAN 总线测量示例 ..................................................................................................... 36 3.6 视频系统 .................................................................................................................... 39 3.7 GPS 使用 .................................................................................................................... 43 3.8 多台采集器组网采集 .................................................................................................. 44 第四章 eDAQ 系统操作注意事项 ............................................................................................ 46 4.1 一般安全守则 ............................................................................................................. 46 4.2 LED 状态信息 ............................................................................................................. 46 4.3 故障诊断 .................................................................................................................... 48 4.4 软件系统升级与板层扩展 ........................................................................................... 48

quartus的约束手册(3篇)

第1篇目录1. 引言2. 约束概述3. 约束类型1. 位置约束2. 时序约束3. 电源和接地约束4. 电压约束5. 信号完整性约束4. 约束设置5. 约束验证6. 常见问题解答7. 总结1. 引言Quartus II 是一款由 Altera 公司开发的现场可编程门阵列(FPGA)设计软件。

在进行 FPGA 设计时,约束是确保设计正确性和性能的关键因素。

本手册旨在提供关于 Quartus II 约束的全面指南,帮助用户了解如何设置和使用约束,以提高设计效率和性能。

2. 约束概述约束是描述设计要求的一系列指令,用于指导 Quartus II 综合器、布局布线器和其他工具生成正确且性能优化的硬件设计。

约束可以基于设计规格、硬件资源限制或性能要求。

3. 约束类型3.1 位置约束位置约束指定了设计中的特定信号或模块应该放置在 FPGA 的哪个位置。

这有助于优化设计性能和资源利用率。

- 固定位置约束:指定一个具体的 FPGA 坐标,将信号或模块放置在该位置。

- 区域约束:指定一个 FPGA 区域,将信号或模块放置在该区域内。

3.2 时序约束时序约束定义了设计中的关键路径延迟要求,包括时钟频率、时钟边沿、数据到达时间和数据保持时间等。

- 时钟约束:指定时钟信号的频率、相位和复位特性。

- 数据路径约束:指定数据路径的延迟要求,包括时钟到数据的传播延迟。

3.3 电源和接地约束电源和接地约束确保设计中的电源和接地网络满足性能要求。

- 电源网络约束:指定电源网络的关键特性,如电压、电流和电源完整性。

- 接地网络约束:指定接地网络的关键特性,如接地电阻和接地完整性。

3.4 电压约束电压约束确保设计中的电压满足设计规格要求。

- 电源电压约束:指定电源电压的范围。

- 电压完整性约束:指定电压波动范围。

3.5 信号完整性约束信号完整性约束确保设计中的信号满足性能要求。

- 信号完整性分析:分析信号在传输过程中的衰减、反射和串扰。

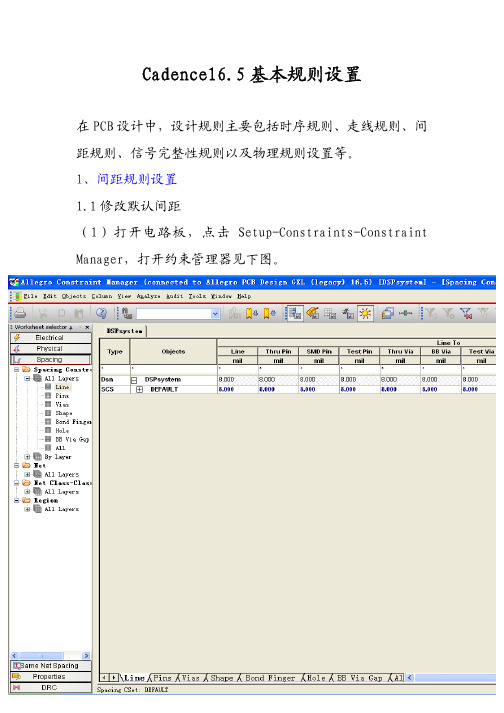

Cadence16.5 基本规则设置

Active window 表示网络正处于转换或者产生噪声的窗口 Senstive window 表示网络处于稳定和易受干扰的状态窗口 Ignore nets 表示计算串扰时可以忽略的网络 Xtalk 表示 max 列填写受扰网络上最大允许的串扰 Peak xtalk 表示 max 列填写一个干扰网络对受干扰网络上产 生的最大可以允许的串扰 (5)、Simulated Xtalk 选项

Topology:如果 verify schedule 选项设置为 yes 则进行 DRC 检查,最大同时转换噪声,单位为 MV,格式为高或者低,单 击 schedule 栏中所对应的表格,在下拉列表中可以选择预 置的几个拓扑结构,包括菊花链(daisy-chaim)、星形(star) 等拓扑结构 Stub length 设置菊花链走线时的最大短桩长度 Parallel 设置并行走线线段的线宽和线间距约束 (2)、Impedance 选项 在 Impedance 工作表内进行目标阻抗和偏差的设置,通过计

Overshoot:在 max 列中输入过冲约束,在 high actual 选项 中出现的为网络的实际高低电压,在 margain 选项中显示的 为最差情况的实际值和 max 的差值 (3)、Edge Distortions 选项

Edge secsitivity:标记网络或者扩展接收端是否对单调性 敏感 First incident switch:标记第一个波形到来时,是否需 要转换 (4)、Estimated Xtalk 选项

2.2 设置物理规则 假设网络 VCC1V2 和 VCC3V3 需要比前面设置的线宽更大。 单击 Edit-Properties 进入属性编辑命令,在 Find 栏选择 Find By Name 见右图所示 单击 More

Cadence约束管理器的基本介绍

Cadenc e原理图约束管理器的基本使用1.1 约束管理器简介约束管理器是一个交叉的平台,以工作薄(workbo ok)和工作表(worksheet)的形式通过用户定义约束管理来管理设计中的各个网络和管脚对。

例如控制某条网络的阻抗值和布线长度等等。

约束管理器具有以下功能:1)它以数据表格的形式与用户接口,使用户能够快速的获取,修改和删除用户定义的约束值。

2)它能够所有的定义的约束进行语法检查。

3)它提供约束的继承,在高等级对象中定义的约束能够被低等级对象所集成。

而且低等级对象可以重新定义约束覆盖从高等级对象继承下来的所有约束。

能够产生原理图和pcb板关于约束捕捉的报告。

2.1 原理图和pcb板间约束捕捉的同步原理图和pcb的约束同步是指在原理图或pcb中定义或修改的约束在原理图和p cb之间可以相互传递的(原理图到pc b或pcb到原理图)。

如下图1所示:图1 原理图与pc b板约束的同步3.1 带约束管理的设计流程带约束管理的设计流程与传统的设计流程相比,其主要包含了约束文件,该约束文件以设计板的名字命名,文件扩展名为.dcf,该文件放在设计板目录下的cons train ts目录下。

例如在E:\KS8695P_DEM O_V100.1目录下创建了KS8695P_D EMO_V100.1工程,设计板的名称为NETCAMERA,那么在E:\KS8695P_DEM O_V100.1\WORKLIB\NETCAMERA\CONSTR AINTS目下会产生n etcamera.dcf约束文件。

带约束管理的设计流程如下图2所示:图2 约束使能的设计流程3.1.1 从原理图导出约束管理到pcb在使能约束管理器的设计流程中,canden ce会产生5个必须发送pcb板上的文件:p stchi p.dat,pstrxp rt.datt,pstxne t.dat,pstcmd b.dat,pstcmb c.dat,其中前3个在传统的设计中也会产生,后2个是在使能约束管理器后产生的文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录第一章约束管理器介绍 (4)1.1约束管理器简介 (4)1.2约束管理器界面简介 (8)1.2.1worksheet selector (8)1.2.2用户接口 (9)1.2.3View选项 (9)1.3启动约束管理器 (11)第2章OBJECTS介绍 (12)2.1P IN-P AIRS (13)2.1.1Pin-Pair规则 (14)2.2N ETS和X NETS (14)2.3B USES (15)2.4M ATCH G ROUPS (15)2.4.1如何确定target pin pair (16)2.4.2相对/匹配的群组规则 (16)2.5D IFF P AIRS (16)2.5.1差分对工作表 (17)2.5.2差分计算器(Differential Calculator)的使用方法 (19)2.5.3差分对规则 (19)2.6D ESIGNS AND S YSTEMS (20)第3章设置网络的走线约束 (21)3.1.1设置网络的最大最小传输延迟 (21)3.1.2设置网络相对传输延迟 (24)3.1.3设置差分对约束 (26)3.1.4查看网络规范格式和物理格式 (28)第4章设置网络的时序和信号完整性约束 (30)4.1设置时序约束 (30)4.2设置信号完整性约束 (32)4.2.1设置电气属性约束 (32)4.2.2设置反射属性约束 (33)第5章电子约束创建和应用 (35)5.1创建ECS ET (35)5.2指定ECS ET给网络 (40)5.3不考虑ECS ET的缺省约束值 (41)5.4在原理图中查看ECS ET (41)第6章ECOS实现 (43)6.1在原理图中增加网络 (43)6.2在原理图中修改约束 (45)6.3在约束管理器中修改约束 (46)6.4在约束管理器中删除约束 (46)6.5在原理图中重新命名网络 (47)第7章在原理图和PCB之间同步约束 (50)7.1从原理图中输出约束 (50)7.2在PCB D ESIGN中查看和添加约束 (50)7.3在原理图中导入并查看约束 (51)7.4在PCB和原理图之间同步约束的两种模式 (52)7.4.1用原理图中的约束重写PCB中的约束 (53)7.4.2在原理图中导入PCB中变更的约束 (56)第8章约束分析 (58)8.1查看工作表单元格和对象 (58)8.2定制约束、定制测量和定制激励 (59)8.2.1定制约束 (59)8.2.1.1 用户定义的属性 (59)8.2.1.2 约束的定制测量 (59)第9章SCHEDULING NETS (61)9.1S CHEDULING N ETS (61)9.2S CHEDULING N ETS-R EVISITED (65)第10章相对传输延迟 (68)第11章MATCH DELAY (73)第12章解决DRC冲突 (74)第13章约束管理器 (76)13.1层次设计中的电子约束 (76)第一章约束管理器介绍约束管理器是一个交叉的平台,以工作簿和工作表的形式在Cadence PCB设计流程中用于管理所有工具的高速电子约束。

约束管理器让你定义、查看和校验从原理图到分析到PCB设计实现的设计流程中每一步的约束。

可以使用约束管理器和SigXplorer Expert开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。

本培训教材描述的主要是怎样在约束管理器中提取约束,并且约束如何与原理图和PCB的属性同步。

本教材的内容是约束管理器、Concept HDL和PCB Design的紧密集成的集锦。

所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。

电子约束(ECSets)就是限制PCB上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。

教材主要内容如下:•第1章~第7章主要关于原理图约束管理器使用:•在约束管理器中提取ECs(电子约束);•在原理图和约束管理器中执行ECO;•在Concept和PCB Design中传递ECs。

这部分面向Concept HDL的约束管理器的初学者,但是要熟悉Concept HDL和PCB Design。

此教材不讨论Concept HDL和PCB Design不同模式和属性的细节,但是会详细地讨论约束管理器过程。

为了快速理解约束管理器的主要特点,可以看看Concept HDL的多媒体教材。

请见Help –Learning Concept HDL–Demos in Concept HDL。

将练习文件project.zip解压缩到一个空的路径\design。

确认设置环境变量CONCEPT_INST_DIR到Cadence安装路径(一般安装时设置好了)。

•第8章~第12章主要关于PCB约束管理器使用,但是省略了与原理图相同的部分。

•本培训教材附两个练习文件:project.zip和golderboard.rar。

1.1 约束管理器简介约束即用户定义的附加到网络或者管脚对上的要求,电子约束管理着网络和管脚对的行为。

可以使用约束管理器来提取和管理电子约束。

Cadence推荐使用约束管理器来提取约束,因为约束管理器有下列特性:•提供工作表为基础的用户接口,允许快速的提取、修改、删除约束。

•支持语法检查•支持约束继承,高层的约束可以被继承,低层的约束可以覆盖高层约束。

•可以定义电子约束集。

•创建约束报告。

约束管理器在流程中的位置和作用请见下图:加入约束管理器的设计流程请见下图:在下图中约束管理器保存电子约束信息在根设计一个新的目录下,约束视图包含*.dcf 文件,里面包含设计的电子约束信息。

在此流程中,在打包时Packager-XL创建5个pst*.dat文件,包含传统设计流程中的3个文件(pstchip.dat, pstxprt.dat, pstxnet.dat),还有两个文件pstcmdb.dat, pstcmbc.dat。

pstcmdb.dat包含当前设计中的电子约束,是constraints 视图中的*.dcf文件的拷贝。

pstcmbc.dat包含的是板中的约束,在执行import physical时产生的。

如果没有*.dcf存在,Packager-XL就允许在传统的流程。

约束管理器是以表格为基础的应用,很容易使用,并且允许创建通用的约束并将其同时应用到很多网络上,如果需求发生改变,可以编辑通用的约束并自动更新用到此约束的网络。

请见图1-1约束管理器界面。

图1-1 约束管理器用户界面在约束管理器,你可以工作在对象(objects)(比如网络、管脚对)和ECSets (Electrical constraint sets电子约束集)。

你可以以电子约束的形式定义一个或者多个约束以满足设计需求,然后指定合适的约束给设计中对象,如果需求变更可以交换ECSets或者重新定义当前的指定。

一个ECSets可以被很多对象应用,对象和ECSets对于整个设计可以是通用的,或者仅设计中的指定网络应用。

约束管理器的特点请见表1-1:表1-1 约束管理器的特点注1: 拓扑模板的存在比约束管理器早,拓扑模板与约束管理器的集成提供一个优选的创建和编辑ECSets 的环境。

拓扑模板除了提供图形环境来访问指定的管脚对和定义网络节点排序(scheduling)也可以使用电子约束。

拓扑模板和ECSets可能会交换使用,但是应该注意此功能是可选的。

在约束管理器中可以管理所有的ECSets,并且ECSets可能仅包含规则而没有相关的拓扑。

1.2 约束管理器界面简介请见图1-1,约束管理器包含以下几个部分:•menu和icon命令选择•worksheet selector用于选择合适的工作表•worksheets用于提取、编辑和校验约束•status bar反馈对象选择和约束进程注意当在约束管理器中选择一个目标时,按右键可以弹出一个上下文敏感的菜单,选择命令执行。

1.2.1 worksheet selector使用worksheet selector启动想要编辑的合适的工作表。

在约束管理器中通过worksheet selector通过Object type管理约束和属性。

Object type就是最上层的文件夹Electrical Constraint Set和Net。

请见图1-2。

图1-2 Object type 和Workbooks在Electrical Constraint Set文件夹中定义通用的规则,创建通用的对象分组(比如相对或者匹配群组和pin-pair),然后再将这些约束ECSets指定给相应的对象。

在Net文件夹可以创建针对指定网络对象分组(symtem,design,bus,diff-pair,Xnet,net,relative or match group,and pin-pair)。

也可以创建基于网络相关属性的ECSet。

这个ECSet将放在Electrical Constraint Set文件夹中。

当扩展Electrical Constraint Set或者Net文件夹时,工作簿通过设计规则组织这些对象,比如Signal Integrity, Timing, Routing, and Custom Measurements,此外在Electrical Constraint Set文件夹还有一个All Constraints工作簿,包含所有工作表中的约束。

在All Constraints的下面有一个User-defined文件夹包含SigXplorer定义的独特的约束。

一般,你定义一个约束在某个指定的工作表中,那么只能设置这个工作表相关的约束,不能设置其他工作表中包含的约束,你可以在All Constraints工作簿中定义这个约束的其他设置,而不用另外再建一个约束。

在All Constraints工作簿也可以用于不同工作表中约束的比较。

1.2.2 用户接口Cadence约束管理器的基本操作与Windows基本操作基本相同。

下面仅将快捷键介绍一下。

提供的快捷键如下:表1-2 快捷键快捷键功能F3 Find NextF9 AnalyzeCntrl+F9 Analysis ModesShift+F9 Analysis SettingsCntrl+F6 View Options1.2.3 View选项约束管理器提供很多选项以定义自己的用户界面。

设置View选项1.在启动约束管理器之前,首先打开项目文件project.cpm,然后打开原理图。

2.在Concept HDL界面,选择【Tools】/【Constraints】/【Edit】。

弹出约束管理器对话框,提醒使用约束管理器要考虑兼容性。