基于Xilinx FPGA的SPI Flash控制器设计与验证

基于FPGA片内Flash实现数据的动态加载和读取

基于FPGA片内Flash实现数据的动态加载和读取周刚; 曹健辉; 彭勃【期刊名称】《《通信技术》》【年(卷),期】2019(052)003【总页数】8页(P750-757)【关键词】FPGA; Spartan-3AN; 片内Flash; SPI接口; 加载和读取【作者】周刚; 曹健辉; 彭勃【作者单位】中国电子科技集团公司第三十研究所四川成都 610041【正文语种】中文【中图分类】TN919.30 引言本项目中涉及到4个通道的射频发射电路,频段覆盖225~400 MHz,射频输出幅度会随着频率的变化而变化。

由于DA输出属于模拟电路,加之元器件的个体差异,常会导致相同电路、不同频率射频输出幅度不一致。

每个通道的输出功率均有平坦度要求,因此每台设备的4个通道均需根据实际输出功率调整射频输出的衰减量,确定4个通道的衰减量后,编译生成本台设备的下载文件。

根据经验,一般1 MHz频率内对应一个校正值。

例如,175 MHz范围只需175个矫正值即可。

此种方式导致每台设备的调试测试均需要重新编译FPGA工程文件,工作量大且不利于FPGA程序的归档和使用。

考虑两种改进方案。

方案一为传统的FPGA+SPI Flash或者FPGA+CPLD+Flash设计方案。

由于硬件已经开发完成,此方案的缺点在于需要修改硬件电路,增加单独的Flash芯片或者CPLD芯片,因此实现难度较大,不建议采用。

方案二为直接利用Xilinx公司Spartan-3AN系列FPGA内含Flash进行设计改进。

此FPGA内含16 MB内存的Flash,在PC中开发参数配置软件,通过串口下载配置文件至FPGA中的片内Flash。

因为FPGA自带串行外围设备接口(Serial Peripheral Interface,SPI),FPGA每次开机后自动读取片内Flash的配置文件,也可以根据需要从FPGA的片内Flash中读取配置文件。

1 Spartan-3AN1.1 Spartan-3AN主要特点Spartan-3AN FPGA平台是Xilinx公司于2007年推出的非易失性FPGA解决方案,基于成熟的90 nm工艺的低成本FPGA构架,融合了SRAM技术和可靠的非易失性闪存技术。

基于FPGA的电机控制器设计与优化

基于FPGA的电机控制器设计与优化电机控制是现代工业中非常重要的一项技术。

随着科技的不断进步,基于FPGA(现场可编程门阵列)的电机控制器越来越受到关注和应用。

本文将介绍基于FPGA的电机控制器的设计与优化方法。

首先,我们需要了解什么是FPGA。

FPGA是一种可编程逻辑器件,可以根据特定的需求而重新配置其内部电路。

相比于传统的ASIC(专用集成电路)设计,FPGA具有灵活性更高、设计周期更短等优势。

因此,基于FPGA的电机控制器可以实现更高效、更智能的控制方案。

在设计基于FPGA的电机控制器时,首先需要明确控制目标。

不同类型的电机有不同的控制要求,例如直流电机、交流电机等。

接下来,我们需要选择合适的FPGA芯片。

常见的FPGA芯片供应商有Altera、Xilinx等,根据实际需求选择适合的芯片型号。

在电机控制器设计的过程中,我们需要采用一种合适的控制算法。

常见的控制算法包括PID控制算法、模型预测控制算法等。

根据电机的特性和性能要求选择合适的控制算法,并在FPGA芯片上实现该算法。

在FPGA上实现电机控制算法可以通过硬件描述语言(如VHDL、Verilog)来进行。

在编写硬件描述语言的代码之前,我们需要先进行电路结构的设计。

根据控制算法的需求,设计电路结构,包括逻辑门、寄存器、计数器等。

设计完电路结构后,我们可以编写对应的硬件描述语言代码。

根据电路结构设计的结果,编写代码描述电路的逻辑功能。

代码编写完成后,可以进行仿真验证,确保代码的正确性。

在代码编写完成后,需要进行综合和布局布线。

综合是将硬件描述语言代码转化为逻辑门级的电路网表,布局布线是将电路网表映射到FPGA芯片的物理结构上。

这两个步骤是将代码转化为实际可用的电路的关键步骤。

设计完成后,我们需要进行电机控制器的优化。

优化可以从多个方面进行,例如功耗优化、面积优化、性能优化等。

通过优化,可以提高电机控制器的效率和可靠性。

优化的方法包括逻辑优化、时序优化、资源共享等。

FPGA_ASIC-基于FPGA的SPI4.2接口设计

基于FPGA的SPI4.2接口设计孙世国陈帅陈倩张恒威北京航天飞行控制中心 100094摘要:本文介绍了一种FPGA和IPX2805之间的SPI4.2接口模块设计的方法,对硬件设计进行了说明,着重阐述了FPGA内部SPI4.2接口模块设计。

该设计简单、高效,解决了商用芯片不能满足高速转发的系统要求的问题。

方案在Altera的Stratix II器件上得到了验证。

关键词:FPGA,IPX2805,SPI4.2The SPI4.2 Interface Module Design Based on FPGASUN SHIGUO CHEN SHUAI CHEN QIAN ZHANG HENGWEIBeijing Aerospace Control Center 100094Abstract:To design SPI4.2 interface module, a method based on FPGA and IPX2805 interface chip is described in this paper, including circuit design diagram . The design is simple and high efficiency.It satisfies the system require of high-speed transmit that is can not satisfied by business chip. The objective is achieved in the Stratix II of Altera.Key words:FPGA,IPX2805,SPI4.21.引言SPI-4.2(System Packet Interface)是OIF(Optical Internetworking Forum)定义的局部高速总线标准,用于PHY层芯片到链路层芯片的10Gbps信号传输。

基于FPGA的SPI Flash配置存储器复用的实现

基于FPGA的SPI Flash配置存储器复用的实现陈燕文;韩焱;徐磊;莫璧铭【摘要】FPGA是一种基于SRAM技术制造的可编程器件,内部数据具有掉电即失的特点.因此,配置电路是FPGA系统中必不可少的部分.本文提出一种复用FPGA配置存储器的方法:配置存储器既能满足FP-GA系统的配置需要,又可以作为通用存储器满足用户存储数据的需求,提高了配置存储器的利用率,使得采集存储系统小型化、集成化成为可能.制定了SPI Flash复用的方案,分析了复用配置存储器的可行性.并且编写基于FPGA的SPI接口控制程序,实现对配置存储器的擦除、读写等操作.利用Modelsim,Chips-cope等调试工具验证了控制程序的可靠性.%FPGA is a programmable device based on SRAM technology,and the internal data in FPGA will be lost when the power fails.Therefore,the configuration circuit is an essential part of the FPGA system.This paper puts forward a method of multiplexing FPGA configuration memory:memory allo-cation can not only meet the needs of FPGA system configuration,but also be used as a universal memo-ry data storage to meet needs of user.This method improves the utilization rate of the memory alloca-tion,and makes it possible to make the acquisition storage system miniaturization and integration.First-ly,the scheme of SPI Flash reuse is worked out,and the feasibility of reusing configuration memory is analyzed.And the SPI interface control program based on FPGA is written to realize the erasure,read-ing and writing of configuration memory.The reliability of the control program is verified by using Mod-elsim,Chipscope and other debugging tools.【期刊名称】《测试技术学报》【年(卷),期】2017(031)006【总页数】7页(P491-497)【关键词】FPGA;配置存储器复用;SPI接口控制;Chipscope【作者】陈燕文;韩焱;徐磊;莫璧铭【作者单位】中北大学信息探测与处理技术山西省重点实验室,山西太原 030051;中北大学信息探测与处理技术山西省重点实验室,山西太原 030051;中北大学信息探测与处理技术山西省重点实验室,山西太原 030051;中北大学信息探测与处理技术山西省重点实验室,山西太原 030051【正文语种】中文【中图分类】TN98FPGA(现场可编程门阵列)是在PAL, GAL, CPLD等可编程器件的基础上进一步发展的产物[1]. 目前主流的FPGA制造工艺均是基于SRAM技术,这种技术使得FPGA能够实现较高的工作频率,但是也决定了FPGA中数据掉电即失的特点[2-3]. 因此,配置电路是FPGA系统中必不可少的一部分. 随着存储技术的快速发展,存储颗粒密度越来越高,储存器向大容量、小体积方向发展[4-7]. FPGA的配置存储器往往在满足存储自身配置程序的同时,仍富余较大的存储空间. 本文提出一种复用FPGA配置存储器的方案,提高了存储器的利用率.本系统采用Xilinx公司的Spartan6-LX16作为主控芯片、华邦公司的W25Q128BV作为数据存储和配置芯片、 MAX1308作为数据转换模块,设计构建了存储采集系统. 制定了SPI Flash配置芯片的复用方案,编写了存储器控制程序,并且对程序功能和复用方案进行了验证,最终实现了对配置芯片的复用.系统组成如图 1 所示,本系统中使用的MAX1308模数转换芯片拥有8个采样通道、最高采样率为1 MPS. MAX1308为并行数据传输,采集一次产生的12 bit数据被同时输出至数据端口. FIFO1与FIFO2是位宽为8、深度为1 024的数据缓冲器. 在采集完成之后,数据的低8 b被写入数据FIFO1,通道标识号(4 bit)和数据的高4 b被写入数据FIFO2. 在SPI读写控制器的协调下,数据被有序地从FIFO中读出并写入SPI FLASH. 系统中的SPI FLASH为复用存储器,既能满足FPGA系统的配置需要,又可以作为通用存储器满足用户存储数据的需求.按照主从关系划分, FPGA中常用的配置方式有主动配置、被动配置和JTAG配置[8],按照数据总线的位宽又可分为串行配置和并行配置[9-10]. 本文中使用SPI Flash作为程序存储器的配置方案是主动串行配置方式的一种. Xilinx公司Spartan6系列芯片程序加载过程如图 2 所示.Spartan 6系列FPGA程序加载方式可以通过模式控制引脚M[1∶0]进行选择. 在采用SPI主动串行配置方式时,M[1∶0]应被设置为10. 在FPGA系统上电之后,外部向FPGA的PROGRAM_B引脚送入一个宽度不小于500ns的低脉冲,清除配置空间,重启配置过程[11]. 接下来初始化标志位INT_B拉低并对模式控制引脚进行采样,当初始化完成之后INT_B拉高. 随后FPGA通过CCLK引脚将时钟送入存储控制器,并且向FLASH发送读命令及数据起始地址[12]. 在接受到读命令和地址信息之后, FLASH将配置信息有序地放入DOUT引脚供FPGA读取[13].在完成配置程序的加载之后, CCLK, DIN, DOUT, CSO等引脚恢复成为普通的用户引脚,这使得在不改变硬件连接的前提下,利用配置FLASH余下的存储空间成为可能.对于确定型号的FPGA来讲,配置文件所需要的储存空间是一定的. 厂家会在芯片手册中对配置文件的大小进行说明. 以Spartan 6 系列中LX16型芯片为例,配置的bit文件的大小为3 731 264 bit,约为456 KB. 为了满足第三方存储器对数据格式的要求,开发工具还需要将bit文件转换为MCS文件. 在转换过程中,加入了校验及地址信息,因此转换之后文件所占的空间变大,转换之后的文件大小为2 MB. 本课题中用到的W25Q128BV配置存储器容量为16 MB,按照配置程序在存储器中的存放规则,将前2 MB的空间作为程序的配置空间,后14 MB作为用户的通用存储空间. 配置空间与通用存储空间对应地址关系如图 3 所示.设计中使用的W25Q128BV型SPI FLASH存储空间为128 Mbit, 由65 536页组成. 页是该Flash最基本的组成单元,一页的容量为256 Byte. 16页组成一个扇区sector(4 KB), 8个扇区组成一块block(32 KB). 该芯片具有先进的写保护机制,并且具有整体擦除和扇区擦除、灵活的页编程指令和写保护功能.本节重点介绍页编程操作、数据读取操作、扇区擦除操作的过程. 本设计中供用户存放数据的地址区间为200 000H-FFFFFFH,因此存储器的读写及擦除操作均是以200 000h为起始地址.在片选信号CS拉低之后,外部向FLASH写入页编程令码02H,随后写入所要目标区域的地址. 地址的一般格式为一个标准的页地址,即数据位的低8 b全为‘0’. 当写入地址的低8 b不为‘0’时,若数据写入时钟周期数多于剩余的字节位数,则在完成从当前位置写到结束位置之后重新回到开始位置进行数据写入,若数据写入时钟周期数小于或者等于剩余的字节位数,则在时钟结束之后就停止数据的写入.在写入地址之后,向FLASH发送256B的数据. 在数据编程期间BUSY信号为1. 在FLASH完成数据编程后,状态寄存器WEL位转换为‘0’. 若要进行下一页数据的编程,需要在BUSY信号拉低之后向FLASH写入写使能命令将WEL位置至1. 图5是读操作程序的仿真图形. 对比图 4 与图 5 可以发现,二者时序操作一致. 该FLASH支持数据单字节读出和多字节读出. 在片选信号CS拉低之后,向FLASH写入数据读取命令码03H,然后写入所要读取区域的地址. 在地址写入之后, FLASH在下一个时钟下降沿时将目标地址的数据加载到数据输出端口. 若片选信号和时钟信号一直有效, FLASH的地址会自动递加并且将数据加载到数据输出总线,直到将FLASH中所有数据读出. 设计中使用此种模式对SPI FLASH进行读操作. 图 7 是Verilog程序仿真图.擦除操作可以将存储器中的存储字节由‘0’置为‘1’,而写数操作只能将‘1’置为‘0’. 因此,擦除操作是数据写入FLASH之前必须要进行的步骤.W25Q128BV型FLASH支持3种擦除方式:扇区擦除、块擦除和双块擦除. 本设计中使用扇区擦除方式对FLASH进行格式化.由图 8 可以看出,在片选信号有效之后向FLASH中写入擦除命令码20 H. 随后写入所要擦除区域的地址即可. 数据擦除期间BUSY为1. 在擦除命令执行之后,状态寄存器WEL位转换为‘0’. 若要进行下一地址的擦除,需要在BUSY信号拉低之后向FLASH写入写使能命令将状态寄存器的WEL标志位至1. 图 9 是程序仿真图.该型FLASH支持3种SPI模式,本设计中使用标准SPI模式. SPI的时钟为25 MHz,使用的是模式3,即在不工作时时钟线是低电平,在时钟下降沿时将数据锁存进设备. 为了便于程序的编写,现对命令码进行分类编码,如表 1 所示.根据SPI的基本控制时序及FLASH对于时序的要求,编写控制程序. 控制状态机如图 10 所示.当前状态为IDLE时,不断查询外部是否有命令码写入. 若有命令码写入跳转至cmd_send状态. cmd_send状态时,首先让spi的片选及时钟使能信号有效,并且完成命令码的接收. 然后根据接收命令码的类型判断状态机下一步的转向. 如果接收到命令码为写使能或写无效命令则直接转到完成状态fini_done;如果是读状态命令跳转则到读等待状态,并且把所要读的数据个数置为1(读一个字节)、位数置为7(8 b);若是为其它命令码,则转至地址发送状态addr_send. 在地址发送完成之后,再次对命令码类型cmd_type进行判断. 处于写状态writ_data时,FIFO控制器将数据从FIFO1和FIFO2中读出并完成并串转换,在时钟时加载至数据输入总线. 在完成读写数之后,转向完成状态fini_done. 处于完成状态fini_done时, spi的片选及时钟使能信号均转成无效.程序是在ISE14.2环境下编写的,结合自带的嵌入式逻辑分析仪Chipscope进行在线调试分析. 调试时对系统输入的模拟信号为峰值为5 V、直流偏置为+2.5 V、频率为1 kHz的正弦波,将AD的采样率设置为400 KPS. 通过设置触发条件抓取不同采集通道上的数据. 图 11,图 12 给出的是采集通道为1时的板级信号.在写入读命令和地址(200000H),测试时采集线连接flash_addr的高16 b,因此显示的是2000H)之后, SPI Flash在时钟下降沿时将目标地址的数据加载至数据输出端口. FPGA在上升沿时把数据锁存进读寄存器(mydata_o)并完成移位操作. 图12是以波形形式显示的读寄存器中数据. 对比模拟输入与的数据输出,二者数据一致. 关闭系统电源之后,重新给系统上电, FPGA将SPI Flash中的配置程序加载至片内. 此时程序同样能够实现预设的功能,说明用户写入的数据并未对配置程序产生影响,验证了复用方案的正确性.本文设计了一种复用FPGA配置存储器方案,并且经过仿真与在线调试验证了复用方案的可行性. 此种方案使得FPGA的配置存储器的存储空间得到充分利用,并且节省采集卡板的空间,使得采集存储系统小型化、集成化成为可能. 此外,本设计中采用的是模块化设计, SPI控制程序可以作为一个模块被例化进其他工程中,因此具有很高的兼容性.【相关文献】[1] 黄耀兴. 现场可编程门阵列性能初探[J]. 硅谷, 2011(5): 193.Huang Yaoxing. Preliminary performance of field programmable gate array [J]. SiliconValley, 2011(5): 193. (in Chinese)[2] 李骞, 汪学刚, 李汉钊. 基于3-DES算法的FPGA加密应用[J]. 电子技术应用, 2008, 34(1):132-134.Li Qian, Wang Xuegang, Li Hanzhao. Application of FPGA encryption based on 3-DES algorithm[J]. Application of Electronic Technology, 2008, 34(1): 132-134.(in Chinese) [3] 李艳, 张东晓, 于芳. RTL综合中FPGA片上RAM工艺映射[J]. 电子学报, 2016, 44(11): 2660-2667.Li Yan, Zhang Dongxiao, Yu Fang. RTL synthesis, FPGA on chip RAM process mapping, Acta[J]. Acta Electronical Sinica, 2016, 44(11): 2660-2667.(in Chinese)[4] 郑文静, 李明强, 舒继武. Flash存储技术[J]. 计算机研究与发展, 2010, 47(4): 716-726. Zheng Wenjing, Li Mingqiang, Shu Jiwu. Flash storage technology[J]. Computer Research and Development, 2010, 47(4): 716-726. (in Chinese)[5] Grupp L M, Caulfield A M, Coburn J, et al. Characterizing flash memory: anomalies, observations, and applications[C]. Ieee/acm International Symposium on Microarchitecture. IEEE, 2010: 24-33.[6] 高剑, 郭士瑞, 蒋常斌. FLASH存储器的测试方法[J]. 电子测量技术, 2008, 31(7): 117-120. Gao Jian, Guo Shirui, Jiang Changbin. Test methods for FLASH memory[J]. Electronic Measurement Technology, 2008, 31(7): 117-120. (in Chinese)[7] Kang D, Jeong W, Kim C, et al. 256 Gb 3 b/Cell V-nand Flash Memory With 48 Stacked WL Layers[J]. IEEE Journal of Solid-State Circuits, 2017, 52(1): 210-217.[8] 张立哲, 刘丽静. 适应远程升级的FPGA配置方法[J]. 计算机与网络, 2011(14): 56-59. Zhang Lizhe, Liu Lijing. FPGA configuration method for remote upgrade[J]. Computer and Network, 2011(14): 56-59. (in Chinese)[9] Wirthlin M, Johnson E, Rollins N, et al. The reliability of FPGA circuit designs in the presence of radiation induced configuration upsets[C]. IEEE Symposium on Field-Programmable Custom Computing Machines. IEEE Computer Society, 2003: 133. [10] 宁李谱, 杨宾峰, 苗青林. FPGA器件的配置方式研究[J]. 河南科技学院学报(自然科学版), 2008, 36(3): 109-110.Ning Lipu, Yang Binfeng, Miao Qinglin. Study of configuration schemes of FPGAs[J]. Journal of Henan Institute of Science and Technology (Natural Science Edition), 2008,36(3): 109-110. (in Chinese)[11] 李飞飞, 苏延川, 王鹏. 基于DSP的FPGA配置方法研究与实现[J]. 现代电子技术, 2011,34(24): 60-62.Li Feifei,Su Yanchuan,Wang Peng. Research and implementation of FPGA configuration with DSP[J]. Modern Electronics Technique, 2011, 34(24): 60-62. (in Chinese)[12] Xie T T. A FPGA Configuration Method for Improving System Initial Efficiency[J]. Computer & Modernization, 2012, 203(7): 215-217.[13] Gomez-Cornejo J, Zuloaga A, Villalta I, et al. A novel BRAM content accessing and processing method based on FPGA configuration bitstream[J]. Microprocessors & Microsystems, 2017, 49: 64-76.。

一种基于PCIe总线的SPIFlash内FPGA程序在线更新方法

56 | 电子制作 2021年05月0 引言采用SPIFlash 配置的FPGA 程序通常都是通过FPGA 厂家提供的程序下载器进行更新,一般仪器FPGA 程序的更新方式有两种:(1)打开产品机箱用专用程序下载器通过JETAG 接口更新FPGA 程序,这种方式操作复杂且需要专业人员完成;(2)把FPGA 程序下载器的功能集成到电路板中,利用厂商提供的程序下载软件更新程序,这种方案需要加入额外电路器件,增加了电路板器件的布局空间、功耗及设计成本。

鉴于一般仪器的CPU 模块与FPGA 之间都有PCIe 总线连接,并且FPGA 和SPIFlash 直接连接,因此在FPGA 正常工作时可以让CPU 软件通过PCIe 总线将要更新的FPGA 程序以文件形式先传递给FPGA,然后在FPGA 内设计SPIFlash 芯片的烧写控制逻辑,进而实现SPIFlash 内FPGA 程序的在线更新。

本文以7系列FPGA 为例,7系列FPGA的配置过程具备MultiBoot 和FallBack 机制——FPGA 在上电配置时,MultiBoot 机制允许FPGA 选择SPIFlash 中指定区域的比特流来配置,此版本比特流称为update 镜像,如果配置失败,则触发FallBack 机制将另一个性能良好的固定版本配置到FPGA 中,从而保证FPGA 可以正常工作,此版本比特流称为golden 镜像。

golden 和update 这两个镜像会一起作为初始化镜像用专用程序下载器下载到SPIFlash 中,在线更新仅对SPIFlash 的update 镜像区域进行更新。

本文在7系列FPGA 的MultiBoot 和FallBack 机制的基础上,阐述了一种在线更新Flash 内FPGA 程序的方法,此方法不需要拆机连接程序下载器,更不需要增加额外硬件,在软件界面上即可控制SPIFlash 内FPGA 程序更新过程。

1 方案设计■1.1 总体方案首先将golden 和update 镜像一起作为SPIFlash 初始化镜像下载到SPIFlash 中,然后需要更新FPGA 程序时,使用在线程序更新功能升级SPIFlash 的update 镜像即可。

FPGA实现SPI

FPGA实现SPIFPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以实现不同的数字电路功能。

SPI(Serial Peripheral Interface)是一种同步串行通信协议,常用于连接外围设备和主控制器。

在本文中,将介绍如何使用FPGA实现SPI。

1.确定硬件资源:首先,需要确定FPGA中可用的IO资源。

SPI需要至少4个IO口,分别是主设备的时钟引脚(SCK),主设备输出的数据引脚(MOSI),主设备输入的数据引脚(MISO)和片选引脚(SS)。

根据所用的FPGA型号,可以查找对应的引脚定义。

2.确定SPI时序:SPI的时序是非常重要的,不同设备可能有不同的时序规范。

一般情况下,SPI的时序包括时钟下降沿数据采样、时钟上升沿数据输出等。

SPI的时序图可以在设备的数据手册中找到。

3. 编写SPI控制器:SPI控制器可以用硬件描述语言如VHDL或Verilog编写。

控制器的功能包括生成时钟、控制数据的发送和接收、以及处理片选信号。

a.时钟生成:SPI通信需要一个时钟信号来驱动数据的传输。

可以通过计数器模块来生成控制器的时钟信号。

计数器的频率一般是SPI时钟频率的若干倍。

b. 数据发送:对于主设备(Master),要发送数据给外设,可以使用移位寄存器(Shift Register)来存储要发送的数据。

可以使用计数器生成移位寄存器的时钟信号,通过串行输入数据,并在时钟的上升沿时将数据发送到MOSI引脚。

c.数据接收:对于主设备,要接收外设发送的数据,可以使用另一个移位寄存器来接收MISO引脚传输的数据。

可以使用计数器生成移位寄存器的时钟信号,通过MISO引脚接收数据,并在时钟的下降沿时将数据存储到接收寄存器。

d.片选控制:SPI通信需要一个片选信号来选择要与主设备通信的外设。

可以通过一个时序控制器实现片选信号的生成。

在与一些外设通信时,使能片选信号,否则禁用片选信号。

XILINX-SPI-FLASH烧写流程小结

Xilinx SPI FLASH 的烧写方法

1、首先在ISE中打开要烧写的工程,然后如图双击打开烧写工具。

2、打开烧写工具之后,双击边界扫描。

3、在右边空白区域右击,选择Cable Auto Connect,然后再次右击空白区域,选择Initial Chain。

4、上一步操作完成后会弹出如下界面,选择NO。

5、选择OK。

6、然后如下列图选择打开。

7、由于我们的板子是SPI FLASH,所以如图选择,并点击箭头。

8、如图一步步选择FLASH容量、输出MCS文件的路径和名称。

9、按以上选择好之后,如下列图,点击OK添加.bit文件,〔如果项目中只包含verilog或者VHDL代码,则直接选择.bit文件,如果包含SDK中的C代码,则选择相应的download.bit文件〕。

10、由于此项目包含C代码,所以如下列图选择。

11、选择好之后会提示是否加入另外一个文件,这里选择NO。

12、如图左击一下左上角的选项,然后双击左下角的选项,活弹出生成文件成功。

13、如图右击选择添加FLASH。

14、选择刚刚生成的MCS文件。

15、选择好板子上的FLASH型号。

16、选择好之后,如图右击首先对FLASH进行擦除。

17、擦除完成之后,选择对FLASH进行编程写入。

18如图可以看到进度条和读ID号。

19、成功。

XilinxFPGASPIFLASH加载流程

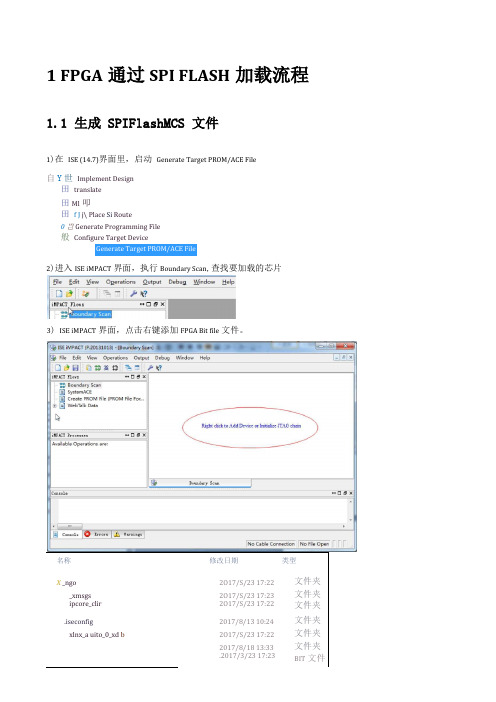

1 FPGA 通过SPI FLASH 加载流程1.1 生成 SPIFlashMCS 文件1)在 ISE (14.7)界面里,启动 Generate Target PROM/ACE File自Y 世 Implement Design田 translate田Ml 叩田 f J j\ Place Si Route0岂 Generate Programming File般 Configure Target Device2)进入ISE iMPACT界面,执行Boundary Scan ,查找要加载的芯片名称 修改日期类型X _ngo2O17/S/23 17:22 文件夹 _xmsgs 2O17/S/23 17:23 文件夹 ipcore_clir 2O17/S/23 17:22 文件夹 .iseconfig2017/8/13 10:24 文件夹 xlnx_a uito_0_xd b2O17/S/23 17:22 文件夹2017/8/18 13:33 文件夹 .2017/3/23 17:23BIT 文件Generate Target PROM/ACE File3) ISE iMPACT 界面,点击右键添加FPGA Bit file 文件。

4) ISE iMPACT界面,启动Create PROM File (PROM File format),进行格式转化,按照截图顺序进行操作。

2017/8/23 17:22 2017/8/23 17:23 2017/8/2317:222017/8/1B 10:24 2017/8/2317:222017/8/18 13:33点击 Generate FileSPI Flash MCS 格式文件已经生成,“Generate Succeeded”文件夹 文件夹 文件夹 文件夹 文件夹 文件夹_ngo J _xm$gsipcore_dir is econfig2017/8/23 17:23 BIT 文彳牛1.2 MCS文件加载至UFLASH1)回到Boundary Scan界面,选中FPGA上面的SPI点击右键,选择fpga_top.mcs文件Ji _ngo 2O17/B/23 17:22 文件夹_xmsgs 2017/&/23 17:23 文彳标Ji ipcore_dir 2017/S/23 17:22 刈丘Jji isecopfig 2017/&/18 10:24 交彳4^谒xlnx_auto_0_xd b 2017/B/23 17:22 文^^Jjjx5t2017/B/1313:33 文件夹<Qfp ga Jop.2O17/&/23 17:40 M匚£ 文化□Untitled.mc& 2017/S/23 15:27 MCS 文仕2)根据板级设计,选择正确的SPI FPGA型号3)选中SPI FPGA,执行Available Operations或者右键选择操作,最后看到“Program Succeeded售 Device Programming Properties - Device 1 Programming Properties Bl Boundary-ScianDevice 1 ( FPGA xc6slxl6 )Property Name ValueVerify画 _____________Genersal CPLD And PR.OM Properties Design-Specific Erase Before Programming 囹 FPGA Device Specific Programming Properties After programming Flash...automatically load FPi C :=LTicelipplyDevice 1 ( Attached FLASH W2!ISE iMPACT (P.20131013) - [Boundary Scan] I E XILINF用> File Edit View Operations Output Debug Window Help Console\S\ ConsoleErrors l _j\ WarningsConfiguration] Dig i I ent JTAG-HS1 10000000 |BonrLd :=Lry Sc :=L T L空 FROM File Formatter : SFI FlElapsed time =20 seciMFACT Flows S--嚣1 Boundary Scan置 SystemACE三 Create PROM File (PROM File For.., S mWebTalk Data Right click device to select operationsJWUWkAvailable Operations are:iMFACT Processes曰 Blank Check 曰 Readback Get Device Checksum f Read Device Statusxc6sbc16 fpga_top.brtTD0 ------------ Z -----Program Program Succeeded。

基于CPLD实现FPGA的SPI Flash配置

基于CPLD实现FPGA的SPI Flash配置在FPGA设计中,通常需要将配置数据存储在外部闪存器中,以便FPGA在上电后可以正确配置。

常用的文化遗产具有以下几种:Parallel Flash:传统的存储器,通常包含16至32位数据总线,需要大量引脚。

但是,它们提供高性能,可以以快速的速度读写数据。

Serial Flash:通常采用SPI(串行外设接口)或QSPI(准同步串行通信接口)接口进行通信,可使用少量引脚,并且内部积累了大量闪存技术。

在此示例应用中,我们将使用CPLD实现FPGA的SPI Flash配置。

SPI Flash框图SPI Flash与FPGA之间的接口非常简单,只需要四个信号,分别是“Chip Select”(选通)、“Clock”(时钟)、“MOSI”(主机输出/从机输入)和“MISO”(从机输出/主机输入)。

FPGA需要传输的读写命令和地址,以及从Flash接收的数据。

因此,与Flash通信的协议非常重要。

常见的协议是“读”和“写”命令序列,以及擦除和编程命令。

操作步骤1. 将SPI Flash的“Chip Select”(CS)引脚连接到FPGA中的任意引脚。

2. 将SPI Flash的“Clock”(CLK)引脚连接到FPGA中的任意引脚。

3. 将SPI Flash的“MOSI”(主机输出/从机输入)引脚连接到FPGA中的任意引脚。

4. 将SPI Flash的“MISO”(从机输出/主机输入)引脚连接到FPGA中的任意引脚。

5. 在FPGA制作的SPI硬核中,设置针脚分配。

如果您使用芯片设计工具,可以使用默认分配。

6. 实现SPI驱动程序以处理读写和闪存操作。

7. 要将配置数据加载到闪存中,首先需要在计算机上生成.bin 文件。

可以使用Xilinx编译器进行编译。

8. 在闪存中使用适当的FLASH编程工具将.bin文件加载到闪存中。

9. FPGA在上电后会读取配置信息,完成初始化并开始操作。

基于FPGA的SPI Flash控制器的设计与实现

基于FPGA的SPI Flash控制器的设计与实现作者:陈炳成来源:《电子世界》2013年第12期【摘要】传统的Flash读写是通过CPU软件编程实现,其读写速度较慢,且占用CPU资源,另外由于Flash芯片本身功能指令较多,使得对芯片进行直接操作变得非常困难。

本文提出一个基于FPGA的SPI Flash读写硬件实现方案,该方案利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,同时编写的SPI Flash控制器IP 核能够进行移植和复用,作为SOC芯片的功能模块。

SPI Flash控制器采用VHDL语言进行编写,在Modelsim 6.5g上通过功能仿真,并且在XUPV5-LX110T FPGA开发板上通过硬件测试,实现结果表明方案的可行性。

【关键词】FPGA;SPI Flash控制器;IP核;VHDL1.引言Flash是一种具有电可擦除的可编程ROM,按接口可以分为两大类:并行Flash和串行Flash。

并行Flash存储量大,速度快;而串行Flash存储量相对较小,但体积小,连线简单,可减小电路面积,节约成本。

SPI Flash是内嵌SPI总线接口的串行Flash,它比起传统的并行总线接口Flash,节省了很多的I/O口资源,从而为系统功能的扩展提供了更多的可能。

随着SPI Flash越来越多地应用到各种领域,其传统读写方式中读写速度不够快、占用CPU资源以及操作不够简便灵活的缺点表现得更为突出,如何解决以上问题成为大家关注的焦点。

利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,且不占用CPU资源,同时编写的SPI Flash控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。

因此提出了一种基于FPGA的SPI Flash控制器的设计方案,并用VHDL实现。

编写的SPI Flash控制器IP核在Modelsim 6.5g上进行了功能仿真,在FPGA开发板上进行了测试验证,可作为功能模块应用于SOC芯片设计。

基于SPI FLASH的FPGA多重配置

基于SPI FLASH 的FPGA 多重配置

通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。

以Virtex5 系列开发板和配置存储器SPI FLASH 为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多重配置实现的具体步骤,对实现复杂硬件设计工程有一定的参考价值。

现代硬件设计规模逐渐增大,单个程序功能越来越复杂,当把多个功能复杂的程序集成到一个FPGA 上实现时,由于各个程序的数据通路及所占用的资源可能冲突,使得FPGA 控制模块的结构臃肿,影响了整个系统工作效率。

通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。

以Virtex5 系列开发板和配置存储器SPI FLASH 为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多重配置实现的具体步骤,对实现复杂硬件设计工程有一定的参考价值。

0 引言

现代硬件程序设计规模越来越大,功能越来越复杂,当多个应用程序同时在一个硬件平台上实现时,各个程序的资源使用和数据通路可能会冲突,这增加了控制电路设计的复杂程度,给开发人员增加了工作量和开发难度。

通过多重配置,可以将多个应用程序根据需要分时加载到FPGA 中,不仅精简了电路设计,而且使系统更加灵活。

FPGA 多重配置的特点可以让特定条件下的用户选择片上资源不多的FPGA 去实现需要很多资源FPGA 才能实现的功能,这大大降低了开发费用,同时提高了FPGA 的利用率。

Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允许用户在不掉。

基于FPGA的SPI接口Flash控制器设计及在存储配置数据中的应用

基于FPGA的SPI接口Flash控制器设计及在存储配置数据中的应用赵庆平;姜恩华【摘要】介绍了SPI工作原理,给出了一种基于FPGA的SPI控制器的设计方法。

利用FPGA丰富的逻辑资源以及产生精确时序的能力,非常方便地对SPI flash进行读写、擦除等操作,从而能快速、准确地存储数据。

阐述SPI控制器的设计过程,使用Modelsim进行仿真验证,并用VHDL硬件描述语言进行编程,下载到FPGA开发板上进行测试验证,对SPI接口Flash进行操作。

证明了系统设计方法的正确性和可靠性。

该方法对FLASH存储控制系统的设计具有普遍适用性,可用于对FPGA配置进行保存。

%It introduces the operating principles of SPI (serial peripheral interface) and gives a designed method by using SPI controller based on FPGA (Field Programmable Gate Array). We can expediently read-write and wipe SPI flash to quickly and accurately storage data with rich logical resources and accurate time series making by FPGA.It also expounds the designing process of SPI controller, which utilizes the simulation and verification by Modelsim and uses VHDL hardware description language controller to program, and then download the program to FPGA development board to test and verify and finally operates the SPI interface flash. It is proved that the method is correct and reliable, and has general applicability to the system designing of the FLASH controller and can be used to save the FPGA configuration.【期刊名称】《唐山师范学院学报》【年(卷),期】2014(000)002【总页数】4页(P69-72)【关键词】SPI控制器;FPGA;VHDL设计;Modelsim仿真【作者】赵庆平;姜恩华【作者单位】淮北师范大学物理与电子信息学院,安徽淮北 235000;淮北师范大学物理与电子信息学院,安徽淮北 235000【正文语种】中文【中图分类】TP332.3使用德致伦公司出品的开发板Genesys,该开发板使用的FPGA芯片是xilinx公司的Virtex-5,Virtex-5系列采用第二代高级芯片组合模块(ASMBLTM)列式架构,采用业界一流的65 nm铜工艺技术,支持多达330 000个逻辑单元,6个时钟管理模块,多达1 200个用户接口,提供从1.2 V到3.3 V的广泛的I/O标准范围,高达16.4 Mb的集成模块存储器,与Select IO技术配合使用,简化源同步接口[4]。

fpga自学笔记——设计与验证

fpga自学笔记——设计与验证FPGA(现场可编程门阵列)是一种集成电路(IC)设备,可通过重新编程实现不同电路的功能。

在现代电子行业中,FPGA被广泛应用于计算机硬件开发、通信系统、控制器和许多其他应用领域。

本篇自学笔记将涵盖FPGA的设计与验证的基本概念和技术。

一、FPGA设计流程FPGA的设计流程包括硬件描述语言(HDL)编写、仿真验证、综合、实现和验证。

以下是FPGA设计流程的详细步骤:1.硬件描述语言编写:FPGA设计通常使用硬件描述语言进行编写,如VHDL(硬件描述语言)或Verilog。

这些语言可以描述出FPGA中各个组件的逻辑和连接关系。

2.仿真验证:对设计进行仿真验证是FPGA设计流程的重要一步。

利用仿真工具,可以检查设计是否满足规范,并进行功能验证。

仿真验证可以帮助发现和解决设计中的问题。

3.综合:综合是将设计转换为FPGA的可编程逻辑单元(PLU)的过程。

综合工具将HDL代码转换为逻辑门电路,并生成一个逻辑网表作为输入。

4.实现:实现是将逻辑网表转换为FPGA器件的过程。

这个过程包括将逻辑网表分配到实际的逻辑单元和I/O资源,进行布线以及生成配置文件。

5.验证:验证是确保设计在FPGA上正常运行的过程。

通常这一步会通过连接实际的外设和运行测试程序来验证设计的功能和性能。

二、FPGA设计与验证工具在FPGA设计与验证中,有许多工具可供选择,如:1.设计工具:FPGA设计工具是用于编写和组织HDL代码的软件。

常用的设计工具包括Xilinx的Vivado和ISE,以及Altera(现在是英特尔)的Quartus II。

这些工具提供了综合、实现和验证的功能。

2.仿真工具:仿真工具用于验证设计的正确性和性能。

常用的仿真工具包括ModelSim、VCS和NC-Verilog等。

这些工具可以模拟设计的行为,并生成波形图以进行分析。

3.布线工具:布线是将逻辑网表分配到FPGA器件中的实际逻辑单元和I/O资源的过程。

FPGA设计与验证

FPGA实现SPI

FPGA实现SPIFPGA(Field-Programmable Gate Array)是一种可编程的逻辑芯片,可以通过编程实现不同的功能。

SPI(Serial Peripheral Interface)是一种通信协议,可以在芯片之间进行数据传输。

要在FPGA上实现SPI,首先需要了解SPI的基本原理和通信方式。

SPI使用主从模式,由一个主设备控制多个从设备。

主设备通过时钟信号(SCLK)控制数据的传输,同时使用一个片选信号(SS)来选择目标从设备。

主设备通过MOSI(Master Out Serial In)线将数据发送给从设备,从设备则通过MISO(Master In Serial Out)线将数据回传给主设备。

为了实现SPI通信,需要在FPGA内部设计SPI控制器。

SPI控制器的主要功能包括时钟生成、数据发送和接收、片选信号控制等。

在FPGA中,可以使用可编程逻辑单元(PL)和可编程输入/输出单元(IOB)来实现SPI控制器。

首先,需要使用PL来生成时钟信号。

可以使用计数器和状态机来实现时钟分频和时序控制。

通过控制计数器以及时钟信号的边沿来生成SPI所需的SCLK信号。

接下来,需要使用IOB来进行数据的发送和接收。

可以将MOSI线和MISO线分别连接到适当的IOB引脚。

对于数据的发送,可以通过内部存储器或寄存器来存储要发送的数据,并通过控制逻辑将数据发送到MOSI线上。

对于数据的接收,从MISO线上获取到的数据需要经过逻辑电平转换,并存储或传递给其他组件。

最后,需要使用逻辑电平转换器来生成SPI的片选信号。

可以使用门电路或者专门的逻辑转换芯片来控制片选信号的逻辑电平。

通常情况下,只有在特定的片选信号处于逻辑低电平时,相关的从设备才能接收和响应数据。

在设计完成后,可以使用硬件描述语言(HDL)如Verilog或VHDL来描述SPI控制器,并使用FPGA开发工具进行综合、布局和编程。

在开发工具中,可以了解到FPGA的资源占用情况,时序约束和时钟分频等设置,以及进行仿真和调试。

xilinx的fpga读取flash的原理

xilinx的fpga读取flash的原理一、概述Xilinx的FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,广泛应用于工业和消费电子领域。

Flash存储器是FPGA 的一种重要外部存储设备,用于存储FPGA的配置信息和其他需要长期保存的数据。

本文将介绍Xilinx的FPGA读取Flash的原理,包括Flash存储器的基本原理、FPGA与Flash的接口设计、数据传输方式以及读取Flash的控制逻辑。

二、Flash存储器原理Flash存储器是一种非易失性存储器,可以像硬盘一样进行写入和擦除操作。

它主要由存储单元和外围电路组成,存储单元通常采用浮栅晶体管结构。

写入操作时,Flash通过把掺杂剂注入到浮栅中来改变浮栅电导率,从而实现电荷的存储。

擦除操作时,通过改变浮栅的电场强度来移除注入到浮栅中的电荷,从而恢复到原始状态。

读取操作时,通过测量电荷的变化来确定存储单元的值。

三、FPGA与Flash接口设计FPGA与Flash之间的接口设计是实现数据传输和控制的关键。

Xilinx的FPGA通常采用AXI-Stream接口与外部设备进行数据传输。

AXI-Stream接口是一种通用的、基于流的接口,适用于高性能数据传输。

FPGA与Flash之间的接口通常包括以下部分:1. 物理层:包括总线协议和物理连接方式,如PCIe、USB、SPI 等。

2. 数据层:用于传输数据和控制信号,包括地址、读写控制信号和数据信号。

3. 控制层:用于实现数据的读取、写入和擦除操作,包括命令、状态机和中断信号。

四、数据传输方式FPGA读取Flash的数据传输方式通常采用AXI-Stream流接口进行数据传输。

FPGA通过发送AXI-Stream控制指令来控制Flash的数据传输,包括数据的起始地址、传输速率和传输周期等。

Flash则根据FPGA的控制指令进行数据的读取和传输。

在数据传输过程中,FPGA和Flash之间需要进行时钟同步和数据校验,以确保数据传输的准确性和完整性。

一种基于FPGA的在线升级方案

第35卷第5期2020年10月成都信息工程大学学报JOURNAL OF CHENGDU UNIVERSITY OF INFORMATION TECHNOLOGYVol.35No.5Oct.2020文章编号:2096-1618(2020)05-0493-06一种基于FPGA 的在线升级方案万垚,李蠡(成都信息工程大学通信工程学院,四川成都610225)摘要:一般对FPGA 程序升级,需要使用下载器通过JTAG 接口与FPGA 连接,在一些不方便开盖的环境下,此种升级方案非常困难。

基于XILINX 公司的XC6SLX9芯片,利用FPGA 的MultiBoot 将多个配置文件下载入Flash 中的特性,介绍一种基于Flash 、FPGA 和RS232串行通信的在线升级方案。

FPGA 通过SPI 总线配置Flash ,ICAP 接口使FPGA 跳转到Flash 的对应地址读取烧写到Flash 中的.bin 文件。

方案可在不增加额外器件且不开盖的情况下仅通过一个RS232通信接口,上位机软件就能完成对用户设计的功能程序或产品程序的升级,对程序存储芯片Flash 的操作均由FPGA 内部逻辑实现。

结果表明,该方法有效且具有很好的移植性和可扩展性。

关键词:SPI ;Flash ;RS232串行通信;ICAP ;MultiBoot中图分类号:TP332.1文献标志码:Adoi :10.16836/j.cnki.jcuit.2020.05.002收稿日期:2019-11-26基金项目:国家自然科学基金资助项目(61601065)0引言如今,电子产品的复杂度和集成度越来越高,产品的迭代速度也在变快。

FPGA 以其低时延、速度快和可重配置的优势已经被应用在通信、工业控制和图像处理等领域。

这些领域的程序算法为适应产品需求的提升也在不断更新。

因此对FPGA 能进行在线升级从而快速更新产品功能的需求被提出。

传统的对FPGA 配置的方案需要对设备进行拆卸,使用JTAG 接口对FPGA 进行重配置进而对程序进行升级。

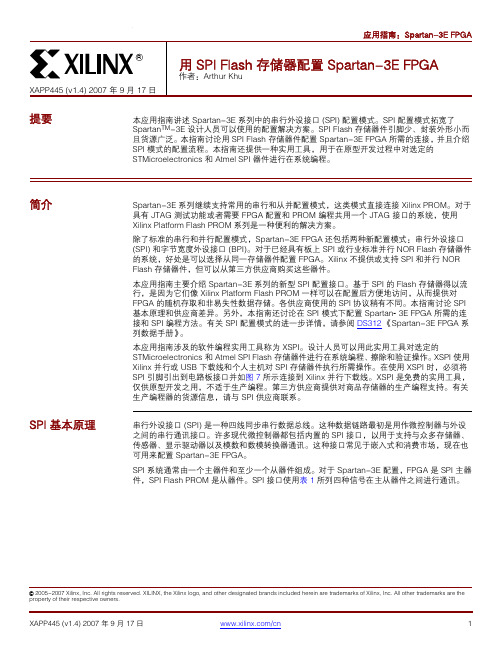

用SPI Flash存储器配置Spartan-3E FPGA

© 2005-2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.提要本应用指南讲述 Spartan-3E 系列中的串行外设接口 (SPI) 配置模式。

SPI 配置模式拓宽了Spartan TM -3E 设计人员可以使用的配置解决方案。

SPI Flash 存储器件引脚少、封装外形小而且货源广泛。

本指南讨论用 SPI Flash 存储器件配置 Spartan-3E FPGA 所需的连接,并且介绍 SPI 模式的配置流程。

本指南还提供一种实用工具,用于在原型开发过程中对选定的 STMicroelectronics 和 Atmel SPI 器件进行在系统编程。

简介Spartan-3E 系列继续支持常用的串行和从并配置模式,这类模式直接连接 Xilinx PROM。

对于具有 JTAG 测试功能或者需要 FPGA 配置和 PROM 编程共用一个 JTAG 接口的系统,使用 Xilinx Platform Flash PROM 系列是一种便利的解决方案。

除了标准的串行和并行配置模式,Spartan-3E FPGA 还包括两种新配置模式:串行外设接口 (SPI) 和字节宽度外设接口 (BPI)。

对于已经具有板上 SPI 或行业标准并行 NOR Flash 存储器件的系统,好处是可以选择从同一存储器件配置 FPGA。

Xilinx 不提供或支持 SPI 和并行 NOR Flash 存储器件,但可以从第三方供应商购买这些器件。

本应用指南主要介绍 Spartan-3E 系列的新型 SPI 配置接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

备 , FG 使 P A一方面 与电脑 串 口通信获得数据 , 另一方面对 S IFah进行控制 , P ls 这样就完成了 F G P A配置数据 的控制 和存储 。

关 键词 : 可编程逻辑门阵列; 串行接口F s;el D ;i lhV ro H LIm仿真 a ig s

中图分 类号 : P 3 . T 3 21

( oi E e et , L gc lm n) 3 2个 1 bt BokR M模 块 , 8k ye的 lc A l 6个 1  ̄ 8b 嵌入式乘 法器 , 8 1 i t 2个锁 相环 ( L ) 4 PL和 个时钟管 理模 块 ( C 。在这 款 14针 tg封 装 的 D M) 4 q F G 中. PA 用户可用 I0为 12个 _ , / 0 3 可以满足本 系统 ] 的需求 。 Fah芯 片采 用 的 配置 芯 片 是 Wi o d公 司 的 l s n n b

关珊 珊 . 洁 敏 周

( 南京航空航天大学 民航学院 , 南京 2 0 1 ) 10 6

摘 要 : 基于 Xlx P A的SI lh i G i F n P a 控制器实现了一种在线配置Fa 的方法。由于 F s 芯片本身功能指令较多, Fs lh s lh a 使得对

它进行直接操作变得非常 困难 , 而利用 F G P A丰富的逻辑资源以及 产生精确 时序 的能力 , F G 以 P A为主设备 ,P l h为从设 SI a Fs

( il v t nClg ,a n n esyo eoats& At n ui ,aj g20 1 ) Cv i i o eeN g U irt iA a o l v i fA rn ui c s oatsN ni 10 6 r c n

Ab t a t S ls o tol rb s d o ln s r c : PIF a h c n r l a e n Xi x FPGA u sfr r id o n—i e c n iu a in meh d o l s e i p t o wa d a kn fo ln o fg r to to fF a h. Th l s h p i ef h s to mo e f cin i sr c in h tma e is ee t o e ain b c me v r d岱 c t b t e F a h c i t l a o r un to n tu t s t a k t d r c p r to e o e y i ul. u s o F PGA c u is rc o i e o r e n r d c sa c r t i n b lt . GA a e u e s ma t re u p n o c p e ih l gc r s u c s a d p o u e c u ae tmi g a iiy FP c n b s d a se q i me t a d S l s s sa e. PGA o n c si e iswih c mp trf rc mmun c to a a a q iiin a d c n r l h n PIF a h a l v F c n e t n s re t o u e o o iain d t c u sto n o to st e S l s n oh rh n h ti GA o fg r t n frc n r la d so a e h s b e mp e n e . PIF a h i t e a d t a t FP s c n u ai o o to n tr g a e n i lme t d i o Ke r s: GA; PIF a h; rlg HDL;i l t n y wo d FP S l s Ve io smu a i o

E AC 7 1 B E C:2 0

d i1 . 9 9 j i n 1 0 - 4 0 2 1 9 .0 2 0 . 2 s

基 于 X l xF G 的 S I ls 制 器 设 计 与 验 证 in P A i P ah控 F

可能 为此 提 出 了一 种 基 于 F G 的 S IFah控 PA P ls

制器 的设计 方法 , 用 V ro D 并 ei gH L实 现 , I m 中 l 在 s i

用成熟 的 4 m低功耗 铜制程技术制 造 , 5n 实现 了性价 比与功 耗 的 完美 平 衡 。该 芯 片有 95 逻 辑 单 元 12个

文献标 识码 : A

文章 编号 :0 5 9 9 (0 2 0 — 2 6 0 10 — 40 21 )2 0 1— 5

现 场可 编程 门阵列 F G P A常 常进行 大数 据 量 的 处 理 . 据 的存 储 便 成 了 问题 , 用 SIFah大容 数 利 P ls 量、 读写 速度 快 、 成本低 廉 以及数 据在 断电后 不丢失 的特点 , 以将 配置数 据存储 于 S I l h中 | 。它 可 P a Fs 1 ] 比起传 统 的并行 总线 接 口 Fah来 说 节省 了很 多 的 l s I0 口资 源 . 而 为 系 统 功能 的扩 展提 供 了更 多 的 / 从

第3 5卷 第 2期 21 0 2年 4月

电 子 器 件

C iee Ju lo lcrn D v e hn s o ma f e t e i s E o c

Vo . 5 No. 13 2

Apr 2 2 . 01

De i n a d Ve i c to fS a h Co tolr Ba e n Xi n sg n rf a in o PIFl s n r le s d o l x FPGA i i GU N h nh n, HOU Je n A S as a Z imi