单片机I-O口推挽输出与开漏输出的区别

详细解说开漏输出和推挽输出

详细解说开漏输出和推挽输出1,开漏输出(Open-Drain)首先讲一下集电极开路输出(Open-Collector),单片机I/O常用的输出方式的开漏输出(Open-Drain),漏极开路电路概念中提到的“漏”是指MOSFET的漏极。

同理,集电极开路电路中的“集”就是指三极管的集电极。

在数字电路中,分别简称OD门和OC门。

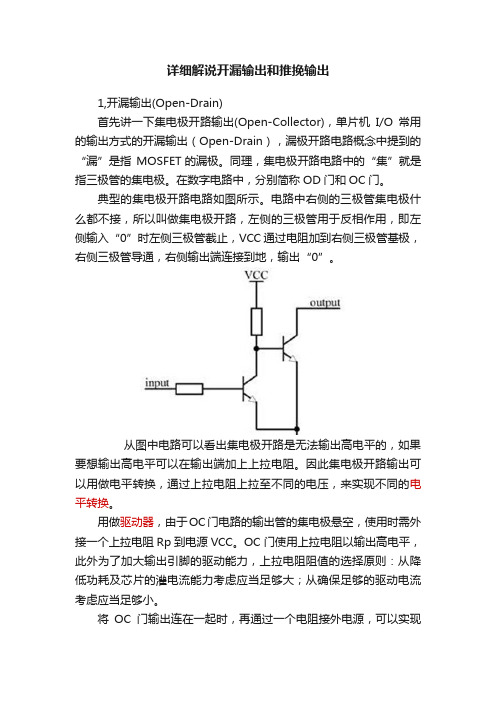

典型的集电极开路电路如图所示。

电路中右侧的三极管集电极什么都不接,所以叫做集电极开路,左侧的三极管用于反相作用,即左侧输入“0”时左侧三极管截止,VCC通过电阻加到右侧三极管基极,右侧三极管导通,右侧输出端连接到地,输出“0”。

从图中电路可以看出集电极开路是无法输出高电平的,如果要想输出高电平可以在输出端加上上拉电阻。

因此集电极开路输出可以用做电平转换,通过上拉电阻上拉至不同的电压,来实现不同的电平转换。

用做驱动器,由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则:从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

将OC门输出连在一起时,再通过一个电阻接外电源,可以实现“线与”逻辑关系。

只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出的高、低电平符合要求,而且输出三极管的负载电流又不至于过大。

集电极开路输出除了可以实现多门的线与逻辑关系外,通过使用大功率的三极管还可用于直接驱动较大电流的负载,如继电器、脉冲变压器、指示灯等。

由于现在MOS管用普遍,而且性能要比晶体管要好,所以很多开漏输出电路,和后面要讲的推挽输出电路都用MOS管实现。

再来就是开漏输出电路,和集电极开路一样,顾名思义,开漏电路就是指从MOSFET的漏极输出的电路。

典型的用法是在漏极外部的电路添加上拉电阻到电源如图所示。

完整的开漏电路应由开漏器件和开漏上拉电阻组成。

漏极开路输出和推挽输出

漏极开路输出和推挽输出一、漏极开路(OD)输出:漏极开路(OD)输出,跟集电极开路输出是十分类似的。

将上面的三极管换成场效应管即可。

这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。

对于漏极开路(OD)来说,输出端相当于三极管的集电极。

要得到高电平状态需要上拉电阻才行。

适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内)。

要实现线与需要用OC(open collector)门电路。

是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务。

电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

所谓开漏电路概念中提到的漏就是指MOSFET的漏极。

同理,开集电路中的集就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动(或驱动比芯片电源电压高的负载)。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC内部仅需很下的栅极驱动电流。

如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。

形成与逻辑关系。

如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

如果作为输出必须接上拉电阻。

接容性负载时,下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢。

如果要求速度高电阻选择要小,功耗会大。

所以负载电阻的选择要兼顾功耗和速度。

单片机IO端口工作原理(P0端口,漏极开路,推挽,上拉电阻,准双向口)

单片机IO端口工作原理(P0端口,漏极开路,推挽,上拉电阻,准双向口)一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:输入缓冲器:在P0口中,有两个三态的缓冲器,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态。

图中有一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

图中另一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

图中的锁存器,D 端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q 非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

那么这个多路选择开关就是用于选择是做为普通I/O口使用还是作为‘数据/地址’总线使用的选择开关了。

单片机IO口推挽与开漏输出详解

单片机I/O口推挽与开漏输出详解推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图三。

图三中那个1K的电阻即是上拉电阻。

如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。

将上面的三极管换成场效应管即可。

这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。

另一种输出结构是推挽输出。

推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。

比起OC或者OD来说,这样的推挽结构高、低电平驱动能力都很强。

开漏 推挽 IO口原理

开漏推挽IO口原理(2008-03-20 17:49:06)转载标签:杂谈推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).漏级开路即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态,若需要产生高电平,则需使用外部上拉电阻或使用如LCX245等电平转换芯片。

有些朋友,尤其是未学过此方面知识的朋友,在实际工作中将I/O口设置为漏开,并想输出高电平,但向口线上写1后对方并未认出高电平,但用万用表测量引脚确有电压,这种认为是不对的,对于高阻状态来说,测量电压是无意义的,正确的方法应是外加上拉电阻,上拉电阻的阻值=上拉电压/芯片引脚最大灌(拉)电流。

推挽(wan)方式可完全独立产生高低电平,推挽方式为低阻,这样,才能保证口线上不分走电压或分走极小的电压(可忽略),保证输出与电源相同的高电平,推挽适用于输出而不适用于输入,因为若对推挽(低阻)加高电平后,I=U/R,I会很大,将造成口的烧毁。

对与C8051F的很多型号片子,将I/O口设置为推挽方式的做法为:PnMDOUT=0xff,Pn=0x00,这样设置I/O口为推挽,并输出低电平(可降低功耗)将I/O口设置为漏开方式的做法为:PnMDOUT=0x00,Pn=0x11,这样设置I/O口为漏开。

如果学过三极管放大电路一定知道,前置单管放大器和功放末级放大电路的区别。

单片机内部的逻辑经过内部的逻辑运算后需要输出到外面,外面的器件可能需要较大的电流才能推动,因此在单片机的输出端口必须有一个驱动电路。

这种驱动电路有两种形式:其中的一种是采用一只N型三极管(npn或n沟道),以npn三极管为例,就是e接地,b接内部的逻辑运算,c引出,b受内部驱动可以控制三极管是否导通但如果三极管的c极一直悬空,尽管b极上发生高低变化,c极上也不会有高低变化,因此在这种条件下必须在外部提供一个电阻,电阻的一端接c(引出脚)另一端接电源(即上拉电阻),这样当三极管的b有高电压是三极管导通,c 电压为低,当b为低电压时三极管不通,c极在电阻的拉动下为高电压,这种驱动电路有个特点:低电压是三极管驱动的,高电压是电阻驱动的(上下不对称),三极管导通时的ec内阻很小,因此可以提供很大的电流,可以直接驱动led甚至继电器,但电阻的驱动是有限的,最大高电平输出电流=(vcc-Vh)/r;另一种是互补推挽输出,采用2只晶体管,一只在上一只在下,上面的一只是n型,下面为p型(以三极管为例),两只管子的连接为:npn(上)的c连vcc,pnp(下)的c接地,两只管子的ee,bb相连,其中ee作为输出(引出脚),bb接内部逻辑,这个电路通常用于功率放大点路的末级(音响),当bb接高电压时npn管导通输出高电压,由于三极管的ec电阻很小,因此输出的高电压有很强的驱动能力,当bb接低电压时npn截至,pnp导通,由于三极管的ec电阻很小因此输出的低电压有很强的驱动能力,简单的例子,9013导通时ec电阻不到10欧,以Vh=2.5v,vcc=5v计算,高电平输出电流最大=250MA,短路电流500ma,这个计算同时告诉我们采用推挽输出时一定要小心千万不要出现外部电路短路的可能,否则肯定烧毁芯片,特别是外部驱动三极管时别忘了在三极管的基极加限流电阻。

单片机IO口推挽输出与开漏输出的区别

单片机I/O口推挽输出与开漏输出的区别推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图三。

图三中那个1K的电阻即是上拉电阻。

如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。

将上面的三极管换成场效应管即可。

这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。

另一种输出结构是推挽输出。

推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。

比起OC或者OD来说,这样的推挽结构高、低电平驱动能力都很强。

单片机IO口推挽、开漏输出、准双向IO详解

单片机IO口推挽、开漏输出、准双向IO详解加入论坛的方式:在公众号对话框内,输入数字“1”,即可进入论坛,无需注册,就是这么简单。

诚邀您的加入。

在学单片机和选用逻辑器件的时候我们常别人说这款芯片是推挽输出驱动能力强,这个引脚是开漏输出需要加上拉电阻。

是不是有时候感觉一头雾水?今天就详解一下推挽和开漏,以后你买芯片的时候就可以和别人大声理论了。

1. 什么是推挽输出推挽输出既可以输出低电平,也可以输出高电平,可以直接驱动功耗不大的数字器件。

2. 推挽输出电路的结构推挽电路是由两个三极管或MOSFET,以推挽方式存在于电路中,电路工作时,两只对称的开关管每次只有一个导通,所以导通损耗小、效率高、既提高电路的负载能力,又提高开关速度。

其示意结构如下图所示:1. 当内部输出1电平时,上边的MOS管导通同时下边的MOS管截至,IO口输出高电平;2. 当内部输出0电平时,上边的MOS管截至同时下边的MOS管导通,IO口输出低电平;3. 什么是开漏输出开漏输出只能输出低电平,如果要输出高电平必须通过上拉电阻才能实现。

就类似于三极管的集电极输出。

4. 开漏输出电路的结构如上图:1. 内部输出1时MOS管截止,输出与地断开,这时候IO口其实是没有驱动能力的,需要外部连接上拉电阻才能输出高电平,才能驱动数字器件;2. 内部输出0时MOS管导通,输出低电平,所以开漏能输出低电平;5. 准双向IO在学51单片机的时候老师告诉我们,51单片机的IO口是准双向的,什么是准双向的?示意如下:其结构类似于开漏输出,只不过是把上拉电阻集成到了单片机内部。

6. IO口如何应用对于推挽输出的IO口可以直接输出高低电平驱动功耗较小的数字器件,但对于开漏输出的话必须要在外部接上拉电阻才行。

比如说LPC11C14单片机的片上I2C资源就是开漏输出的,如果要使用这两个引脚做输出就必须加上拉电阻,如下图所示:进入论坛的方式:在公众号对话框内,输入数字“1”,即可进入论坛,无需注册,就是这么简单。

推挽输出、开漏输出、复用开漏输出、复用推挽输出以及上拉输入、下拉输入..

推挽输出、开漏输出、复用开漏输出、复用推挽输出以及上拉输入、下拉输入、浮空输入、模拟输入区别(Push-pull output, open drain output, multiplexing, multiplexing open drain output push-pull output and pull input and pull-down input, floatinginput, analoThe push-pull output, open drain output, multiplexing, multiplexing open drain output push-pull output and pull input and pull-down input, floating input, analog input differenceAbout Push-Pull Outputs, open drain outputs, multiplexed open drain outputs, and multiplexed Push-Pull OutputsPull down input, input, floating input, analog input and differenceWhen I read the data book recently, I found that there are 8 kinds of configuration for GPIO in Cortex-M3:(1) GPIO_Mode_AIN analog input(2) GPIO_Mode_IN_FLOATING floating input(3) GPIO_Mode_IPD pull down input(4) GPIO_Mode_IPU pull-up input(5) GPIO_Mode_Out_OD open drain output(6) GPIO_Mode_Out_PP push-pull output(7) GPIO_Mode_AF_OD multiplex open drain output(8) GPIO_Mode_AF_PP multiplex push-pull outputFor the novice, I think this concept is must know, usually contact is the most open drain push-pull output, output, pull the input of the three, but has not done up to these. So, here's a summary:Push-pull output: can output high, low level, connect digital devices; push-pull structure is generally refers to two transistors respectively by two complementary signal control, always in a triode conduction time another cut-off. The high and low levels are limited by the power of the IC.The push-pull circuit is the two parameter of the same transistor or MOSFET in push-pull mode exists in the circuit, each responsible for the positive and negative half cycles of wave amplification, circuit, power switch two symmetrical tube only one conduction,Therefore, the conduction loss is small and the efficiency is high. The output can either tap the load or extract the current from the load. The push-pull type output stage not only improves the load capacity of the circuit, but also increases the speed of switching.Detailed understanding:As shown, the output stage of the push-pull amplifier has twoarms (two sets of amplifying elements). When an arm current increases, another arm current decreases, and the two states rotate in turn. For load, it seems that a "arm" is pushing, a "arm" in the pull, together to complete the current output task. When the output high power, that is, the lower load gate input high power, the output current will be lower than the gate from the power supply through the VT3 pull out. In this way, when the output is high or low, the VT3 and the VT5 will work alternately, thus reducing the power consumption and improving the endurance of each tube. Because no matter which way to go, the resistance of the pipe is very small, so that the RC constant is very small, and the conversion speed is very fast. Therefore, the push-pull type output stage not only improves the load capacity of the circuit, but also improves the switching speed.Open drain output: the output is equivalent to the collector of the triode. In order to get a high level state, a pull-up resistor is needed. It is suitable for making current mode drivers and has relatively strong ability to absorb current (less than 20mA in general)The open drain circuit has the following characteristics:1. use external circuit drive capability to reduce IC internal drive. When the IC is internally MOSFET, the drive current is flowing from the external VCC through the R, pull-up, MOSFET to GND. The IC requires only a very low gate drive current.2. generally speaking,Open drain is a device used to connect different levels, withthe matching level, because the open drain pin is not connected to an external pull-up resistor, only the output low, if you need to have a high level output function requires a pull-up resistor, a good advantage is by changing the power supply voltage on it can change the transmission level. For example, with a pull-up resistor, you can provide TTL/CMOS level output. The resistance of the pull-up resistor determines the speed at which the level of the logic level is converted. The higher the resistance, the lower the speed, the smaller the power consumption, so the choice of load resistance should take into account both power consumption and speed3., OPEN-DRAIN offers flexible output, but also has its weakness, that is, to bring the delay along the rising edge. Because the rising edge charges the load through an external pull-up passive resistor, when the resistor is selected, the time delay is small, but the power consumption is large; on the contrary, the delay is large and the power consumption is small. Therefore, if the delay is required, it is recommended to use the falling edge output.4., you can connect multiple open drain Pin to one line. Througha pull-up resistor, a logical relationship is formed without increasing the number of devices. This is also the principle of I2C, SMBus and other buses to determine the bus occupancy status. Added: what is "line and"? :In a node (line), connect a pullup resistor to the collector C power VCC or VDD and N or NPN NMOS or drain D transistor, the transistor emitter E or S source are connected with a ground wire, as long as there is a transistor saturation, this node(line) is pull to the ground level.Because the base transistor current injection (NPN) or gate with high level (NMOS), the transistor will be saturated, so the base or gate of the node (line) is the relationship or non NOR logic. If this node is followed by an inverter is OR or logic.In fact, can be simply understood as: all pins are connected together, an external pull-up resistor, if there is a pin output to logic 0, equivalent to the ground, and the parallel loop "is equivalent to a wire short circuit, so the external circuit logic level is 0, only for high level, and the result is logic 1.For push-pull output and open drain output, the last one is outlined in the simplest form:This figure is on the left side of the push-pull output mode, the comparator output high power triode PNP usually below and above the pipe cut-off, NPN triode output level VS+; when the comparator output low on the contrary, PNP triode output and connected to low electrical level. The right side can be understood as open drain output, which needs to be pulled up.Floating input: input for floating, very authoritative interpretation has not been found, but from the following diagram to understand.The floating input is generally used for the external input keys, combined with the input part of the circuit diagram, Iunderstand the floating input condition, level IO is uncertain, completely decided by external input, if the pin is left unconnected in case of the level of the read port is uncertain.Pull input / pull-down input / analog input: these concepts are well understood and can be easily understood from the literal.Multiplex open drain output and multiplex push-pull output: this can be understood as the configuration of the GPIO port when it is used as the second function (that is not used as a universal IO port)Finally, a summary of the use of the situation:Select IO mode in STM32(1) _IN_FLOATING - floating input floating input, can do KEY identification, RX1(2) pull input _IPU - IO internal pull-up resistor input(3) bring down the input _IPD - IO internal pull-down resistor input(4) analog input _AIN - use ADC analog input or save power at low power consumption(5) open drain output _OUT_OD - IO output 0, connect GND, IO output 1, suspension, need external pull-up resistor, can realize the output high level. When the output is 1, the state of the IO port is pulled high by the pull-up resistor, butbecause it is an open drain output mode, the IO port can also be changed from an external circuit to a low level or constant. Can read the IO input level changes, the realization of C51 IO two-way function(6) push-pull output _OUT_PP - IO output, 0-, GND, IO output, 1 - VCC, read input value is unknown(7) multiplex function push-pull output _AF_PP - chip internal and external functions (I2C, SCL, SDA)(8) the open drain output of multiplex function _AF_OD - chip internal and external functions (TX1, MOSI, MISO.SCK.SS)STM32 settings instance:(1) simulation using the I2C open drain output _OUT_OD, pull-up resistor, can output 0 and 1 readings; first GPIO_SetBits (GPIOB, GPIO_Pin_0); pull up, then you can read the value of IO; GPIO_ReadInputDataBit (GPIOB, GPIO_Pin_0);(2) if the supreme resistance is high, the IO default; need to read the value of IO, you can use the pull input _IPU and float input _IN_FLOATING and open drain output _OUT_OD;。

什么是开漏输出、推挽输出、开集输出、OC、OD、线或线与逻辑

开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。

TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。

它可以吸收很大的电流,但是不能向外输出电流。

所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。

OC门开漏输出和OD门开漏输出都是为了同一个目的,都是为了实现逻辑器件的线与逻辑,当然选用不同的外接电阻也可以实现外围驱动能力的增加。

当你应用此电路的时候,要注意应用时要加上拉电阻接电源,这样才能保证逻辑的正确,在电阻上要根据逻辑器件的扇入扇出系数来确定,但一般mos电路带载同样的mos电路能力比较强,所以电阻通常可以选择2.2k,4.9k这样一些常用的。

推挽输出与开漏输出的区别推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.要实现线与需要用OC(open collector)门电路.是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

推挽,开漏,强上拉,弱上拉,强下拉,弱下拉输出

详解开漏输出,推挽输出,上拉电阻

首先我们来建立开漏输出与推挽输出的模型吧!这两幅图是开漏输出的简化模型!推挽输出实际上应是把图三的电阻也换成一个开关(即场效应管),当上面开关接通,下面关断时,输出高电平;当上面开关关断,下面开关接通时,输出低电平;当二者都关断时,呈高阻态,此时可以输入信号。

当然不允许两者同时接通,所以才叫推挽,即同一时刻二者最多只能有一个工作。

为什么要有开漏输出?因为它有以下优点:1.利用外部电路的驱动能力,减少IC内部的驱动;2.可以将多个开漏输出的Pin,连接到一条线上。

形成“与逻辑” 关系。

如果是推挽输出显然是不行的,因为假如你把要”与”的I/O口都挂到一条线上,那么在一些高一些低的情况下显然会烧掉场效应管(原因是两个场效应管直接连通了,联想上面的模型去想吧)3.可以利用改变上拉电源的电压,改变传输电平。

比如你想这个I/O口输出3.3V 电平,那么只需要把上拉电平设为3.3V就OK了撒!这个5V的51单片机也可以输出3.3V电平了,呵呵!但前提是用P0口哈!那开漏输出又有什么不足的呢?1.输出电流低,因为上拉电阻一般取的比较大(为了减少静态功耗),所以驱动力不足,而推挽输出用的是场效应管,当然驱动能力强了.2. 带来上升沿的延时,因为上升沿是通过外接上拉无源电阻对负载充电的,当电阻选择小时延时就小、但功耗大,反之延时大功耗小。

推挽输出的优点:1.驱动能力强,因为用的是场效应管,当然驱动能力强了.2.真正的双向口推挽输出的缺点:1.不能把两个都是推挽输出的CMOS门级相连,这样当一高一低时很容易因功耗过大烧管子,推挽输出一般用于驱动.关于双向口与准双向口!什么是准双向口?首先我们要明白什么是双向口?双向口是指输入输出口具有三态,即输出高,输出低,和输入高阻态例如PO口作为地址/数据复用口时就是完全意义上的双向口,它的上下两个场效应管交替工作,当上面的场效应管工作时,输出1,当下面的场效应管工作时,输出0,当两个都不工作时,为高阻输入态.此时实际上就和推挽输出没有两样。

推挽、开漏、强上拉、弱上拉、强下拉、弱下拉输出

推挽、开漏、强上拉、弱上拉、强下拉、弱下拉输出[转]推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止开漏输出:输出端相当于三极管的集电极.要得到高电平状态需要上拉电阻才行.适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC(集电极开路)门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

什么是开漏输出、推挽输出、开集输出、OC、OD、线或线与逻辑

什么是开漏输出、推挽输出、开集输出、OC、OD、线或线与逻辑开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。

TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD 门,它的输出就叫做开漏输出。

它可以吸收很大的电流,但是不能向外输出电流。

所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。

OC门开漏输出和OD门开漏输出都是为了同一个目的,都是为了实现逻辑器件的线与逻辑,当然选用不同的外接电阻也可以实现外围驱动能力的增加。

当你应用此电路的时候,要注意应用时要加上拉电阻接电源,这样才能保证逻辑的正确,在电阻上要根据逻辑器件的扇入扇出系数来确定,但一般mos电路带载同样的mos电路能力比较强,所以电阻通常可以选择2.2k,4."9k这样一些常用的。

推挽输出与开漏输出的区别推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极.要得到高电平状态需要上拉电阻才行.适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.要实现线与需要用OC(open collector)门电路.是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:组成开漏形式的电路有以下几个特点:1.利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up,MOSFET到GND。

开漏(Open-Drain)和推挽(Push-Pull)输出

开漏(Open-Drain)和推挽(Push-Pull)输出推荐到论坛| 收藏漏级开路即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态,若需要产生高电平,则需使用外部上拉电阻或使用如LCX245等电平转换芯片。

有些朋友,尤其是未学过此方面知识的朋友,在实际工作中将I/O 口设置为漏开,并想输出高电平,但向口线上写1后对方并未认出高电平,但用万用表测量引脚确有电压,这种认为是不对的,对于高阻状态来说,测量电压是无意义的,正确的方法应是外加上拉电阻,上拉电阻的阻值=上拉电压/芯片引脚最大灌(拉)电流。

推挽方式可完全独立产生高低电平,推挽方式为低阻,这样,才能保证口线上不分走电压或分走极小的电压(可忽略),保证输出与电源相同的高电平,推挽适用于输出而不适用于输入,因为若对推挽(低阻)加高电平后,I=U/R,I会很大,将造成口的烧毁。

对与C8051F的很多型号片子,将I/O口设置为推挽方式的做法为:PnMDOUT=0xff,Pn=0x00,这样设置I/O口为推挽,并输出低电平(可降低功耗)将I/O口设置为漏开方式的做法为:PnMDOUT=0x00,Pn=0x11,这样设置I/O口为漏开。

如果学过三极管放大电路一定知道,前置单管放大器和功放末级放大电路的区别。

单片机内部的逻辑经过内部的逻辑运算后需要输出到外面,外面的器件可能需要较大的电流才能推动,因此在单片机的输出端口必须有一个驱动电路。

这种驱动电路有两种形式:其中的一种是采用一只N型三极管(npn或n沟道),以npn三极管为例,就是e接地,b接内部的逻辑运算,c 引出,b受内部驱动可以控制三极管是否导通但如果三极管的c极一直悬空,尽管b极上发生高低变化,c极上也不会有高低变化,因此在这种条件下必须在外部提供一个电阻,电阻的一端接c(引出脚)另一端接电源,这样当三极管的b有高电压是三极管导通,c电压为低,当b为低电压时三极管不通,c极在电阻的拉动下为高电压,这种驱动电路有个特点:低电压是三极管驱动的,高电压是电阻驱动的(上下不对称),三极管导通时的ec内阻很小,因此可以提供很大的电流,可以直接驱动led甚至继电器,但电阻的驱动是有限的,最大高电平输出电流=(vcc-Vh)/r;另一种是互补推挽输出,采用2只晶体管,一只在上一只在下,上面的一只是n型,下面为p型(以三极管为例),两只管子的连接为:npn(上)的c连vcc,pnp(下)的c接地,两只管子的ee,bb相连,其中ee作为输出(引出脚),bb接内部逻辑,这个电路通常用于功率放大点路的末级(音响),当bb接高电压时npn管导通输出高电压,由于三极管的ec电阻很小,因此输出的高电压有很强的驱动能力,当bb接低电压时npn截至,pnp导通,由于三极管的ec电阻很小因此输出的低电压有很强的驱动能力,简单的例子,9013导通时ec电阻不到10欧,以Vh=2.5v,vcc=5v计算,高电平输出电流最大=250MA,短路电流500ma,这个计算同时告诉我们采用推挽输出时一定要小心千万不要出现外部电路短路的可能,否则肯定烧毁芯片,特别是外部驱动三极管时别忘了在三极管的基极加限流电阻。

集电极开路输出、开漏输出、推挽输出

【电子大讲堂】集电极开路输出、开漏输出、推挽输出集电极开路(OC)输出:集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为"0"时,输出也为"0")。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V 电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图三。

图三中那个1K的电阻即是上拉电阻。

如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。

如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1K电阻上的压降也为0,所以输出端的电压就是5V了,这样就能输出高电平了。

但是这个输出的内阻是比较大的(即1KΩ),如果接一个电阻为R的负载,通过分压计算,就可以算得最后的输出电压为5*R/(R+1000)伏,即5/(1+1000/R)伏。

所以,如果要达到一定的电压的话,R就不能太小。

如果R真的太小,而导致输出电压不够的话,那我们只有通过减小那个1K的上拉电阻来增加驱动能力。

但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值,另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。

推挽、开漏、强上拉、弱上拉、强下拉、弱下拉输出

推挽、开漏、强上拉、弱上拉、强下拉、弱下拉输出推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).上拉电阻:1、当TTL电路驱动CMOS电路时,如果TTL电路输出的高电平低于CMOS 电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC(集电极开路)门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在CMOS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1. 驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

推挽输出与开漏输出结构和原理详解

推挽输出与开漏输出结构和原理详解推挽输出和开漏输出是指在数字电路中用于驱动外部负载的两种常用结构。

它们在控制信号的输出方式、应用领域和工作原理等方面有所不同。

下面将对推挽输出和开漏输出进行详解。

1.推挽输出结构及原理推挽输出结构是一种常用的数字电路输出结构,它由一个NPN型晶体管和一个PNP型晶体管组成,用于驱动负载。

推挽输出在广泛的应用领域中,如信号灯控制、音频放大器、电机驱动等。

推挽输出的结构示意图如下:```VccR1Input signal/,\NPN PNP Load_______```推挽输出的工作原理如下:(1) 当输入信号为低电平(0V)时,NPN晶体管截止,PNP晶体管饱和,输出接近Vcc电压,负载得到驱动。

(2) 当输入信号为高电平(Vcc)时,NPN晶体管饱和,PNP晶体管截止,输出接近0V,负载失去驱动。

推挽输出的特点:-输出电流能够提供相对较高的电流驱动能力;- 输出电压可以与Vcc相同,也可以与地(GND)相同;-推挽输出的集电极电阻很小,因此可以提供较低的输出电压误差;-适用于推挽驱动、电机驱动、音频放大器等需要提供大电流的应用场景。

2.开漏输出结构及原理开漏输出结构也是一种常用的数字电路输出结构,它通过NPN晶体管或MOSFET管驱动负载。

开漏输出结构广泛应用于数字IC、微控制器、I2C总线等。

开漏输出的结构示意图如下:```VccR1Input signal_____,______ LoadNPNN-MOS```开漏输出的工作原理如下:(1)当输入信号为低电平(0V)时,NPN晶体管截止或MOSFET导通,输出接近0V,负载得到驱动。

(2) 当输入信号为高电平(Vcc)时,NPN晶体管饱和或MOSFET截止,输出为高阻态(Open),负载失去驱动。

开漏输出的特点:-输出电流能够提供相对较高的电流驱动能力;-输出电压只能接近地(GND);-输出电压的高、低电平通过外部上拉电阻(R1)进行限制;-适用于非对称驱动、开关电源控制等需要较高的输出电流和开路状态的应用场景。

推挽、开漏、强上拉、弱上拉、强下拉、弱下

推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).上拉电阻:1、当TTL电路驱动COM S电路时,如果TTL电路输出的高电平低于C O MS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC(集电极开路)门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1. 驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

推挽输出和开漏输出详解

open-drain与push-pull】GPIO的功能,简单说就是可以根据自己的需要去配置为输入或输出。

但是在配置GPIO管脚的时候,常会见到两种模式:开漏(open-drain,漏极开路)和推挽(push-pull)。

对此两种模式,有何区别和联系,下面整理了一些资料,来详细解释一下:图表?1 Push-Pull对比Open-Drain常见的GPIO的模式可以配置为open-drain或push-pull,具体实现上,常为通过配置对应的寄存器的某些位来配置为open-drain 或是push-pull。

当我们通过CPU去设置那些GPIO的配置寄存器的某位(bit)的时候,其GPIO硬件IC内部的实现是,会去打开或关闭对应的top transistor。

相应地,如果设置为了open-d模式的话,是需要上拉电阻才能实现,也能够输出高电平的。

因此,如果硬件内部(internal)本身包含了对应的上拉电阻的话,此时会去关闭或打开对应的上拉电阻。

如果GPIO硬件IC内部没有对应的上拉电阻的话,那么你的硬件电路中,必须自己提供对应的外部(external)的上拉电阻。

而push-pull输出的优势是速度快,因为线路(line)是以两种方式驱动的。

而带了上拉电阻的线路,即使以最快的速度去提升电压,最快也要一个常量的R×C的时间。

其中R是电阻,C是寄生电容(parasitic capacitance),包括了pin脚的电容和板子的电容。

但是,push-pull相对的缺点是往往需要消耗更多的电流,即功耗相对大。

而open-drain所消耗的电流相对较小,由电阻R所限制,而R不能太小,因为当输出为低电平的时候,需要sink更低的transistor,这意味着更高的功耗。

(此段原文:because the lower transistor has to sink that current when the output is low; that means higher power consumption.)而open-drain的好处之一是,允许你cshort()多个open-drain的电路,公用一个上拉电阻,此种做法称为wired-OR连接,此时可以通过拉低任何一个IO的pin脚使得输出为低电平。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单片机I/O口推挽输出与开漏输出的区别

推挽输出:可以输出高,低电平,连接数字器件;

开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).

推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.

我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管集电极什幺都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为0时,输出也为0)。

对于图1,当左端的输入为0时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V

电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为1时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,1时断开,0时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那幺输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。