指令流水线设计

流水线设计实践报告总结

流水线设计实践报告总结引言流水线是一种有效的计算机硬件设计方法,通过将指令执行过程分成若干个流水级,每个流水级独立执行不同的任务,从而实现指令级并行。

在计算机体系结构设计中,流水线的应用被广泛研究和应用,大大提高了计算机的性能。

本报告主要总结了流水线设计实践过程中的经验和教训,以及对流水线设计的展望。

流水线设计实践经验选择合适的流水级划分流水线的性能取决于流水级的数量和粒度划分。

在流水线设计实践中,首先需要根据指令集和执行过程的特点,选择合适的流水级划分方式。

一般而言,流水级的划分越多,可以并行执行的指令数量越多,性能也就越高。

然而,过多的流水级也会导致流水线的延迟增加,因此需要根据具体应用场景进行取舍。

确保流水线各个阶段的平衡流水线各个阶段的执行时间应该尽量一致,以保持流水线的均衡性。

如果有某个阶段的执行时间远大于其他阶段,就会导致该阶段成为性能瓶颈,影响整个流水线的性能。

因此,在流水线设计过程中,要进行细致的性能分析和优化,尽量减少各个阶段的执行时间差异。

处理数据相关性和冒险流水线中经常会出现数据相关性和冒险问题,例如数据依赖、控制相关等。

这些问题会导致流水线的执行顺序被打乱,从而影响性能和正确性。

在流水线设计实践中,需要采取一些措施来处理这些问题,例如通过数据前推、分支预测等技术来解决数据相关性和冒险问题。

同时,还需要进行严格的验证和测试,确保流水线设计在各种情况下都能正确执行。

流水线设计中的教训不要过度依赖流水线并行性虽然流水线设计可以提高计算机的性能,但并不是所有任务都适合使用流水线并行。

在一些特殊情况下,流水线设计可能会导致性能损失,例如任务之间存在较高的依赖关系、任务的执行时间较短等。

因此,在流水线设计过程中,要充分考虑任务的特点和上下文,避免过度依赖流水线并行性。

考虑技术发展和应用需求的变化流水线设计是一个不断发展和演进的过程。

随着技术的进步和应用需求的变化,可能会出现新的挑战和机遇。

流水线设计

流水线设计1. 概述在计算机科学中,流水线是一种用于提高计算机性能的技术。

它将复杂的任务划分为一系列简单的子任务,并且在同时执行这些子任务的同时传递数据,从而实现更高的吞吐量和更短的响应时间。

本文将介绍流水线设计的基本原理和常见的应用。

我们将讨论流水线的架构、流水线的设计要点以及流水线中可能遇到的一些问题和解决方案。

2. 流水线的架构流水线的基本架构由以下几个组成部分组成:2.1. 输入单元输入单元负责接收外部输入并将其转换为计算机可以处理的格式。

它可以是键盘、鼠标、传感器等。

输入单元还可以包括解码器、缓冲区等组件,以提高数据传输的效率和稳定性。

2.2. 控制单元控制单元负责协调整个流水线中的各个组件的操作。

它根据指令和状态信息来决定下一步的操作,并将相应的指令发送给执行单元。

2.3. 执行单元执行单元是流水线中最重要的部分之一。

它负责执行任务的实际计算部分。

执行单元可以包括算术逻辑单元(ALU)、浮点运算单元(FPU)、乘法器、除法器等。

执行单元可以根据具体的需求进行扩展和优化。

2.4. 存储单元存储单元用于存储流水线中的数据和指令。

它可以是寄存器、缓存、内存等。

存储单元要具备高速访问和大容量的特性,以满足流水线的高效率要求。

2.5. 输出单元输出单元将计算结果输出给外部设备或其他计算机系统。

它可以是显示器、打印机、网络接口等。

输出单元还可以包括编码器、缓冲区等组件,以提高数据传输的效率和稳定性。

3. 流水线的设计要点在设计流水线时,我们需要考虑以下几个要点:3.1. 指令级并行流水线可以将任务划分为一系列子任务,并且在同时执行这些子任务的同时传递数据。

这种指令级并行可以提高计算机的性能。

在设计流水线时,我们需要合理划分子任务,并确保它们之间的依赖关系正确处理。

3.2. 数据冲突在流水线中,由于子任务之间的数据传递,可能会出现数据冲突的情况。

数据冲突会导致流水线的停顿和性能损失。

为了解决数据冲突,我们需要采取一些技术手段,如使用缓存、乱序执行、数据旁路等。

基于MIPS指令集的流水线CPU设计与实现

基于MIPS指令集的流水线CPU设计与实现刘秋菊;张光照;王仲英【摘要】提出了一种CPU设计方案,实现指令集为MIPS指令集中选取15条指令作为本CPU的基本指令,采用基本5步流水线CPU设计.分析了流水线CPU的逻辑结构与指令的处理过程,给出了取指阶段IF、译码阶段ID、执行阶段EX、内存访问阶段MEM、寄存器写回阶段WB阶段的设计与实现.对流水线产生的相关性问题,采用Bubble法和Forwarding法相结合的方法来消除相关性,在FPGA平台上进行了测试,测试结果表明,该方案符合设计要求.%In this paper,a design method of CPU was proposed,the instruction set of the CPU contained 15 items of MIPS instruction set,and the basic method of five step pipeline CPU design was used.Analyses were conducted on the logic structure of the pipeline CPU and the processing of the instruction.This paper also gave design and realization of stage IF,stage ID,stage EX,stage MEM and stage WB.About the pipeline-related problems,the paper adopted Bubble and Forwarding technologies to eliminate it.The tests on the FPGA platform show that the scheme meets the design requirements.【期刊名称】《实验室研究与探索》【年(卷),期】2017(036)008【总页数】6页(P148-152,172)【关键词】流水线;中央处理器;设计;指令集【作者】刘秋菊;张光照;王仲英【作者单位】郑州工程技术学院信息工程学院,郑州450000;河南经贸职业学院技术科学系,郑州450018;河南经贸职业学院技术科学系,郑州450018【正文语种】中文【中图分类】TP332在工业设计和机器人研究中,微处理器作为控制部件的核心是设计的关键,其性能直接影响整个系统的性能。

指令流水实验报告

实验目的:本次实验旨在通过指令流水技术,提高CPU的指令执行效率,减少指令执行时间,并加深对指令流水线工作原理的理解。

实验环境:1. 操作系统:Windows 102. 编译器:GCC3. 指令集:x864. CPU:Intel Core i5-8265U实验内容:1. 设计一个简单的指令序列,包含加法、减法、乘法和除法等指令。

2. 使用指令流水技术,对指令序列进行优化,提高指令执行效率。

3. 对比优化前后的指令执行时间,分析指令流水技术的效果。

实验步骤:1. 编写实验程序,实现指令序列的执行。

2. 编译实验程序,生成可执行文件。

3. 使用计时工具,记录指令序列执行前后的时间。

4. 分析实验结果,总结指令流水技术的效果。

实验程序代码:```c#include <stdio.h>#include <time.h>int main() {int a = 10, b = 5, c = 0, d = 0;clock_t start, end;double cpu_time_used;// 优化前start = clock();c = a + b;d = a - b;c = c b;d = d / b;end = clock();cpu_time_used = ((double) (end - start)) / CLOCKS_PER_SEC; printf("优化前执行时间:%f 秒\n", cpu_time_used);// 优化后(使用指令流水技术)start = clock();c = a + b;d = a - b;c = c b;d = d / b;end = clock();cpu_time_used = ((double) (end - start)) / CLOCKS_PER_SEC; printf("优化后执行时间:%f 秒\n", cpu_time_used);return 0;}```实验结果分析:通过对比优化前后的指令执行时间,可以看出指令流水技术能够有效提高指令执行效率。

MIPS指令五级流水CPU设计资料

0

0

PCSrc

31:26 5:0

CLK A1 A2 A3

1 WE3 RD1 1 RD2 0 1 0 0 WriteReg4:0 1 SrcA

CLK 010 Zero ALUResult A

0 WE 1 ReadData 0 1

ALU

Instruction Memory

20:16

SrcB

Register WD3 File

指令预取

取指令 3 执行指令 3

若 取指 和 执行 阶段时间上 完全重叠 指令周期 减半 速度提高 1 倍

时间?

二、 流水线操作时空图

空间 执行操作 取数操作 分析指令 1 I 2 2 3 3 4 4 5 5 6 6 7 7

1

1

2

2

3

3

4

4

5

5

6

6

7

7

取指令 1 2 3 4 5 6 7 T0 T1 T2 T3 T4 T5 T6 装入阶段 稳定流水阶段

2. 数据相关

不同指令因重叠操作,可能改变操作数的 读/写 访问顺序 • 写后读相关(RAW) SUB R1,R2,R3 ;(R2) (R3) ;(R5)+(R1) ;(R2) R1 R4 ADD R4,R5,R1 • 读后写相关(WAR) STA M,R2 ADD R2,R4,R5 M 存储单元 R2 R3 R3 ;(R4)+(R5) ;(R2)× (R1) ;(R4) (R5)

4.5 MIPS指令五级流水CPU设计

4.5.1 多周期CPU回顾 4.5.2 指令流水基本概念 4.5.3 MIPS指令流水的实现

4.5.1 多周期CPU回顾

多周期CPU特点 – 指令的执行划分为多个步骤 – 每个步骤占用一个CPU周期 – 不同指令的指令周期不同 – 指令串行执行

冯诺依曼原理的应用

冯诺依曼原理的应用1. 什么是冯诺依曼原理冯·诺依曼原理(通常称为冯诺依曼体系或冯洛伊曼结构)指的是计算机中用于处理指令和数据的基本原则和方法。

它由冯·诺依曼于1945年提出,是现代计算机设计的基石,被广泛应用于各种计算机系统中。

2. 冯诺依曼原理的要点冯诺依曼原理主要包括以下要点:2.1 存储程序冯诺依曼原理将程序指令和数据存储在同一个存储器中,程序可以按照一定的顺序被执行。

这种存储程序的设计方式,为计算机的灵活性和可编程性提供了基础。

2.2 指令流水线冯诺依曼原理鼓励将计算机的处理过程划分为多个阶段,并使每个阶段的工作可以同时进行,以提高计算机的效率。

这种流水线的方式可以将计算机的处理能力最大化,提高计算机的运行速度。

2.3 存储器系统冯诺依曼原理提倡使用存储器来存储指令和数据,并采用统一的存储器系统来管理这些存储器。

这种设计可以使计算机的存储器资源得到合理利用,并方便进行存储器的扩展。

2.4 控制单元和算术逻辑单元冯诺依曼原理将计算机的处理过程分为控制和运算两部分,分别由控制单元和算术逻辑单元来完成。

控制单元用于管理程序的执行和数据的传输,而算术逻辑单元用于进行数据的计算和逻辑运算。

3. 冯诺依曼原理的应用冯诺依曼原理在计算机领域的应用非常广泛,以下列举了几个典型的应用场景:3.1 通用计算机系统冯诺依曼原理是现代通用计算机设计的基础,绝大部分的计算机系统都采用了冯诺依曼原理。

这种设计方式使得计算机具有很高的灵活性和可编程性,可以用于执行各种不同类型的计算任务。

3.2 控制系统冯诺依曼原理的指令流水线设计思想被广泛应用于控制系统中。

控制系统需要处理大量的输入和输出数据,并进行实时的决策和控制。

冯诺依曼原理的流水线设计可以提高控制系统的响应速度和处理能力。

3.3 数字信号处理冯诺依曼原理的存储器系统对于数字信号处理非常重要。

数字信号处理需要大量的数据存储和高效的数据处理能力,冯诺依曼原理的存储器系统可以满足这一需求,并且通过流水线设计可以提高处理效率。

mcu流水线概念

流水线是现代RISC核心的一个重要设计,它极大地提高了性能。

对于一条具体的指令执行过程,通常可以分为五个部分:取指令,指令译码,取操作数,运算(ALU),写结果。

其中前三步一般由指令控制器完成,后两步则由运算器完成。

按照传统的方式,所有指令顺序执行,那么先是指令控制器工作,完成第一条指令的前三步,然后运算器工作,完成后两步,在指令控制器工作,完成第二条指令的前三步,在是运算器,完成第二条指令的后两部……很明显,当指令控制器工作时运算器基本上在休息,而当运算器在工作时指令控制器却在休息,造成了相当大的资源浪费。

解决方法很容易想到,当指令控制器完成了第一条指令的前三步后,直接开始第二条指令的操作,运算单元也是。

这样就形成了流水线系统,这是一条2级流水线。

如果是一个超标量系统,假设有三个指令控制单元和两个运算单元,那么就可以在完成了第一条指令的取址工作后直接开始第二条指令的取址,这时第一条指令在进行译码,然后第三条指令取址,第二条指令译码,第一条指令取操作数……这样就是一个5级流水线。

很显然,5级流水线的平均理论速度是不用流水线的4倍。

流水线系统最大限度地利用了CPU资源,使每个部件在每个时钟周期都工作,大大提高了效率。

但是,流水线有两个非常大的问题:相关和转移。

在一个流水线系统中,如果第二条指令需要用到第一条指令的结果,这种情况叫做相关。

以上面哪个5级流水线为例,当第二条指令需要取操作数时,第一条指令的运算还没有完成,如果这时第二条指令就去取操作数,就会得到错误的结果。

所以,这时整条流水线不得不停顿下来,等待第一条指令的完成。

这是很讨厌的问题,特别是对于比较长的流水线,比如20级,这种停顿通常要损失十几个时钟周期。

目前解决这个问题的方法是乱序执行。

乱序执行的原理是在两条相关指令中插入不相关的指令,使整条流水线顺畅。

比如上面的例子中,开始执行第一条指令后直接开始执行第三条指令(假设第三条指令不相关),然后才开始执行第二条指令,这样当第二条指令需要取操作数时第一条指令刚好完成,而且第三条指令也快要完成了,整条流水线不会停顿。

数字系统设计-流水线CPU设计

实验报告课程名称:数字系统设计实验Ⅱ学院:信电系数字系统设计实验Ⅱ流水线MIPS微处理器设计ContentsPart 1实验目的 (3)Part 2实验任务 (3)Part 3实验原理 (4)Part 4实验步骤 (12)1.IF级设计 (12)2.ID级设计 (14)3.Decode单元设计 (16)4.ALU单元设计 (22)5.EX级设计 (27)6.顶层模块设计 (29)Part 5仿真和波形分析 (37)1.IF级仿真分析 (37)2.Decode单元仿真分析 (38)3.ALU仿真分析 (40)4.顶层仿真分析 (41)Part 6心得 (42)实验报告一、实验目的(1)了解提高CPU性能的方法。

(2)理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

(3)掌握流水线MIPS微处理器的工作原理。

(4)掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器。

设计要求:(1)至少执行下列MIPS32指令。

①算数运算指令:ADD ADDU SUB SUBU ADDI ADDU②逻辑运算指令:AND OR NOR XOR ANDI ORI XORI SLT SLTI SLTU SLTIU③移位指令:SLL SLLV SRL SRLV SRA④条件分支指令:BEQ BNE BGEZ BGTZ BLEZ BLTZ⑤无条件跳转指令:J JR⑥数据传输指令:LW SW⑦空指令:NOP(2)在用5级流水线技术,对数据冒险实现转发或阻塞功能。

(3)在XUP Vietex-II Pro开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz.三、实验原理1.流水线MIPS CPU总体设计与构建流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用在高档CPU的构建中。

根据MIPS处理器指令的特点,将整体的处理过程分为取指令(IF)、指令译码、执行、存储器访问和寄存器写回五级,对应多周期CPU的五个处理阶段。

MIPS指令五级流水CPU设计剖析

MIPS指令五级流水CPU设计剖析MIPS指令五级流水将指令的执行过程划分为取指(Instruction Fetch, IF)、译码(Instruction Decode, ID)、执行(Execution, EX)、访存(Memory Access, MEM)和写回(Write Back, WB)五个阶段。

每个阶段由一个独立的硬件逻辑电路实现,这样指令可以在同一时间在不同阶段同时执行,从而提高了CPU的吞吐量。

在取指阶段,CPU从指令缓存(Instruction Cache)中读取指令,并将其送入指令译码阶段。

取指阶段主要包括以下几个步骤:首先,CPU从PC寄存器中读取下一条指令的地址;然后,CPU将这个地址发送到指令缓存中,读取对应的指令;最后,CPU将读取到的指令送入译码阶段。

在译码阶段,CPU对指令进行译码,确定指令的类型和操作数,并将这些信息传递给执行阶段。

译码阶段主要包括以下几个步骤:首先,CPU从指令中解析出操作码和操作数;然后,CPU根据操作码确定指令的类型,并确定需要使用的操作数;最后,CPU将指令类型和操作数传递给执行阶段。

在执行阶段,CPU执行指令的实际操作,并计算结果。

执行阶段主要包括以下几个步骤:首先,CPU根据指令类型和操作数进行相应的运算;然后,CPU将计算结果传递给访存阶段或写回阶段,具体传递给哪个阶段取决于指令的类型;最后,CPU将执行完成的指令从流水线中清除。

在访存阶段,CPU将数据存储到内存或从内存中读取数据,并将数据传递给下一个阶段。

访存阶段主要包括以下几个步骤:首先,CPU将执行阶段产生的数据存储到内存;然后,CPU从内存中读取数据;最后,CPU将读取到的数据传递给写回阶段或下一个指令的取指阶段。

在写回阶段,CPU将执行阶段产生的结果写回到寄存器文件(Register File)中,以保存计算结果。

写回阶段主要包括以下几个步骤:首先,CPU将执行阶段产生的结果写入寄存器文件;然后,CPU更新PC寄存器的值,以指向下一条需要执行的指令;最后,CPU将流水线上所有已经执行完成的指令清除。

第六章 指令流水线

Instruction Memory Instruction

应保存后面阶段用到的 指令和PC+4的值!

指令在随后阶段被送出译码! PC+4用来计算转移目标地址

不需控制信号,因为每条指令执行功能一样,是确定 的,无需根据指令的不同来控制执行不同的操作!

译码/取数(Reg/Dec)阶段

Clk

° Location 10: lw $1, 0x100($2 ) You are here! 能:$1 <- Mem[($2) + 0x100]

Ifetch Reg/Dec RegWr

1 0

功

Mem Branch

Exec ExtOp ALUOp

PC+4 Imm Rs Ra Rb Rt RFile Rt Rw Di Rd

PC+4 Imm busA bus Exec B Unit

0 1

RegWr 是Wr段 的信号

Mem/Wr Register Ex/Mem Register Zero Data Mem RADo WA Di

ID/Ex Register

Store指令呢?

RegDes=x, ALUSrc=1 ALUop=addu, Extop=1

0 Mux

Branch指令呢?

RegDes=x, ALUSrc=0 ALUop=subu, Extop=1

Extender

imm 16

32 ExtOp=?

1

Ori指令呢?

RegDes=0, ALUSrc=1 ALUop=or, Extop=0

°Exec:16位立即数符号扩展后与寄存器值相加,计算主存地址 °Mem:将寄存器读出的数据写到主存 • Wr: 加一个空的写阶段,使流水线更规整!

冯诺依曼计算机工作原理的设计思想

冯诺依曼计算机工作原理的设计思想

冯诺依曼计算机工作原理的设计思想是基于存储程序的概念。

其主要特点包括以下几点:

1. 存储程序:冯诺依曼计算机将程序和数据以相同的方式存储在计算机的内存中。

程序中的指令和数据都被存储在存储器中的不同地址上,可以被按需读取和写入。

2. 指令流水线:冯诺依曼计算机借鉴了装配线工作方式,引入指令流水线的概念。

指令流水线将指令的执行过程分为多个步骤,并使得多条指令可以并行执行,提高了计算机的效率。

3. 控制单元和运算器的分离:冯诺依曼计算机将计算机的功能分为控制单元和运算器。

控制单元负责从内存中读取指令并解析执行流程,而运算器则负责执行实际计算操作。

4. 寄存器:冯诺依曼计算机引入了寄存器的概念,用于临时存储数据和指令。

寄存器的使用可以提高计算速度,并减少对内存的访问。

5. 存储器的层次结构:冯诺依曼计算机采用了存储器的层次结构,分为高速缓存、主存和辅助存储器。

不同层次的存储器具有不同的速度和容量,可以根据需求进行数据的存取。

6. 数据和指令的二进制表示:冯诺依曼计算机使用二进制来表示数据和指令。

所有的数据和指令在计算机内部都以二进制的形式进行处理和存储。

7. 硬件和软件的分离:冯诺依曼计算机将硬件和软件分离,使得计算机的功能可以通过更改软件来实现,而不需要对硬件进行改动。

冯诺依曼计算机的设计思想在现代计算机中得到了广泛的应用,成为计算机结构设计的基础。

通过存储程序的概念,指令流水线的引入等方法,可以提高计算机的运行效率和性能,同时也方便了软件的开发和维护。

计算机体系结构实训课程学习总结指令级并行与流水线设计

计算机体系结构实训课程学习总结指令级并行与流水线设计在计算机科学与技术领域中,计算机体系结构是一门关于计算机硬件与软件的核心学科。

在我修习的计算机体系结构实训课程中,我学习了指令级并行与流水线设计,掌握了该领域的核心概念与技术,下面是我对该课程的学习总结和心得体会。

一、指令级并行概述指令级并行是指在一个周期内同时执行多条指令,以减少指令的执行时间,提高计算机的性能。

在学习指令级并行的过程中,我了解了计算机指令的基本原理及其执行过程。

通过学习指令流水线、数据前推、乱序执行等技术,我深入理解了指令级并行的优势和实现方法。

在实训过程中,我通过搭建指令级并行的实验平台,进行了仿真实验和性能分析。

通过比较顺序执行和指令级并行执行的效果,我发现指令级并行可以大幅度提高计算机的执行效率。

而在实现指令级并行时,我也面临了一些挑战,如数据相关、控制相关等问题,但通过优化代码和调整指令执行顺序,我成功地解决了这些问题。

这个过程让我深刻体会到指令级并行设计的重要性和技术难点。

二、流水线设计与优化流水线设计是指将计算机指令的执行过程划分为多个阶段,并使不同阶段的指令并行执行,从而提高计算机的吞吐量。

在学习流水线设计的过程中,我深入了解了流水线的原理、特点和结构。

通过学习流水线的组织方式、数据冒险、控制冒险等问题,我掌握了流水线设计的关键技术。

在实验中,我设计了一个基于流水线的简单计算机,并通过编写适当的指令集和流水线寄存器,实现了流水线的功能。

通过性能测试,我发现流水线设计可以显著提高计算机的执行效率和吞吐量。

然而,我也发现了一些流水线设计中的问题,比如分支预测错误、资源冲突等,这些问题对流水线的性能产生了负面影响。

通过调整分支预测策略和添加冲突检测机制,我成功地进行了优化,提高了流水线设计的性能。

三、实训过程中的收获与反思通过学习指令级并行与流水线设计,我不仅极大地提高了对计算机体系结构的理解和掌握,还培养了解决实际问题的能力。

第7章流水线结构RISC CPU设计

(7-4)

7.3流水线的性能评价

7.3.1 流水线的性能指标

2.CPU性能公式

总时钟周期数 CPU时间 时钟频率

(7-5)

总时钟周期数 CPI (7-6) IC

CPU时间

(CPI

i 1

n

CPI IC (7-7) 总CPU时间 时钟频率

(7-8)

i

ICi )

时钟频率

CPI

7.1.2流水线CPU的时空图

空间S

I 1 I 2I 3I 4I 5 I 6 I 7 I 8I 9 I 10

空间S

WB EX ID IF

I3 I4 I5 I1 I2 I3 I4 I5 I1 I2 I3 I4 I5 I1 I2 I3 I4 I5 I1 I2 I3 I4 I5 1 2 3 4 5 6 7 8 时间T

Reg

图7-10 例7-4的流水线状态图

ALU

7.2 流水线中的主要问题及处理 CC1 CC2 CC3 CC4 CC5

时钟周期

CC6

ALU

程 序 Reg 执 LW R1,0(R2) IM 7.2.3 数据竞争的处理技术 行 序 列 SUB R4,R1,R5 IM

ALU

DM

Reg

Reg

气泡

DM

AND R6,R1,R7

Reg

ALU

程 序 Reg 执 ADD R1,R2,R3 IM 行 序 列 7.2.3 数据竞争的处理技术 SUB R4,R1,R5 IM

ALU

7.2 流水线中的主要问题及处理

DM Reg DM

时钟周期

CC1

CC2

CC3

CC4

CC5

CC6

pipeline原理

pipeline原理

Pipeline(管道)是一种计算机科学中常见的概念,它通常用于描述一系列处理单元(或阶段)按顺序连接起来,以便完成特定任务或处理数据流。

在计算机科学和工程中,管道的概念被广泛应用于多个领域,包括操作系统、编程语言、软件工程等。

在计算机体系结构中,Pipeline通常用于描述指令流水线。

指令流水线是一种处理器设计技术,通过将指令执行过程分解为多个阶段,并使每个阶段同时执行不同指令的部分,以提高处理器的吞吐量和性能。

典型的流水线包括取指、译码、执行、访存和写回等阶段,每个阶段负责处理指令执行过程中的不同部分。

这种流水线设计可以使处理器在同一时刻执行多条指令,从而提高指令的处理速度。

在软件工程中,Pipeline常用于描述持续集成和持续交付

(CI/CD)流程。

持续集成是指开发人员频繁地将代码集成到共享存储库中,并通过自动化构建和测试流程来验证新代码的正确性。

持续交付是指将经过测试和验证的代码自动部署到生产环境中。

Pipeline在这里通常指代一系列自动化的步骤,包括代码检查、编译、单元测试、集成测试、部署等,这些步骤按顺序连接起来,形

成一个自动化的流程,以确保代码的质量和稳定性。

总的来说,Pipeline是一种将多个处理单元按顺序连接起来的

概念,它在计算机体系结构、软件工程等领域都有重要的应用。

通

过合理设计和使用Pipeline,可以提高系统的性能、可靠性和效率。

指令系统的设计原理

指令系统的设计原理

指令系统的设计原理主要包括以下几点:

1. 指令集设计:指令集是计算机通过操作码进行操作的一组指令集合。

在设计指令集时,要考虑到计算机的性能、资源使用效率、指令的多样性和易用性等因素。

常见的指令集包括精简指令集(RISC)和复杂指令集(CISC)。

2. 指令格式设计:指令格式指的是指令的布局和组织方式。

通常包括操作码、寄存器地址、内存地址和立即数等字段。

指令格式的设计要尽可能简洁明了,在满足操作需求的同时,尽量减少指令的长度,以提高指令的执行效率。

3. 寻址方式设计:寻址方式指的是指令中操作数的读写方式。

常见的寻址方式有立即寻址、直接寻址、间接寻址和相对寻址等。

寻址方式的选择要根据计算机的结构、内存管理和数据传输等因素进行合理的设计。

4. 流水线设计:流水线是指将指令执行过程划分为多个阶段,并在不同阶段同时执行不同指令的技术。

流水线设计可以提高计算机的运行效率。

在设计流水线时,需要考虑指令之间的依赖关系、资源冲突和指令流程等因素。

5. 排队调度算法设计:排队调度算法用于确定指令的执行顺序和资源分配,以提高计算机的并发性和效率。

常见的调度算法有先来先服务(FCFS)、最短作业优先(SJF)和时间片轮转等。

调度算法的设计要根据应用场景、任务性质和系

统资源等因素进行综合考虑。

通过合理的指令系统设计,可以提高计算机的执行效率、并发性和资源利用率,提高计算机的性能和可靠性。

复杂指令集流水线系统设计

复杂指令集流水线系统设计

靳文兵;左琦

【期刊名称】《微电子学与计算机》

【年(卷),期】2012(29)4

【摘要】摒弃传统流水线设计必须先将复杂指令集指令转化为精简指令集指令,然后再按照精简指令集实现流水线的方法.采用拓展的哈佛结构,设计新型指令流水线前端多指令缓冲和双指令指针,以及流水线中、后端双总线寄存器组和多端口数据存储器,优化指令流水线结构,实现高效率的复杂指令集指令流水线系统.设计从理论上解决了复杂指令集流水线实现的两个难点:寄存器和存储器读写冲突问题,以及流水线各阶段功能和任务划分.VHDL语言建模,用ModelSim和Xilinx仿真、测试,证明复杂指令集流水线系统设计可行.

【总页数】4页(P19-22)

【关键词】微处理器;复杂指令集;流水线;多端口存储器;读写冲突

【作者】靳文兵;左琦

【作者单位】北京理工大学计算机学院;北方自动控制技术研究所

【正文语种】中文

【中图分类】TP32

【相关文献】

1.电能表用外置断路器检测流水线输送系统设计 [J], 纪伊琳;黄友朋;路韬

2.流水线自动抓送料机械手控制系统设计 [J], 杨云鹏

3.新一代智能电能表自动化检定流水线系统设计 [J], 倪胡旋;丁隽洁;王媛;刘岑岑;李艳

4.蔬菜育苗播种流水线压穴滚筒装置改进与控制系统设计 [J], 孙晗;郭广川;唐帅;薛金林;林相泽;李群

5.气振盘式精密播种三段式流水线控制系统设计与试验 [J], 韦运余;陈进;杨铭;练毅;乔祥山

因版权原因,仅展示原文概要,查看原文内容请购买。

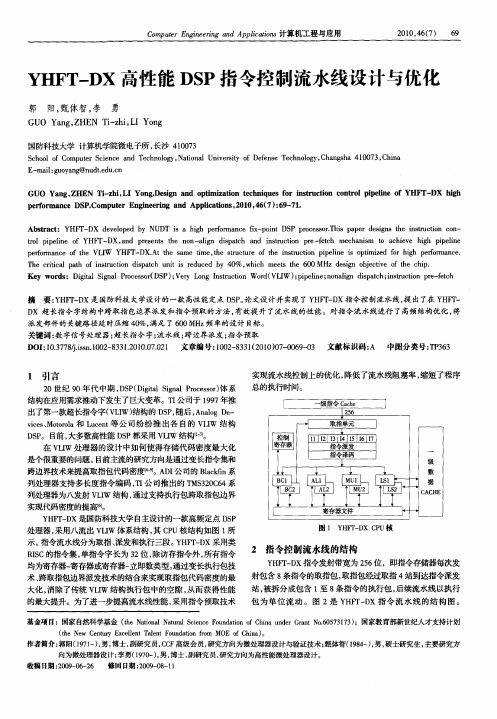

YHFT-DX高性能DSP指令控制流水线设计与优化

国防科技大学 计算机学院微 电子所 , 长沙 4 07 10 3

S h o f C mp tr S in e a d T c n lg , t n l Unv r i f n e T c n l g , a g h 1 0 3 Chn c o l o o ue ce c n e h oo y Na i a i est o Dee s e h oo Ch n s a 4 0 7 , i a o yf y E- i: u y n @n d .d .n mal g o a g u t u c e

GUO n ZHE Ti z i LI Yo g De i n a d o t z t n t c n q e o n t u t n c n r l p p l e o Ya g, N - h , n . sg n p mi a o e h i u s f r i sr c i o t o i ei f YHF DX i h i i o n T— hg

C m u rE  ̄ne n n p l a os o p t n en g a dA pi t n 计算机工程 与应用 e ci

2 1 ,6 7 0 04 ( )

6 9

Y TD HF — X高性 能 D P指令控制流水线设计 与优化 S

郭 阳, 甄体 智 , 李 勇

GU Y n , HE i z i L n O a g Z N T — h , I Yo g

:P 6 T33

1 引言

2 世纪 9 0 0年代 中期 , S ( it in rcso) 系 D P Dg a Sga Poesr体 i l l 结构在应用需求推动下发生了巨大变革 。 I 司于 19 年推 T公 97 出了第一款超长指令字 ( L 结构的 D P 随后 ,n o D — V1 w) S, A a g e l v e、 trl L cn 等公 司纷 纷 推 出各 自的 v i sMo o a和 u et c o uw 结 构

MIPS指令五级流水CPU设计资料

MIPS指令五级流水CPU设计资料1.指令和指令流水线MIPS指令集包含大约50条指令,包括算术/逻辑操作、存储器操作、分支和跳转等。

五级流水线是一种用于加速指令处理的技术,将指令执行过程划分为五个阶段:取指(Instruction Fetch, IF)、译码(Instruction Decode, ID)、执行(Execution, EX)、访存(Memory Access, MEM)和写回(Write Back, WB)。

2.数据通路和控制信号3.流水线冲突在流水线处理器中,常见的冲突有结构冲突、数据冲突和控制冲突。

结构冲突是由于多个指令需要同时访问同一个硬件资源而引起的,例如两个指令同时需要访问寄存器堆。

数据冲突是由于指令之间存在依赖关系而引起的,例如一条指令需要使用前一条指令的结果作为操作数。

控制冲突是由于分支指令的执行导致流水线中的指令不按顺序执行。

4.冲突解决技术为了解决流水线冲突,可以采用以下技术:延迟槽、旁路、分支预测和动态调度。

延迟槽是将分支指令后面的一条指令当作分支指令的一部分,使得分支指令的下一条指令能够在分支决策前执行。

旁路技术用于解决数据冲突,将计算结果旁路给后续指令使用。

分支预测技术用于解决控制冲突,根据过去的分支历史进行预测。

动态调度技术则根据指令的真实执行情况来进行调度,以最大程度地减少冲突。

5.性能优化为了提高CPU的性能,可以采取一些优化技术,例如流水线分段、超标量和超流水线。

流水线分段将指令流水线划分为多个段,使得每个段可以并行工作,提高指令的吞吐量。

超标量技术引入多个功能单元来同时执行多条指令,提高指令的并行度。

超流水线技术则进一步增加流水线的级数,以提高指令的处理速度。

总结:MIPS指令五级流水线CPU是一种高效的处理器设计,它采用五级流水线来加速指令处理,并通过解决流水线冲突来提高指令执行的效率。

该CPU的设计需要考虑数据通路和控制信号,以及解决冲突的技术和性能优化的方法。

基于DLX指令集的5级流水线CPU设计与实现

基于DLX指令集的5级流水线CPU设计与实现一、渊源 (1)二、基础 (2)1、从系统角度和程序执行角度体会CPU概貌 (2)2、CPU设计的重点:指令集和流水线,指令集就是协议 (3)3、流水线—20世纪最伟大的发明 (10)4、流水线带来的烦恼—相关 (16)5、流水线结构的颠覆:记分牌与tomasulo算法(与设计无关) (21)三、设计与实现 (26)一、渊源诞生于1977年的英特尔8086以现在微电子专业本科生的水平完全可以做出来,龙芯的负责人胡伟武的毕业设计作品就是8086CPU。

我们学过的大三的时候看了《编码》后觉得比较有感觉就写了一篇文章叫作《从零开始构建一台计算机》,主要说了一下对编码思想的理解,只记得当时心情相当激动,好像二进制世界刚刚向我打开。

很重要的一部分是以自己的理解说了一下CPU与接口的相互作用关系,这是因为那时与单片机正打得火热。

当时对于CPU的理解几乎为零,所以一笔带过了CPU的构造与工作原理,骗自己说那是非常复杂的东西,一直把它奉作系统大脑,却从不知道它到底是什么。

但对CPU原理的理解对于写出高效的程序是很关键的。

上个学期,一个“神童”级的人物出现了,王超。

这个感觉还不如我们年龄大的科大博士后,教我们《现代微处理器体系结构》,不得不说收获很大,对如何设计、实现、测试、分析、评估、优化一个CPU有了比较清晰的认识。

考试完之后一直想整理整理,一直懒得动,这项任务像一块石头一样堵在心口,现在我想好好写写,作为上个学期的真正结束。

基础部分主要是之前课上课下的的笔记,实现部分主要是实验室老大单麾扬的杰作,他用了两天时间在modelsim下用verlog语言编写了整个工程,这个西工大的哥哥,真是各种令人折服。

二、基础1、从系统角度和程序执行角度体会CPU概貌我们沿用至今的冯诺依曼提出的计算机系统硬件结构:运算器、控制器、存储器、输入设备、输出设备。

其中运算器和控制器从功能角度来说就是中央处理单元CPU。

项目四PLC功能指令应用任务二装配流水线控制

包括传感器、开关、按钮等,用于检测流水 线各工位的运行状态和操作指令。

PLC控制器

作为核心控制单元,负责接收输入信号、处 理逻辑运算和发出控制指令。

输出设备

如电机、气缸、电磁阀等,用于控制流水线 的动作和执行相关操作。

通讯模块

实现PLC与上位机或其他设备之间的数据交 换和通信。

软件设计

控制算法 I/O配置 控制程序编写 人机界面设计

,便于后期维护和升级。

05

PLC功能指令应用在装配 流水线控制中的案例分 析

案例一

总结词

顺序控制指令在装配流水线控制中起到关键作用,能够实现按照预设顺序自动控制设备的启停,提高 生产效率。

详细描述

通过使用顺序控制指令,PLC能够按照预设的逻辑顺序,自动控制装配流水线上的设备启停,实现自 动化生产。这种控制方式能够大大提高生产效率,减少人工干预,降低生产成本。

计数器指令的应用

计数器指令用于对装配流水线上的工件进行计数,并控制流 水线的运行速度和节奏。通过设置计数器的初始值和触发条 件,PLC能够精确地控制流水线的运行次数和间隔。

计数器指令的应用可以与顺序控制指令结合使用,实现更复 杂的动作序列和逻辑控制。

移位指令的应用

移位指令用于控制装配流水线上的工 件在生产线上的位置移动。通过将工 件从一个位置移到另一个位置,实现 工件的组装、检测和包装等操作。

THANKS FOR WATCHING

感谢您的观看

提高企业竞争力

装配流水线控制能够提高 企业的生产效率和产品质 量,增强企业的市场竞争 力。

装配流水线控制的历史与发展

历史

装配流水线控制起源于20世纪初的 美国汽车工业,后来逐渐推广到其他 制造业领域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

五级流水线指令执行过程

• 取指级(IF):从存储器取指令,每个周期取出一条指令。PC加4 取指级( ) 从存储器取指令,每个周期取出一条指令。PC加 • 译码级(DE):译出所要执行的指令的功能并识别出所需的资源,这 译码级( ) 译出所要执行的指令的功能并识别出所需的资源, 些资源包括通用寄存器、总线和功能部件,提供流水线控制互锁, 些资源包括通用寄存器、总线和功能部件,提供流水线控制互锁,并 从寄存器读出操作数。 从寄存器读出操作数。 • 执行级(EX):完成指令功能。 执行级( ) 完成指令功能。 • 存储器访问(MEM):完成LOAD/STORE访问。 存储器访问(MEM) 完成LOAD/STORE访问。 LOAD/STORE访问 • 写回级(WB):用来将结果或存储器读出的数据写入寄存器。 写回级( ) 用来将结果或存储器读出的数据写入寄存器。

取指

00000000

5BFF_C000

译码

00000001

执行

00000002

写回

00000002

5BFF_C001

5BFF_C000

5BFF_C001

5BFF_C001

IR

Src译码 RF读 ALU执行 Dst译码 RF写

ALU控制译码 Dst域保存

地址输出 取指 PC +4 选择

数据输出

数据输入

ERA[i] Cbus[i] EWR[i] CLK ERB[i] DFF Bbus[i] Abus[i]

寄存器组

C总线 R0 R1

ERAi ERBi EWRi src1 ERA0 ERB0 EWR0

IR

dst Rdst src2

寄存 器译 码逻 辑

R31

A总线 B总线

寄存器组

clk AB[31:2] DB[31:0] rd IR[31:0] ERA0 ERA1

指令流水线设计

指令编码-op域 指令编码 域

IR31~29 IR28~26 0 1 2 3 4 5 6 7 SHIFT SHIFT REG1 0 REG2 1 REG3 2 3 be bl ble bg bge bne br ba ret reta

蓝色阴影的指令暂不实现

CTRL 4 bal bsr bint 5 stob stos stib stis stw

//0 move R31, R31, #0 //1 move r30, r31, #FF //2 move r1, r31, #1

• 010_110_11111_11111_110_00000_00000000 • 010_110_11111_11110_110_00000_11111111 • 010_110_11111_00001_110_00000_00000001

Sequential fetch decode execute Inst1 fetch decode execute Inst2 fetch decode execute Inst3 Total=9 cycles

指令流水线模型

L 输入⇒

S1 ⇒

L

S2 ⇒

L

……

L

⇒ Sk

L

⇒

输出

时钟 τ τm

d

• 触发器将流水级输入/输出隔离 • 流水级由组合逻辑构成,并要求各段的时延大致相等 • 时钟脉冲宽度等于τm+d,通常τm>>d约1到2个数量级 τ 约 到 个数量级

• 地址端口 • 寄存器组 •桶式移位器 桶式移位器 • ALU • 数据端口

通用寄存器组

• 通用寄存器:32个32位寄存器 0~R31。 通用寄存器: 个 位寄存器 位寄存器R • ERA[31:0]:ERA[i]为1则读寄存器 中的数据到 总线 : 则读寄存器Ri中的数据到 为 则读寄存器 中的数据到A总线 • ERB[31:0]: ERB[i]为1则读寄存器 中的数据到 总线 : 则读寄存器Ri中的数据到 为 则读寄存器 中的数据到B总线 • EWR[31:0]:EWR[i]为1则将 总线上的数据写入寄存器 : 则将C总线上的数据写入寄存器 为 则将 总线上的数据写入寄存器Ri

在一个时钟周期内完成的工作量就少了。 在一个时钟周期内完成的工作量就少了。 流水线停顿的损失很高,会抵消深流水线带来的增益。 流水线停顿的损失很高,会抵消深流水线带来的增益。 流水线越深,控制逻辑就越复杂。 流水线越深,控制逻辑就越复杂。如果控制逻辑在一定程度上成为 关键路径,使流水线再深也是无效的。 关键路径,使流水线再深也是无效的。 流水周期至少在单个门延时的20倍以上。 流水周期至少在单个门延时的20倍以上。 20倍以上

• 001_011_11111_00000_000_00000_11_0_11110 //3 addi r0, r31, r30 • 001_101_00000_00000_001_00000_11_0_11110 //4 cmpi r0, r0, r30

指令流水线—空间换取时间 指令流水线 空间换取时间

指令格式

•

指令的功能由OP 域和 域决定。 域和f 域决定。 指令的功能由

• •

src1:源操作数1寄存器 :源操作数 寄存器 src2:源操作数2寄存器 :源操作数 寄存器

• •

dst:目的操作数寄存器 : lit:8位立即数(有符号数) : 位立即数 有符号数) 位立即数(

指令机器码

1. 2. 3. 4. 5. move move move addi cmpi r31, r30, r1, r0, r0, r31, r31, r31, r31, r0, #0 #FF #1 r30 r30

微处理器外部时序

地址总线AB

微处理器 CPU

存储器

输入/输出 接口电路

外围 设备

数据总线DB 控制总线CB

clk AB[31:2] DB[31:0] rd IR[31:0]

5BFF_C000 5BFF_C001

00000000

5BFF_C000

00000001

00000002

5BFF_C001

数据通路

IF

DE

EX MEM WB

三级指令流水线

• 取指级(IF):从存储器取指令,每个周期取出一条指令。PC加4 取指级( ) 从存储器取指令,每个周期取出一条指令。PC加 • 译码级(DE):译出所要执行的指令的功能并识别出所需的资源,这 译码级( ) 译出所要执行的指令的功能并识别出所需的资源, 些资源包括通用寄存器、总线和功能部件,提供流水线控制互锁, 些资源包括通用寄存器、总线和功能部件,提供流水线控制互锁,并 从寄存器读出操作数。 从寄存器读出操作数。 • 执行和写回:完成指令功能,将结果写入寄存器。 执行和写回:完成指令功能,将结果写入寄存器。

•

•

控制信号产生

IF DE EX

op

DB[31:0]

f IR

译 码 逻 辑

D 触 发 器

Cin S[3:0] M

ALU

RC[31:0]

src1 5-32 src2 5-32 dst

ERA[31:0] ERB[31:0] dst[4:0]

RF

5-32 EWR[31:0]

WB

控制信号产生

clk AB[31:2] DB[31:0] rd IR[31:0]

指令流水线

• 如果一个微处理器有 个流水级,与一个相同的没有流水线的设 如果一个微处理器有10个流水级, 个流水级 计相比,其理想性能能达到多少? 计相比,其理想性能能达到多少? • 如果流水线越深,性能越好。那为什么不只增加流水级来获得更 如果流水线越深,性能越好。 高的性能? 高的性能?

• • • •

MEM 6 ldob ldos ldib ldis ldw 7

ARITH ARITH LOGIC LOGIC COMP COMP MOVE MOVE SYS SYS

NOP

指令编码— 指令编码 f 场

IR15~13 000 001 010 011 100 101 110 111 SYS ldSR stSR lds sts MOVE movee movel movele moveg movege movene move move compo compi COMP LOGIC and nor xnor not andnot or xor nand ARITH (C=0) addi subi muli divi addo subo mulo divo ARITH (C=1) addic subic muli divi addoc suboc mulo divo shro shlo SHIFT shli shlr shri

5BFF_C000 5BFF_C001

00000000

5BFF_FF_C001

REG2指令执行过程 指令执行过程

• •

取指级:从程序存储器读取指令字并保存到IR。 加 取指级:从程序存储器读取指令字并保存到IR。PC加4 IR 译码级:译出指令执行所需要的BS、ALU控制信号并在周期末保存到D 译码级:译出指令执行所需要的BS、ALU控制信号并在周期末保存到D触 BS 控制信号并在周期末保存到 发器。IR寄存器中源操作数 寄存器中源操作数src1和源操作数src2 发器。 IR 寄存器中源操作数 1 和源操作数 2 域经译码后得到寄存器 组读信号,在下半时钟周期读取源操作数到A 总线。 组读信号,在下半时钟周期读取源操作数到A、B总线。指令字中目的寄 存器场dst dst由 位寄存器Rdst保存传递到执行级。 Rdst保存传递到执行级 存器场dst由5位寄存器Rdst保存传递到执行级。 执行级:ALU、BS根据译码级译出的控制信号完成相应的动作 根据译码级译出的控制信号完成相应的动作, 执行级:ALU、BS根据译码级译出的控制信号完成相应的动作,将结果 输出到C总线并在周期末锁存。 Rdst寄存器进行译码并保存到写信号 输出到C 总线并在周期末锁存。 对Rdst 寄存器进行译码并保存到写信号 寄存器EWR 对于条件传送指令,在执行级对条件是否成立进行判断。 EWR。 寄存器EWR。对于条件传送指令,在执行级对条件是否成立进行判断。 写回级: 上半时钟周期将结果数据写入寄存器。 写回级:在上半时钟周期将结果数据写入寄存器。 周期将结果数据写入寄存器