低频锁相放大器设计

第3章 低频功率放大器的设计与制作

第3章低频功率放大器的设计与制作3.1设计任务与要求3.1.1 设计任务设计并制作具有弱信号放大能力的低频功率放大器,其原理框图如图3-1所示:图3-1 低频功率放大器原理框图3.1.2 要求1、在放大通道的正弦信号输入电压峰峰值为20mV,等效负载电阻R L为8Ω条件下,放大通道应满足:(1)额定输出功率P out≥0.5W,输出波形无明显失真;(2)带宽BW为50Hz~10kHz;(3)在P out下的效率≥50%;(4)在P out下和BW内的非线性失真系数≤5%;(5)前置放大器与功率放大器采用+12V单电源供电。

2、在放大通道的输入端接入驻极体,应能放大不失真的语音信号。

3、自行设计并制作满足本设计任务要求的稳压电源。

3.2 低频功率放大器的总体方案设计根据系统原理框图及要求,低频功率放大器的总体电路结构如图3-2所示:图3-2低频功率放大器电路结构图电路工作原理:电路共分两级,第一级为前置放大部分,第二级为功率放大部分。

电源经C1、C2、C3滤除其中的干扰信号,其中电阻R1是将微小信号放大级与功率放大级隔离,避免两级间的相互干扰,R2是限流电阻,同时为驻极体提供合适的静态工作电流。

驻极体产生的微小信号经电容C4耦合到第1个运算放大器A的反相输入端,对输入信号进行电压放大,R5、R6、R7、R8分压,为运算放大器提供合适的静态工作点,避免放大信号的失真。

信号经C6耦合到第2个运放B的同相输入端,此运放构成电压跟随器,用作前后级的阻抗匹配,理想运放有较高的输入阻抗和较低的输出阻抗,可以抑制有用信号的衰减。

信号经B运放7脚输出由电容C7耦合到电位器RP1,RP1起到音量调节的作用,信号由RP1的中心抽头再进入LM386芯片的3脚,该芯片是功率放大集成芯片,通过调节1、8脚之间的电阻R9和电容C9的大小,进而调节功率放大倍数。

最后信号从5脚输出,经电容C12连接到扬声器。

外围的R11、RP2支路构成大环路电压并联负反馈电路,稳定输出端的电压信号,减小非线性失真。

低频功率放大器的设计设计

摘要实用低频功率放大器主要应用是对音频信号进行功率放大,本文介绍了具有弱信号放大能力的低频功率放大器的基本原理、内容、技术路线。

整个电路主要由稳压电源、前置放大器、功率放大器、波形变换电路共4 部分构成。

稳压电源主要是为前置放大器、功率放大器提供稳定的直流电源。

前置放大器主要是电压的放大。

功率放大器实现电流、电压的放大。

波形变换电路是将正弦信号电压变换成规定要求的方波信号。

设计的电路结构简洁、实用,充分利用到了集成功放的优良性能。

实验结果表明该功率放大器在带宽、失真度、效率等方面具有较好的指标、较高的实用性,为功率放大器的设计提供了广阔的思路关键词:正弦波—方波转换电路弱信号前置放大级电路功率放大电路自制稳压电源电路目录第一章前言 (1)第二章总体方案设计 (3)2.1总体方案论证 (3)2.2单元模块方案论证与比较: (3)2.2.1波形变换电路: (3)2.2.2弱信号前置放大级: (4)2.2.3功率放大级: (4)2.2.4自制稳压电源: (5)2.3方案选择: (5)第三章单元模块设计 (6)3.1各单元模块功能介绍及电路设计: (6)3.1.1波形变换电路: (6)3.1.2弱信号前置放大级电路: (7)3.1.3功率放大电路 (10)3.1.4自制稳压电源电路: (12)3.2特殊器件的介绍 (12)第四章系统调试 (14)4.1.稳压电源的调试: (14)4.2.前置放大电路和波形转换电路的调试: (14)第五章系统功能、指标参数 (15)5.1 要求指标与实测指标对比,见表1: (15)总结 (16)参考文献 (17)致谢 (18)第一章前言功率放大器在家电、数码产品中的应用越来越广泛,与我们日常生活有着密切关系。

随着生活水平的提高,人们越来越注重视觉,音质的享受。

在大多数情况下,增强系统性能,如更好的声音效果,是促使消费者购买产品的一个重要因素。

低频功率放大器作为音响等电子设备的后即放大电路,它的主要作用是将前级的音频信号进行功率放大以推动负载工作,获得良好的声音效果。

锁定放大器的设计

目录1.摘要与系统方案选择2.设计原理与理论分析3.交流放大器4.有源带通滤波器5.硬件设计6.加法器7.二阶带通滤波器8.参考通道9.实验数据10.软件程序11.参考文献锁定放大器的设计摘要本系统以TI公司超低功耗MSP430G2553作为处理核心,进行控制和测量。

信号通道对调制正弦信号输入运用加法电路以后,先进行衰减10000倍,然后进行交流放大10000倍(一级放大100倍,二级放大100倍),让信号通过信号通道,一级放大用高精度仪表放大器 INA114对信号进行初步的放大,进一步提升系统的噪声抑制比,二级放大应用TI通用双运放OPA2237实现。

相敏检波模块(相敏检波器,低通滤波器和直流放大器)由数字电路用单片机来实现,参考信号通过自制的电阻分压网络降压和TI公司的LM324电压比较器实现移相器,调理后汇总进入数字检波模块最后显示出结果,顺利完成了题目要求。

关键词:微弱信号放大精密仪表放大器放大器数字检波一、系统方案与选择1.放大电路的选择方案一:选用普通运算放大器,价格便宜,技术成熟,操作难度小。

但是会将内部严重的噪声放大,共模抑制比一般,测量会存在很大的误差。

方案二:采用高精度仪表放大器INA114是一种通用的仪表放大器,尺寸小精度高,价格低廉,应用广泛。

对于系统的前端放大电路用INA114只需要一个外部电阻就可以设置,电路简单。

由于被测信号小,就要求前置放大器必须具备低噪声的特点,否则将由于放大器本身的噪声将使放大器的本身噪声将使信号淹没的更深。

另外,还要考虑前置放大器具备足够的放大倍数,强的共模抑制比。

综上,放大器信号通道要求具有低噪声和高效益的性能,而TI公司的仪表放大器IN114完美的达到了要求。

增益在1--10000之间的任意增益值, 共模抑制比高(G=1000时为50dB),失调电压低,漂移小(0.25uV∕°C)测量精准。

2.相敏检测装置的选择方案一:输出前的低通滤波器和直流放大器运用模拟电路来实现,电路简单操作容易,但是考虑到全局都用模拟来实现会带来较大误差。

低频功率放大器的设计

01 Chapter定义应用低频功率放大器的定义和应用01020304033. 元器件选择011. 确定设计需求和目标022. 选择合适的放大电路拓扑结构6. 测试与调试7. 文档编写02 Chapter电压跟随器设计偏置电路设计输入阻抗匹配030201电流放大设计驱动能力增强失真度控制功率输出设计输出级的负载通常是扬声器等低阻抗设备,因此需要进行输出阻抗与负载的匹配设计。

负载匹配保护电路设计03 Chapter增益带宽积和转换速率增益带宽积转换速率输出功率输出功率是功率放大器驱动负载的能力,通常以分贝(dB)为单位表示。

在低频功率放大器的设计中,提高输出功率可以通过增加电源电压、优化输出级电路等方式实现。

失真度失真度衡量放大器输出信号与输入信号的差异,包括谐波失真、交越失真等。

在低频功率放大器的设计中,降低失真度是关键目标之一。

这可以通过采用线性度更好的放大器件、改进偏置电路、降低工作温度等方式实现。

输出功率与失真度效率与线性度效率效率是指功率放大器输出功率与输入功率的比值,表示放大器将输入功率转换为输出功率的能力。

在低频功率放大器的设计中,提高效率有助于降低能耗,实现节能环保。

提高效率的方法包括采用开关类功放、Doherty功放等高效功放架构。

线性度线性度衡量放大器输出信号与输入信号之间的线性关系。

在低频功率放大器中,线性度直接影响信号的保真度。

改善线性度可以通过使用高线性度的放大器件、采用负反馈技术、预失真技术等方法来实现。

04 Chapter电路仿真与设计验证仿真软件选择01电路搭建与参数设置02仿真结果分析03电路板制作实际电路搭建与调试元器件选择与采购电路板制作与测试验证结果分析与设计改进建议测试数据收集设计改进建议THANKS。

简易锁相放大器的设计-TIE2E中文社区

锁相放大器的原理锁相放大器L队(Lock.in Amplifier,简称L队)就是利用互相关的原理设计的一种同步相干检测仪。

它是一种对检测信号和参考信号进行相关运算的电子设备。

在测量中,噪声是一种不希望的扰乱信号,它是限制和影响测量仪器的灵敏度的白噪声和1/f噪声的低频噪声。

这些噪声是无法用屏蔽等措施消除的。

为了减少噪声对有用信号的影响,常用窄带滤波器滤除带外噪声,以提高信号的信噪比。

但是,由于一般滤波器的中心频率不稳,而且带宽和中心频率以及滤波器的Q值有关等原因,使它不满足更高的滤除噪声之要求。

根据相关原理,通过乘法器和积分器串联,进行相关运算,除去噪声干扰,实现相敏检波,锁相放大器采用互相关接受技术使仪器抑制噪声的性能提高了好几个数量级。

另外,还可以用斩波技术,把低频以至直流信号变成高频交流信号后进行处理,从而避开了低频噪声的影响。

锁相放大器抑制噪声的性能如下:国内外生产的锁相放大器的等效噪声带宽厶在103Hz数量级,少数的可以达到4×104Hz,信号带宽2.55×106Hz,可见,仪器具有非常窄的信号和噪声带宽,通常带通滤波器由于Q值的定义,常规滤波器很难达到一些性能。

而锁相放大器被测信号和参考信号是同步的,它不存在频率稳定性问题,所以可以把它看成为一个“跟踪滤波器"。

它的等效Q值由低通滤波器的积分时间常数决定,所以对元件和环境的稳定性要求不高。

研究表明,锁相放大器使信噪比提高一万多倍即信噪比提高了80dB以上。

这足以表明,采用相关技术设计的锁相放大器具有很强的抑制噪声能力。

目前锁相放大器有如下特点:极高的放大倍数,若有辅助前置放大器,增益可达101l(即220dB),能检测极微弱信号交流输入、直流输出,其直流输出电压正比于输入信号幅度及被测信号与参考信号相位差,满刻度灵敏度达pV、nV甚至于pV量级。

由此可见,锁相放大器具有极强的抗噪声性能。

它和一般的带通放大器不同,输出信号并不是输入信号的放大,而是把交流信号放大并变成相应的直流信号。

锁相放大器的设计

锁相放大器的设计【摘要】本系统以超低功耗MSP430G2553作为处理核心,用OPA244、OPA2237、LM324N、LM3119等实现对微弱信号的检测。

该电路由信号调理模块、移相器模块、相敏检波器和数码管四个模块组成。

信号调理模块包括加法器,交流放大器,四阶带通滤波器,信号调理电路子模块,其具有微弱信号放大和调理、抑制干扰和噪声的作用。

移相器模块由多个比较器,积分器组成,实现与被测信号的同步,产生可180°移相的方波传输给MCU,由数码管显示被测信号的幅度。

【关键词】微弱信号;移相器;msp430;相敏检波器1.锁相放大器设计原理根据相关接收原理,在相关接收中,可以把两个信号的函数f1(t)和f2(t)的相关函数定义为:它是度量一个随机过程在时间t和两时刻线性相关的统计参数,如果f1(t)和f2(t)完全没有关系,则相关函数将是一个常数。

下面我们设有两个信号x(t)、y(t)为:其中n1(t)、n2(t)为噪声,Vs(t)为待测信号,Vr(t)为参考信号。

则相关函数为:展开得:因为信号和噪声不相关,且噪声的平均值为零,所以都为零。

故:这样我们可以看到,两个信号经过相乘和积分处理后就可以把噪声抑制,锁相放大器的核心就是根据这个原理设计的。

2.设计方案的论证如图1所示,该方案将数字脉冲电位器用模拟移相器取代,其中移相器是由多个小模块依次作为输入产生不同的波形,最终实现将正弦信号调整为相位不同的方波信号。

且该处采用模拟器件容易实现,便于分级检测输出的波形,及时对硬件电路进行修正和改进。

图13.硬软件设计3.1 硬件的总体设计通过理论分析,该系统主要由由三部分组成,即:信号通道,参考通道和其他相关器。

加法器将被测信号S(t)和噪声信号n(t)以1:1叠加后通过电阻分压网络将叠加后的信号进行衰减。

信号通道由放大器和带通滤波器组成,其作用是把微弱信号放大到足以推动相关器的工作电平,并兼有抑制和滤掉部分干扰和噪声,扩大仪器动态范围的性能;参考通道由触发整形和移相器组成,其作用是产生与被测信号同步的对称方波,再由方波驱动给相关器;相关器由数字相敏检波器组成,是锁定放大的核心部件,具有动态范围大、漂移小、时间常数可调等性能。

锁相放大器设计解析

C题:锁定放大器的设计摘要:本设计对于检测微弱信号的锁存放大器进行论述,锁定放大器主要包括交流放大器、带通滤波器、相敏检波器、低通滤波器、直流放大器及液晶显示等几个部分。

其中,交流放大器以INA128为主要构成部件,实现交流信号的放大从而作为带通滤波器的输入;带通滤波器用UAF42构成,实现对900Hz到1100Hz频带范围的滤波过程,其误差小于20%;相敏检波器的主要部件采用乘法器MPY634,得到的信号在输入低通滤波器经直流放大器放大后输入显示电路,显示出被测信号的幅度及有效值。

另外,在相敏检波器部分的方波驱动信号由参考信道的参考信号经触发整形、移相、比较而来。

同时,为了更好的检测出锁定放大器的性能,在信号的输入端增加加法器电路,实现被测信号与干扰信号的1:1叠加,当干扰信号的频率为1050Hz—2100Hz时,输出端的测量误差小于10%。

锁定放大器在实际应用中用途广泛,尤其对于微弱信号检测方向站着主导地位,随着科技的发展已渐渐的融入人类的生活之中,拥有很好的发展前景。

关键词:带通滤波器;相敏检波器;显示;方波驱动1 总体方案设计1.1方案比较与选择1.1.1微弱信号检测模块方案比较方案一:采用滤波电路检测微弱信号,通过滤波电路将微弱信号从强噪声中检测出来,但滤波电路中心频率是固定的,而信号的频率是可变的,无法达到要求,由此可见该方案不满足要求。

方案二:采用取样积分电路检测小信号,采用取样技术,在重复信号出现的期间取样,并重复N次,则测量结果的信噪比可改善√N倍,但这种方法取样效率低,不利于重复频率的信号恢复。

方案三:采用锁相放大器检测小信号,锁相放大器由信号通道、参考通道和相敏检波器等组成,其中相敏检波器(PSD)是锁相放大器的核心,PSD把从信号通道输出的被测交流信号进行相敏检波转换成直流,只有当同频同相时,输出电流最大,具有良好的检波特性。

由于该被测信号的频率是指定的且噪声强、信号弱,正好适用于锁相放大器的工作情况,故选择方案三。

低频放大器的设计

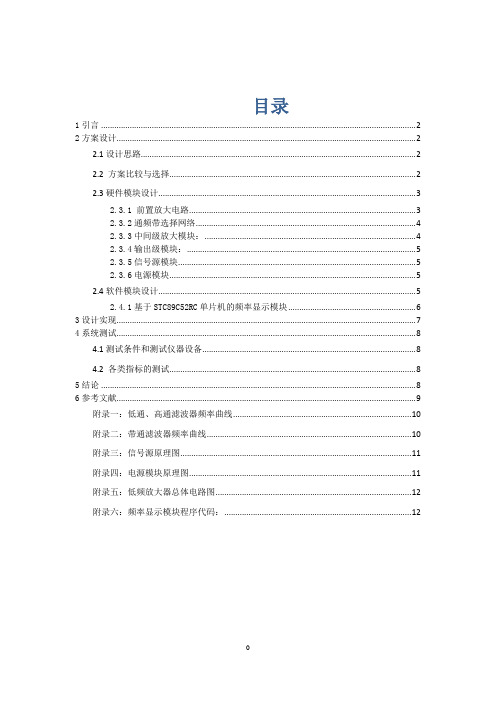

目录1引言 (2)2方案设计 (2)2.1设计思路 (2)2.2 方案比较与选择 (2)2.3硬件模块设计 (3)2.3.1 前置放大电路 (3)2.3.2通频带选择网络 (4)2.3.3中间级放大模块: (4)2.3.4输出级模块: (5)2.3.5信号源模块 (5)2.3.6电源模块 (5)2.4软件模块设计 (5)2.4.1基于STC89C52RC单片机的频率显示模块 (6)3设计实现 (7)4系统测试 (8)4.1测试条件和测试仪器设备 (8)4.2 各类指标的测试 (8)5结论 (8)6参考文献 (9)附录一:低通、高通滤波器频率曲线 (10)附录二:带通滤波器频率曲线 (10)附录三:信号源原理图 (11)附录四:电源模块原理图 (11)附录五:低频放大器总体电路图 (12)附录六:频率显示模块程序代码: (12)低频放大器的设计摘要基于以运算放大器(OP07、OP37)为主要芯片,设计并制作一个低频放大器。

通过三级耦合放大,基本达到2000倍的增益。

电路利用仪用放大电路作为输入级抑制噪声,增大输入电阻。

在二级电路利用四阶有源带通滤波器实现了3KHz到5KHz的通频带,抑制干扰信号。

由各单个元器件的漂移特性,巧妙采用放大级正向、反向输入端,有效的抑制了零漂。

另外以电压跟随器作为末级输出,减小了输出电阻。

各级间以阻容耦合的方式,有效地抑制了直流信号。

关键字:低频放大器滤波器零点漂移增益步进1引言在很多电子线路中,对于一个非常微弱的低频电压信号,需要放到很大的倍数来使用和使其他的仪器识别、测量。

本次设计一个低频放大器来实现对低频信号的放大。

本次设计的低频放大器要满足以下基本要求:(1).电压放大倍数200-2000倍,最大不失真输出幅度不小于10V。

放大倍数可预置(步进≯200倍);(2).通频带3kHz-5kHz;(3).放大倍数为2000倍时,测得输出噪声电压峰—峰值等效到输入端小于1mV;(4).输入电阻不小于100kΩ,输出电阻不大于50Ω。

低频功率放大器的设计说明书

毕业设计说明书课题名称: 低频功率放大器的设计系别电子信息工程系专业应用电子技术毕业设计起讫时间:2摘要介绍了一种具有小信号放大能力的低频功率放大器的设计和制作,论述了系统的设计原理、理论依据、工作流程、程序设计、测试方法和实验数据等。

系统主要由电压放大电路、输出级电路、带阻滤波器和显示电路等组成,电路结构简捷,技术合理、器件成本低、省电节能、性价比高。

实验结果表明,该功率放大器在功率、通频带、失真度和效率等方面具有较好的指标、较高的实用性和节能性,并很好地实现了对低频信号的功率放大作用,符合技术规范和设计要求。

关键词:低频;功率放大器;频率;失真;效率AbstractThis paper presents a small-signal amplification with the ability to design and production of low-frequency power amplifier, discusses the system design principles, theoretical basis, workflow, programming, testing methods and experimental data. System is mainly from the voltage amplifier circuit, the output stage circuit, band-reject filters and display circuit etc., the circuit structure is simple, sound technology, device, low cost, power-efficient, cost-effective. The experimental results show that the power amplifier in the power, pass-band, distortion and efficiency indicators has a better, higher utility and energy efficiency, and well realized the power of the low-frequency signal amplification,Meet the technical specifications and design requirements.Key words:low-frequency;power;amplifier;frequency;distortion;efficiency目录摘要 (1)Abstract (1)1 前言 (3)1.1功率放大器的发展史 (3)1.2本课题的意义 (4)2 系统设计 (5)2.1总体设计方案 (5)2.1.1设计思路 (5)2.1.2方案论证与比较 (5)2.3理论分析与计算 (7)3 系统电路的设计 (8)3.1 弱信号前置放大级 (8)3.1.1工作原理 (8)3.1.2抑制零点漂移的原理 (9)3.2功率放大级 (10)3.2.1复合管的特点 (10)3.2.2工作原理 (11)3.2.3元件的作用 (11)4 制作与调试 (12)4.1整体电路调试 (12)4.1.1主要测试仪器 (12)4.1.2产品的调试 (12)4.2主要技术指标测试 (12)4.3测试结果分析 (13)4.4注意事项 (13)6 总结 (14)致谢 (16)参考文献 (17)附录A (18)附录B (19)1 前言1.1功率放大器的发展史功率放大器是一个技术已经相当成熟的领域,几十年来,人们为之付出了不懈的努力,无论从线路技术还是元器件方面,乃至于思想认识上都取得了长足的进步。

低频放大电路的设计(共8张PPT)

l 2.掌握低频小信号放大电路的设计方法。

二、设计任务与要求

l 输入信号电压幅值Uim=10mV;放大电路输入阻抗

l

Ri≥100kΩ;输出电阻Ro≤100Ω;

l

频带范围0Hz--2000Hz,误差为±10%;

l

输出电压幅值为1V,误差为±10%;负载电阻为1kΩ。参考

频率(Hz)

1 500 1000 1500 1800 1900 1950 2000 2050 2100 2500

测量值Uo (V) 理论值Uo (V)

4.测量输入电阻和输出电阻

第七页,共8页。

六、实验报告要求

写出设计步骤及计算公式,画出电路图,并标注元件 参数值。 整理实验数据,计算实验结果。 把理论值与实验结果进行比较,说明误差原因。

第八页,共8页。

Ui

R

R

A

+

CC

Af()U Uof

Uo

10A2fjQ 10

0

1 RC

Af

1

Rf R1

二阶低通滤波电路

1 Q

3

Af

第四页,共8页。

l

输出电路:

l

同相比例电路或电压跟随电路。

然后用示波器观察输出端,在波形无明显失真的条件下,用毫伏表测量Uo的值。

掌握低频小信号放大电路的设计方法。

同相比例电路或电压跟随电路。

3.ADCL-IV型电子实验仪;

4.函数发生器;

5.示波器;

6.集成运放:LM324 ,电位计、电阻、电容若干。

第六页,共8页。

五、实验内容与步骤

1.根据设计要求,设计出完整电路,计算和确定元件参数。 2.在实验仪器上安装好电路,检查无误后接通电源。 3.测量电路的输出: (1)从正弦信号发生器上用屏蔽线接入输入信号,使其频率 为在5波00形H无z,明电显压失有真效的值条为件U下i=,10用mV毫。伏然表后测用量示U波o的器值观。察输出端, (2)改变输入信号的频率,测量Uo的值,并填入表中。

OCL低频功率放大器设计报告

OCL低频功率放大器设计报告报告:OCL低频功率放大器设计一、设计目标本次设计的目标是设计一个OCL(Push-Pull)低频功率放大器。

要求输入电压幅值为0.1V,输出电压幅值为10V,带宽为20Hz~20kHz,采用集成运放作为放大电路的核心元件。

二、设计方案1. 电路结构选择OCL(Push-Pull)架构是一种常用的低频功率放大器设计方案,能够提供较高的输出功率。

该电路结构由两个互补的输出管组成,能够消除交叉失真。

在本次设计中,我们选择使用OCL结构。

2. 放大器核心元件选择为了实现低频放大,我们选择使用集成运放作为放大器的核心元件。

集成运放具有高增益、低失调和低噪音等特点,能够满足本次设计的要求。

3. 输入级电容耦合为了阻隔输入信号的直流偏置,我们在输入级采用了电容耦合的方式。

电容耦合器的电容决定了该电路的低频截止频率,设计时需要合理选择电容值。

4. 负反馈电路设计为了提高放大器的线性度和稳定性,我们引入了负反馈电路。

通过负反馈,可以使放大器的增益稳定,并降低非线性失真。

本次设计选择了电压跟随型负反馈电路。

5. 输出级选择在输出级,我们选择了互补输出管,能够提供较高的输出功率,并能够消除交叉失真。

为了保证输出信号的稳定性,输出级需要通过负反馈电路进行稳定。

三、设计流程1. 确定输入和输出电压幅值根据设计要求,输入电压幅值为0.1V,输出电压幅值为10V。

2. 确定放大器的增益根据输入和输出电压幅值,可以计算出放大器的增益。

放大器的增益计算公式为:增益 = 输出电压幅值 / 输入电压幅值 =10V / 0.1V = 100。

3. 选择集成运放根据设计要求和放大器的增益,选择适合的集成运放。

根据集成运放的参数手册,查找到符合要求的集成运放。

4. 选择电容值根据放大器的截止频率要求,选择合适的电容值。

根据截止频率计算公式,计算出所需的电容值。

截止频率= 1 / 2πRC,其中R为输入电阻,假设为10kΩ,C为电容值。

毕业设计低频功率放大器设计与制作

毕业设计低频功率放大器设计与制作系别:电子电气工程系专业:应用电子技术班级:姓名:XXX学号:指导教师:完成时间:毕业设计任务书注:任务书必需由指导教师和学生相互交流后,由指导教师下达并交所属系部毕业设计(论文)领导小组审核后发给学生,最后同窗生毕业论文等其它材料一路存档。

毕业设计开题报告题目:低频功率放大器设计与制作系别:电子电气工程系专业:应用电子技术班级:姓名:XXX学号:13159020XXXXX指导教师:xx2017年 11月 15日前言随着科技的进展,在现代生活中,彩灯作为一种景观应用愈来愈多。

城市马路,大街小巷,商业店铺各类彩灯有点让人“乱用渐欲你人眼”的感觉,各类花腔形式。

在家庭装饰或商业区的灯光布置中常常需要完成彩灯循环点亮或数字计数等动态灯光成效,给生活增添光荣,那这彩灯是怎么能够如此显示呢?本设计依照这种灯的原理,应用数字电子技术的逻辑器件设计电路原理图和编写VHDL语言来进行分析也编写,并在QUATURS II软件上实现编译,调试,波形仿真与分析,和下载到FPGA上运行,实现彩灯功能,并能自由操纵彩灯循环点亮的快慢,从而实现彩灯的原理。

最终完成的是灯光装饰中的彩灯循环点亮,数字计数和频率调剂等功能的设计。

设计彩灯操纵器,能够操纵彩灯的闪烁频率,花腔,如何闪烁。

各类公交上,银行门口上的红色字体都是多路彩灯操纵器操纵的LED管显像,这不单单能使彩灯更有观赏性,还能为商家提供吸引顾客眼球的方式。

因此很多店铺商家都请人为他们设计彩灯操纵器,使得他们店铺眼前的彩灯显现各类不同,让人眼前一亮的彩灯来吸引顾客,提高商业价值。

目录(范文)摘要 (1)第1章绪论 (2)1.1课题背景 (2)1.2遥控器原理 (2)1.3设计任务 (2)1.4设计的意义 (2)第2章无线遥控原理 (4)2.1发射电路原理 (4)2.2接收电路原理 (4)2.3天线原理 (4)2.3.1 什么是天线 (4) (5)第3章遥控方案设计 (6)3.1系统设计 (6)3.2解决方案一 (6)3.3解决方案二 (7)3.4方案论证 (8)第4章系统实现 (9)4.1工具介绍 (9)4.1.1 Protus原理图与仿真 (9)4.1.2 Protel原理图与电路板制作 (9)第5章系统测试 (11)5.1无线发射接收测试 (11)5.2程序测试 (12)5.3系统整体测试 (12)参考文献 (13)附录 (14)摘要盆腔炎医治仪,利用物理的电、热、磁等生理作用,增进人体神经肌肉组织兴奋和局部血液循环,并有镇痛作用。

低频功率放大器的设计与制作

目录摘要 (2)第一章方案设计与选择 (3)第二章电源 (4)2.1桥式整流电路 (4)2.1.1 电路组成和工作原理 (4)2.2 变压器 (4)2.2.1 分类 (5)2.3 滤波原理 (5)2.3.1电容滤波 (6)2.3.2 电容滤波电路的特点 (7)2.4 稳压电源 (8)2.4.1 集成稳压 (8)第三章实验内容 (9)第四章安装与调试过程 (10)第五章总结与体会 (12)第六章致谢 (13)附录一 (14)附录二 (15)低频功率放大器的设计与制作(分离件)作者:李明[摘要]:功率放大是一种能量转换的电路,在输入信号的作用下,晶体管把直流电源的能量,转换成随输入信号变化的输出功率送给负载.整个电路主要由稳压电源、前置放大器、功率放大器、波形变换电路共4个部分构成,电路结构简单,所选器件价格便宜,并给出了测试结果. 功率放大器的主要任务是为了获得一定的不失真的输出功率,一般在大信号状态下工作。

输出信号去驱动负载,如:驱动扬声器,使之发出声音;驱动电机伺服电路,驱动显示设备的偏转线圈控制电机运动状态。

实验结果表明该功率放大器在放大倍数、效率、等方面具有较好的指标、较高的实用性,为功率放大器的设计提供了广阔的思路.[关键词]:功率放大器放大倍数效率前言随着电子技术的飞速发展,电子新技术、新产品不断涌现,电子技术的广泛应用,促进了工农业生产、也丰富了人们的物质文化生活。

其中功率放大器也随着科技的不断进步得到了很大的发展功率放大器简称功放,它和其它放大电路一样,实际上也是一种能量转换电路,这一点它和我们以前学的电压放大电路没有本质区别。

但是它们的任务是不相同的,电压放大电路属小信号放在电路,它们主要用于增强电压或电流的幅度,而功率放大器的主要任务是为了获得一定的不失真的输出功率,一般在大信号状态下工作。

输出信号去驱动负载,如:驱动扬声器,使之发出声音;驱动电机伺服电路,驱动显示设备的偏转线圈控制电机运动状态。

锁相放大器

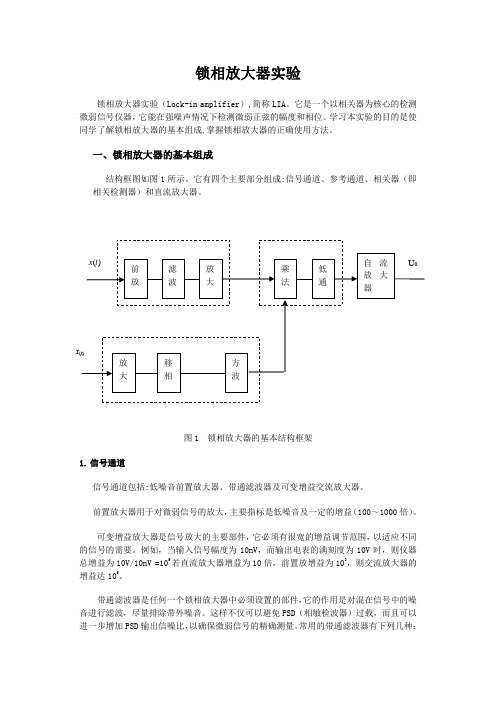

锁相放大器实验锁相放大器实验(Lock-in amplifier),简称LIA。

它是一个以相关器为核心的检测微弱信号仪器,它能在强噪声情况下检测微弱正弦的幅度和相位。

学习本实验的目的是使同学了解锁相放大器的基本组成,掌握锁相放大器的正确使用方法。

一、锁相放大器的基本组成结构框图如图1所示。

它有四个主要部分组成:信号通道、参考通道、相关器(即相关检测器)和直流放大器。

图1 锁相放大器的基本结构框架1.信号通道信号通道包括:低噪音前置放大器、带通滤波器及可变增益交流放大器。

前置放大器用于对微弱信号的放大,主要指标是低噪音及一定的增益(100~1000倍)。

可变增益放大器是信号放大的主要部件,它必须有很宽的增益调节范围,以适应不同的信号的需要。

例如,当输入信号幅度为10nV,而输出电表的满刻度为10V时,则仪器总增益为10V/10nV =109若直流放大器增益为10倍,前置放增益为103,则交流放大器的增益达105。

带通滤波器是任何一个锁相放大器中必须设置的部件,它的作用是对混在信号中的噪音进行滤波,尽量排除带外噪音。

这样不仅可以避免PSD(相敏检波器)过载,而且可以进一步增加PSD输出信噪比,以确保微弱信号的精确测量。

常用的带通滤波器有下列几种:(1) 高低通滤波器图2为一个高通滤波器和一个低通波滤波器组成的带通滤波器,其滤波器的中心频率f 0及带宽B 由高低滤波器的截止频率f c1决定和f c2决定。

锁相放大器中一般设置几种截止频率,从而根据被测信号的频率来选择合适的频率f 0及带宽B 。

但是带宽滤波器带宽不能过窄,否则,由于温度、电源电压波动使信号频谱离开带通滤波器的通频带,使输出下降。

为了消除电源50Hz 的干扰,在信号通道中常插入组带滤波器。

(2)同步外差技术上述高低通滤波器的主要缺点是随着被测信号频率的改变,高低通滤波器的参数也要改变,高低通滤波器的参数也要改变,应用很不方便。

为此,要采用类似于收音机的同步外差技术,原理框图如图3所示。

低频小信号放大器电路设计.

摘要低频小信号放大器电路设计摘要实用性低频小信号放大器电路设计,它主要用于使用前置放大器的低频小信号的电压经过集成块LM358的放大使其增益二十几倍,达到信号放大的作用,本文介绍了其基本原理,内容,与低频放大微弱信号放大能力的技术路线,设计电路图方案等。

本系统是基于(IC)LM358设计而成的一种低频小信号放大器,整个电路主要由稳压电源,前置放大电路,波形变换电路3部分。

电源主要是为前置放大器提供稳定的直流电源。

前置放大器主要是由ML358一级放大电路和ML358二级放大电路组成,第一级可以将电压放大5倍,第二级可以放大1-5倍,总增益20-25倍,接通电源后,信号发生器产生信号,示波器用于变换的波形显示。

通过波形的数据变化,计算出增益效果,是否满足设计需求。

该设计的电路结构简单,实用,充分利用了集成功放的优良性能。

实验结果表明,前置放大器的带宽,失真,效率等方面具有较好的指标,具有较高的实用性,为小信号放大器的设计是一个广泛的思考。

关键词:低频小信号,电压放大,前置放大级电路,集成块LM358AbstractDesign of low frequencysmall signal amplifierAbstract:The utility of low frequency small signal amplifier circuit design, it is mainly used for voltage low frequency small signal using a pre amplifier after amplification integrated block LM358 has gain 20 times, achieve signal amplification effect, this paper introduces the basic principle, content, and low frequency amplification technology route of weak signal amplification ability, circuit design scheme.The system is based on (IC) a low frequency small signal amplifier LM358 designed, the whole circuit is mainly composed of a regulated power supply, preamplifier circuit, a waveform transform circuit 3 parts. The power supply is mainly to provide a stable DC power for the preamplifier. The preamplifier is mainly composed of ML358 amplifier and ML358 two stage amplifier circuit, the first stage of the voltage can be magnified 5 times, second can be magnified 1-5 times, 20-25 times of the total gain, power, signal generator generates a signal, oscilloscope is used to transform the waveform display. By the waveform data changes, calculated the gain effect, whether meet the design requirements.The design of the circuit structure is simple, practical, make full use of the excellent performance of the integrated amplifier. The experimental results show that, the pre amplifier bandwidth, distortion, has better efficiency indicators, and has higher practicability, designed for small signal amplifier is a broad thinking.Keywords:Lowfrequency smalsignal,voltage amplification,preamplifiercircuit,Integrated block LM358常州工学院延陵学院毕业设计说明书目录第1章绪论 (1)前言 (3)1.1课题研究背景 (3)1.2课题主要研究内容 (4)第2章设计方案分析 (5)2.1设计任务 (6)2.2设计分析 (7)2.2.1设计技术指标 (7)2.2.2集成块LM358的介绍 (8)2.3 LM358概述 (9)2.3.1 LM358的原理与应用 (9)2.3.2 LM358行情介绍 (10)第3章前置放大器的设置原理描述 (10)3.1总体方框图设计 (11)3.2方案设计与论证 (12)3.3前置放大电路设计 (13)3.4电压跟随器电路设计 (16)第4章软件介绍......................................................................... (17)4.1 proteus仿真软件概述 (19)第5章系统的软硬件调试 (22)5.1实验电路功能的测试 (23)5.2硬件调试 (23)5.2.1上电前的调试 (23)5.2.2 上电调试 (24)5.3各模块调试 (24)5.4整机调试 (25)第6章详细元器件清单 (25)6.1电路图汇总 (26)6.2实验仪器清单 (26)6.3实验元器件清单如下表 (27)结论 (27)致谢 (28)参考文献 (31)附录 (32)第1章绪论前言在科学研究和工程实践中,经常遇到的微伏级信号的检测有问题,如材料分析的地震波速度,测定,测量卫星信号接收器的荧光强度,红外检测的生物信号测量等。

低频功率放大器的设计与制作-毕业设计

低频功率放大器的设计与制作学生:指导教师:内容摘要:本文介绍了一种基于NE5534设计而成的低频功率放大器。

是由直流稳压电源,前置放大器,带阻电路,COMS功率放大器,峰值检测和数据采集显示六个模块组成。

直流稳压电源主要由15V双电源与LM317与LM337,7805构成,可输出正负15V 电压和5V电压,分别为功率放大器和显示模块提供所需的电压。

前置放大器是两级放大,构成一个带通放大器。

CMOS功率放大器是由N沟道和P沟道场效应管构成的OCL电路。

带阻电路用于滤除电源的公共频率。

峰值检测将负载输出的稳定电压并将电压降低至5V以下。

液晶显示模块显示的结果,主要是将20HZ~20KHZ的小信号放大,输出功率大于5W且输出的噪音电压有效值小于5mv,并将系统输出功率,直流电压的输出功率,整机效率显示出来。

功率放大器作用主要是给负载提供所需要功率,它不仅仅是音频设备中必不可少的器件,同时在测量系统和控制系统中也有广泛应用。

低频功率放大器已经是一个相当成熟的技术。

几十年来,无论是从线路技术和元器件的方面,还是思想方面都有很大进步。

它可以由集成元件构成,也可以由分立元件构成。

集成功率放大器具有功放体积模块小,外围电路简单,性能优越,易调试,制作简单,保护功能齐全等优点。

而用分立元件制作,如果精心设计,则在效率和失真的方面要远远优于集成功放。

本设计在功率放大级采用COMS管,具有功耗低,失真小,噪声低,性价比高和稳定性好等特点,并能实时显示整机效率,直流电源功率和输出功率。

可广泛应用于测量系统和控制系统。

关键词:低频功率放大器 MOS管 NE5534 OCLDesign and manufacture of low-frequency power amplifier Abstract: This article describes an approach based on NE5534 designs of low-frequency power amplifiers. Is made up of DC voltage, preamplifier, band stop circuit, COMS amplifier with peak detection and data acquisition display consists of six modules. Main 15V DC power supply dual power supply with LM317 and LM337,7805 composition, positive and negative voltage of 15V and 5V output voltages, power amplifier respectively and display module provide the required voltage. Preamplifier is a two-level zoom in, form a bandpass amplifier. Is n-channel and p-channel CMOS power amplifier tube consisting of OCL Dojo effects circuits. Public frequency band stop circuit to remove power. Peak detect stability of the output voltage and the load will reduce the voltage to 5V. LCD display module displays the results, mostly 20HZ~20KHZ small-signal amplifier, the output power is greater than 5W, output noise voltage is less than 5MV, and system output power, DC voltage output power, machine efficiency visible.Power amplifier is mainly needed to provide load power, it is not only essential components of the audio device, both measurement and control systems are also widely used. Low frequency power amplifier is a fairly mature technology. For decades, both in terms of lines of technologies and components, is thought have made a lot of progress. It can consist of integrated components, can also be constructed from discrete components. Integrated power amplifiers with power amplifier module size small, simple peripheral circuit, superior performance, easy to debug, and producing simple, perfect protection function and so on. Made with discrete components, if carefully designed, in terms of efficiency and distortion is much better than the integrated amplifiers. COMS in the power stage tube this design, low power consumption, small distortion, low noise, high performance and good stability characteristics, and displayed in real time unit efficiency, DC power supply and output power. Can be widelyused in measuring systems and control systems. Keywords:Low-frequency power amplifiers MOS tube NE5534OCL目录1 系统电路设计 (1)1.1 系统总体方案 (1)1.2 系统硬件设计 (1)1.3 单元电路设计 (2)1.3.1 前置放大器的分析与设计 (2)1.3.2 功率放大级的设计 (3)1.3.3 带阻滤波器的分析与设计 (5)1.3.4 峰值检测 (7)1.3.5 稳压直流电源的设计 (8)1.3.6 显示模块 (9)2 软件设计 (9)2.1 系统流程图 (9)2.2 相关算法 (10)2.2.1 输出功率计算 (10)2.2.2 电源输出功率计算 (10)2.2.3 整机效率计算 (10)3 测试方法与结果分析 (11)3.1 测试仪器 (11)3.2 输出噪声电压有效值测试 (11)3.3 放大倍数的测试 (11)3.4 输入电阻的测试 (12)3.5 通频带的测试 (12)3.6 低频功率放大器效率测试 (13)4 结束语 (14)附录1: 功率放大器电路原理图 (15)附录2: 液晶显示PORTUES仿真图 (16)附录3: 显示程序 (17)参考文献 (28)低频功率放大器的设计与制作1 系统电路设计1.1 系统总体方案本系统是由前置放大器,带阻滤波器,功率放大级,数据采集,峰值检测和液晶显示等六个部分构成。

低频功率放大器设计

低频功率放大器设计低频功率放大器是电子领域中常见的一种电路元件,其主要作用是将输入信号进行放大,从而使得输出信号具有较大的功率。

是工程技术中一个重要的研究方向,对于提高放大器的性能、降低功耗、增加稳定性有着重要意义。

在低频功率放大器设计中,首先需要确定放大器的工作频率范围。

在设计低频功率放大器时,需要考虑到信号的频率范围,以及不同频率下的放大器增益和带宽等参数。

同时,还需要考虑到放大器的稳定性和线性度,以确保输出信号与输入信号之间的保真度。

在选择低频功率放大器的器件时,需要考虑到器件的参数以及工作特性。

常见的低频功率放大器器件包括三极管、场效应管等。

在选择器件时,需要考虑到器件的最大功率承受能力、频率响应等参数,以保证放大器的性能和稳定性。

低频功率放大器设计中一个重要的考虑因素是功率效率。

功率效率是指放大器输出功率与输入功率之比,通常以百分比来表示。

提高功率效率是低频功率放大器设计中的一个重要目标,可以通过优化电路结构、选择合适的器件等方式来实现。

此外,在低频功率放大器设计中还需要考虑到电路的稳定性和抗干扰能力。

稳定性是指放大器对于外部环境变化的适应能力,抗干扰能力是指放大器对于外部干扰信号的抵抗能力。

通过合理设计电路结构、添加滤波器等方式可以提高放大器的稳定性和抗干扰能力。

在低频功率放大器设计中,电路的仿真和验证是一个重要的环节。

通过使用仿真软件对设计的放大器电路进行仿真分析,可以评估电路的性能和特性,进而进行调整和优化。

同时,通过实际的实验验证,可以验证仿真结果的准确性,确保设计的放大器电路符合要求。

梳理一下本文的重点,我们可以发现,低频功率放大器设计涉及到多个方面的知识和技术,需要综合考虑电路结构、器件选择、功率效率、稳定性和抗干扰能力等因素。

只有在全面考虑这些因素的基础上,才能设计出性能优良、稳定可靠的低频功率放大器。

希望通过不断的研究和实践,能够不断提高低频功率放大器设计水平,为电子领域的发展做出贡献。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

?????

R9 R1 ???? C2 2 6 3 8 1 VR3 1 IC1 IC2 R6 R2 R7 C32 C7 IC3 VR3 4 0 1 R10 1 4 4 7 7 C5 T2 C6 3 8 3 8 R13 R15 3 1 R4 2 6 7 7 C10 R8 2 6 C17 R14 2

VR4 R21 7 C20 T5 6 8 R18 1 4 IC5 R19 IC6 4 R20 C27 R25 7 7 R24 2 6 3 8 R26 1 4 IC9 IC8 1 4 3 8 7 R16 R17 2 6 3 8 2 6 Vo

改进的低频锁相放大器框图

输入

带通 滤波 器

模拟 移相 器

同步 积分 器

PSD

积分器 与直流 放大器

脉冲产 生电路

方波整 形电路

直流 输出

低频锁相放大器电路图

-12v R12 C13 D1 C1 C11 C24 D4 -12 R23 1 2 3 4 5 6 7 8 S4 VDD S6 S2 OUT S1 S7 S0 CD4051 S5 S3 INH A VEE B VSS C IC4 16 15 14 13 12 11 10 9 R11 C14 D2 ????? 1 2 3 4 5 6 7 8 S4 VDD S6 S2 OUT S1 S7 S0 CD4051 S5 S3 INH A VEE B VSS C IC7 R3 R5 C12 16 15 14 13 12 11 10 9 D3 C23 T4 +12v R22 +12v

进一步改进的低频锁相放大器

当被测信号与参考信号的相位改变 必须调整移相器的参数, 时,必须调整移相器的参数,再进行调 这样有很多不便。 试,这样有很多不便。故在上述改进中 加入锁相环技术。 加入锁相环技术。使其产生与被测信号 的频率和相位相同的方波信号。 的频率和相位相同的方波信号。

锁相环结构框图

积分器 vc 压控振 荡器

fo

改进后的锁相放大器框图

输入 信号

带通滤 波器

同步积 分器

PSD

积分器 与直流 放大器

锁相环 电路

直流 输出

改进后的锁相放大电路图

-12v R12 C13 D1 -12 R23 C1 C11 C24 D4 1 2 3 4 5 6 7 8 S4 VDD S6 S2 OUT S1 S7 S0 CD4051 S5 S3 INH A VEE B VSS C IC4 16 15 14 13 12 11 10 9 R11 C14 D2 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 C23 T4 +12v R22 +12v S4 VDD S6 S2 OUT S1 S7 S0 CD4051 S5 S3 INH A VEE B VSS C IC7 C12 R3 R9 R1 ? ? ? ? C2 2 6 3 8 1 R10 IC1 IC3 R2 C32 R19 1 4 4 U6 1 2 3 4 5 6 7 8 PP VDD PC1O ZENER COM IN SING IN VCO O PC2O INHIBIT R2 C1A R1 C1B DE OUT VSS VCO CD4046 IN C8 2.2UF 16 15 14 13 12 11 10 9 +12v R15 1M R14 100K R16 100K R26 R24 R25 7 C27 3 8 R13 R15 IC5 3 8 1 4 R18 1 4 IC6 3 8 7 7 C10 R8 2 6 C17 7 R14 2 6 C20 T5 7 R16 R17 2 6 R20 VR4 R21 D3

低频锁相放大器设计

典型的锁相放大器设计

前置 放大 器 触发 电路 带通 滤波 器 可调 移相 器 交流 放大 器 方波 发生 器

PSD

x(t)

积分 器与 直流 放大 器

输出

r(t)

改进的低频锁相放大器

由于在常规低频设计时, 由于在常规低频设计时,对相敏检 测后的半正弦信号进行滤波滤成平稳的 直流信号时难度较大, 直流信号时难度较大,故在信号通道先 用模拟移相器实现相位移动, 用模拟移相器实现相位移动,电路简单 易行。 易行。经过精心调试可达到移相精度要 求。而同步积分电路通过积分使正弦信 号转变为近似的方波信号。 号转变为近似的方波信号。

C7 0.01uF

2 6 6 3 8 8 1 4 IC9 IC8 Vo

7 2 3 1 4

? ? ? ? ?

谢 谢

同步积分滤波器

对周期信号进行周期重复测量,同步、 对周期信号进行周期重复测量,同步、准确积累起 可使信号幅度越积越大。由于噪声是随机的, 来,可使信号幅度越积越大。由于噪声是随机的,不具 有重复性,在不同周期的对应点的值有正有负,积累后 有重复性,在不同周期的对应点的值有正有负, 可部分抵消。因而噪声增长不如信号增长得快。 可部分抵消。因而噪声增长不如信号增长得快。这样信 噪比得到很大提高, 噪比得到很大提高,可使淹没在噪声中的信号被检测出 来。 实现同步累积的条件: 实现同步累积的条件: 1、信号能重复,即要求信号是周期的。 、信号能重复,即要求信号是周期的。 2、能同步累积,即要求有一个与待测信号相位差 、能同步累积, 固定的参考信号。 固定的参考信号。 3、累积完后信号能保持一段时间。 、累积完后信号能保持一段时间。