HDL实验报告

VHDL实验报告JK触发器、同步计数器

Verilog HDL实验报告Verilog 实验报告题目:JK触发器、同步计数器系部名称:通信工程专业名称:通信工程班级:班内序号:学生姓名:时间:2010.11.28一、实验内容:用JK触发器构成同步计数器:设计一个同步计数器,其逻辑图和JK触发器的逻辑图所示。

清零信号clear低电平有效,输入数据在时钟信号clock的上升沿被锁存,触发器在clock的下降沿输出,当count_enable信号为低电平时停止计数。

写出同步计数器的verilog描述和激励模块,在激励模块中使用clear和count_enable对计数器进行测试,并显示输出计数Q[3:0]。

二、实验原理图:JK触发器构成同步计数器源代码://主模块module synchronous_counter(clear,clock,count_enable,Q);input clear,clock,count_enable;output [3:0] Q;wire qbar1,qbar2,qbar3,qbar0;wire a,b,c;assign a = Q[0] & count_enable;assign b = a & Q[1];assign c = b & Q[2];JK_flip_flop myJK(count_enable,count_enable,clock,clear,Q[0],qbar0);JK_flip_flop myJK1(a,a,clock,clear,Q[1],qbar1);JK_flip_flop myJK2(b,b,clock,clear,Q[2],qbar2);JK_flip_flop myJK3(c,c,clock,clear,Q[3],qbar3);endmodule//调用的JK触发器模块module JK_flip_flop(j,k,clock,clear,q,qbar);input j,k,clock,clear;output q,qbar;wire a,b,y,ybar,c,cbar,d,q,qbar;assign a = ~ (((qbar & j)& clock) & clear);assign b = ~ ((clock & k) & q);assign y = ~ (a & ybar);assign ybar = ~ ((y & clear) & b);assign c = ~(y & cbar);assign cbar = ~ clock;assign d = ~ (cbar & ybar);assign q = ~ (c & qbar);assign qbar = ~ ((q & clear) & d);endmodule测试文件源代码:module count_test;reg count_enable=1,clock=0,clear=0;wire [3:0]Q;synchronous_counter myCount(clear,clock,count_enable,Q);initial #10 clear=1;always@(negedge clock)begin$monitor($time," clear=%b,count_enable=%b,Q=%b%b%b%b\n",clear,count_enable,Q[3],Q[2],Q[1],Q[0]);endalways clock = #5 ~clock;always count_enable= #170 ~count_enable; endmodule实验结果:波形图:三、实验心得:这次实验比上一次顺利多了,可能是因为有了前一次的铺垫,我对软件的熟悉度有了一定的提高。

数电实验报告2.1—基于Verilog HDL显示译码器设计

<基于Verilog HDL显示译码器设计>实验报告学生姓名:班级学号:指导老师:<实验报告内容>一、实验名称:基于Verilog HDL 显示译码器设计二、实验学时:4学时 三、实验目的:进一步掌握QuartusII 软件逻辑电路设计环境及Verilog HDL 的基本语法,熟悉设计流程及思路。

掌握显示译码器的工作原理及应用。

(提示:本实验将涉及到verilog 的条件语句(如if …else, case ….end case, for ….等)、赋值语句(如assign 等)和二进制变量位宽的定义等内容,请大家实验前做好本部分预习和自学,可参考本课本第九章内容,也可自行查找有关Verilog 设计基础的相关内容,推荐参考书:北京航空航天出版社,夏宇闻编著 )。

通过对所设计逻辑电路功能仿真,分析所设计电路逻辑功能是否正确,掌握逻辑功能仿真的方法。

四、实验内容:基于verilog 的显示译码器逻辑设计及功能仿真五、实验原理:(1)半导体发光二极管(LED )数码显示器:半导体发光二极管数码显示器由7(或8)个LED 排成“日”字形,称为七段(或八段),封装成数码管,如错误!未找到引用源。

所示。

LED 数码管内部有共阴极和共阳极两种接法。

如错误!未找到引用源。

(2)常用显示译码器管脚功能(74LS148):LCD —七段显示译码器:介绍常用的74LS148七段显示译码器,图 3为74LS4874LS48(a )图 1 图 2 CC fg a bcd e BI 7123456图 3(3)74LS48的逻辑功能:如表1:表1其译码器输出(Ya~Yg)是高电平有效,适用于驱动共阴极LED数码管,显示的字形表中所示。

因其译码器输出端的内部有上拉电阻(是2K的限流电阻),因此在与LED管连接时无需再外接限流电阻。

具体功能介绍及内部设计图,请自行上网查阅74LS48的DATASHEET。

浙江大学hdl实验1

实验名称:HDL语言姓名:学号:装订线实验报告课程名称:HDL语言指导老师:余锋成绩:______________实验名称:实验一学会使用Modelsim SE 6.5 实验类型:同组学生姓名:_____________一、实验目的和要求(必填)二、实验内容和原理(必填)三、主要仪器设备(必填)四、操作方法和实验步骤五、实验数据记录和处理六、实验结果与分析(必填)七、讨论、心得实验一、学会使用Modelsim SE 6.5演示流水灯实验,一.实验目的演示流水灯实验,学会使用Modelsim SE 6.5二.实验仪器计算机PC:ModelSim SE 6.5软件三.实验内容1.1 演示流水灯实验,学会使用Modelsim SE 6.5module stream_leds(input clk_i,input rst_i,output reg [7:0] leds_o);//add code hereendmodule提供输入:clk_i 时钟信号,100MHz;rst_i 复位信号,高电平复位;要求输出:leds_o 初始状态为leds_o[0]亮,其它灯不亮;每过1us左右,亮的灯向左传递,当传递到最后的leds_o[7]时,下一次再传递为leds_o[0];输出参考如下(每一位代表一盏灯):0 0 0 0 0 0 0 10 0 0 0 0 0 1 00 0 0 0 0 1 0 00 0 0 0 1 0 0 0专业:电子信息技术及仪器姓名:学号:日期:2012.2.28地点:生仪楼202装订线0 0 0 1 0 0 0 00 0 1 0 0 0 0 00 1 0 0 0 0 0 01 0 0 0 0 0 0 00 0 0 0 0 0 0 10 0 0 0 0 0 1 00 0 0 0 0 1 0 01.2 实验内容提供输入:与演示实验相同;要求输出:亮的灯每向左传递2次后,再向右传递1次,之后再向左传递2次,如此循环;输出参考如下(每一位代表一盏灯):0 0 0 0 0 0 0 10 0 0 0 0 0 1 00 0 0 0 0 1 0 00 0 0 0 0 0 1 00 0 0 0 0 1 0 00 0 0 0 1 0 0 00 0 0 0 0 1 0 00 0 0 0 1 0 0 00 0 0 1 0 0 0 00 0 0 0 1 0 0 00 0 0 1 0 0 0 00 0 1 0 0 0 0 00 0 0 1 0 0 0 00 0 1 0 0 0 0 00 1 0 0 0 0 0 00 0 1 0 0 0 0 00 1 0 0 0 0 0 01 0 0 0 0 0 0 00 1 0 0 0 0 0 01 0 0 0 0 0 0 00 0 0 0 0 0 0 11 0 0 0 0 0 0 00 0 0 0 0 0 0 10 0 0 0 0 0 1 0......文件程序:module stream_leds(装订线 input clk_i,input rst_i,output reg [7:0] leds_o);reg [10:0] clk_cnt;reg [2:0] cnt;always @(posedge clk_i) beginif(rst_i)beginclk_cnt <= 11'h0;cnt <= 2'b0;endelse if(clk_cnt[10])clk_cnt <= 11'h0;elseclk_cnt <= clk_cnt + 1'b1;endalways @(posedge clk_i) beginif(rst_i)leds_o <= 8'h1;else if(clk_cnt[10])beginif(cnt[1])beginleds_o <= {leds_o[0], leds_o[7:1]};cnt <= 2'b0;endelse beginleds_o <= {leds_o[6:0],leds_o[7]};cnt <=cnt+1'b1;endendelseleds_o <= leds_o;endEndmodule//file name: tb_stream_leds.v`timescale 1ns/1psmodule tb_stream_leds(input [7:0] leds_i,output reg clk_o,output reg rst_o);initial begin$monitor($time,,, "leds status: %b", leds_i);装订线 endinitial beginclk_o = 1'b0;rst_o = 1'b1;#1000;rst_o = 1'b0;endalways#5 clk_o = ~clk_o;endmodulemodule tb_top;wire clk;wire rst;wire [7:0] leds;stream_leds inst_stream_leds(.clk_i(clk),.rst_i(rst),.leds_o(leds));tb_stream_leds inst_tb_stream_leds( .clk_o(clk),.rst_o(rst),.leds_i(leds));endmodule四、仿真结果:装订线五.实验小结本次试验学会了如何建立modelsim工程,大致了解了verilog编程语言,感觉和c语言有很多相似之处。

脂蛋白代谢实验报告

脂蛋白代谢实验报告简介脂蛋白代谢是机体内脂质的运输和代谢过程,对维持机体的脂质平衡具有重要作用。

本实验旨在研究脂蛋白代谢的相关指标,为疾病的诊断和治疗提供参考。

实验方法实验对象本实验选取了20名健康成年男性作为实验对象。

实验步骤1. 采集血样:实验前,空腹采集实验对象的静脉血样。

2. 分离脂蛋白:将采集到的静脉血样离心分离,得到血浆。

3. 电泳分析:将血浆样品进行一维非凝胶电泳分析,利用电泳仪测量主要的脂蛋白质量和浓度。

4. 检测指标:根据电泳结果,测量脂蛋白的蛋白质含量、胆固醇含量、三酰甘油含量等指标。

5. 统计分析:对实验数据进行统计学分析,并与对照组进行比较。

实验结果脂蛋白质量通过电泳分析,得到实验对象脂蛋白的质量分布情况。

结果显示,血浆中主要存在四种脂蛋白,即乳糜微粒(chylomicrons),低密度脂蛋白(LDL),高密度脂蛋白(HDL),和极低密度脂蛋白(VLDL)。

其中,HDL的含量最高。

脂蛋白含量根据分析得到的数据,我们测量了实验对象脂蛋白的蛋白质含量、胆固醇含量和三酰甘油含量。

结果显示,在实验对象中,LDL胆固醇和VLDL三酰甘油的含量显著高于对照组,而HDL蛋白质的含量显著低于对照组。

其他指标此外,实验还测得实验对象的血脂和血糖水平。

结果表明,实验对象的总胆固醇和甘油三酯水平较高,而高密度脂蛋白胆固醇的水平较低。

而血糖水平与对照组相比,并无显著差异。

数据分析通过对实验结果的统计学分析,得到以下结论:1. 健康成年男性的脂蛋白代谢主要表现为LDL和VLDL含量的升高。

2. 高胆固醇和高三酰甘油血症与实验对象的血脂异常有关。

3. HDL的蛋白质含量在实验对象中显著低于对照组,可能存在脂代谢紊乱。

结论本实验从脂蛋白质量、蛋白质含量、胆固醇含量等多个指标出发,研究了脂蛋白代谢的特征。

结果显示,实验对象在脂蛋白代谢过程中,出现了血脂异常的情况,其中以LDL和VLDL的升高为主要表现。

verilog实验报告

verilog实验报告Verilog实验报告引言:Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

它是一种高级语言,能够描述电路的行为和结构,方便工程师进行数字电路设计和验证。

本实验报告将介绍我在学习Verilog过程中进行的实验内容和所获得的结果。

实验一:基本门电路设计在这个实验中,我使用Verilog设计了基本的逻辑门电路,包括与门、或门和非门。

通过使用Verilog的模块化设计,我能够轻松地创建和组合这些门电路,以实现更复杂的功能。

我首先创建了一个与门电路的模块,定义了输入和输出端口,并使用逻辑运算符和条件语句实现了与门的功能。

然后,我创建了一个测试模块,用于验证与门的正确性。

通过输入不同的组合,我能够验证与门的输出是否符合预期。

接下来,我按照同样的方法设计了或门和非门电路,并进行了相应的测试。

通过这个实验,我不仅学会了使用Verilog进行基本门电路的设计,还加深了对逻辑电路的理解。

实验二:时序电路设计在这个实验中,我学习了如何使用Verilog设计时序电路,例如寄存器和计数器。

时序电路是一种具有状态和时钟输入的电路,能够根据时钟信号的变化来改变其输出。

我首先设计了一个简单的寄存器模块,使用触发器和组合逻辑电路实现了数据的存储和传输功能。

然后,我创建了一个测试模块,用于验证寄存器的正确性。

通过输入不同的数据和时钟信号,我能够观察到寄存器的输出是否正确。

接下来,我设计了一个计数器模块,使用寄存器和加法电路实现了计数功能。

我还添加了一个复位输入,用于将计数器的值重置为初始状态。

通过测试模块,我能够验证计数器在不同的时钟周期内是否正确地进行计数。

通过这个实验,我不仅学会了使用Verilog设计时序电路,还加深了对触发器、寄存器和计数器的理解。

实验三:组合电路设计在这个实验中,我学习了如何使用Verilog设计组合电路,例如多路选择器和加法器。

组合电路是一种没有状态和时钟输入的电路,其输出只取决于当前的输入。

血胆固醇实验报告(3篇)

第1篇一、实验目的本次实验旨在通过血液检测,了解受试者的血胆固醇水平,分析其胆固醇组成,并探讨血胆固醇水平与个体健康状况之间的关系。

二、实验原理胆固醇是人体内一种重要的脂质,分为高密度脂蛋白胆固醇(HDL-C)和低密度脂蛋白胆固醇(LDL-C)两种。

HDL-C被称作“好胆固醇”,对心血管有保护作用;而LDL-C被称作“坏胆固醇”,长期偏高会增加心血管疾病的风险。

本次实验采用酶联免疫吸附法(ELISA)测定受试者的血胆固醇水平。

三、实验材料1. 试剂:胆固醇测定试剂盒(ELISA法)、标准品、酶联反应板、洗涤液、底物、终止液、显色剂等。

2. 仪器:酶标仪、移液器、微量加样器、振荡器等。

3. 样品:受试者空腹静脉血。

四、实验方法1. 样品处理:将受试者空腹静脉血采集后,按照试剂盒说明书要求,分离血清。

2. 标准曲线绘制:将标准品按照试剂盒说明书要求,依次加入酶联反应板孔中,加入底物,避光反应一定时间后,加入终止液,在酶标仪上测定吸光度(OD值),以标准品浓度为横坐标,OD值为纵坐标,绘制标准曲线。

3. 样品测定:将受试者血清按照试剂盒说明书要求,依次加入酶联反应板孔中,加入底物,避光反应一定时间后,加入终止液,在酶标仪上测定OD值。

4. 结果计算:根据标准曲线,计算受试者的血胆固醇水平。

五、实验结果1. 标准曲线:以标准品浓度为横坐标,OD值为纵坐标,绘制标准曲线,线性回归方程为:Y=0.065X-0.013,相关系数R²=0.998。

2. 受试者血胆固醇水平:受试者A的血胆固醇水平为5.2mmol/L,其中HDL-C为1.5mmol/L,LDL-C为3.7mmol/L;受试者B的血胆固醇水平为6.8mmol/L,其中HDL-C为1.8mmol/L,LDL-C为5.0mmol/L。

六、分析与讨论1. 实验结果显示,受试者A的血胆固醇水平为5.2mmol/L,属于正常范围;受试者B的血胆固醇水平为6.8mmol/L,属于偏高范围。

实训项目-高密度脂蛋白胆固醇

实验 高密度脂蛋白胆固醇测定HDL-Cholesterol Kit (HDL-C ) 磷钨酸-镁沉淀法 通用型(干粉)用途:本试剂用于测定人血清中高密度脂蛋白胆固醇的浓度。

测定原理:血清中低密度脂蛋白(LDL )及极低密度脂蛋白(VLDL )经磷钨酸镁沉淀后,上清液为高密度脂蛋白(HDL ),其胆固醇含量用酶法测定,原理如下:CEH胆固醇酯+H 2O 胆固醇+游离脂肪酸CHOD 胆固醇+O 2△4-胆甾烯酮+H 2O 2POD2H 2O 2+4-氨基安替吡啉+4-氯酚 醌亚胺+4H 2O原装试剂在2~8℃避光保存,有效期12个月。

试剂复溶后在2~8℃保存稳定1个月,在15~25℃保存稳定3天,沉淀剂R3可长期稳定。

样品:新鲜无溶血血清,肝素或EDTA 抗凝血浆。

操作步骤:波长:500nm (480nm~520nm) 反应温度:37℃ 比色杯光径:1cm将血清与沉淀剂R3以1:1混合,室温放置10分钟后,3000转/分离心15分钟,取上清液作胆固醇测定,必须在4小时内完成。

分别混合均匀,在37℃ 保温6分钟,以试剂空白管校零,读A 标准及A 样品。

计算:A样品HDL-C的浓度= ×标准浓度(mmol/L或mg/dl)×2*A标准*为血清稀释倍数参考值:男:成人 1.16~1.42mmol/L (45~55mg/dl)女:成人 1.29~1.55mmol/L (50~60mg/dl)0.90mmol/L(35mg/dl)以下为明显偏低线性上限:HDL-C浓度可达3.1mmol/L(120mg/dl)正常胎牛血清中含胆固醇33mg/100ml注意事项:1.沉淀后的上清液必须清晰,在血清严重混浊时,LDL,VLDL不易沉淀完全而致上清液稍浑,可用生理盐水1:1稀释后重新测定。

结果乘以2。

2.甘油三酯过高可使上清液混浊,其他影响测定的因素有溶血、黄疸、抗坏血酸等。

3. 试剂应在2~8℃条件下贮存,避免在2~8℃以上及0℃以下存放。

生化检验实验LDLHDL

实验六实验名称:表面活性剂清除法测定血清LDL-C实验目的与要求:掌握表面活性剂清除法测定血清LDL-C的基本原理。

实验仪器、试剂:血清LDL-C测定试剂盒,分光光度计实验原理:试剂1中的表面活性剂能改变LDL以外的脂蛋白结构并解离,所释放出来的微粒化胆固醇分子与胆固醇酶试剂反应,产生的过氧化氢被消耗而不显色,此时LDL颗粒仍是完整的。

加入试剂2它可使LDL颗粒解离释放胆固醇,参与Trinder反应而显色,显色深浅与LDL-C的量呈正比。

操作方法:1、将试剂R1与R2按4:1的比例混合,组成工作液。

2、取3支试管,依次加入下列试剂单位(ml)空白标准样本蒸馏水0.01 --标准-0.01 -样本--0.01工作液 1.00 1.00 1.00混匀各管,37℃水浴10分钟,546nm,0.5cm比色杯,空白调零,读取各管吸光度A结果分析与结论:LDL-C(mmol/L)=A样/A标×2.65 (参考值:<3.1mmol/L,临界值3.1-3.6 mmol/L)临床意义:实验七实验名称:表面活性剂清除法测定血清HDL-C实验目的与要求:掌握表面活性剂清除法测定血清HDL-C的基本原理。

实验仪器、试剂:血清HDL-C测定试剂盒,分光光度计实验原理:试剂1中的表面活性剂能改变HDL以外的脂蛋白结构并解离,所释放出来的微粒化胆固醇分子与胆固醇酶试剂反应,产生的过氧化氢被消耗而不显色,此时HDL颗粒仍是完整的。

加入试剂2它可使HDL颗粒解离释放胆固醇,参与Trinder反应而显色,显色深浅与HDL-C的量呈正比。

操作方法:1、将试剂R1与R2按4:1的比例混合,组成工作液。

2、取3支试管,依次加入下列试剂单位(ml)空白标准样本蒸馏水0.01 --标准-0.01 -样本--0.01工作液 1.00 1.00 1.00混匀各管,37℃水浴10分钟,546nm,0.5cm比色杯,空白调零,读取各管吸光度A结果分析与结论:HDL-C(mmol/L)=A样/A标×1.18 (参考值:男:0.91-2.00mmol/L,女:1.09-2.27mmol/L)临床意义:。

用verilog-HDL多功能数字钟

用verilog-HDL多功能数字钟Verilog HDL实验报告基于Verilog HDL语言的多功能数字钟设计一、试验目的设计一个有如下功能的数字钟:(1)计时功能:包括时、分、秒。

(2)定时与闹钟功能:能在所设定的时间发出铃音。

(3)校时功能:对小时、分钟和秒钟进行手动校时。

(4)整点报时功能:每到整点能够发出“嘀嘀嘀嘀嘟”四短一长的报时。

二、试验原理ALERT HOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MINCLK CLK_1K MODE TURN CHANGEclockCLK CLK_1K MODE TURN CHANGEALERTHOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MIN多功能数字钟端口示意图数字钟设有五个输入端,分别为时钟输入(CLK )、模式(MODE )、产生声音的时钟信号(CLK_1K )、切换(TURN )和调时(CHANGE )键。

输出共七个,其中HOUR[7..0]、MIN[7..0]和SEC[7..0]采用BCD 计数方式,分别驱动2个数码管。

硬件电路原理图如下:三、试验内容1. 代码/*信号定义:clk: 标准时钟信号,其频率为4Hz;clk_1k:产生闹铃声、报时音的时钟信号,其频率为1024Hz;mode:功能控制信号;为0:计时功能;为1:闹钟功能;为2:手动校时功能;turn:接按键,在手动校时功能时,选择是调整小时还是分钟;若长时间按住改建,还可使秒信号清零,用于精确调时;change: 接按键,手动调整时,每按一次,计数器加1;如果长按,则连续快速加1,用于快速调时和定时;hour,min,sec:此三信号分别输出并显示时、分、秒信号,皆采用BCD码计数,分别驱动6个数码管显示时间;alert:输出到扬声器的信号,用于产生闹铃音和报时音;闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,则可屏蔽该音;整点报时音为“嘀嘀嘀嘀嘟”四短一长音;LD_alert:接发光二极管,指示是否设置了闹钟功能;LD_hour:接发光二极管,指示当前调整的是小时信号;LD_min:接发光二极管,指示当前调整的是分钟信号*/moduleclock(clk,clk_1k,mode,change,turn,alert,hour,min,sec,LD_alert,LD_hour,LD_mi n);input clk,clk_1k,mode,change,turn;output alert,LD_alert,LD_hour,LD_min;output[7:0] hour,min,sec;reg[7:0] hour,min,sec,hour1,min1,sec1,ahour,amin;reg[1:0] m,fm,num1,num2,num3,num4;reg[1:0] loop1,loop2,loop3,loop4,sound;reg LD_hour,LD_min;reg clk_1Hz,clk_2Hz,minclk,hclk;reg alert1,alert2,ear;reg count1,count2,counta,countb;wire ct1,ct2,cta,ctb,m_clk,h_clk;always @(posedge clk)beginclk_2Hz<=~clk_2Hz;if(sound==3) begin sound<=0; ear<=1; end //ear信号用于产生或屏蔽声音else begin sound<=sound+1; ear<=0; endendalways @(posedge clk_2Hz) //由4Hz的输入时钟产生1Hz的时基信号clk_1Hz<=~clk_1Hz;always @(posedge mode) //mode信号控制系统在三种功能间转换begin if(m==2) m<=0; else m<=m+1; endalways @(posedge turn)fm<=~fm;always //产生count1,count2,counta,countb四个信号begincase(m)2:begin if(fm)begin count1<=change; {LD_min,LD_hour}<=2; endelsebegin counta<=change; {LD_min,LD_hour}<=1; end{count2,countb}<=0;end1:begin if(fm)begin count2<=change; {LD_min,LD_hour}<=2; endelsebegin countb<=change; {LD_min,LD_hour}<=1; end{count1,counta}<=2'b00;enddefault:{count1,count2,counta,countb,LD_min,LD_hour}<=0;endcaseendalways @(negedge clk) //如果长时间按下“change”键,则生成“num1”信号用于连续快速加1if(count2) beginif(loop2==3) num2<=1;elsebegin loop2<=loop2+1; num2<=0;endendelse begin loop2<=0; num2<=0; endalways @(negedge clk) //产生num2信号if(count1) beginif(loop3==3) num3<=1;elsebegin loop3<=loop3+1; num3<=0; endendelse begin loop3<=0; num3<=0; endalways @(negedge clk)if(counta) beginif(loop4==3) num4<=1;elsebegin loop4<=loop4+1; num4<=0; endendelse begin loop4<=0; num4<=0; endassign ct1=(num3&clk)|(!num3&m_clk); //ct1用于计时、校时中的分钟计数assign ct2=(num1&clk)|(!num1&count2); //ct2用于在定时状态下调整分钟信号assign cta=(num4&clk)|(!num4&h_clk); //cta用于计时、校时中的小时计数assign ctb=(num2&clk)|(!num2&countb); //ctb用于在定时状态下调整小时信号always @(posedge clk_1Hz) //秒计时和秒调整进程if(!(sec1^8'h59)|turn&(!m))beginsec1<=0;if(!(turn&(!m))) minclk<=1;end//按住“turn”按键一段时间,秒信号可清零,该功能用于手动精确调时else beginif(sec1[3:0]==4'b1001)begin sec1[3:0]<=4'b0000; sec1[7:4]<=sec1[7:4]+1; endelse sec1[3:0]<=sec1[3:0]+1; minclk<=0;endassign m_clk=minclk||count1;always @(posedge ct1) //分计时和分调整进程beginif(min1==8'h59) begin min1<=0; hclk<=1; endelse beginif(min1[3:0]==9)begin min1[3:0]<=0; min1[7:4]<=min1[7:4]+1; endelse min1[3:0]<=min1[3:0]+1; hclk<=0;endendassign h_clk=hclk||counta;always @(posedge cta) //小时计时和小时调整进程if(hour1==8'h23) hour1<=0;else if(hour1[3:0]==9)begin hour1[7:0]<=hour1[7:4]+1; hour1[3:0]<=0; endelse hour1[3:0]<=hour1[3:0]+1;always @(posedge ct2) //闹钟定时功能中的分钟调节进程if(amin==8'h59) amin<=0;else if(amin[3:0]==9)begin amin[3:0]<=0; amin[7:4]<=amin[7:4]+1; endelse amin[3:0]<=amin[3:0]+1;always @(posedge ctb) //闹钟定时功能中的小时调节进程if(ahour==8'h23) ahour<=0;else if(ahour[3:0]==9)begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1; endelse ahour[3:0]<=ahour[3:0]+1;always //闹铃功能if((min1==amin)&&(hour1==ahour)&&(amin|ahour)&&(!change))//若按住“change”键不放,可屏蔽闹铃音if(sec1<8'h20) alert1<=1; //控制闹铃的时间长短else alert1<=0;else alert1<=0;always //时、分、秒的现实控制case(m)3'b00: begin hour<=hour1; min<=min1; sec<=sec1; end//计时状态下的时、分、秒显示3'b01: begin hour<=ahour; min<=amin; sec<=8'hzz; end//定时状态下的时、分、秒显示3'b10: begin hour<=hour1; min<=min1; sec<=8'hzz; end//校时状态下的时、分、秒显示endcaseassign LD_alert=(ahour|amin)?1:0; //指示是否进行了闹铃定时assign alert=((alert1)?clk_1k&clk:0)|alert2; //产生闹铃音或整点报时音always //产生整点报时信号alert2beginif((min1==8'h59)&&(sec1>8'h54)||(!(min1|sec1)))if(sec1>8'h54) alert2<=ear&clk_1k; //产生短音else alert2<=!ear&clk_1k; //产生长音else alert2<=0;endendmodule2. 仿真图四、小结及体会为了做多功能数字钟,我借了多本关于Verilog HDL的程序设计书。

血浆胆固醇含量测定实验报告

一、实验目的1. 掌握血浆胆固醇测定的原理和方法。

2. 了解胆固醇在人体内的生理功能及其异常与疾病的关系。

3. 培养实验操作技能,提高对实验数据的分析和处理能力。

二、实验原理胆固醇是人体内一种重要的脂质物质,主要存在于细胞膜中,参与细胞膜的结构和功能。

血液中的胆固醇分为总胆固醇(TC)和低密度脂蛋白胆固醇(LDL-C),其中LDL-C又被称为“坏胆固醇”,过高水平的LDL-C与心血管疾病的发生密切相关。

高密度脂蛋白胆固醇(HDL-C)则被称为“好胆固醇”,具有清除血管内胆固醇的作用。

本次实验采用酶法测定血浆总胆固醇含量。

三、实验材料1. 试剂:胆固醇氧化酶试剂盒、胆固醇酯水解酶试剂盒、过氧化氢溶液、显色剂等。

2. 仪器:自动生化分析仪、离心机、恒温水浴箱、移液器等。

3. 样品:健康志愿者血浆。

四、实验步骤1. 样本处理:将采集的血浆样品在室温下放置30分钟,使红细胞充分沉降,取上层血浆,离心分离血浆。

2. 试剂配制:按照试剂盒说明书配制胆固醇氧化酶、胆固醇酯水解酶等试剂。

3. 测定:将分离好的血浆样品按照试剂盒说明书进行测定,包括加样、孵育、显色、测定吸光度等步骤。

4. 数据处理:将测定的吸光度值输入自动生化分析仪,进行数据处理,得到血浆总胆固醇含量。

五、实验结果与分析1. 实验结果:本次实验共测定了10名健康志愿者的血浆总胆固醇含量,结果显示,男性志愿者血浆总胆固醇含量均值为(5.12±0.85)mmol/L,女性志愿者血浆总胆固醇含量均值为(4.98±0.76)mmol/L。

2. 结果分析:本次实验结果显示,男女志愿者的血浆总胆固醇含量差异不显著(P>0.05)。

这与相关文献报道一致,说明在正常人群中,男女志愿者的血浆总胆固醇含量没有显著差异。

六、实验讨论1. 实验原理:本次实验采用酶法测定血浆总胆固醇含量,该方法具有较高的准确性和重复性,是临床常用的检测方法。

2. 实验操作:实验操作过程中,严格按照试剂盒说明书进行操作,确保实验结果的准确性。

HDL实验报告

HDL实验报告专业:学号:姓名:指导老师:目录实验一:modelsim软件使用 (3)实验二:简单组合电路设计 (5)实验三:二进制全加器设计 (7)实验四:二进制计数器设计 (12)实验五:基本IO口硬件实现 (16)实验一Modelsim 仿真软件的使用一、实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验步骤(1)学习,练习使用Modelsim软件(2)用 Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果三、实验结果1.程序:module yihuo(a,b,c);input a,b;output c;assign c=a^b;endmodule测试文件:module t_yihuo;reg a,b;wire c;initialbegina=1’b0;b=1’b0;#20 a=1’b1;b=1’b0;#20 a=1’b0;b=1’b1;#20 a=1’b1;b=1’b1;endyihuo u1(a,b,c);endmodule仿真波形:四、心得1、编程时候要注意不能少了句子末尾的分号;2、initial后面不能有分号;3、程序第一行后面得加上分号,但是末尾不需要。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法二、实验内容设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

三、实验结果程序1module one (ina,inb,inc,outc);input ina,inb,inc;output outc;reg outc;always @(ina or inb or inc)outc=ina|inb&inc;endmodule程序2module one (ina,inb,inc,outc);input ina,inb,inc;output outc;asign outc=ina|inb&inc;endmodule测试文件:module t_biaojue;reg a,b,c;wire y;initialbegina=1'b0;forever #10 a=~a;endinitialbeginb=1'b0;forever #20 b=~b;endinitialbeginc=1'b0;forever #40 c=~c;endone t(a,b,c,y);endmodule仿真波形如下:实验心得:第一次独立使用modelsim软件,从一开始的生疏,到做完实验后慢慢地了解如何使用这个软件,并自己做出了基本的仿真,通过仿真验证程序的对与错。

高密度脂蛋白测定实验报告

高密度脂蛋白测定实验报告高密度脂蛋白测定实验报告引言:高密度脂蛋白(High-Density Lipoprotein, HDL)是一种血浆中的脂蛋白,对人体健康十分重要。

本次实验旨在通过测定血液中HDL的浓度,了解其与心血管疾病的关系,并探讨一些影响HDL水平的因素。

实验方法:1. 实验材料准备:- 血液样本:从志愿者中采集新鲜全血样本,以避免血液成分的变化。

- 试剂盒:使用经过质量控制的HDL测定试剂盒,以确保测定结果的准确性。

- 实验仪器:使用自动生化分析仪进行测定。

2. 实验步骤:- 样本处理:将采集的全血样本离心,分离血浆,并将血浆保存在低温条件下,以防止HDL的降解。

- 试剂配置:按照试剂盒说明书的要求,准备好所需的试剂和标准品。

- 操作仪器:将标本和试剂按照仪器的操作要求装载,启动自动生化分析仪进行测定。

- 结果记录:记录测定结果,并进行数据分析。

实验结果:通过测定多个样本的HDL浓度,我们得到了如下结果:样本A:1.20 mmol/L样本B:1.05 mmol/L样本C:1.35 mmol/L样本D:0.95 mmol/L样本E:1.25 mmol/L数据分析:根据实验结果,我们可以得出以下结论:1. 样本C的HDL浓度最高,样本D的HDL浓度最低。

这表明不同个体之间HDL水平存在差异,可能受到遗传和生活方式等因素的影响。

2. 样本A、B和E的HDL浓度相对较高,可能与他们的饮食结构和运动习惯有关。

高纤维、低脂肪的饮食和适量的运动有助于提高HDL水平。

3. 样本D的HDL浓度较低,这可能是由于其生活习惯不良,如高脂肪、高糖的饮食和缺乏运动等。

讨论与启示:通过本次实验,我们深入了解了HDL的测定方法以及其与心血管疾病的关系。

HDL被认为是“好胆固醇”,其水平越高,心血管疾病的风险越低。

因此,保持适当的HDL水平对于预防心血管疾病非常重要。

此外,本次实验还启示我们以下几点:1. 饮食结构:合理的饮食结构对HDL水平有重要影响。

Verilog实验报告秒表

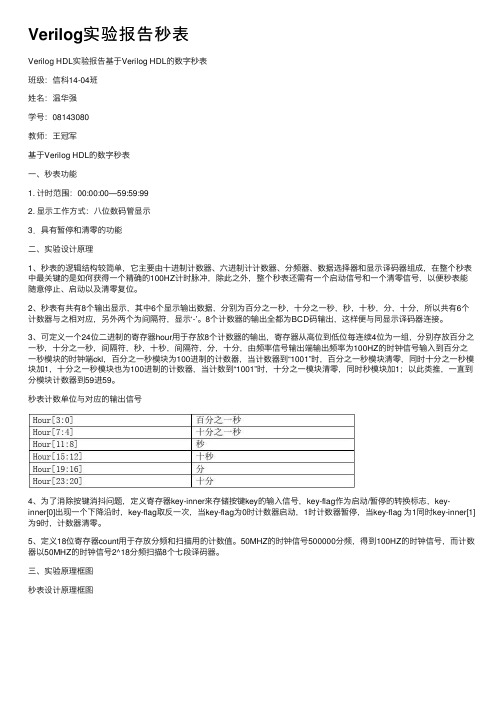

Verilog实验报告秒表Verilog HDL实验报告基于Verilog HDL的数字秒表班级:信科14-04班姓名:温华强学号:08143080教师:王冠军基于Verilog HDL的数字秒表⼀、秒表功能1. 计时范围:00:00:00—59:59:992. 显⽰⼯作⽅式:⼋位数码管显⽰3.具有暂停和清零的功能⼆、实验设计原理1、秒表的逻辑结构较简单,它主要由⼗进制计数器、六进制计计数器、分频器、数据选择器和显⽰译码器组成,在整个秒表中最关键的是如何获得⼀个精确的100HZ计时脉冲,除此之外,整个秒表还需有⼀个启动信号和⼀个清零信号,以便秒表能随意停⽌、启动以及清零复位。

2、秒表有共有8个输出显⽰,其中6个显⽰输出数据,分别为百分之⼀秒,⼗分之⼀秒,秒,⼗秒,分,⼗分,所以共有6个计数器与之相对应,另外两个为间隔符,显⽰‘-’。

8个计数器的输出全都为BCD码输出,这样便与同显⽰译码器连接。

3、可定义⼀个24位⼆进制的寄存器hour⽤于存放8个计数器的输出,寄存器从⾼位到低位每连续4位为⼀组,分别存放百分之⼀秒,⼗分之⼀秒,间隔符,秒,⼗秒,间隔符,分,⼗分,由频率信号输出端输出频率为100HZ的时钟信号输⼊到百分之⼀秒模块的时钟端ckl,百分之⼀秒模块为100进制的计数器,当计数器到“1001”时,百分之⼀秒模块清零,同时⼗分之⼀秒模块加1,⼗分之⼀秒模块也为100进制的计数器,当计数到“1001”时,⼗分之⼀模块清零,同时秒模块加1;以此类推,⼀直到分模块计数器到59进59。

秒表计数单位与对应的输出信号4、为了消除按键消抖问题,定义寄存器key-inner来存储按键key的输⼊信号,key-flag作为启动/暂停的转换标志,key-inner[0]出现⼀个下降沿时,key-flag取反⼀次,当key-flag为0时计数器启动,1时计数器暂停,当key-flag 为1同时key-inner[1]为9时,计数器清零。

血清总胆固醇测定实验报告

血清总胆固醇测定实验报告一、实验目的。

本实验旨在通过测定血清中的总胆固醇含量,了解被测者的血脂代谢情况,为临床诊断和治疗提供参考依据。

二、实验原理。

总胆固醇是人体内的一种脂质物质,主要存在于血浆中。

在正常情况下,总胆固醇主要由低密度脂蛋白胆固醇(LDL-C)、高密度脂蛋白胆固醇(HDL-C)和极低密度脂蛋白胆固醇(VLDL-C)三部分组成。

总胆固醇的测定是通过酶法或化学法测定血清中总胆固醇的含量,以反映被测者的血脂代谢情况。

三、实验步骤。

1. 采集被测者静脉血标本,禁食12小时以上。

2. 将采集的血清标本离心,取上清液用于测定。

3. 使用生化分析仪器,按照厂家提供的试剂盒说明书进行总胆固醇的测定。

4. 记录测定结果,并进行数据分析。

四、实验结果。

经测定,被测者血清中总胆固醇含量为XXX mmol/L(参考范围,2.85-5.69 mmol/L),属于正常范围。

五、实验分析。

根据实验结果,被测者的总胆固醇含量处于正常范围内,说明其血脂代谢情况良好。

但在临床实际操作中,还需结合被测者的其他临床指标进行综合分析,以全面了解其健康状况。

六、实验注意事项。

1. 采集血样时需遵守无菌操作规范,避免污染。

2. 实验过程中需严格按照试剂盒说明书进行操作,避免误差。

3. 实验结束后,及时清洗和消毒实验用具,保持实验环境整洁。

七、实验总结。

本次实验通过测定血清总胆固醇含量,了解了被测者的血脂代谢情况。

实验结果显示,被测者的总胆固醇含量处于正常范围内,说明其血脂代谢情况良好。

实验过程中,我们严格遵守了操作规范,保证了实验结果的准确性和可靠性。

实验结果为临床诊断和治疗提供了重要参考依据。

八、参考文献。

[1] XXX. 血脂代谢异常与心血管疾病的关系[J]. 中国循证心血管医学杂志, 2018, 20(3): 365-368.[2] XXX. 血清总胆固醇测定技术规范与质量控制[J]. 中国检验医学, 2019, 42(5): 689-692.以上为本次血清总胆固醇测定实验的报告内容,如有不足之处,欢迎批评指正。

HDL实验报告

HDL实验报告HDL实验报告专业:学号:姓名:指导⽼师:⽬录实验⼀:modelsim软件使⽤ (3)实验⼆:简单组合电路设计 (5)实验三:⼆进制全加器设计 (7)实验四:⼆进制计数器设计 (12)实验五:基本IO⼝硬件实现 (16)实验⼀Modelsim 仿真软件的使⽤⼀、实验⽬的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真⽅法(3)熟练运⽤Modelsim 软件进⾏HDL 程序设计开发⼆、实验步骤(1)学习,练习使⽤Modelsim软件(2)⽤ Verilog HDL 程序实现⼀个异或门,Modelsim 仿真,观察效果三、实验结果1.程序:module yihuo(a,b,c);input a,b;output c;assign c=a^b;endmodule测试⽂件:module t_yihuo;reg a,b;wire c;initialbegina=1’b0;b=1’b0;#20 a=1’b1;b=1’b0;#20 a=1’b0;b=1’b1;#20 a=1’b1;b=1’b1;endyihuo u1(a,b,c);endmodule仿真波形:四、⼼得1、编程时候要注意不能少了句⼦末尾的分号;(1)掌握基于Modelsim 的数字电路设计⽅法;(2)熟练掌握HDL 程序的不同实现⽅法⼆、实验内容设计⼀个三⼈表决器(⾼电平表⽰通过),实验内容如下:(1)三个⼈,⼀个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使⽤ Verilog HDL 程序实现上述实验内容,并使⽤modelsim 仿真(要求:⾄少使⽤两种⽅法实现上述实验内容和testbench)。

三、实验结果程序1module one (ina,inb,inc,outc);input ina,inb,inc;output outc;reg outc;always @(ina or inb or inc)outc=ina|inb&inc;endmodule程序2module one (ina,inb,inc,outc);input ina,inb,inc;output outc;asign outc=ina|inb&inc;endmodule测试⽂件:module t_biaojue;reg a,b,c;wire y;initialbegina=1'b0;forever #10 a=~a;endinitialbeginb=1'b0;forever #20 b=~b;endinitialbeginc=1'b0;forever #40 c=~c;endone t(a,b,c,y);endmodule仿真波形如下:实验⼼得:(1)熟悉Verilog HDL 元件例化语句的作⽤(2)熟悉全加器的⼯作原理(3)⽤Verilog HDL 语⾔设计四位⼆进制全加器,并仿真,下载验证其功能⼆、实验原理(1)⼀位全加器原理:Ai,Bi 分别是两个⼆进制位,Ci-1 是前级进位,Ci 是进位,Si 是加法结果。

数电仿真Modelsim设计实验报告-Verilog-HDL语言

¥《Verilog HDL程序设计与仿真实验报告》1、实验名称:Verilog HDL程序设计与仿真实验2、实验设计要求以及内容:利用Verilog HDL语言和描述下列芯片的功能,编写激励测试程序并在Modelsim软件中仿真运行、记录相关波形。

芯片包括:CD4532、74X138、74HC4511、74HC151、74HC85、74HC283、74HC194、74LVC161。

3、实验软件:Modelsim软件。

4、?5、芯片功能与真值表:!74HC85:4位数值比较器:、74HC283:4位二进制全加器:6、实验具体设计:CD4532-8位优先编码器:模块设计代码:moduleCD4532(EI,I,Y,GS,EO);I(EI_in),.I(D_in),.Y(Q_result),.GS(GS_result),.EO(EO_result));、endmodule74X138-3 线-8线译码器:模块设计代码:module _74X138(A,EN,Y);(A_in),.EN(EI_in),.Y(Y_result));endmodule74HC4511-七段显示译码器:《模块设计代码:module _74HC4511(D,LE,BL,LT,a,b,c,d,e,f,g);reg F000,F001,F002,F110,F111,F112,F220,F221,F222,F330,F331,F332;//中间节点,依次对应Ai=Bi,Ai<Bi,Ai>为位数(0~3)always@(A,B,I0,I1,I2)beginif(A[3]>B[3])//比较第4位begin F330=0; F331=0; F332=1; endelse if(A[3]<B[3])begin F330=0; F331=1; F332=0; end)elsebegin F330=1; F331=0; F332=0; endif(A[2]>B[2])//比较第3位begin F220=0; F221=0; F222=1; endelse if(A[2]<B[2])begin F220=0; F221=1; F222=0; endelsebegin F220=1; F221=0; F222=0; end*if(A[1]>B[1])//比较第2位begin F110=0; F111=0; F112=1; endelse if(A[1]<B[1])begin F110=0; F111=1; F112=0; endelsebegin F110=1; F111=0; F112=0; endif(A[0]>B[0])//比较第1位begin F000=0; F001=0; F002=1; end%else if(A[0]<B[0])begin F000=0; F001=1; F002=0; endelsebegin F000=1; F001=0; F002=0; end//输出结果如下if((F000&&F110&&F220&&F330)&&I0)//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=1; endelse if((F000&&F110&&F220&&F330)&&(~I0&&I1&&I2))//低位进位信号出错}begin Fab2=0; Fab1=0; Fab0=0; endelse if((F000&&F110&&F220&&F330)&&(~I0&&~I1&&~I2))//低位进位信号出错begin Fab2=1; Fab1=1; Fab0=0; endelse//低位进位信号正常beginFab2=F332||F330&&F222||F330&&F220&&F112||F330&&F220&&F110&&F002||F330&&F220&&F110&&F000&&I2;Fab1=F331||F330&&F221||F330&&F220&&F111||F330&&F220&&F110&&F001||F330&&F220&&F110&&F000&&I1;Fab0=F330&&F220&&F110&&F000&&I0;end>endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC85_tb;reg [3:0] A_in,B_in;reg I0_in,I1_in,I2_in;wire Fab0_result,Fab1_result,Fab2_result;¥initialbeginI0_in=0;I1_in=0;I2_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B、#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0100; B_in=4'b1001; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位~A_in=4'b0010; B_in=4'b0010; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 $stop();end_74HC85 U1(A_in,B_in,I0_in,I1_in,I2_in,Fab0_result,Fab1_result,Fab2_result); endmodule—74HC283-4位二进制全加器:模块设计代码:module _74HC283(A,B,Ci,Co,S);//4位二进制全加器input Ci;//低位进位信号input [3:0] A,B;//输入信号output reg [3:0] S;//输出结果output reg Co;//高位进位信号Co=C[3]>reg [3:0] C,G,P;integer k;always@(A,B,Ci)beginfor(k=0;k<4;k=k+1)beginG[k]=A[k]&&B[k];P[k]=A[k]&&~B[k]||~A[k]&&B[k];]endC[0]=G[0]||P[0]&&Ci;C[1]=G[1]||P[1]&&C[0];C[2]=G[2]||P[2]&&C[1];C[3]=G[3]||P[3]&&C[2];S[0]=P[0]&&~Ci||~P[0]&&Ci;S[1]=P[1]&&~C[0]||~P[1]&&C[0];S[2]=P[2]&&~C[1]||~P[2]&&C[1];~S[3]=P[3]&&~C[2]||~P[3]&&C[2];Co=C[3];endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC283_tb;reg [3:0] A_in,B_in;【reg Ci_in;//低位进位信号wire [3:0] S_out;//本位相加结果wire Co_out;//高位进位信号initialbeginCi_in=0;A_in=4'b1010;B_in=4'b0111;(#10 begin A_in=4'b0011; B_in=4'b1111; end#10 begin A_in=4'b0101; B_in=4'b1001; end#10 begin A_in=4'b1111; B_in=4'b0010; end #10 $stop();endalways #5beginCi_in=~Ci_in;//循环改变低位进位信号{end_74HC283 U1(A_in,B_in,Ci_in,Co_out,S_out);endmodule74HC194-4位双向移位寄存器:模块设计代码:module _74HC194(S0,S1,Dsl,Dsr,CP,CR,D,Q);//4位双向移位寄存器_P339 input S0,S1;//输入端口,input Dsr,Dsl;//串行数据输入input CP,CR;//时钟和清零input [3:0] D;//并行数据输入output reg [3:0] Q;//输出结果always@(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else<case({S1,S0})2'b00:Q<=Q;//输出保持不变2'b01:Q<={Q[2:0],Dsr};//右移,低位移向高位2'b10:Q<={Dsl,Q[3:1]};//左移,高位移向低位2'b11:Q<=D;//并行置数endcaseendendmodule?对应testbench设计代码:`timescale 1ns/1nsmodule _74HC194_tb;reg [3:0] D_in;//并行数据输入reg S0_in,S1_in;//控制信号输入端口reg Dsr_in,Dsl_in;//串行数据输入reg CP_in,CR_in;//时钟和清零,清零为低电平有效wire [3:0] Q_out;//输出结果¥initialbeginCP_in=1;CR_in=1;S0_in=1;S1_in=1;//开始先输入串行数据Dsr_in=0;Dsl_in=0;&D_in=4'b0110;#243 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end)always #15//循环调整控制输入信号,周期60nsbegincase({S1_in,S0_in})2'b00:begin S1_in=0; S0_in=1; end2'b01:begin S1_in=1; S0_in=0; end2'b10:begin S1_in=1; S0_in=1; end2'b11:begin S1_in=0; S0_in=0; endendcase(endalways #10//循环调整串行数据输入信号,周期40nsbegincase({Dsr_in,Dsl_in})2'b00:begin Dsr_in=0; Dsl_in=1; end2'b01:begin Dsr_in=1; Dsl_in=0; end2'b10:begin Dsr_in=1; Dsl_in=1; end2'b11:begin Dsr_in=0; Dsl_in=0; end|endcaseend_74HC194 U1(S0_in,S1_in,Dsl_in,Dsr_in,CP_in,CR_in,D_in,Q_out);endmodule74LVC161-4位二进制同步计数器:模块设计代码:module _74LVC161(CEP,CET,PE,CP,CR,D,TC,Q);//4位二进制同步计数器_P340 ]input CEP,CET,PE,CP,CR;//输入端口input [3:0] D;//并行数据输入output TC;//进位输出output reg [3:0] Q;//输出结果wire CE;assign CE=CEP&CET;//CE=1时计数器计数assign TC=CET&PE&(Q==4'b1111);//产生进位输出信号always@(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else if(~PE) Q<=D;//PE=0,同步输入数据else if(CE)beginif((TC==1)&&(Q==4'b1111))Q<=4'b0000;//计数器计满后自动归零elseQ<=Q+1'b1;//加1计数endelse Q<=Q;//保持输出不变endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74LVC161_tb;reg CEP_in,CET_in,PE_in,CP_in,CR_in;//输入端口reg [3:0] D_in;//并行数据输入wire TC_out;//进位输出wire [3:0] Q_out;//输出结果initialbeginCEP_in=0;CET_in=1;PE_in=0;CP_in=1;CR_in=1;D_in=4'b1101;#10 begin PE_in=1;D_in=4'b1001; end#20 begin CEP_in=1; CET_in=1; end#220 begin PE_in=0; end#23 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end_74LVC161 U1(CEP_in,CET_in,PE_in,CP_in,CR_in,D_in,TC_out,Q_out);endmodule7、输出仿真波形以及相关数据:CD4532-8位优先编码器:以下波形由上至下依次是:D_in, EI_in, Q_result, GS_result, EO_result;74X138-3 线-8线译码器:以下波形由上至下依次是:A_in, EI_in, Y_result;74HC4511-七段显示译码器:以下波形由上至下依次是:D_in, LE_in, LT_in, A, B, C, D, E, F, G;74HC151-八选一数据选择器:以下波形由上至下依次是:S_in, D_in, E_in, Y0_result, Y1_result;74HC85-4位数值比较器:以下波形由上至下依次是:A_in, B_in, I0_in, I1_in, I2_in, Fab0_result, Fab1_result, Fab2_result;74HC283-4位二进制全加器:以下波形由上至下依次是:A_in, B_in, S_out, Co_out;74HC194-4位双向移位寄存器:以下波形由上至下依次是:D_in, S0_in, S1_in,Dsr_in, Dsl_in, CP_in, CR_in, Q_out;74LVC161-4位二进制同步计数器:以下波形由上至下依次是:CEP_in, CET_in, PE_in, CP_in, CR_in, D_in, T_out, Q_out;8、仿真结果分析:仿真输出波形符合预期,与芯片的功能表描述的功能相符。

血清高密度脂蛋白HDL测定

血清高密度脂蛋白HDL测定1 检验目的指导本室工作人员规范操作本检测项目,确保检测结果的准确。

2 实验原理表面活性剂HDL ————————→ HDL(可溶)胆固醇酯化酶HDL-胆固醇————————→胆固酮 + H2O2胆固醇氧化酶PODH2O2 + DSBMT + 4-氨基安替比林—————→红紫色色素3 标本:3.1 病人准备:应禁食12小时抽血.3.2 类型:血清3.3 标本存放留取标本后请尽快分离血清。

在冰箱保存的条件下(2~8℃)稳定3天,-20℃保存至少可以稳定3个月。

3.4 标本运输室温条件下运输3.5 标本拒收标准细菌污染的不能做测定。

4 实验材料4.1 试剂:宁波美康生物科技股份有限公司血清高密度脂蛋白胆固醇(HDL)测定试剂盒(浙械注准20142400141)4.1.1 试剂组成试剂1(R1):哌嗪-1,4-双(2-乙磺酸) 缓冲液pH 7.0 50mmol/L胆固醇脂酶(CE) 800U/L胆固醇氧化酶(CO) 400U/L过氧化氢酶 20KU/LTriton X-100 2ml/L 试剂2(R2):哌嗪-1,4-双(2-乙磺酸) 缓冲液pH 7.0 50mmol/L过氧化物酶(POD) 1000U/L4-氨基安替比林(4-APP) 1.0mmol/LN,N-双(4-磺丁基)-3-甲基苯胺(DSBMT)0.5mmol/L4.1.2 试剂准备:试剂为即用式。

4.1.3 试剂稳定性与贮存:试剂保存于2~8℃,若无污染,可稳定至失效期。

试剂不可冰冻。

试剂可避光保存可稳定12个月;试剂开口稳定1个月。

4.1.4 变质指示:当试剂有看得见的微生物生长,有浊度,或者未开盖的液体有沉淀时,表明试剂已变质,不能继续使用。

4.1.5 注意事项:试剂中含叠氮钠(0.95g/L)为防腐剂。

不可入口!避免接触皮肤及粘膜。

应采取必要的预防措施使用试剂4.2 校准品:建议使用宁波美康生物科技有限公司提供的脂类标准品进行全点校准操作。

hdl实验报告

目录实验一:基本IO实验(仿真)...:. (1)实验二:二进制计数器设计 (3)实验三:四位全加器的八位显示 (6)实验四:用状态机产生1101序列并验证 (9)实验五:基本IO口硬件实现 (12)实验一、基本IO实验(仿真)一、实验内容1. 学习ModelSim 软件的使用2、modelsim下编写基本IO口程序3、初步掌握Verilog语言的设计输入,编译,仿真和调试过程。

4、使用modelsim 仿真实验,观察效果二、实验原理利用定时时钟CLK作为输入(高电平为1,低电平0),输出到一个LED。

KEY1 低电平是LED亮,电平时LED灭,从而实现仿真三、源程序1,程序testio.vmodule testio(key1,led1);input key1;output led1;assign led1 = ~ key1;endmodule2,仿真t_testio.vmodule t_testio;reg data_in;wire data_out;initialbegindata_in = 0;#50 data_in = 1;#50 data_in = 0;#50 data_in = 0;$stop;endtestio test(.key1(data_in),.led1(data_out));endmodule四、仿真图五、心得体会这是我第一次使用modelsim软件,我了解了仿真的作用,通过仿真我就可以验证程序的对与错,并且在老师的讲解下,我懂得了如何在程序里打入中文,受益良多。

实验二、二进制计数器设计一、实验目的(1)熟悉Verilog HDL 时序电路的设计方法;(2)了解清零和使能的概念,以及同步清零和异步清零的区别(3)用Verilog HDL 语言设计二进制计数器,并仿真,下载验证其功能;二、实验原理计数器是最常见的寄存器逻辑电路,从微处理器的地址发生器到频率计都需要用到计数器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

HDL实验报告专业:电子科学与技术学号:1062910112姓名:李斌斌指导教师:梁瑞宇实验一Modelsim 仿真软件的使用一、实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验步骤(1)学习,练习使用Modelsim软件(2)用 Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果三、实验结果(a)程序:module yhm(a,b,c);input a,b;output c;assign c=a^b;endmodulemodule t_yhm;reg a,b;wire c;initialbegina=1’b0;b=1’b0;#10 a=1’b1;b=1’b0;#10 a=1’b0;b=1’b1;#10 a=1’b1;b=1’b1;endyhm u1(a,b,c);endmodule(b)波形四、心得1、只有多练习才能更好的使用软件2、实验编程时要细心仔细3、遇到问题应该多与同学、老师交流4、一定要自己动手编程,找出问题所在才能有所收获5、通过仿真我们才能知道自己编写的程序是否正确实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法二、实验内容设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

三、实验结果1、程序(a)module bjq(a,b1,b2,c);input a,b1,b2;output c;assign c=a^((!a)&b1&c2);endmodule(b)module bjq(a,b1,b2,c);input a,b1,b2;output c;reg c;always@(a or b1 or b2)beginif (a)c=1;elseif (b1&b2)c=1;elsec=0;endendmodulemodule t_bjq;reg ain,b1in,b2in;wire cout;initialbeginain=1;b1in=0;b2in=0;#50 ain=1;b1in=1;b2in=0;#50 ain=1;b1in=0;b2in=1;#50 ain=1;b1in=1;b2in=1;#50 ain=0;b1in=0;b2in=0;#50 ain=0;b1in=1;b2in=0;#50 ain=0;b1in=0;b2in=1;#50 ain=0;b1in=1;b2in=1;$stop;endbjq test(.a(ain),.b1(b1in),.b2(b2in),.c(cout));endmodule2、波形四、心得体会1、注意变量的遍历2、每一个问题都不止有一种解决方法,学会寻求简便的方法完成任务3、要熟悉掌握数电知识并且灵活运用实验三二进制全加器设计一、实验目的(1)熟悉Verilog HDL 元件例化语句的作用(2)熟悉全加器的工作原理(3)用Verilog HDL 语言设计四位二进制全加器,并仿真,下载验证其功能二、实验原理(1)一位全加器原理:Ai,Bi 分别是两个二进制位,Ci-1 是前级进位,Ci 是进位,Si 是加法结果。

表达式:Si=A i⊕Bi⊕Ci-1 ;Ci-1=Ai&Bi+Ai&Ci-1+Bi&Ci-1 ;⑵四位全加器:四个一位全加器串联;三、实验内容(1)用Verilog HDL 语言描述一位全加器,并使用modelsim 仿真验证结果。

(2)用Verilog HDL 元件例化语句实现四位全加器,modelsim 仿真并下载到实验箱,用按键模拟输入,led 灯模拟输出,验证结果。

(3)设计程序将加法结果分开输出,即十位数和个位数分别用四位数组表示。

四、实验结果(1)、程序module qjq1 (a, b, c, cout, out);input a, b, c;output cout, out;assign cout =a~^b~^c;assign out = (a & b) | (a &c) | (b & c);波形(2)、程序2Module qjq4(ad1,ad2,c,sc,ss);input [3:0] ad1,ad2;input c;output [3:0] ss;output sc;wire c1,c2,c3;qjq1 u1(ad1[0],ad2[0],c,c1,ss[0]); qjq1 u2(ad1[1],ad2[2],c1,c2,ss[1]); qjq1 u3(ad1[2],ad2[2],c2,c3,ss[2]); qjq1 u4(ad1[3],ad2[3],c3,sc,ss[3]);endmodulemodule t_qjq4;reg [3:0] ad1,ad2;reg c;wire sc;wire [3:0]ss;initialbeginad1=4'b0;forever#10 ad1=ad1+4'b1;endinitialbeginad2=4'b0;forever#160ad2=ad2+4'b1;endinitialbeginc=0;forever#2560 c=~c;endqjq4 u3(ad1,ad2,c,sc,ss); endmodule波形(3)module qjq4(ad1,ad2,c,sc,ss);input [3:0] ad1,ad2;input c;output [3:0] ss ,sc;qjq1 u1(ad1[0],ad2[0],c,sc[1],ss[0]);qjq1 u2(ad1[1],ad2[2],sc[0],sc[1],ss[1]); qjq1 u3(ad1[2],ad2[2],sc[1],sc[2],ss[2]); qjq1 u4(ad1[3],ad2[3],sc[2],sc[3],ss[3]); assign ss={sc,ss}/4’b1010;assign sc={sc,ss}%4’b1010;endmodulemodule t_qjq4;reg [3:0] ad1,ad2;reg c;wire [3:0]sc;wire [3:0]ss;initialbeginad1=4'b0;forever#10 ad1=ad1+4'b1;endinitialbeginad2=4'b0;forever#160 ad2=ad2+4'b1;endinitialbeginc=0;forever#2560 c=~c;endqjq4 u3(ad1,ad2,c,sc,ss);endmodule五、心得体会1、实验前一定要做好预习准备工作2、可以把复杂的问题分解为数个小问题,逐个解决,最终达到目的,就像数全加器,整体复杂,其实单个全加器就简单得多3、多位变量进行遍历是,要注意倍数关系4、要熟悉掌握数电知识并且灵活运用六、思考题在仿真时,输出结果会有毛刺,采用什么方法可以消除毛刺?答:利用D触发器可以消除毛刺实验四二进制计数器设计一、实验目的(1)熟悉Verilog HDL 时序电路的设计方法;(2)了解清零和使能的概念,以及同步清零和异步清零的区别(3)用Verilog HDL 语言设计二进制计数器,并仿真;二、实验原理一般计数器可以分为两类:加法计数器和减法计数器。

加法计数器每来一个脉冲计数值加1;减法计数器每来一个脉冲计数器值减1;有时将两者做在一起称可逆计数器。

三、实验内容及步骤(1)编程实现二进制计数器并仿真。

按实验原理要求编写一个二进制计数器,并仿真。

module counter (count, clk, reset);output [3:0] count;input clk, reset;reg [3:0] count;always @ (posedge clk or posedge reset)if (!reset)count = 4'h00;elsecount <= count + 4'h01;endmodule自行编写testbench 文件(2)编程实现十进制计数器,含同异步清零端和进位输出端,编程实现,并modelsim 仿真。

(3)增加预置功能(增加五位输入引脚),实现任意的五位二进制数的计数器。

四、实验结果(1) module t_counter;reg reset,clk;wire [3:0] count;initialbeginclk = 0;forever #10 clk=~clk;endinitialbeginreset=1;#5 reset=~reset;#10 reset=~reset;#50 reset=~reset;#10 reset=~reset;endcounter u1(count,clk,reset);endmodule;(2)、module counter (sc,count, clk, reset); output [3:0] count;output reg sc;input clk, reset;reg [3:0] count;always @ (posedge clk or negedge reset)if (!reset)begincount <= 4'b0000;sc <= 1'b0;endelseif(count==4'b1010)beginsc<=1'b1;count<=4'b0000;endelsebeginsc<=1'b0;count<=count+4'b0001;endendmodulemodule testbench;reg reset,clk;wire [3:0] count;wire sc;initialbeginclk = 0;forever #10 clk=~clk;endinitialbeginreset=1;#15 reset=~reset;#25 reset=~reset;#40 reset=~reset;#55 reset=~reset;endcounter u1(sc,count,clk,reset); endmodule(3)、module counter (sc,count,ina, reset); output [3:0] count;output reg sc;input reset;input [4:0] ina;reg [3:0] count;always @ (ina or negedge reset)if (!reset)begincount <= 4'b0000;sc <= 1'b0;endelseif(count==4'b1010)beginsc<=1'b1;count<=4'b0000;endelsebeginsc<=1'b0;count<=count+4'b0001; endendmodulemodule testbench;reg [4:0]ina;reg reset;wire [3:0] count;wire sc;initialbeginina=5'b0;forever #10 ina=ina+5'b1;endinitialbeginreset=1;#15 reset=~reset;#25 reset=~reset;#40 reset=~reset;#55 reset=~reset;endcounter u1(sc,count,ina,reset); endmodule五、心得体会1、学会利用复位信号,时钟清零2、可以利用计数器来实现分频功能3、if判断应与敏感表里的敏感沿相同4、预置等同于变相的清零实验六动态数码管显示一、实验目的1.进一步了解FPGA的设计流程和加深对Quatus II的使用。