半导体后封装工艺及设备

半导体封装制程及其设备介绍

半导体封装制程及其设备介绍一、概述半导体芯片是一种微型电子器件,半导体封装制程是将芯片进行外层包装,从而保护芯片、方便焊接、测试等工作的过程。

比较常见的半导体封装方式有芯片贴装式、铅框式、无铅框式等。

本文将从半导体封装的制程入手,为大家介绍半导体封装制程及其设备。

二、半导体封装制程1. 粘结半导体封装的第一步是将芯片粘结到支撑贴片(Leadframe)上面。

支撑贴片是一种晶粒尺寸相对较大、但还不到电路板级别的导体片。

常用的粘接剂有黄胶、银胶等,其使用在制程时会加热到一定温度,使其能够黏合贴片和芯片。

2. 线缆连接芯片被粘接到支撑贴片上方后,需要进行内部连线。

通常使用铜线作为内部连线,常用的连线方式有金线焊接和铜线焊接。

它们的区别很大程度上取决于封装要求和芯片使用情况。

3. 包封装在连线之后,开始进行半导体封装的最后一步–包封装。

包封装是将芯片包封闭在一起,以进一步保护它。

常用的封装方式有QFP、BGA、SOIC、CHIP 贴片等。

三、半导体封装设备介绍1. 芯片粘结设备芯片粘结设备是半导体封装的第一步。

常用的芯片粘结设备包括黄胶粘合机、银胶粘合机、重合机等。

不同类型的设备适用于不同封装要求的芯片。

2. 线缆连接设备目前,铜线焊接机处于主流位置。

与金线焊接机相比,铜线焊接机具有成本更低、可靠度更高的优点。

因此,其能够更好地满足不同类型的芯片封装要求。

3. 包封装设备包封装设备是半导体封装的重要步骤。

常用的设备有 QFP 封装机、CHIP 贴片封装机等。

它们能够满足不同类型的封装要求,使芯片更加可靠。

四、半导体封装制程及其设备涉及到了许多知识点。

本文从制程和设备两个角度,为大家介绍了半导体封装制程及其设备。

不同的封装方式和设备对于产品的品质、成本以及生产效率都有很大的影响。

因此,在选择半导体封装制程和设备时,需要根据实际情况进行选择,以确保产品达到最佳性能和质量要求。

半导体封装制程及其设备介绍

Solder paste

Die Prepare(芯片预处理) To Grind the wafer to target thickness then separate to single chip

---包括来片目检(Wafer Incoming), 贴膜(Wafer Tape),磨片(Back Grind),剥膜(Detape),贴片(Wafer Mount),切割(Wafer Saw)等系列工序,使芯片达到工艺所要求的形状,厚度和尺寸,并经过芯片目 检(DVI)检测出所有由于芯片生产,分类或处理不当造成的废品.

B Wafer roughness Measurement 粗糙度测量仪 主要为光学反射式粗糙度测量方式;

4.Grinding 配套设备

A Taping 贴膜机 B Detaping 揭膜机 C Wafer Mounter 贴膜机

Wafer Taping -- Nitto DR300II

Alignment

1.27, 0.762 mm (50, 30miles)

Ceramic 2, 4 direction lead

20~80

Ceramic

1.27,1.016, 0.762 mm (50, 40, 30

miles)

20~40

大家应该也有点累了,稍作休息

大家有疑问的,可以询问和交流

Surface Mount

半导体设备供应商介绍-前道部分

半导体设备供应商介绍-前道部分

常用术语介绍

1. SOP-Standard Operation Procedure 标准操作手册 2. WI – Working Instruction 作业指导书 3. PM – Preventive Maintenance 预防性维护 4. FMEA- Failure Mode Effect Analysis 失效模式影响分析 5. SPC- Statistical Process Control 统计制程控制 6. DOE- Design Of Experiment 工程试验设计 7. IQC/OQC-Incoming/Outing Quality Control 来料/出货质量检验 8. MTBA/MTBF-Mean Time between assist/Failure 平均无故障工作时间 9. CPK-品质参数 10. UPH-Units Per Hour 每小时产出 11. QC 7 Tools ( Quality Control 品管七工具 ) 12. OCAP ( Out of Control Action Plan 异常改善计划 ) 13. 8D ( 问题解决八大步骤 ) 14. ECN Engineering Change Notice ( 制程变更通知 ) 15. ISO9001, 14001 – 质量管理体系

半导体封装制程及其设备介绍详解演示文稿

半导体封装制程及其设备介绍详解演示文稿一、引言二、半导体封装制程的整体流程1.设计和制备芯片:在封装过程开始之前,需要进行半导体芯片的设计和制备。

这包括设计电路、选择材料、制造芯片等步骤。

2.选型和设计封装方案:根据芯片功能和其他要求,选择合适的封装方案。

封装方案的选择包括外形尺寸、引脚数量和布局、散热设计等。

3.制备基板:选择合适的基板材料,并进行加工和制备。

基板的制备是封装制程中的核心环节之一,目的是为芯片提供支撑和连接。

4.芯片连接:将芯片连接到基板上,通常使用焊接技术或金线键合技术。

焊接是将芯片的引脚与基板的焊盘连接起来,金线键合则是用金线将芯片与基板进行连接。

5.包封:将芯片和连接线封装进封装材料中,形成最终的封装产品。

常见的封装材料有环氧树脂和塑料,也有针对特殊应用的金属封装。

6.测试和质量检验:对封装后的产品进行测试和质量检验,确保其符合设计要求和标准。

测试主要包括电性能测试、可靠性测试和环境适应性测试等。

7.封装后处理:包括喷涂标识、气密性测试、老化测试等。

这些步骤都是为了保证封装产品的质量和性能稳定。

三、半导体封装制程的关键步骤及设备介绍1.基板制备基板制备是封装制程中的核心步骤,主要包括以下设备:(1)切割机:用于将硅片切割成芯片,常见的切割机有钻石切割机和线切割机。

(2)干法清洗机:用于清洗芯片表面的杂质。

清洗机主要有氧气等离子体清洗机和干气流清洗机等。

(3)晶圆胶切割机:用于将芯片粘贴在基板上。

2.连接技术连接技术是将芯片与基板连接起来的关键步骤,常见的设备有:(1)焊接机:用于焊接芯片和基板之间的引脚和焊盘。

常见的焊接机有波峰焊机和回流焊机。

(2)金线键合机:用于将芯片与基板之间进行金线键合连接。

常见的金线键合机有球焊键合机和激光键合机等。

3.封装工艺封装工艺是将芯片和连接线封装进封装材料中的步骤,主要设备有:(1)半导体封装设备:用于将封装材料和连接线封装成最终产品。

半导体封装制程与设备材料知识介绍

24~32

Ceramic Plastic

2.54 mm (100miles)

Surface Mount

SOP Small Outline Package

QFP Quad-Flat

Pack

封裝型式

Shape

Typical Features

Material Lead Pitch No of I/O

Plastic

1.27 mm (50miles) 2 direction

lead

8 ~40

Plastic

1.0, 0.8, 0.65 mm 4 direction

lead

88~200

Surface Mount

FPG

Flat Package of Glass

LCC

Leadless Chip

Carrier

封裝型式

Shape

Tester

Digital

Credence

SC312

Digital

Teradyne

J750

Mix-Signal Credence

Quartet one and one+

Mix-Signal HP

HP93000 P600

Mix-Signal HP

HP93000 C400

Mix-Signal Teradyne

Die Attach (上片)

Deposition (沉积)

WireBonding (焊线)

Wafer Inspection (晶圆检查) 前段結束

Molding (塑封)

Laser mark (激光印字)

Laser Cut & package saw Testing

半导体激光器封装工艺与设备共17页文档

封装工艺与设备-烧结

真空焊接系统

主要用途:

➢通过预成型焊片,实现芯片与管座或热 沉共晶贴片。

芯片

C-mount

Au80Sn20焊片

封装工艺与设备-金丝球焊

主要用途:

➢芯片与陶瓷金属或管座之间导电连接。

超声波金丝球焊机

C-mount

TO

封装工艺与设备-焊引线

电烙铁

铜引线

主要用途:

➢C-mount管座引线连接。

焊锡丝

助焊剂

C-mount

封装工艺与设备-目检

主要用途:

➢贴片、键合、封帽等精细观察与 测量,不良品外观异常分析。

金相显微镜

体式显微镜

封装工艺与设备-老化

直流稳压电源

主要用途:

➢激光器封装后不同温度下可靠性 测试与分析。

冷水机试

主要用途:

➢单管和裸管芯(结合探针台)P-IV曲线、光谱及远场发散角测量。

39、勿问成功的秘诀为何,且尽全力做你应该做的事吧。——美华纳

40、学而不思则罔,思而不学则殆。——孔子

半导体激光器光电参数测试系统

P-I-V

光谱

远场发散角

封装工艺与设备-封帽

主要用途:

➢不同型号TO管封帽。

封帽机

Thanks!

谢谢!

36、自己的鞋子,自己知道紧在哪里。——西班牙

37、我们唯一不会改正的缺点是软弱。——拉罗什福科

xiexie! 38、我这个人走得很慢,但是我从不后退。——亚伯拉罕·林肯

半导体激光器封装工艺与设备

半导体激光器封装工艺与设备

封装工艺与设备-蒸镀

主要用途:

➢热沉蒸镀焊料; ➢陶瓷片蒸镀金属电极。

半导体封装技术后固化工艺流程介绍

一、介绍半导体封装技术半导体封装技术是将芯片和其它元件封装在一起,以保护芯片不受外界影响,并便于安装和使用的技术。

其主要步骤包括前固化、粘合、后固化、切割等。

二、半导体封装技术后固化工艺的重要性后固化工艺是半导体封装技术中不可或缺的一部分,它直接影响到封装件的质量和性能。

掌握后固化工艺流程至关重要。

三、半导体封装技术后固化工艺流程介绍1. 探针测试在封装过程中,需要对芯片进行探针测试,以确保其正常工作。

探针测试是一种非常关键的测试工艺,可发现芯片的问题,保证最终封装件的质量。

2. 后固化材料选择选择合适的后固化材料对封装件的性能至关重要。

适合的后固化材料能够增强封装件的耐热性、防潮性和绝缘性能,提高其可靠性。

3. 后固化温度和时间控制后固化的温度和时间对封装件的性能影响很大。

合理的固化温度和时间能够确保封装件在使用过程中不会出现老化、断裂等问题。

4. 后固化工艺监控通过对后固化工艺进行监控和调整,可以确保封装件的质量稳定。

监控指标包括固化温度、时间、环境湿度等。

及时发现问题并进行调整,是保证封装件质量的重要手段。

5. 器件存放和包装封装件固化后,需要进行适当的存放和包装,以防止其受潮和污染。

良好的存放和包装措施可以有效延长封装件的使用寿命。

四、结语后固化工艺流程对半导体封装技术起着至关重要的作用,只有严格控制后固化工艺流程,才能保证封装件的质量和性能。

希望本文对您了解半导体封装技术后固化工艺流程有所帮助。

后固化工艺是半导体封装技术的重要环节,它不仅影响到封装件的质量和性能,还直接关系到整个封装过程的稳定性和可靠性。

在半导体封装行业中,后固化工艺流程是一个至关重要的部分。

接下来,我们将更详细地讨论后固化工艺流程的相关内容。

1. 后固化温度和时间的控制后固化的温度和时间是确保封装件质量稳定的关键参数。

在后固化的过程中,需要对温度和时间进行严格的控制和监测。

通常情况下,固化的温度和时间会根据所使用的后固化材料和封装件的具体要求而有所不同。

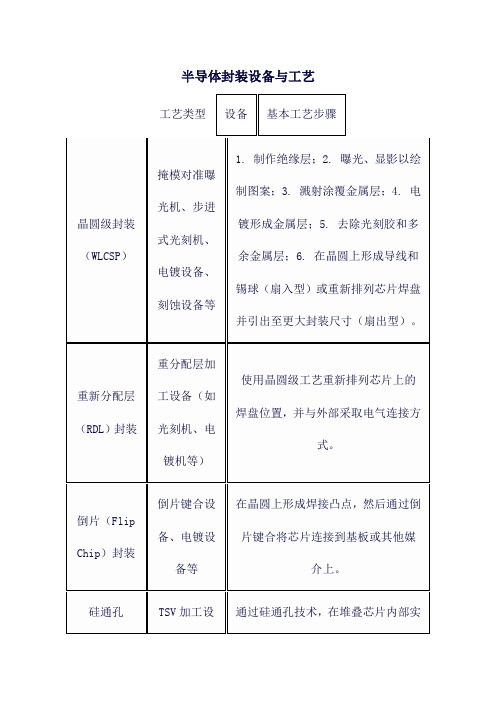

半导体封装设备与工艺

工艺类型

设备

基本工艺步骤

晶圆级封装(WLCSP)

掩模对准曝光机、步进式光刻机、电镀设备、刻蚀设备等

1. 制作绝缘层;2. 曝光、显影以绘制图案;3. 溅射涂覆金属层;4. 电镀形成金属层;5. 去除光刻胶和多余金属层;6. 在晶圆上形成导线和锡球(扇入型)或重新排列芯片焊盘并引接,通常需要钻孔、电镀等步骤。

引线框架封装

引线框架制造设备、模塑设备等

1. 制作引线框架;2. 将芯片固定到引线框架上;3. 用环氧树脂模塑料等塑料材料覆盖芯片;4. 进行固化等后续处理。

基板封装

基板制造设备、自动贴片设备、回流焊设备等

1. 制作基板;2. 自动贴片将芯片、元件等固定到基板上;3. 通过回流焊等方式进行电气连接;4. 进行后续测试和封装处理。

重新分配层(RDL)封装

重分配层加工设备(如光刻机、电镀机等)

使用晶圆级工艺重新排列芯片上的焊盘位置,并与外部采取电气连接方式。

倒片(Flip Chip)封装

倒片键合设备、电镀设备等

在晶圆上形成焊接凸点,然后通过倒片键合将芯片连接到基板或其他媒介上。

硅通孔(TSV)封装

TSV加工设备(如钻孔机、电镀机等)

半导体后端工艺:传统封装方法组装工艺的八个步骤

一、背景介绍半导体是现代电子行业的核心材料,其应用范围广泛,涉及到各种电子设备和系统。

半导体芯片的制作过程包括前端工艺(制作芯片)和后端工艺(封装芯片)。

后端工艺封装芯片是保护芯片、连接外部电路和提高功率传输效率的重要环节。

传统的封装方法组装工艺是后端工艺的关键部分,其包括多个步骤,需要严谨的操作和精密的设备。

二、后端工艺封装的意义半导体芯片在制造完成后需要进行封装,主要是为了保护芯片,连接外部电路和提高功率传输效率。

传统的封装方法组装工艺是后端工艺封装芯片的重要环节,对最终产品的性能和可靠性起到至关重要的作用。

三、传统封装方法组装工艺的八个步骤1. 原材料准备:准备封装芯片所需要的原材料,包括芯片、封装材料、连接线、塑料封装体等。

2. 芯片粘接:将芯片固定在封装底座或引线架上,使用导电胶水或金线等材料进行粘接。

3. 封装体注塑:将上述粘接好的芯片放入封装模具中,通过注塑工艺将封装材料注入模具,形成封装体。

4. 引线焊接:在封装体上焊接连接线,连接线的焊接需要高精度的自动化焊接设备。

5. 封装测试:对封装完成的芯片进行测试,检查连接线是否焊接良好,芯片功能是否正常。

6. 封装涂覆:对封装体进行表面处理,包括防潮、防尘、绝缘涂层等。

7. 功能测试:对封装完成的芯片进行功能测试,验证其性能和可靠性。

8. 包装:将封装完成的芯片进行包装,包括标识、说明书、静电防护包装等。

四、传统封装方法组装工艺的挑战和发展方向传统封装方法组装工艺存在着一些挑战,包括制程复杂、工艺精度要求高、生产效率低等问题。

随着半导体技术的发展,新型封装技术如3D封装、MEMS封装等逐渐成熟,为解决传统封装方法组装工艺的挑战提供了新的思路。

未来,随着智能手机、物联网、人工智能等应用领域的不断扩大,半导体芯片的封装工艺也将不断创新,以满足市场对芯片性能和功能的需求。

传统封装方法组装工艺在半导体后端工艺中扮演着重要的角色,其具体的步骤和发展方向对于半导体行业的发展具有重要意义。

半导体后封装工艺及设备_图文

Vintage : 2000

Load Lock : Narrow Body and Tilt Out

Robots (standard, HP, HP+, VHP, etc)

12寸的Endura

Varian 3290 STQ Sputtering System

SDIP24、54、64、56、QFP48 SOP、SSOP、QFP、TSOP、SSOP DIP、HDIP、

SDIP、HSOP、LQFP DIP、SOIC、MSO、TSO、PLCC、TO、SOT SD2P、SDIP、SKDIP、SIP、ZIP、FSIP、FDIP、QFP

、SOP、PLCC

AMAT

endura 5500

TSV参数 最小TSV直径 最小TSV间距 TSV深宽比

焊凸间距

芯片间距

芯片厚度

参数值 1m 2 m >20 25 m

5 m(微凸点180℃) 15 m (无铅铜焊柱260℃)

15-60 m

铜通孔中, TiN粘附/阻挡层和铜种子层都通过溅射来沉

积。然而,要实现高深宽比(AR > 4∶1)的台阶覆盖,传

Quantum Sources DC Biasable SST Heaters Digital Eurotherm Heater Controllers Recipe Controlled Heaters RF Etch Station with Heat Low Voltage Ignitor Vips Option with V250 Turbo Pump Load Lock Turbo Option with V70 Turbo Pump ECS Control System 17 Inch Touchscreen Monitor Ferro-Fluidic Coaxial Feedthru 12KW Gen II Power Supplies (Switchable to 3 or 6KW) CTi On-Board Cryo Pump with Compressor Optional CTi Water Pump ( Available upon request )

半导体封装后固化工艺流程介绍

尊敬的读者:以下是有关半导体封装后固化工艺流程的介绍:一、工艺流程概述1. 半导体封装后固化工艺,是指将封装好的半导体芯片在制程结束后,通过一系列步骤使其达到固化状态,以保证产品的稳定性和可靠性。

2. 固化工艺流程主要包括固化剂的选择、固化工艺参数的确定、固化设备的配置和工艺的优化等环节。

二、固化剂的选择1. 固化剂是固化工艺流程中的关键因素之一,其选择直接影响到产品的性能和质量。

2. 固化剂应具有良好的流动性、可溶性和高温稳定性,以确保在固化过程中能够充分覆盖芯片表面并形成均匀的固化层。

3. 固化剂还应具有较高的硬度和耐腐蚀性,以保障产品在使用过程中不易受到外界环境的损害。

三、固化工艺参数的确定1. 固化工艺参数包括固化温度、时间、压力等关键参数,其确定需要进行大量的实验和分析工作。

2. 固化温度应根据固化剂的特性和半导体芯片的材料选取合适的范围,并通过实验确定最佳数值。

3. 固化时间需结合固化剂的固化速度和芯片的尺寸进行合理设置,以确保固化层能够充分固化而不产生裂纹。

4. 固化压力影响固化过程中固化剂的流动和薄膜的形成,需根据具体工艺条件合理调整。

四、固化设备的配置1. 固化设备是固化工艺流程中的重要工具,其配置应考虑到生产的规模和产品的特性。

2. 固化设备需具备良好的温度控制能力和压力控制能力,同时还应具备自动化程度高、稳定性好的特点。

3. 固化设备还需具备较好的兼容性,能够适应不同封装结构和封装材料的需求。

五、工艺的优化1. 在固化工艺的实际应用中,不断优化工艺是提高产品质量和生产效率的关键。

2. 通过不断的实验研究和数据分析,找出固化工艺中的瓶颈和问题,采取相应的改进措施,以确保固化工艺流程的稳定和可靠。

3. 还需要不断地引入新的技术和材料,以提高固化工艺的效率和降低生产成本。

总结:以上是半导体封装后固化工艺流程的介绍,固化工艺对于半导体产品的质量和可靠性具有至关重要的作用,需要在实际生产中严格控制各个环节,不断进行优化和改进,以确保产品能够达到预期的性能和寿命要求。

芯片封装设备有哪些芯片封装工艺流程

芯片封装设备有哪些芯片封装工艺流程1.锡膏喷涂设备:通过喷涂锡膏将焊盘涂覆在芯片上,用于后续的焊接连接。

2.进料机器人:用于将原材料芯片送入封装设备,并确保供料的准确和高效。

3.精密半自动贴片机:用于将芯片精确地贴片到PCB(印刷电路板)上,实现芯片和电路板的连接。

4.焊接机:在芯片贴片后,通过焊接技术将芯片与电路板进行连接,完成芯片的外部电气连接。

5.装配机器人:用于将其他元器件(如电阻、电容等)精确地安装到电路板上,以完成电路的组装。

6.封装机:将电路板和芯片封装在外壳内,以便保护芯片不受外界环境的干扰。

7.检测设备:用于对封装的芯片进行测试和检测,以确保其质量和可靠性,包括外观检测、电性能测试等。

8.标识设备:用于在封装完成的芯片上标识产品型号、批次号等信息。

以上是一些常见的芯片封装设备。

这些设备通常会在芯片封装工艺流程中使用。

芯片封装工艺流程主要包括以下几个步骤:1.设计封装方案:根据芯片的功能和尺寸要求,选择合适的封装方式,设计封装方案。

2.制作封装模具:根据封装方案,制作适用于芯片封装的模具。

3.准备封装材料:准备封装所需的材料,包括芯片、封装胶、封装材料等。

4.芯片贴片:利用贴片机将芯片精确地贴片到PCB上,并与电路板焊接连接。

5.焊接连接:通过焊接技术将芯片与电路板进行电气连接,一般采用焊膏和热风或回流炉进行焊接。

6.粘贴封装胶:在芯片周围涂覆封装胶,保护芯片并固定其位置。

7.清洗和烘干:清洁封装后的芯片以去除封装胶和焊接残留物,并通过烘干过程确保芯片干燥。

8.封装测试:对封装后的芯片进行各项测试,包括外观检测、电性能测试等。

9.封装包装:将封装完成的芯片进行包装,标记型号、批次号等信息。

以上是芯片封装设备及其封装工艺流程的介绍,芯片封装的流程和设备的选择会因芯片的要求和封装方式的不同而有所差异,但大致步骤都是相似的。

芯片封装工艺的良好执行对于芯片的性能和可靠性有着重要的影响。

史上最全的半导体材料工艺设备汇总

史上最全的半导体材料工艺设备汇总半导体材料工艺设备是制造半导体器件所必需的关键工具和设备,涵盖了从原始材料制备到最终器件组装的各个环节。

下面是史上最全的半导体材料工艺设备汇总,详细介绍了常用的设备和其工艺原理。

1.单晶生长设备:单晶生长是制备高纯度晶体的关键步骤,其中最常用的方法是蒸发法、溶液法和气相传递法。

著名的单晶生长设备包括气相村田炉、石英管感应加热炉和悬浮区域溶液法生长设备等。

2.制备工艺设备:用于制备半导体器件的设备,如光刻机、薄膜沉积设备、离子注入机和扩散炉等。

光刻机用于在硅片表面绘制图案,薄膜沉积设备用于在硅片上沉积薄膜,离子注入机用于将杂质注入硅片中以改变其电学性质,而扩散炉则用于在高温下将杂质扩散到硅片中。

3.工艺控制设备:用于控制制备过程中的温度、压力和流量等参数,保证器件质量的一致性。

常见的工艺控制设备有真空泵、温度控制器、压力调节器和流量计等。

4.测试和检测设备:用于测试和评估半导体器件的性能和品质。

测试和检测设备有各种测试仪器,如电子显微镜、扫描电镜、红外摄像头和光学显微镜等。

5.清洗设备:用于去除制备过程中的杂质和污染物,确保器件的纯净度。

常见的清洗设备包括酸洗机、溶液喷淋机和超声波清洗机等。

6.封装设备:用于将单个芯片封装成完整的器件,保护芯片免受外界环境的影响。

封装设备有多种形式,如焊接机、贴片机和封装材料等。

7.气体和液体供应设备:用于提供制备过程中所需的气体和液体,如氢气、氮气、甲烷和硫酸等。

供应设备有蓄压罐、瓶装气体和化学品储存柜等。

8.废气处理设备:用于处理制备过程中产生的废气,防止对环境的污染。

常见的废气处理设备包括废气吸收装置、废气净化器和废气燃烧器等。

9.冷却和加热设备:用于控制制备过程中的温度,保持设备稳定运行。

常见的冷却和加热设备有冷却塔、冷却循环泵和加热炉等。

10.自动化控制系统:用于自动化监控和管理整个制备过程,提高生产效率和产品质量。

自动化控制系统包括各种传感器、控制器和计算机软件等。

半导体封装后道工艺

半导体封装后道工艺半导体封装后道工艺,这听起来好像很神秘,其实就像是给半导体这个小“精灵”穿上漂亮又实用的外衣,让它能够在各种各样的电子设备里好好发挥作用。

半导体封装后道工艺包含好多环节呢。

咱们先说芯片切割这个事儿。

你可以把一块半导体晶圆想象成一块大蛋糕,芯片切割呢,就是把这个大蛋糕切成一块一块的小蛋糕,每一块小蛋糕就是一个单独的芯片。

这可不像咱们平常切蛋糕那么简单,得用特别精密的设备,就像超级精细的手术刀一样,要是切歪了一点,那这个芯片可能就没法好好工作了,就好比小蛋糕切得歪歪扭扭的,看着就不舒服,吃起来也不方便。

这一步啊,对精度的要求特别高,差之毫厘就可能谬以千里呢。

再来说说芯片贴装。

这个环节就像是把一颗珍贵的宝石镶嵌到戒指上。

芯片就是那颗宝石,而基板就像是戒指。

要把芯片稳稳地、精确地贴装到基板上,得用专门的胶水或者焊接技术。

这胶水啊,可不是咱们平常粘东西的胶水,那可是高科技的胶水,就像魔法胶水一样,能把芯片牢牢地固定住。

焊接呢,更像是一种超级精密的针线活,要把芯片和基板之间的电路连接起来,就像用针线把宝石和戒指连起来,要是有个焊点没焊好,就像针线没缝好,电路就不通畅了,芯片也就没法正常工作了。

接着就是引线键合了。

这就好比是在芯片和基板之间搭建桥梁。

这些细细的金属线就像是桥梁的钢索,把芯片上的焊点和基板上的焊点连接起来。

这个过程得非常小心,金属线要是断了或者没接好,那就像桥梁断了一样,信号就过不去了。

而且每一根金属线的位置和连接都要恰到好处,这可需要操作人员有非常熟练的技巧,就像一个经验丰富的建筑工人建造桥梁一样,容不得半点马虎。

还有封装测试这个环节呢。

这就像是给已经穿上衣服的半导体做一个全面的体检。

要检查它在各种环境下是不是都能正常工作,比如温度高一点、低一点的时候,就像检查一个人在不同天气下是不是都能健康生活一样。

要是发现有问题,就得赶紧找出来是哪个环节出了毛病,是芯片本身呢,还是封装过程中的某个步骤。

半导体工艺流程所需设备及材料

半导体工艺流程所需设备及材料1. 芯片设计:芯片设计软件是用来设计芯片电路的主要工具。

常用的芯片设计软件有Cadence和Synopsys等。

这些软件由相应的厂家提供。

2.晶圆制备:晶圆制备是将单晶硅材料生长成具有特定晶面方向的圆片。

晶圆切割机是用来将单晶硅棒切割成固定尺寸的圆片的设备。

较常见的晶圆切割机厂家有DISCO和ADE等。

3. 清洗和薄膜沉积:清洗是为了去除晶圆表面的杂质和污染物,常用的清洗设备有湿法清洗设备和干法清洗设备。

薄膜沉积是为了在晶圆表面上形成一层薄膜,在半导体工艺中常用的薄膜沉积设备有化学气相沉积(CVD)和物理气相沉积(PVD)设备。

较常见的薄膜沉积设备厂家有Applied Materials、Tokyo Electron和Lam Research等。

4. 光刻图案制作:光刻是在晶圆表面上通过光学曝光形成特定图案的过程。

光刻设备使用的是光刻胶和光刻胶图案制作设备。

常见的设备厂家有ASML和Nikon等。

而常用的光刻胶厂家有东京欢迎(Tokyo Ohka Kogyo, TOK)和JSR等。

5. 离子注入:离子注入是将特定的掺杂原子注入到晶圆表面的过程,以改变晶圆的电学性质。

离子注入设备由AMAT(Applied Materials)、Axcelis和DEU等厂家提供。

6. 局部导电:局部导电是为了在晶圆上形成导电通路。

常用的局部导电设备有离子束刻蚀机和激光刻蚀机。

设备厂家有Carl Zeiss、Lasertec和KLA-Tencor等。

7. 成像和固化:成像是为了检查已形成的芯片图案的质量,并进行修复。

而固化是为了在芯片上形成可靠的电器连接。

常用的成像和固化设备有显微镜、电子束曝光机和高温热处理设备等。

设备厂家有ASML、JEOL和Canon等。

8. 封装:封装是将芯片封装到合适的封装材料中,以保护芯片并提供外部引脚。

封装设备厂家主要有胜达(Shuntong)、ASE和Amkor等。

半导体制造主要设备及工艺流程

半导体制造主要设备及工艺流程主要设备:1.清洗设备:用于清洗硅片,去除表面的杂质和污染物。

主要有超声波清洗机和流体喷洗机。

2.涂覆设备:用于在硅片表面涂覆光刻胶。

主要有旋涂机和喷涂机。

3.曝光设备:用于将光刻胶上的图案转移到硅片上。

主要有光刻机和直写机。

4.退火设备:用于去除光刻胶和修复表面缺陷。

主要有热退火炉和激光退火机。

5.切割设备:用于将硅片切割成单个芯片。

主要有切割机和钻孔机。

6.清除设备:用于清除硅片表面的残留物。

主要有湿法清洗机和干法清洗机。

主要工艺流程:1.接收硅片:开始时,原始硅片被送至半导体制造工厂,并经过检查和测试,以确保质量符合要求。

2.清洗:硅片被放入超声波清洗机或流体喷洗机中进行清洗,以去除表面的杂质和污染物。

3.涂覆:清洗后的硅片被放入旋涂机或喷涂机中,涂覆一层光刻胶在硅片表面。

4.曝光:涂覆光刻胶的硅片被放入光刻机或直写机中,通过曝光机将图案转移到光刻胶上。

5.退火:曝光后的硅片经过热退火炉或激光退火机退火,以去除光刻胶和修复表面缺陷。

6.切割:退火后的硅片被送到切割机或钻孔机中进行切割,将硅片切割成单个芯片。

7.清除:切割后的芯片进一步进行清除,以去除硅片表面的残留物。

8.检验和测试:清除后的芯片被检查和测试,以确保质量和功能合格。

9.封装:通过封装设备将芯片封装到塑料封装中,并连接到引脚。

10.测试:封装后的芯片被送到测试设备中进行功能测试和性能评估。

11.校准:测试后的芯片也经过校准,以确保准确性和一致性。

12.包装和出货:测试和校准后,芯片被放入包装盒中,然后运送到客户。

以上是半导体制造的主要设备及工艺流程的详细介绍。

这个过程需要高度的精确性和技术要求,以确保半导体产品的质量和性能。

半导体电子元器件封装工艺流程

半导体电子元器件封装工艺流程一、晶圆制造后的准备。

半导体电子元器件封装之前,那晶圆可是刚刚经历了复杂的制造过程呢。

晶圆就像是一个宝藏,上面有好多好多微小的芯片,这些芯片可是未来元器件的核心部分。

不过这个时候的晶圆可不能直接拿去封装,得先进行一些检测和准备工作。

比如说要检查晶圆上的芯片有没有什么缺陷,就像挑水果一样,得把坏的挑出去,只留下好的芯片。

而且还要对晶圆进行切割前的标记,就像是给每个小芯片都标上一个独特的记号,这样后面在封装的时候就不会搞混啦。

二、晶圆切割。

接下来就到了激动人心的晶圆切割环节。

这就好比是把一块大蛋糕切成小块一样,不过这个蛋糕可小得不得了,而且切的时候得特别特别精准。

切割的工具也是非常精细的,就像一把超级小的刀,要把晶圆按照之前标记好的位置切成一个个独立的小芯片。

这过程可不能马虎,要是切歪了或者切坏了芯片,那这个芯片可能就报废了。

每一个小芯片都是未来电子设备里的小英雄,所以切割的时候要小心翼翼的,就像对待自己心爱的小宝贝一样。

三、芯片粘贴。

切割好芯片之后呢,就得把芯片粘贴到封装的基板上啦。

这个基板就像是芯片的小床,要让芯片舒舒服服地躺在上面。

粘贴的胶水也很有讲究,得是那种能很好地固定芯片,又不会对芯片有什么不良影响的胶水。

这就像是给芯片找了一个合适的床垫,让它能稳稳地待在那里。

而且在粘贴的时候,要保证芯片的位置准确无误,就像把一幅画准确地挂在墙上一样,不能歪一点。

四、引线键合。

这可是个技术活呢。

芯片粘贴好了之后,要把芯片上的电极和封装基板上的引脚连接起来,这个连接就靠引线键合啦。

这就像是在芯片和外界之间搭起了一座座小桥梁,通过非常细的金属丝来实现连接。

操作人员得用专门的设备,像一个超级精细的小工匠一样,把金属丝精准地焊接到芯片和基板的相应位置上。

这个过程要快、准、稳,不然的话,这些小桥梁要是搭得不好,信号就没办法正常传输啦。

五、封装保护。

芯片和基板连接好之后,可不能就这么赤裸裸地放在那里,得给它们穿上一层保护衣。

半导体制造主要设备及工艺流程

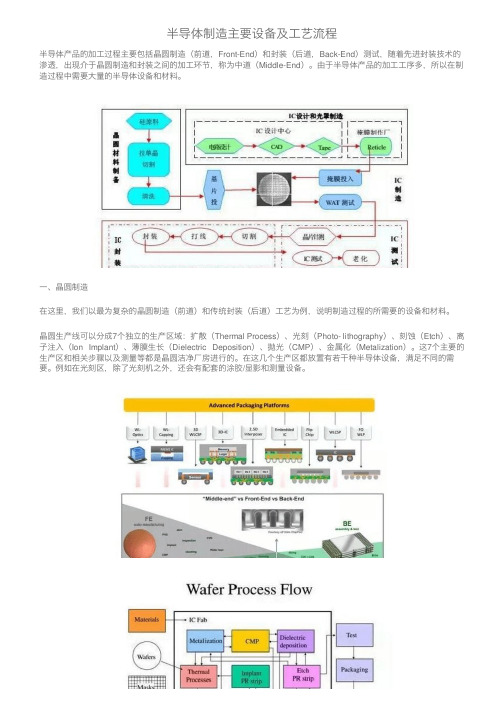

半导体制造主要设备及⼯艺流程半导体产品的加⼯过程主要包括晶圆制造(前道,Front-End)和封装(后道,Back-End)测试,随着先进封装技术的渗透,出现介于晶圆制造和封装之间的加⼯环节,称为中道(Middle-End)。

由于半导体产品的加⼯⼯序多,所以在制造过程中需要⼤量的半导体设备和材料。

⼀、晶圆制造在这⾥,我们以最为复杂的晶圆制造(前道)和传统封装(后道)⼯艺为例,说明制造过程的所需要的设备和材料。

晶圆⽣产线可以分成7个独⽴的⽣产区域:扩散(Thermal Process)、光刻(Photo- lithography)、刻蚀(Etch)、离⼦注⼊(Ion Implant)、薄膜⽣长(Dielectric Deposition)、抛光(CMP)、⾦属化(Metalization)。

这7个主要的⽣产区和相关步骤以及测量等都是晶圆洁净⼚房进⾏的。

在这⼏个⽣产区都放置有若⼲种半导体设备,满⾜不同的需要。

例如在光刻区,除了光刻机之外,还会有配套的涂胶/显影和测量设备。

传统封装(后道)测试⼯艺可以⼤致分为背⾯减薄、晶圆切割、贴⽚、引线键合、模塑、电镀、切筋/成型和终测等8个主要步骤。

与IC晶圆制造(前道)相⽐,后道封装相对简单,技术难度较低,对⼯艺环境、设备和材料的要求远低于晶圆制造。

三、半导体⼯艺解析半导体制造⼯艺是集成电路实现的⼿段,也是集成电路设计的基础。

⾃从1948年晶体管发明以来,半导体器件⼯艺技术的发展经历了三个主要阶段:1950年采⽤合⾦法⼯艺,第⼀次⽣产出了实⽤化的合⾦结三极管;1955年扩散技术的采⽤是半导体器件制造技术的重⼤发展,为制造⾼频器件开辟了新途径;1960年平⾯⼯艺和外延技术的出现是半导体制造技术的重⼤变⾰,不但⼤幅度地提⾼了器件的频率、功率特性,改善了器件的稳定性和可靠性,⽽且也使半导体集成电路的⼯业化批量⽣产得以成为现实。

⽬前平⾯⼯艺仍然是半导体器件和集成电路⽣产的主流⼯艺。

半导体先进封装工艺与设备

半导体先进封装工艺与设备《半导体先进封装工艺与设备》1. 半导体先进封装工艺的历史1.1 早期的封装摸索嘿,朋友!咱们先来聊聊半导体先进封装工艺的历史。

其实啊,在半导体刚诞生的时候,封装就像是给半导体这个小宝贝做一个简单的襁褓。

早期的封装工艺可简单啦,主要就是把芯片包起来,起到保护和连接外部电路的作用。

就好比你把一个很脆弱的小物件放在一个小盒子里,这个盒子就是最开始的封装。

那时候,封装技术还比较粗糙,就像搭积木一样,只是简单地把芯片和引脚连接起来。

1.2 发展的驱动力随着时间的推移呢,是什么让封装工艺不断发展呢?说白了就是需求。

就像咱们生活里,从黑白电视到彩色电视,再到现在的智能电视,功能越来越强大,对半导体的要求也越来越高。

半导体芯片要更小、性能要更强,这就逼着封装工艺不断进步。

就像我们要把更多的东西装进更小的行李箱,就得想出更巧妙的办法。

像计算机技术的飞速发展,智能手机的出现,都对半导体封装工艺提出了更高的要求,于是就慢慢朝着先进封装工艺迈进了。

2. 半导体先进封装工艺的制作过程2.1 前期准备在制作半导体先进封装之前啊,有好多准备工作呢。

首先得有干净的环境,这就好比咱们做蛋糕,得有个干净的厨房一样。

如果有灰尘之类的杂质,就像蛋糕里混进了沙子,那可就糟糕了。

然后就是要对芯片进行检测,看看这个芯片有没有什么“小毛病”,就像检查水果有没有坏的地方一样,只有好的芯片才能进行下一步的封装。

2.2 芯片贴装接下来就是芯片贴装啦。

这个过程就像是把一颗珍贵的宝石镶嵌到戒指上。

芯片要精确地贴到基板上,这个基板就像是芯片的“床”。

这可不能有一点偏差,要是贴歪了,就像戒指上的宝石镶歪了,既不美观,也会影响功能。

而且在贴装的时候,还得用特殊的胶水或者焊接材料来固定芯片,就像用强力胶把宝石牢牢地粘在戒指上一样。

2.3 引线键合芯片贴好之后呢,就到了引线键合这一步。

这就好比是在芯片和外部电路之间搭起一座座“小桥梁”。

半导体后道工艺设备折旧年限标准

半导体后道工艺设备折旧年限标准

一、设备类型

半导体后道工艺设备主要包括封装测试设备、研磨设备、切割设备等。

不同类型的设备由于其使用状况、制造材料和技术进步等因素的不同,折旧年限也会有所差异。

二、使用状况

设备的折旧年限受到其使用状况的影响。

一般来说,使用频繁、高强度的设备折旧年限较短,而使用较少、低强度的设备折旧年限较长。

因此,在确定折旧年限时,需要充分考虑设备的使用状况。

三、制造材料

设备的制造材料也会影响其折旧年限。

一些高精度、高质量的材料容易受到磨损和损坏,因此折旧年限较短;而一些耐用的材料则具有较长的折旧年限。

四、技术进步

随着半导体技术的不断发展,后道工艺设备也在不断更新换代。

因此,在确定折旧年限时,需要考虑技术进步对设备价值的影响。

一般来说,技术进步较快的设备折旧年限较短,而技术进步较慢的设备折旧年限较长。

五、经济因素

经济因素也是影响设备折旧年限的重要因素之一。

设备的折旧年限应该与其经济价值相符合,不能过高或过低。

如果设备的经济价值较高,折旧年限可以适当延长;如果设备的经济价值较低,折旧年限可以适当缩短。

六、折旧方法

在确定设备的折旧年限时,还需要考虑所采用的折旧方法。

常用的折旧方法包括直线法、加速折旧法等。

不同的折旧方法会对设备的折旧年限产生影响。

七、税法规定

税法规定也是确定设备折旧年限时需要考虑的因素之一。

不同国家和地区对于设备折旧的规定可能存在差异,因此在确定折旧年限时需要了解当地的税法规定。

半导体后端封装工艺

半导体后端封装工艺哎呀,说起半导体后端封装工艺,这可真是个技术活儿,得慢慢道来。

你知道的,半导体芯片,就是那些小得不能再小,但功能强大的家伙,它们在制造出来之后,还得经过一系列的封装过程,才能变成我们熟悉的那些电子设备里的“大脑”。

就拿我上次去参观的那个半导体工厂来说吧,那真是让我大开眼界。

一进车间,就看到一排排的机器在那儿忙活,工人们穿着无尘服,戴着口罩和手套,一个个专注得不得了。

我得说,那环境,比我家的厨房还干净!首先,他们得把那些裸芯片——就是还没穿衣服的芯片——放在一个特制的框架上。

这个框架,就像是给芯片量身定做的小床,得确保芯片放得稳稳当当的。

然后,就是焊接了。

你别小看这个焊接,这可是个精细活儿。

工人们得用一种特制的焊锡,一点点地把芯片的引脚和框架连接起来。

这个过程得非常小心,因为芯片非常脆弱,一不小心就可能报废。

焊接完了,还得检查。

他们用一种叫做X光的机器,就像是给芯片做体检一样,看看焊接的地方有没有问题。

如果有问题,那就得重新来过,这可是个既费时又费力的活儿。

接下来,就是封装了。

这个步骤,就像是给芯片穿上衣服。

他们会用一种特殊的塑料或者陶瓷材料,把芯片和框架整个包裹起来。

这样做,一方面是为了保护芯片,另一方面也是为了散热。

你想想,芯片工作起来,那温度可是很高的,不散热怎么行?封装完了,还得测试。

他们会把封装好的芯片放到一个测试台上,接上电源,看看芯片工作是否正常。

如果一切正常,那这个芯片就算是合格了。

如果不行,那就得回炉重造。

整个过程,就像是在做一个精细的艺术品,每一个步骤都得小心翼翼。

我看着那些工人们,他们的眼神里透露出一种专注和自豪。

毕竟,他们手里的,可是现代科技的心脏啊!所以说,半导体后端封装工艺,不仅仅是技术活儿,更是一种艺术。

每一个细节,都关系到芯片的性能和寿命。

这就像是做菜,火候、调料,每一个细节都得恰到好处,才能做出一道美味的佳肴。

而半导体后端封装,就是科技大餐中的那道主菜,让人期待,也让人敬佩。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TSV的研究动态

TSV参数 最小TSV直径 最小TSV间距

TSV的研究动态

参数值 1m 2 m

TSV深宽比

焊凸间距 芯片间距 芯片厚度

>20

25 m

5 m(微凸点180℃) 15 m (无铅铜焊柱260℃)

15-60 m

铜通孔中, TiN粘附/阻挡层和铜种子层都通过溅射来沉 积。然而,要实现高深宽比(AR > 4∶1)的台阶覆盖,传 统的PVD直流磁控技术效果并不令人满意。基于离子化 金属等离子体( IMP)的PVD 技术可实现侧壁和通孔底部 铜种子层的均匀沉积。由于沉积原子的方向性以及从通 孔底部到侧壁溅射材料过程中离子轰击的使用, IMP提 供更好的台阶覆盖性和阻挡层/种子层均匀性。由于电 镀成本大大低于PVD /CVD,通孔填充一般采用电镀铜的 方法实现。

Company Logo

传统半导体封装的工艺流程

封装技术发展方向

☆圆晶级封装(WLCSP) ☆覆晶封装(Flip Chip) ☆系统封装(SiP) ☆硅穿孔(Through-Silicon-Via) ☆射频模组(RF Module) ☆ Bumping 技术的印刷(Printing)和电镀(Plating)

ENDURA腔体构成

ENDURA传输过程

谢谢!

MSP-3200 型全自动磁控溅射 镀膜设备 本设备可在硅片、陶瓷、

玻璃、石英、Ⅲ-Ⅴ族化 合物、金属等材料表面 镀制各种金属、非金属、 化合物薄膜材料。如Al、 Au、Pt、Cr、Ti、Ni、 Cu、NiCr、TiW、W、 SiO、AlO、TaN、ITO、 AZO等,沉积的薄膜具 有良好的均匀性、附着 力,设备具有溅射速率 快、基片升温低、加热 稳定等特点。

AMAT endura 5500

Brief Description Wafer Size : 200mm Vintage : 2000 Load Lock : Narrow Body and Tilt Out

Robots (standard, HP, HP+, VHP, etc)

12寸的Endura

4

5 6

江苏长电科技

赛意法微电子有限公司 上海松下半导体有限公司

TO-XX、SOT./SOD、DIP 、SOP、PLCC/DQF、IP、 HSOP、SDIP、HSIP、SSOP、FSIP、FDIP

DIP、SOP、BGA SOP008、SOP016、018、028、SDIP028、042; LQFP048、NFS-52、QFP084、TQFP100、TO-220E

贴膜

打磨

刻蚀

绝缘层 处理

切割

贴装

溅镀

钻孔

设备:磨抛机、深反应离子刻蚀、激光打孔、磁控溅射

TSV互连的3D芯片堆叠关键技术

(1)通孔的形成; (2)绝缘层、阻挡层和种子层的淀积; (3)铜的填充(电镀)、去除和再分布引线(RDL)电镀; (4)晶圆减薄; (5)晶圆/芯片对准、键合与切片。

采用磁控溅射

7

8 9

东芝半导体(无锡)有限公司

甘肃永红器材 上海阿法泰克电子有限公司

SDIP24、54、64、56、QFP48

SOP、SSOP、QFP、TSOP、SSOP DIP、HDIP、 SDIP、HSOP、LQFP DIP、SOIC、MSO、TSO、PLCC、TO、SOT

10

无锡华润微电子封装总厂

SD2P、SDIP、SKDIP、SIP、ZIP、FSIP、FDIP、QFP、 SOP、PLCC

--- 3D封装与硅通孔( TSV)工艺技术

2008年至今国际上也只有东芝、Oki-新兴公司,STMicroelectronics、Aptina这些半导体巨头在手机CIS芯片晶圆级 封装中使用最新的TSV技术,并相继研发实现了量产.文中 研究了基于TSV技术的CIS产品晶圆级封装工艺流程,这一 工艺流程经过了批量生产的考验.重点研究了在背面打孔溅 镀铝层后,光刻、镀覆Zn/Ni层、刻蚀铝、去胶、镀覆Au金 属层的顺序问题。

denton vacuum discovery 635/785

denton vacuum Phoenix

AJA公司 ATC-B-3400-H

Unaxis公司 LLS EVOⅡ

Unaxis Cluster Line200

TSV1200-S型磁控溅射镀膜机

磁控溅射PVD镀膜, 氮化钛(TiN)、氮碳 化钛(TiCN)、氮化 锆(ZrN)、氮化铬 (CrN)、氮化铝钛 (TiAIN)、碳化钛 (TiC)等

晶圆级芯片封装WLCSP

(Wafer Level Chip Scale Packaging)

圆片级CSP产品的封装工艺流程

★ 在圆片上制作接触器的圆片级CSP的封装工艺流程;

圆片→二次布线→减薄→在圆片上制作接触器→接触器电 镀→测试、筛选→划片→激光打标 ★ 在圆片上制作焊球的圆片级CSP的封装工艺流程 圆片→二次布线→减薄→在圆片上制作焊球→模塑包封或 表面涂敷→测试、筛选→划片→激光打标

---基于TSV技术的CIS芯片晶圆级封装工艺研究

中国大陆半导体封装测试产业 前十大厂商

排名 1 2 3 厂商 Motorola天津半导体有限公司 北京三菱四通微电子公司 南通富士通微电子有限公司

DIP、SIP、SOP、QFP、SSOP、TQFP、MCM

主要封装方式

QFP、CGP、BGA、SSOP、FLIP CHIP

Varian

3290 STQ Sputtering System

Quantum Sources DC Biasable SST Heaters Digital Eurotherm Heater Controllers Recipe Controlled Heaters RF Etch Station with Heat Low Voltage Ignitor Vips Option with V250 Turbo Pump Load Lock Turbo Option with V70 Turbo Pump ECS Control System 17 Inch Touchscreen Monitor Ferro-Fluidic Coaxial Feedthru 12KW Gen II Power Supplies (Switchable to 3 or 6KW) CTi On-Board Cryo Pump with Compressor Optional CTi Water Pump ( Available upon request )

IC Package (IC的封装形式)

• QFN—Quad Flat No-lead Package 四方无引脚扁平封装 • SOIC—Small Outline IC 小外形IC封装 • TSSOP—Thin Small Shrink Outline Package 薄小外形封装 • QFP—Quad Flat Package 四方引脚扁平式封装 • BGA—Ball Grid Array Package 球栅阵列式封装 • CSP—Chip Scale Package 芯片尺寸级封装

TSV 技术__第四代封装技术

硅通孔技术(TSV)是通过在芯片和芯片之间、晶圆和晶圆之间制

作垂直导通,实现芯片之间互连的最新技术。 硅通孔TSV (Through-Silicon Via)技术是半导体集成电路产 业迈向3D-SiP 时代的关键技术 TSV技术一般和WLCSP 相结合,工艺流程上可以先钻孔和后钻孔, 主要工艺流程如下: