用VHDL设计快速BCD码加法器

加法计数器的设计实验报告

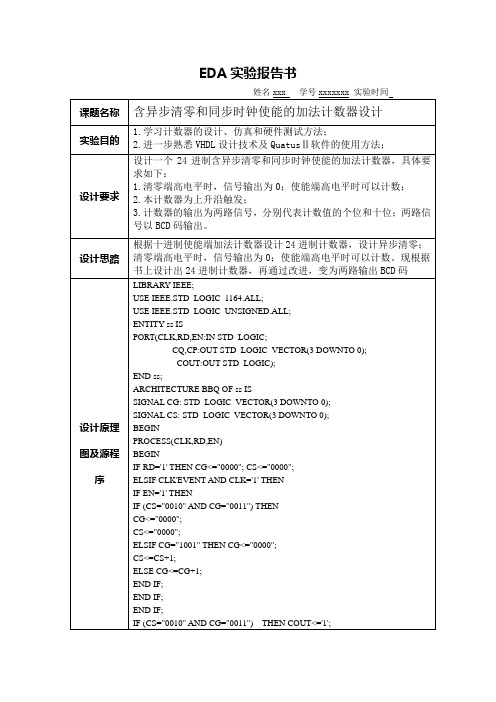

EDA实验报告书姓名xxx 学号xxxxxxx 实验时间课题名称含异步清零和同步时钟使能的加法计数器设计实验目的1.学习计数器的设计、仿真和硬件测试方法;2.进一步熟悉VHDL设计技术及QuatusⅡ软件的使用方法;设计要求设计一个24进制含异步清零和同步时钟使能的加法计数器,具体要求如下:1.清零端高电平时,信号输出为0;使能端高电平时可以计数;2.本计数器为上升沿触发;3.计数器的输出为两路信号,分别代表计数值的个位和十位;两路信号以BCD码输出。

设计思路根据十进制使能端加法计数器设计24进制计数器,设计异步清零;清零端高电平时,信号输出为0;使能端高电平时可以计数。

现根据书上设计出24进制计数器,再通过改进,变为两路输出BCD码设计原理图及源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ss ISPORT(CLK,RD,EN:IN STD_LOGIC;CQ,CP:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT:OUT STD_LOGIC);END ss;ARCHITECTURE BBQ OF ss ISSIGNAL CG: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL CS: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,RD,EN)BEGINIF RD='1' THEN CG<="0000"; CS<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF EN='1' THENIF (CS="0010" AND CG="0011") THENCG<="0000";CS<="0000";ELSIF CG="1001" THEN CG<="0000";CS<=CS+1;ELSE CG<=CG+1;END IF;END IF;END IF;IF (CS="0010" AND CG="0011") THEN COUT<='1';ELSECOUT<='0';END IF;CQ<=CG;CP<=CS;END PROCESS;END BBQ;仿真波形图问题讨论1.设计一个60进制的加法计数器,具体要求与本实验中的24进制计数器相同。

vhdl加法计数器

6、编写一个4位加法计数器VHDL源程序,要求:复位信号reset低电平清零,变高后在clk上升沿开始工作,输入时钟信号为clk,输出为q。

(以十二进制为例)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY counter ISPORT(clk,reset:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY priorityencoderARCHITECTURE rtl OF counter ISSIGNAL count: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINq<=cout;PROCESS(clk,reset)ISBEGINIF(reset=’0’)THENcout<="0000";ELSIF(clk’EVENT AND clk=’1’)THENIF(cout="1011")THENcout<="0000"ELSEcout<=cout+’1’;END IF;END IF;END PROCESS;END ARCHITECTURE rtl;4位二进制并行加法器的源程序ADDER4B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER4B IS --4位二进制并行加法器PORT(CIN:IN STD_LOGIC;--低位进位A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);--4位加数B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);--4位被加数S:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--4位和CONT:OUT STD_LOGIC);END ADDER4B;ARCHITECTURE ART OF ADDER4B ISSIGNAL SINT:STD_LOGIC_VECTOR(4 DOWNTO 0);SIGNAL AA,BB:STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINAA<='0'& A;--将4位加数矢量扩为5位,为进位提供空间BB<='0'& B;--将4位被加数矢量扩为5位,为进位提供空间SINT<=AA+BB+CIN ;S<=SINT(3 DOWNTO 0);CONT<=SINT(4);END ART;8位二进制加法器的源程序ADDER8B.VHDLIBRARY IEEE;USE IEEE_STD.LOGIC_1164.ALL;USE IEEE_STD.LOGIC_UNSIGNED.ALL:ENTITY ADDER8B IS--由4位二进制并行加法器级联而成的8位二进制加法器PORT(CIN:IN STD_LOGIC;A:IN STD_LOGIC_VECTOR(7 DOWNTO 0);B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);S:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT:OUT STD_LOGIC);END ADDER8B;ARCHICTURE ART OF ADDER8B ISCOMPONENET ADDER4B--对要调用的元件ADDER4B的界面端口进行定义PORT(CIN:IN STD_LOGIC;A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CONT:OUT STD_LOGIC);END COMPONENT ;SIGNAL CARRY_OUT:STD_LOGIC;--4位加法器的进位标志BEGINU1:ADDER4B --例化(安装)一个4位二进制加法器U1PORT MAP(CIN=>CIN,A=>A(3 DOWNTO 0),B=>B(3DOWNTO0),S=>S(3 DOWNTO 0),COUT=>CARRY_OUT);U2:ADDER4B --例化(安装)一个4位二进制加法器U2PORT MAP(CIN=>CARRY_OUT,A=>A(7 DOWNTO 4),B=>B(7 DOWNTO 4),S=>S (7 DOWNTO 4);CONT=>CONT);END ART;六进制计数器的源程序CNT6.VHD(十进制计数器的源程序CNT10.VHD与此类似)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6 ISPORT (CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC );END CNT6;ARCHITECTURE ART OF CNT6 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA)BEGINIF CLR='1' THEN CQI<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF ENA='1' THENIF CQI=“0101” THEN CQI<=“0000”;ELSE CQI<=CQI+'1';END IF;END IF;END IF;END PROCESS;PROCESS(CQI)BEGINIF CQI=“0000” THEN CARRY_OUT<='1';ELSE CARRY_OUT<='0';END IF;END PROCESS;CQ<=CQI;END ART;十进制计数器LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;ENTITY count10 ISPORT(clk: IN STD_LOGIC;seg: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END count10;ARCHITECTURE a1 OF count10 ISsignal sec: STD_LOGIC; signal q : STD_LOGIC_VECTOR(21 DOWNTO 0);signal num: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINprocess(clk) ----get 1 hz clock pulsebeginif clk'event and clk='1' then q<=q+1; end if;sec<=q(21); --get 1 hz clock pulseend process;timing: process(sec) beginif sec'event and sec='1' thenif num<9 then num<=num+1; else num<="0000"; end if;end if;end process;B1: block --bcd-7segsBegin --gfedcbaseg<= "0111111" when num=0 else"0000110" when num=1 else"1011011" when num=2 else"1001111" when num=3 else"1100110" when num=4 else"1101101" when num=5 else"1111101" when num=6 else"0000111" when num=7 else"1111111" when num=8 else"1101111" when num=9 else"0000000";end block;END a1;四位全加器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity add isport(a,b:in std_logic_vector(3 downto 0);cin:in std_logic;s:out std_logic_vector(3 downto 0);cout:out std_logic);end add;architecture beh of add isbeginprocess(a,b,cin)ariable x:std_logic_vector(3 downto 0);variable m,n,l:integer;beginm:=conv_integer(a);n:=conv_integer(b);l:=m+n+conv_integer(cin);x:=conv_std_logic_vector(l,4);s<=x(3 downto 0);cout<=x(3);end process;end beh;10位计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT ( CLK ,clr : IN STD_LOGIC ;CQ : OUT STD_LOGIC_VECTOR ( 3 DOWNTO 0 ));END ENTITY CNT10;ARCHITECTURE ONE OF CNT10 ISBEGINPROCESS ( CLK , clr )V ARIABLE LCQ : STD_LOGIC_VECTOR ( 3 DOWNTO 0 ); BEGINIF RST = …1‟ THEN LCQ := “0000”;ELSIF CLK‟EVENT AND CLK = …1‟ THENIF LCQ < 9 THEN LCQ := LCQ + 1;ELSE LCQ := “0000” ;END IF; END IF;CQ <= LCQ ;END PROCESS;END ARCHITECTURE ONE;八位串行二进制全加器use ieee.std_logic_1164.all;entity product_adder_subtracter isport(a,b:in std_logic_vector(7 downto 0);s:out std_logic_vector(8 downto 0));end;architecture behavioral of product_adder_subtracter isbeginbehavior:process(a,b) isvariable carry_in:std_logic;variable carry_out:std_logic;variable op2:std_logic_vector(b'range);beginop2:=b;end if;for index in 0 to 7 loopcarry_in:=carry_out;s(index)<=a(index) xor op2(index)xor carry_in ;carry_out:=(a(index)and op2(index))or(carry_in and (a(index) xor op2(index)));end loop;s(8)<=a(7) xor op2(7) xor carry_out;end process;end;8、根据已给出全加器VHDL程序,试写出一个四位逐位进位加法器的VHDL源程序。

vhdl BCD码加法器

实验一BCD码加法器一、实验目的了解BCD 码的构成。

了解BCD 码加法器的原理和设计实现方法。

巩固Quartus II 的使用。

二、实验内容与要求通过键盘输入两组4BIT的二进制数据,按照二进制加法器原理进行加和,求出和合进位,并通过电路静态数码LED显示灯输出显示,完成编译、综合、适配、仿真、实验箱上的硬件测试。

三、实验平台(1)硬件:计算机、GX-SOC/SOPC-DEV-LABCycloneII EP2C35F672C8核心板(2)软件:Quartus II四、实验原理BCD码是二进制编码的十进制码,也就是用4位二进制数来表示十进制中的0~9这十个数。

由于4位二进制数有0000~1111共16种组合,而十进制数只需对应4位二进制数的10种组合,故从4位二进制数的16种组合中取出10种组合来分别表示十进制中的0~9,则有许多不同的取舍方式,于是变形成了不同类型的BCD码。

当BCD码相加的值小于等于9时,结果仍旧是正确的BCD码;当两个码相加的结果大于9时,必须作加6的修正处理,对于大于19的值作加12的修正处理,对于大于29的值作加18的修正处理。

然后根据仿真进行实验及验证。

六、仿真截图七、硬件实现八、程序代码1LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY f_ADDER IsPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END f_ADDER;ARCHITECTURE fd1 Of f_ADDER Is Component HADDERPort( a,b: In Std_Logic;co,so: Out Std_Logic);END Component;Component oraPort(a,b: In Std_Logic;c: Out Std_Logic);END Component;Signal d,e,f: Std_Logic;BeginU1: HADDERPort Map(a=>X,b=>Y,Co=>d,so=>e);U2:HADDERPort Map(a=>e,b=>cin,Co=>f,so=>sum);U3:ora Port Map(a=>d,b=>f,c=>cout);END ARCHITECTURE fd1;2LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY HADDER IsPort (a,b: In Bit;Co, So: Out Bit);END HADDER;ARCHITECTURE fh1 Of HADDER Is BEGINSo <= (a Xor b);Co <= (a And b);END fh1;3LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY ora IsPort ( a: in Std_Logic;b: in Std_Logic;c: out Std_Logic);END ora;ARCHITECTURE org OF ora ISBEGINc <= a Or b;END org;4Library ieee;Use ieee.std_logic_1164.all;Entity Qadd isPort (a:in std_logic_VECTOR(7 DOWNTO 0);b:in std_logic_VECTOR(7 DOWNTO 0);--cin:in std_logic;s:out std_logic_VECTOR(7 DOWNTO 0));End Qadd;Architecture one of Qadd isSignal c0,c1,c2,c3,c4,c5,c6,c7 : std_logic;Component f_ADDERPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END Component;Beginu1 :F_ADDERPort map(sum=>s(0),cout=>c0,X=>a(0),Y=>b(0),cin=>'0'); u2 :F_ADDERPort map(sum=>s(1),cout=>c1,X=>a(1),Y=>b(1),cin=>c0 ); u3 : F_ADDERPort map(sum=>s(2),cout=>c2,X=>a(2),Y=>b(2),cin=>c1 ); u4 : F_ADDERPort map(sum=>s(3),cout=>c3,X=>a(3),Y=>b(3),cin=>c2 ); u5 : F_ADDERPort map(sum=>s(4),cout=>c4,X=>a(4),Y=>b(4),cin=>c3 ); u6 : F_ADDERPort map(sum=>s(5),cout=>c5,X=>a(5),Y=>b(5),cin=>c4 ); u7 :F_ADDERPort map(sum=>s(6),cout=>c6,X=>a(6),Y=>b(6),cin=>c5 ); u8 : F_ADDERPort map(sum=>s(7),cout=>c7,X=>a(7),Y=>b(7),cin=>c6 ); END;九、实验总结。

VHDL全加器的设计

实验四全加器的设计一、实验目的通过VHDL语言设计4位全加器,掌握加法器的设计方法;学习利用软件工具的模块封装(1位全加器)及连接使用方法,在软件工具的原理图输入法下完成4位全加器的设计。

二、实验原理根据数字电路全加器的理论知识,按图1所示的1位全加器的管脚图进行设计。

图 1 1位全加器管脚图三、实验内容用VHDL语言设计1位全加器,进行编译、波形仿真及器件编程。

代码一见附录,仿真图如下图 2 1位全加器功能仿真图使用原理图设计4位全加器进行编译、波形仿真及器件编程。

原理图如下仿真图如下用VHDL语言设计4位全加器,进行编译、波形仿真及器件编程,代码二见附录,仿真图如下图 5 4位全加器功能仿真图附录代码一、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity swqjq isport (a,b:in std_logic;ci:in std_logic;co:out std_logic;s:out std_logic);end swqjq;architecture zhang of swqjq isbeginprocess (a,b,ci)beginif(a='0'and b='0'and ci='0') thens<='0';co<='0';elsif(a='1'and b='0'and ci='0') thens<='1';co<='0';elsif(a='0'and b='1'and ci='0') thens<='1';co<='0';elsif(a='1'and b='1'and ci='0') thens<='0';co<='1';elsif(a='0'and b='0'and ci='1') thens<='1';co<='0';elsif(a='0'and b='1'and ci='1') thens<='0';co<='1';elsif(a='1'and b='0'and ci='1') thens<='0';co<='1';elses<='1';co<='1';end if;end process;end zhang;代码二、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport ( ci:in std_logic;a,b:in std_logic_vector(3 downto 0);s:out std_logic_vector(3 downto 0);co:out std_logic);end adder4b;architecture zhang of adder4b issignal sint:std_logic_vector(4 downto 0); signal aa,bb:std_logic_vector(4 downto 0); beginaa<='0'&a(3 downto 0);bb<='0'&b(3 downto 0);sint<=aa+bb+ci;s(3 downto 0)<=sint(3 downto 0);co<=sint(4);end zhang;。

vhdl通用十进制加法器

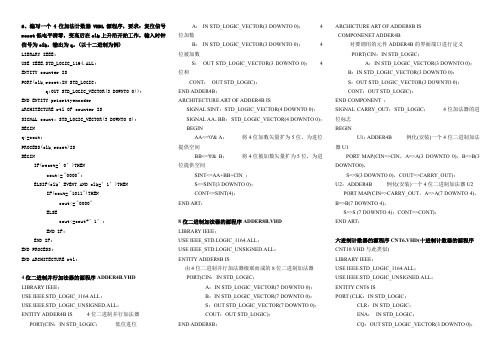

湖南人文科技学院课程设计报告课程名称:VHDL语言与EDA课程设计设计题目:通用十进制加法器系别:通信与控制工程系专业:电子信息工程班级:学生姓名:学号:起止日期:指导教师:教研室主任:指导教师评语:指导教师签名:年月日成绩评定项目权重成绩1、设计过程中出勤、学习态度等方面0.22、课程设计质量与答辩0.53、设计报告书写及图纸规范程度0.3总成绩教研室审核意见:教研室主任签字:年月日教学系审核意见:主任签字:年月日摘要随着科技的发展,通用十进制加法器的应用已广泛融入到现实生活中。

EDA 技术的应用引起电子产品及系统开发的革命性变革。

本文采用EDA技术设计,并以VHDL语言为基础制作的通用十进制加法器。

该系统借助于强大的EDA工具和硬件描述语言可实现两个一位以上的十进制数的加法,在输入两个十进制数之后,给出两个数的相加结果。

本设计充分利用VHDL“自顶向下”的设计优点以及层次化的设计概念,提高了设计的效率。

设计主要步骤:首先利用QUARTUS‖来编辑、编译、仿真各个模块;然后以原理图为顶层文件建立工程,再进行引脚锁定、编译、下载,最后采用杭州康芯电子有限公司生产的GW48系列/SOPC/EDA实验开发系统,进行硬件测试。

关键词:通用十进制加法器;EDA技术;VHDL语言; QUARTUS‖目录设计要求 (1)1、方案论证与对比 (1)1.1方案一 (1)1.2方案二 (1)1.3 方案的对比与选择 (2)2、设计原理 (2)3、通用十进制加法器的主要硬件模块 (3)3.1 4位BCD码全加器模块 (3)3.2八加法器的实现框图 (3)4、调试与操作 (4)4.1通用十进制加法器的功能仿真 (4)4.2模式选择与引脚锁定 (4)4.2.1模式选择 (4)4.2.2引脚锁定 (5)4.3设备与器件明细表 (6)4.4调试 (6)4.4.1软件调试 (6)4.4.2硬件调试 (6)5、总结与致谢 (7)5.1总结与思考 (7)5.2致谢 (7)附录 (8)附录一 (8)附录二 (9)参考文献 (11)通用十进制加法器设计要求1、用VHDL 硬件描述语言设计4位的BCD 码全加器;2、以4位BCD 码全加器为模块设计两位十进制数的加法。

vhdl编程实例

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

1用VHDL设计的一位二进制全加器的示例程序

1用VHDL设计的一位二进制全加器的示例程序VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种硬件编程语言,它使用结构化的方法来描述数字系统中的电路。

在设计一位二进制全加器之前,我们需要了解一下什么是二进制全加器。

二进制全加器是一种逻辑电路,用于将两个二进制位以及一个进位输入相加,并生成一个和输出以及一个进位输出。

以下是一个使用VHDL编写的一位二进制全加器的示例程序:```vhdl-- Entity声明entity full_adder isportA, B, Cin : in std_logic; -- 输入端口,分别对应两个二进制位和进位Sum, Cout : out std_logic -- 输出端口,分别对应和和进位end full_adder;-- Architecture实现architecture behavior of full_adder isbeginprocess(A, B, Cin)variable temp_sum : std_logic;begintemp_sum := (A xor B) xor Cin; -- 计算和值Sum <= temp_sum; -- 输出和值Cout <= (A and B) or (Cin and (A xor B)); -- 计算进位end process;end behavior;```该程序定义了一个名为`full_adder`的实体,它有3个输入端口(A,B和Cin)和2个输出端口(Sum和Cout)。

`std_logic`是VHDL中的一种数据类型,用于表示逻辑电平。

在架构部分,程序使用一个过程来计算和值(temp_sum)和进位(Cout)。

和值的计算通过使用异或(`xor`)操作符来实现,进位的计算则使用与(`and`)和或(`or`)逻辑操作符的组合来实现。

实验BCD码加法器

实验二 文本输入方式设计数字逻辑电路一、实验目的:1、 掌握VHDL 语言的基本语法和设计文件的基本结构。

2、 掌握组合逻辑电路的特性及设计和调试方法。

3、 掌握时序逻辑电路的特性及设计和调试方法。

4、 掌握常用的组合逻辑电路和时序逻辑电路的设计方法。

二、实验的硬件要求:1、 EDA/SOPC 实验箱。

2、 计算机。

三、实验原理数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。

组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。

时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。

1、组合逻辑电路①组合逻辑电路的定义通常组合逻辑电路可以用图1.1所示结构来描述。

其中,X0、X1、…、Xn 为输入信号, L0、L1、…、Lm 为输出信号。

输入和输出之间的逻辑函数关系可用式1.1表示: ②组合逻辑电路的设计方法组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组 合电路。

理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。

在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。

设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。

组合电路的基本设计步骤可用图1.2来表示。

③组合逻辑电路的特点及设计时的注意事项a)组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。

(实际电路中图 2.1 组合逻辑电路框图L0=F0(X0,X1,···Xn) · · ·Lm=F0(X0,X1,···Xn)(1.1)图 2.2 组合电路设计步骤示意图图还要考虑器件和导线产生的延时)。

并行二进制BCD码加法器VHDL设计

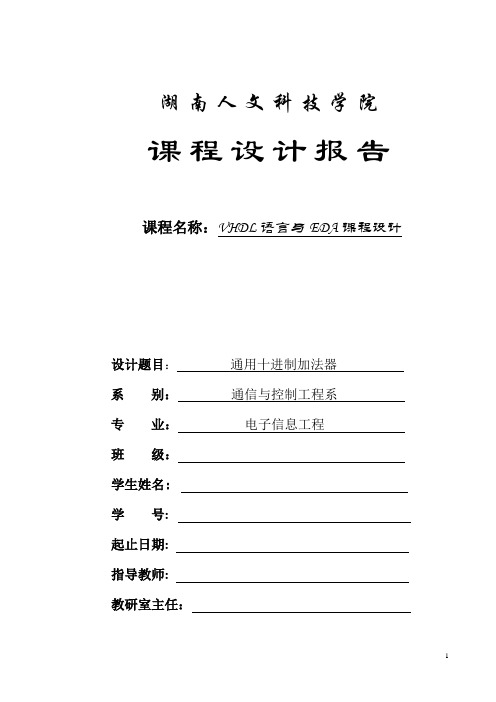

并行二进制BCD码加法器VHDL设计1.并行二进制加法器设计:下面是并行二进制加法器的VHDL设计:```vhdl--全加器entity full_adder isport(A, B, Cin : in std_logic;S, Cout : out std_logic);end entity;architecture behavioral of full_adder isbeginS <= A xor B xor Cin;Cout <= (A and B) or (Cin and (A xor B));end architecture;--4位并行二进制加法器entity parallel_binary_adder isport(A, B : in std_logic_vector(3 downto 0);S : out std_logic_vector(3 downto 0);Cout : out std_logic);end entity;architecture behavioral of parallel_binary_adder isport(A, B, Cin : in std_logic;S, Cout : out std_logic);signal C : std_logic;beginFA0 : full_adder port map(A(0), B(0), '0', S(0), C);FA1 : full_adder port map(A(1), B(1), C, S(1), C);FA2 : full_adder port map(A(2), B(2), C, S(2), C);FA3 : full_adder port map(A(3), B(3), C, S(3), Cout);end architecture;```我们先定义了一个全加器(`full_adder`)实体,包含了输入信号A、B、Cin以及输出信号S、Cout。

VHDL加法器设计1

VHDL 加法器设计设计要求:采用QuartusII 集成开发环境利用VHDL 硬件描述语言设计传播进位加法器,直接进位加法器,线形进位加法器,平方根进位加法器,并比较这四种加法器的性能。

为了便于比较性能,将四种加法器都设定为28位。

一、全加器设计全加器是上述四种加法器的基础部件,首先应当设计一位全加器。

设计原理:i i i iS ABC ABC ABC ABC A B C=+++=⊕⊕0i i C AB BC AC =++VHDL 程序:仿真结果:--一位全加器设计library ieee;use ieee.std_logic_1164.all; entity fulladd isport ( A: in std_logic;B: in std_logic; cin:in std_logic; sumbit:out std_logic; cout:out std_logic );end fulladd;architecture behav of fulladd is beginsumbit<=(A xor B) xor cin;cout<=(a and b) or (cin and a) or (cin and b); end behav;二、传播进位加法器设计实际上加法器就是是全加器的级联,其中的每个FA网络为一个全加器(采用上文所述的全加器)VHDL代码:--传播进位加法器library ieee;use ieee.std_logic_1164.all;use work.all;entity carry_propogate_adder isport (A: in std_logic_vector(27 downto 0);B: in std_logic_vector(27 downto 0);cin:in std_logic;sum:out std_logic_vector(27 downto 0);cout:out std_logic);end carry_propogate_adder;architecture behav of carry_propogate_adder issignal ct:std_logic_vector(28 downto 0);component fulladd isport (A: in std_logic;B: in std_logic;cin:in std_logic;sumbit:out std_logic;cout:out std_logic);end component;beginct(0)<=cin;cout<=ct(28);G1: for i in 0 to 27 generatel1:fulladd port map (A(i),B(i),ct(i),sum(i),ct(i+1));end generate G1;end behav;功能仿真:延时测定:由图中的两个时间bar 的差值可看出,sum 值和cout 值几乎同时计算出,其Tdelay=28.332ns (cin 无关)三、直接进位加法器设计 设计原理:首先将AB 输入转换为PG 输入,若每级的P 输入都是‘1’则直接将Ci 传给Co ,否则像传播进位加法器一样计算其AB-PG 转换网络原理:Fa 全加器原理:P A B G AB=⊕=o i iC G PC S P C =+=⊕VHDL 代码:-- FA 子单元 library ieee;use ieee.std_logic_1164.all;entity Fa isport (Pi,Gi,Ci:in std_logic; Coi,Si:out std_logic); end Fa;architecture Fabehav of Fa is beginCoi<=Gi or (Pi and Ci);Si<=Pi xor Ci; end Fabehav; --ABtoPG 转换网络 library ieee;use ieee.std_logic_1164.all;entity PGNet isport(Ai,Bi:in std_logic; Pi,Gi:out std_logic); end PGNet;architecture PGbehav of PGNet is beginPi<=Ai xor Bi;Gi<=Ai and Bi; end PGbehav; --传播进位加法器 library ieee;use ieee.std_logic_1164.all; entity bypass_adder is port(A,B:in std_logic_vector(27 downto 0); Ci:in std_logic; Sum:out std_logic_vector(27 downto 0); Co:out std_logic );end bypass_adder;architecture adderbehav of bypass_adder is component Fa is port (Pi,Gi,Ci:in std_logic; Coi,Si:out std_logic ); end component; component PGNet is port(Ai,Bi:in std_logic; Pi,Gi:out std_logic ); end component;signal P,G:std_logic_vector(27 downto 0); signal C:std_logic_vector(28 downto 0); signal BP:std_logic; begin C(0)<=Ci; G1: for i in 0 to 27 generate l1: PGNet port map(A(i),B(i),P(i),G(i)); end generate G1; G2: for i in 0 to 27 generate l2:Fa port map (P(i),G(i),C(i),C(i+1),Sum(i)); end generate G2; BP<='1' when P="11111111111111111111111111111111" else '0'; Co<=Ci when BP='1' else C(8); end adderbehav;功能仿真:延时仿真:当通过直接进位网络(图中testp值全部为1时),进位信号有一定提前,但由于计算所有的P值本身也需要一定时间,所以改善并不明显。

BCD码加法器

+ 7 → + 0111

………… …………

13 1011

1101在8421BCD码中是非法码,结果错误,如果加6修正后,则产生了进位信号,且本位

1101

+ 0110

…………

1,0011

“0011”也是正确的。

③若和产生进位,则结果错误,也需加6修正。如

8 1000

+ 9 → + 1001

卓越工程师班第一次大作业

用四位全加器构成

一位BCD码加法器

班级:001111

作者:00111116 江新远

实现方式一:器件

一、问题

用四位二进制全加器74LS283构成一位8421BCD码加法电路

二、74LS283介绍

74LS283是TTL双极型并行4位全加器,,特点是先行禁卫,因此运算速度很快,其外形为双列直插。它有两组4位二进制数输入 ,一位低位向本位的进位输入 ,有一组二进制输出 ,一个最高位的进位输出,改器件所完成的4位二进制加法如图所示。

由于S是二进制的,所以最后取S的后四位加6就好。但是为防止S的后四位加6,仍然大于10,故先用S1等于S的后四位加6,然后再取S1的后四位。

附代码:

library ieee;

use fhomework1 is

port(a,b:in std_logic_vector(3 downto 0);

c:outbit;

………… …………

17 1,0001

虽产生了进位,但本位和不正确,若加6修正

1,0001

+ 0110

…生错误的原因是8421BCD码为十进制,逢十进一,而四位二进制数是逢十六进一,故二者进位关系不同。其中刚好相差6,故需加6进行修正。

VHDL语言的位加法器的设计方案

基于 VHDL 语言的8位加法器的设计作者:吴中友(陕理工物理电子信息科学与技术专业07级1班,陕西汉中 723000)指导教师:蒋嫒[摘要]利用VHDL言语,实现两个4位并行进位加法器,然后将其级联成为一个8位加法器,再实现一个二进制转换成十进制动态显模块,以显示相加结果,并在仿真软MAX+plus II中进行仿真。

[关键词]VHDL、加法器、MAX+plus IIDesignof 8-bit Adder based on VHDLWu Zhongyou(Department of Physics,ShaanxiUniversity of Technology,Hanzhong,Shaanxi 723000)Tutor:Jiang YuanAbstract:using VHDL, and the road to achieve two 4-bit adder, and then cascade into an 8-bit adder, and then converted to decimal binary to achieve a dynamic explicit module to display the sum of the results, and the simulation software MAX + plus II for simulation.Key words VHDL, adder, MAX + plus II0.引言加法器是用来实现加法的器件,即它是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

加法器常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用,是计算机进行算术逻辑运算的基本部件。

研究加法器的实现对于电子硬件设计及其的理论发展的认识和理解具有重要意义。

1.设计原理加法器是数字系统中的基本逻辑器件。

vhdl全加器实验报告

vhdl全加器实验报告VHDL全加器实验报告引言:在数字电路设计领域,全加器是一种基本的逻辑电路。

它用于将两个二进制数相加,并产生相应的和与进位输出。

在本次实验中,我们将使用VHDL语言设计和模拟一个全加器电路,并通过实验验证其功能和正确性。

一、实验目的本实验的目的是通过设计和模拟一个VHDL全加器电路,加深对数字电路和VHDL语言的理解。

具体目标如下:1. 学习并掌握全加器的原理和电路结构;2. 掌握VHDL语言的基本语法和使用方法;3. 设计和模拟一个全加器电路,并验证其正确性;4. 分析和评估全加器电路的性能和优化方法。

二、全加器的原理和电路结构全加器是一种用于二进制加法的逻辑电路。

它接受两个输入位和一个进位输入位,并产生一个和输出位和一个进位输出位。

全加器的电路结构通常由两个半加器和一个或门组成。

半加器用于计算两个输入位的和,而或门用于计算进位输出位。

三、VHDL语言的基本语法和使用方法VHDL是一种硬件描述语言,用于描述和模拟数字电路。

它具有丰富的语法和功能,可以方便地进行电路设计和仿真。

VHDL语言的基本语法包括实体声明、端口声明、信号声明、过程声明等。

在本次实验中,我们将使用VHDL语言来描述和模拟全加器电路。

四、全加器电路的设计和模拟在本次实验中,我们将使用VHDL语言设计和模拟一个4位全加器电路。

首先,我们需要定义输入和输出信号,并声明全加器的实体和端口。

接下来,我们可以使用VHDL语言描述全加器的逻辑电路,包括半加器和或门的连接关系。

最后,我们可以使用仿真工具对全加器电路进行模拟,并观察输出结果。

五、全加器电路的验证和性能评估在模拟过程中,我们可以通过输入不同的二进制数来验证全加器电路的正确性。

我们可以逐个比较输入和输出的二进制数,并检查和进位输出是否与预期结果一致。

如果全加器电路能够正确地计算和输出结果,则说明设计和模拟过程是正确的。

此外,我们还可以评估全加器电路的性能和优化方法。

vhdl加法器二位BCD码加法器的VHDL源程序如下

vhdl加法器二位BCD码加法器的VHDL源程序如下导读:就爱阅读网友为您分享以下“二位BCD码加法器的VHDL源程序如下”资讯,希望对您有所帮助,感谢您对的支持!二位BCD码加法器的VHDL源程序如下:ibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity bcdadd is ---------------------实体部分port(key:in std_logic;---------------定义key输入口a0,a1,b0,b1:in integer range 0 to 9; -----定义两个加数的输入口a0l,a1l,b0l,b1l,s0l,s1l,s2l:out std_logic_vector(6 downto 0);----定义七个输出数码管s:out std_logic);----定义Key指示灯输出口end;architecture one of bcdadd is ----------结构体部分signal one:integer range 0 to 18; ----定义两个数的个位相加之后的信号signal ten:integer range 0 to 19; -----定义两个数的十位相加之后的信号signal co1,co2:integer range 0 to 1; ----定义个位和十位的进位信号signal s0,s1:integer range 0 to 15;beginp1:process(one,ten,a0,b0,a1,b1,co1)----第一个进程,进行加运算beginone<=a0+b0; --------------------个位相加之和if one>9 then --------------------和大于9,进位为1 co1<=1;s0<=one-10; -----------------------个位的值else -----------------------和小于9,进位为0co1<=0;s0<=one; -------------------------个位的值end if;ten<=a1+b1+co1;----------------------十位相加值和,加数包括个位来的进位if ten>9 then -------------------和大于9,进位为1co2<=1;s1<=ten-10;-------------------十位的值else ----------------------------------和小于9,进位为0co2<=0;s1<=ten;-----------------------十位的值end if;end process p1;p2:process(a0,a1,b0,b1) ----------第二个进程,两个加数的输出数码管显示译码begincase a0 is ----------------------被加数的个位显示译码when 0=>a0l<=“1000000”;when 1=>a0l<=“1111001”;when 2=>a0l<=“0100100”;when 3=>a0l<=“0110000”;when 4=>a0l<=“0011001”;第1页共4页when 5=>a0l<=“0010010”; when 6=>a0l<=“0000010”; when 7=>a0l<=“1111000”; when 8=>a0l<=“0000000”; whenothers=>a0l<=“ZZZZZZZ”; end case; case a1 is ------------------------------被加数的十位显示译码when 0=>a1l<=“1000000”; when 1=>a1l<=“1111001”; when 2=>a1l<=“0100100”; when 3=>a1l<=“0110000”; when 4=>a1l<=“0011001”; when 5=>a1l<=“0010010”; when 6=>a1l<=“0000010”; when 7=>a1l<=“1111000”; when 8=>a1l<=“0000000”; when 9=>a1l<=“0010000”; when others=>a1l<=“ZZZZZZZ”; end case; case b0 is-----------------------------加数的个位显示译码when 0=>b0l<=“1000000”; when 1=>b0l<=“1111001”; when 2=>b0l<=“0100100”; when 3=>b0l<=“0110000”; when 4=>b0l<=“0011001”; when 5=>b0l<=“0010010”; when 6=>b0l<=“0000010”; when8=>b0l<=“0000000”; when 9=>b0l<=“0010000”; when others=>b0l<=“ZZZZZZZ”; end case; case b1 is ----------------------------加数的十位显示译码when 0=>b1l<=“1000000”; when 1=>b1l<=“1111001”; when 2=>b1l<=“0100100”; when 3=>b1l<=“0110000”; when 4=>b1l<=“0011001”; when 5=>b1l<=“0010010”; when 6=>b1l<=“0000010”; when 7=>b1l<=“1111000”; when 8=>b1l<=“0000000”; when 9=>b1l<=“0010000”; when others=>b1l<=“ZZZZZZZ”;第2页共4页end case;end process p2;p3:process(key,s0,s1,co2,a0,a1,b0,b1) --------第三个进程,和的显示译码以及输入大于9是的出beginif key=…0‟ or a0>9 or b0>9 o r a1>9 or b1>9 then --当key等于0或者两个输入中的任何一个位大于9,和的数码显示均为“Z”状态s0l<=“ZZZZZZZ”;s1l<=“ZZZZZZZ”;s2l<=“ZZZZZZZ”;elsecase s0 is-------------------------------和的个位显示译码when 0=>s0l<=“1000000”;when 1=>s0l<=“1111001”;when 2=>s0l<=“0100100”;when 3=>s0l<=“0110000”;when 4=>s0l<=“0011001”;when 5=>s0l<=“0010010”;when 6=>s0l<=“0000010”;when 7=>s0l<=“1111000”;when 8=>s0l<=“0000000”;when 9=>s0l<=“0010000”;wh en others=>s0l<=“ZZZZZZZ”; end case;case s1 is--------------------------------和的十位显示译码when 0=>s1l<=“1000000”;when 1=>s1l<=“1111001”;when 2=>s1l<=“0100100”;when 3=>s1l<=“0110000”;when 4=>s1l<=“0011001”;when 5=>s1l<=“0010010”;when 6=>s1l<=“0000010”;when 7=>s1l<=“1111000”;when 8=>s1l<=“0000000”;when 9=>s1l<=“0010000”;when others=>s1l<=“ZZZZZZZ”; end case;case co2 is --------------------------和的百位显示译码when 0=>s2l<=“1000000”;when 1=>s2l<=“1111001”;end case;end if;end process p3;第3页共4页p4:process(key) -------------第四个进程,设置key的指示灯beginif key=…1‟ then s<=…1‟ ; else s<=…0‟;end if;end process p4;end;第4页共4页百度搜索“就爱阅读”,专业资料,生活学习,尽在就爱阅读网,您的在线图书馆。

vhdl 加法器

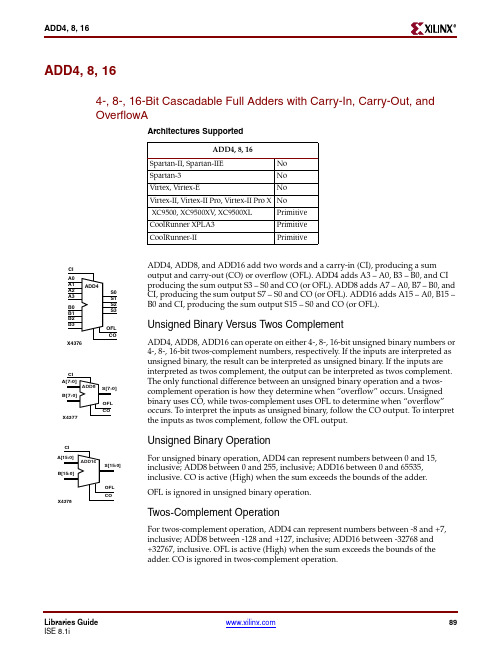

ADD4, 8, 164-, 8-, 16-Bit Cascadable Full Adders with Carry-In, Carry-Out, and OverflowAArchitectures SupportedADD4, ADD8, and ADD16 add two words and a carry-in (CI), producing a sum output and carry-out (CO) or overflow (OFL). ADD4 adds A3 – A0, B3 – B0, and CI producing the sum output S3 – S0 and CO (or OFL). ADD8 adds A7 – A0, B7 – B0, and CI, producing the sum output S7 – S0 and CO (or OFL). ADD16 adds A15 – A0, B15 – B0 and CI, producing the sum output S15 – S0 and CO (or OFL).Unsigned Binary Versus Twos ComplementADD4, ADD8, ADD16 can operate on either 4-, 8-, 16-bit unsigned binary numbers or 4-, 8-, 16-bit twos-complement numbers, respectively. If the inputs are interpreted as unsigned binary, the result can be interpreted as unsigned binary. If the inputs are interpreted as twos complement, the output can be interpreted as twos complement. The only functional difference between an unsigned binary operation and a twos-complement operation is how they determine when “overflow” occurs. Unsigned binary uses CO, while twos-complement uses OFL to determine when “overflow” occurs. To interpret the inputs as unsigned binary, follow the CO output. To interpret the inputs as twos complement, follow the OFL output.Unsigned Binary OperationFor unsigned binary operation, ADD4 can represent numbers between 0 and 15, inclusive; ADD8 between 0 and 255, inclusive; ADD16 between 0 and 65535, inclusive. CO is active (High) when the sum exceeds the bounds of the adder.OFL is ignored in unsigned binary operation.T wos-Complement OperationFor twos-complement operation, ADD4 can represent numbers between -8 and +7, inclusive; ADD8 between -128 and +127, inclusive; ADD16 between -32768 and +32767, inclusive. OFL is active (High) when the sum exceeds the bounds of the adder. CO is ignored in twos-complement operation.ADD4, 8, 16Spartan-II, Spartan-IIE No Spartan-3No Virtex, Virtex-ENo Virtex-II, Virtex-II Pro, Virtex-II Pro X NoXC9500, XC9500XV , XC9500XL Primitive CoolRunner XPLA3Primitive CoolRunner-IIPrimitiveADD8 Implementation Spartan-II, Spartan-IIE, Virtex, Virtex-E Libraries GuideADD8 Implementation Spartan-3, Virtex-II, Virtex-II Pro, Virtex-II Pro XADD4 Implementation XC9500/XV/XL, CoolRunner XPLA3, CoolRunner-II Libraries GuideADD8 Implementation XC9500/XV/XL, CoolRunner XPLA3, CoolRunner-II UsageThis design element is schematic or inference only -- no instantiation.VHDL Inference Code (ADD4)architecture Behavioral of ADD issignal sum: std_logic_vector(WIDTH-1 downto 0);signal zeros: std_logic_vector(WIDTH-1 downto 0) := (others => '0'); beginprocess (CI, A, B, sum)beginsum <= ('0' & A) + ('0' & B) + (zeros & CI);S <= sum(WIDTH-1 downto 0);CO <= sum(WIDTH);end process;end Behavioral;Verilog Inference Code (ADD4)always @ (A or B or CI)begin{CO,sum} <= A + B + CI;end Libraries Guide。

2位BCD码加法器

2位BCD码加法器一、实验内容:利用V erilog HDL语言,编写一个2为BCD码加法器程序,并在DE2板是实现功能的运用。

A0、A1,B0、B1分别是2个输入数字,S0-S2为输出,经过BCD加法器的运算,能实现BCD码加法功能。

设计思路:A0、B0分别是A、B的低位,相加的值T0=A0+B0,若T0>10,则Z0赋值为10,同时进位C0=1,和值低位S0=T0-Z0;同理,高位A1、B1,T1=A1+B1+C0,若T1>10,则Z1=10,进位C1=1,和值高位S1=T1-Z1;S2=C1。

二、实验源程序:1)BCD加法器module BCDadder(A0,A1,B0,B1,S0,S1,S2,clear); //定义输入模块input [3:0]A0; //考虑到A0、B0、A1、B1的值可能input [3:0]A1; 超过十进制数8,顾定义长度为4位;input [3:0]B0;input [3:0]B1;input clear;output S0;output S1;output S2;reg [3:0]S0;reg [3:0]S1;reg [3:0]S2;reg [4:0]C0;reg [4:0]C1;reg [4:0]T0; //低位和值可能超过16,所以定义T0、T1长reg [4:0]T1; 度为5;reg [4:0]Z0;reg [4:0]Z1;always @(posedge clear) //以每一次复位上升沿到来开始计算和值;beginT0=A0+B0; //低位相加和值赋T0;if(T0>9)beginZ0=10; //如果低位相加有进位,则赋值Z0=10;C0=1; //如果T0>9,则有进位,此时C0=1;endelsebeginZ0=0;C0=0;endbeginT1=A1+B1+C0; //高位为A1加B1再加进位C0,赋值给T1;if(T1>9)beginZ1=10;C1=1;endelsebeginZ1=0;C1=0;endendbeginS0=T0-Z0; //和值S0到S1赋值;S1=T1-Z1;S2=C1;endendendmodule2)输入数A0、A1、B0、B1显示module indisplay(A0,A1,B0,B1,displayA0,displayA1,displayB0,displayB1); input [3:0]A0;input [3:0]A1;input [3:0]B0;input [3:0]B1;output [6:0]displayA0;output [6:0]displayA1; //定义7段数码管的输出;output [6:0]displayB0;output [6:0]displayB1;reg [6:0]displayA0;reg [6:0]displayA1; //定义其类型为寄存器类型;reg [6:0]displayB0;reg [6:0]displayB1;always@(A0 or A1 or B0 or B1) //当输入A、B中任何一位变化,即执行输入显示程序;begincase(A0) //输入A0显示4'd0:displayA0=7'b1000000;4'd1:displayA0=7'b1111001;4'd2:displayA0=7'b0100100;4'd3:displayA0=7'b0110000;4'd4:displayA0=7'b0011001;4'd5:displayA0=7'b0010010;4'd6:displayA0=7'b0000010;4'd7:displayA0=7'b1011000;4'd8:displayA0=7'b0000000;4'd9:displayA0=7'b0010000;default: displayA0=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(A1) //输入A1显示4'd0:displayA1=7'b1000000;4'd1:displayA1=7'b1111001;4'd2:displayA1=7'b0100100;4'd3:displayA1=7'b0110000;4'd4:displayA1=7'b0011001;4'd5:displayA1=7'b0010010;4'd6:displayA1=7'b0000010;4'd7:displayA1=7'b1011000;4'd8:displayA1=7'b0000000;4'd9:displayA1=7'b0010000;default:displayA1=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(B0) //输入B0显示4'd0:displayB0=7'b1000000;4'd1:displayB0=7'b1111001;4'd2:displayB0=7'b0100100;4'd3:displayB0=7'b0110000;4'd4:displayB0=7'b0011001;4'd5:displayB0=7'b0010010;4'd6:displayB0=7'b0000010;4'd7:displayB0=7'b1011000;4'd9:displayB0=7'b0010000;default:displayB0=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(B1) //输入B1显示4'd0:displayB1=7'b1000000;4'd1:displayB1=7'b1111001;4'd2:displayB1=7'b0100100;4'd3:displayB1=7'b0110000;4'd4:displayB1=7'b0011001;4'd5:displayB1=7'b0010010;4'd6:displayB1=7'b0000010;4'd7:displayB1=7'b1011000;4'd8:displayB1=7'b0000000;4'd9:displayB1=7'b0010000;default:displayB1=7'b1000000; //默认时,数码管显示数字“0”;endcaseendendmodule3)输出显示module display(S0,S1,S2,display1,display2,display3);input[3:0] S0;input[3:0] S1;input[3:0] S2;output[6:0] display1;output[6:0] display2;output[6:0] display3;reg[6:0] display1;reg[6:0] display2;reg[6:0] display3;always @(S0 or S1 or S2) //当和值S中的任何一位变化,就开始执行显示程序;begincase(S0) //和值第一位S0显示;4'd0:display1=7'b1000000;4'd1:display1=7'b1111001;4'd2:display1=7'b0100100;4'd3:display1=7'b0110000;4'd4:display1=7'b0011001;4'd5:display1=7'b0010010;4'd6:display1=7'b0000010;4'd7:display1=7'b1011000;4'd8:display1=7'b0000000; //默认时,数码管显示数字“0”;default: display1=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(S1) //和值第二位S1显示;4'd0:display2=7'b1000000;4'd1:display2=7'b1111001;4'd2:display2=7'b0100100;4'd3:display2=7'b0110000;4'd4:display2=7'b0011001;4'd5:display2=7'b0010010;4'd6:display2=7'b0000010;4'd7:display2=7'b1011000;4'd8:display2=7'b0000000;4'd9:display2=7'b0010000;default:display2=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(S2) //和值第三位S2显示;4'd0:display3=7'b1000000;4'd1:display3=7'b1111001;4'd2:display3=7'b0100100;4'd3:display3=7'b0110000;4'd4:display3=7'b0011001;4'd5:display3=7'b0010010;4'd6:display3=7'b0000010;4'd7:display3=7'b1011000;4'd8:display3=7'b0000000;4'd9:display3=7'b0010000;default:display3=7'b1000000; //默认时,数码管显示数字“0”;endcaseendendmodule4)模块连接三、实验仿真与实现1)BCD加法器仿真输入A为24,B为48,当clear复位后,和值S为72,与理论一致,故BCD加法器正常;输入A为06,B为14,在clear的上升沿来到是计算和值,display得出相应值,从仿真结果可以看出程序正常实现BCD码加法器功能。

用VHDL语言设计BCD-七段译码

简单电路的VHDL语言描述一、实验内容1.用VHDL语言设计BCD-七段译码驱动芯片,编译、下载,并进行电路功能验证。

(1) 程序源代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DELED ISPORT(NUM:IN STD_LOGIC_VECTOR(3 DOWNTO 0);A,B,C,D,E,F,G: OUT STD_LOGIC);END ENTITY DELED;ARCHITECTURE ART OF DELED ISSIGNAL LED:STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINPROCESS(NUM)BEGINCASE NUM ISWHEN "0000"=>LED<="1111110";WHEN "0001"=>LED<="0110000";WHEN "0010"=>LED<="1101101";WHEN "0011"=>LED<="1111001";WHEN "0100"=>LED<="0110011";WHEN "0101"=>LED<="1011011";WHEN "0110"=>LED<="1011111";WHEN "0111"=>LED<="1110000";WHEN "1000"=>LED<="1111111";WHEN "1001"=>LED<="1111011";WHEN "1010"=>LED<="1110111";WHEN "1011"=>LED<="0011111";WHEN "1100"=>LED<="1001110";WHEN "1101"=>LED<="0111101";WHEN "1110"=>LED<="1001111";WHEN OTHERS=>LED<="1000111";END CASE;END PROCESS;A<=LED(6);B<=LED(5);C<=LED(4);D<=LED(3);E<=LED(2);F<=LED(1);G<=LED(0);END ART;(2) 程序的编译和电路功能的仿真结果电路的编译电路功能的仿真(3) 电路的引脚分配电路引脚分配图2.用VHDL语言设计一个分频器,输出100Hz方波的电路,编译、仿真、下载,并进行电路功能的验证。

Verilog HDL 二位BCD码加法器

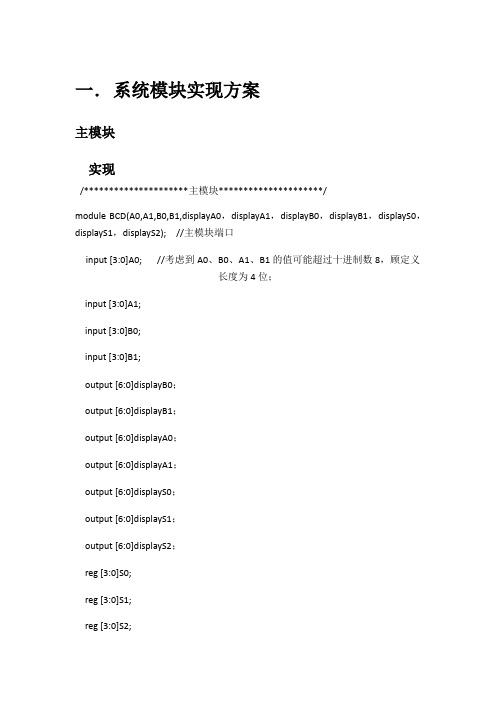

一.系统模块实现方案主模块实现/*********************主模块*********************/module BCD(A0,A1,B0,B1,displayA0,displayA1,displayB0,displayB1,displayS0,displayS1,displayS2); //主模块端口input [3:0]A0; //考虑到A0、B0、A1、B1的值可能超过十进制数8,顾定义长度为4位;input [3:0]A1;input [3:0]B0;input [3:0]B1;output [6:0]displayB0;output [6:0]displayB1;output [6:0]displayA0;output [6:0]displayA1;output [6:0]displayS0;output [6:0]displayS1;output [6:0]displayS2;reg [3:0]S0;reg [3:0]S1;reg [3:0]S2;reg [4:0]C0;reg [4:0]C1;reg [4:0]T0; //低位和值可能超过16,所以定义T0、T1长度为5;reg [4:0]T1;reg [4:0]Z0;reg [4:0]Z1;always //不停重复;beginT0=A0+B0; //低位相加和值赋T0;if(T0>9)beginZ0=10; //如果低位相加有进位,则赋值Z0=10;C0=1; //如果T0>9,则有进位,此时C0=1;endelsebeginZ0=0;C0=0;endbeginT1=A1+B1+C0; //高位为A1加B1再加进位C0,赋值给T1;if(T1>9)beginZ1=10;C1=1;endelsebeginZ1=0;C1=0;endendbeginS0=T0-Z0; //和值S0到S1赋值;S1=T1-Z1;S2=C1;endenddisplay in0(displayA0,A0);display in1(displayA1,A1);display in2(displayB0,B0);display in3(displayB1,B1);display out0(displayS0,S0);display out1(displayS1,S1);display out2(displayS2,S2);endmodule说明由于实验所用开发板芯片应用EP2C35F672C6,不设置时序,always结构让程序处于不停执行状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用VHDL 设计快速BCD 码加法器

Ξ

The D esign of Rap id Adder Usi ng VHDL

南京邮电学院 (南京210003) 张生平 薛 梅

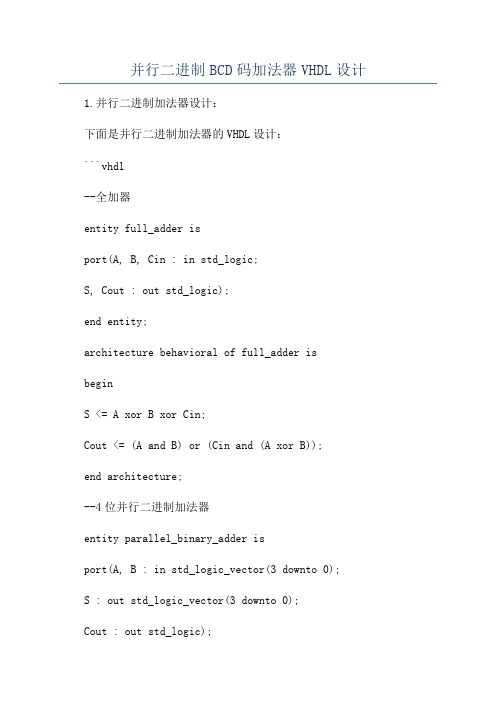

【摘 要】 介绍了一种多位BCD 码快速加法器的设计方法,并给出了3位BCD 码加法器的V HDL 源程序和在Foundati on Series 3.1i 环境中的模拟结果。

关键词:VHDL ,BCD ,程序【Abstract 】 T h is p ap er in troduces a w ay fo r design ing rap id adder ,and an exam p le of 32b it 2BCD 2adder is p rovided in V HDL ,and also the si m u lati on resu lt in Foundati on Series 3.1i is given .

Keywords :VHSI C Hardware D escr iption Language ,B i nary Coded D ec i m a l ,program

通常对BCD 操作数进行计算的方法是将BCD 输入变换成二进制数,按正数的二进制格式进行计

算,然后把二进制数计算结果变换回BCD 符号。

例如加法运算,首先按二进制格式进行运算,然后进行修正。

再用中规模集成电路设计多位BCD 数加法器,采用二进制加法器(如74283)构成BCD 加法器然后进行级连,或直接用BCD 加法器(如M C 14560)进行级连。

这样构成的加法器,位数增加,速度显著降低。

随着可编程逻辑器件的出现,可以将多位的BCD 加法器做到可编程器件内部,图

1

图1 BCD 数直接相加示意图

所示为3位BCD 加法器的设计方法示意图。

其设计

思想如下:两个BCD 数A 和B 是12位(按二进制)的操作数,代表000-999之间的十进制数。

首先将A 、B 按二进制数相加得和数E ,并通过加法生成了进位C 4、C 8、C 12。

然后,利用每个4位数组上加6(0110)来调整加法结果E ,得到调整结果F ,并生成进位D 4、D 8、D 12,结合以上两次运算结果和进位,产生和数和进位位。

和产生的基本思想为:两个BCD 数相加,同时计算出直接按二进制相加和需进行十进制调整的两种结果,然后按位在两种结果中选择其一作为和数。

选择的依据为:在按二进制加和十进制调整时,只要其中之一出现进位或两者都出现进位,则和应取调整后的结果;若按二进制加和十进制调整均无进位,则和数应取按二进制加的结果。

以下给出3位BCD 码加法器的V HDL 源程序以及在Foundati on Series 3.1i 环境中的仿真结果(见图2)。

3位BCD 码加法器的V HDL 源程序如下:lib rary IEEE ;

u se IEEE .std logic 1164.all ;u se IEEE .std logic un signed .all ;en tity bcdadd 3is po rt (

a :in STD LO G I C V ECTO R (11

dow n to 0);

b :in STD LO G I C V ECTO R (11dow n to 0);

・

22・电子工程师

计算机应用 V ol .27N o .6 2001

Ξ收稿日期:2001—03—27

图2 3位BCD 加法器仿真结果

sum :ou t STD LO G I C V ECTO R (11dow n to 0);

c :ou t STD LO G I C );en

d bcdadd 3;

arch itectu re bcdadd 3 arch of bcdadd 3is begin

p rocess (a ,b )

variab le e 04:std logic vecto r (4dow n 2to 0);

variab le e 48:std logic vecto r (4dow n 2to 0);

variab le e 812:std logic vecto r (4dow n to 0);

variab le f 04:std logic vecto r (4dow n 2to 0);

variab le f 48:std logic vecto r (4dow n 2to 0);

variab le f 812:std logic vecto r (4dow n to 0);begin

e 04:=(’0’&a (3dow n to 0))+b (3dow n to 0);

e 48:=(’0’&a (7dow n to 4))+b (7dow n to

4)+e 04(4);

e 812:=(’0’&a (11dow n to 8))+b (11dow n to 8)+e 48(4);

f 04:=(’0’&e 04(3dow n to 0))+"0110"; f 48:=(’0’&e 48(3dow n to 0))+"0110"+f 04(4);

f 812:=(’0’&e 812(3dow n to 0))+"0110"+f 48(4);

if (e 812(4)=’1’o r f 812(4)=’1’)then sum (11dow n to 8)<=f 812(3dow n to 0);

else

sum (11dow n to 8)<=e 812(3dow n to 0)+f 48(4);

end if ;

if (e 48(4)=’1’o r f 48(4)=’1’)then

sum (7dow n to 4)<=f 48(3dow n to 0);

else

sum (7dow n to 4)<=e 48(3dow n to 0)+f 04(4);

end if ;

if (e 04(4)=’1’o r f 04(4)=’1’)then

sum (3dow n to 0)<=f 04(3dow n to 0);

else

sum (3dow n to 0)<=e 04(3dow n to 0);

end if ;

c <=e 812(4)o r f 812(4); en

d p rocess ;end bcdadd 3 arch ;

根据以上思路,很容易实现多位BCD 数相加。

且运用上述设计方法,BCD 数位数增加更能体现出其优越性。

将利用上述设计方法设计的BCD 码加法器做到FPGA 中,占用资源相对较少,且运算速度较快。

参 考 文 献

1 李琼瑞.国外最新应用电路设计精选.北京:电子工业出

版社,1998年9月

2 边计年.用V HDL 设计电子线路.北京:清华大学出版

社,2001年9月

3 侯伯亨,顾新.V HDL 硬件描述语言数字逻辑电路设计.

西安:西安电子科技大学出版社,1999年9月

4 张豫滇,谢劲草.电子电路设计与实验技术.南京:南京邮

电学院,2001年3月 ■

《电子工程师》愿做广大电子工程师们的知心朋友

・

32・张生平,等:用VHDL 设计快速BCD 码加法器。