电力电子技术第3版仿真实验模型第1章4

电力电子技术(第3版)PPT 第一章 电力电子器件

Date:

2021-6-26

Page: 25

§1.3 晶闸管的保护、扩容和简单测试

§1.3 晶闸管的保护、扩容和简单测试

2) 非线性电阻保护

硒堆由成组串联的硒整流片构成,如图所示为硒堆保护几种接 法。(a)图为单相时的接法。单相时用两组对接后再与电源并联; (b)、(c)为三相的接法,三相时用三组对接成Y形或用六组结成D形。

硒堆保护几种接法 a)单相连接 b)三相Y型连接 c)三相△连接

(1)电阻均流 如图b)所示,在并联的各晶闸管中串入一小电阻R是最简便的均流方

法。均流电阻R由下式决定: R (0.5 ~ 2)UT () I Ta

串入均流电阻R后,电流分配不均匀度可大大地改善,但因电阻上有损耗, 并且对动态均流不起作用,只适用于小功率场合。对于大电流器件的并联,均 流可领先各并联支路的快熔电阻、电抗器电阻和连接导线电阻的总和来达到。

Date:

2021-6-26

Page: 31

§1.3 晶闸管的保护、扩容和简单测试

(1)静态均压(正反向阻断状态下的均压)

Date:

2021-6-26

Page: 32

§1.3 晶闸管的保护、扩容和简单测试

(2)动态均压(开通过程与关断过程的均压)

Date:

2021-6-26

Page: 33

§1.3 晶闸管的保护、扩容和简单测试

IF

UROM URSM

+

_

电力电子仿真实验

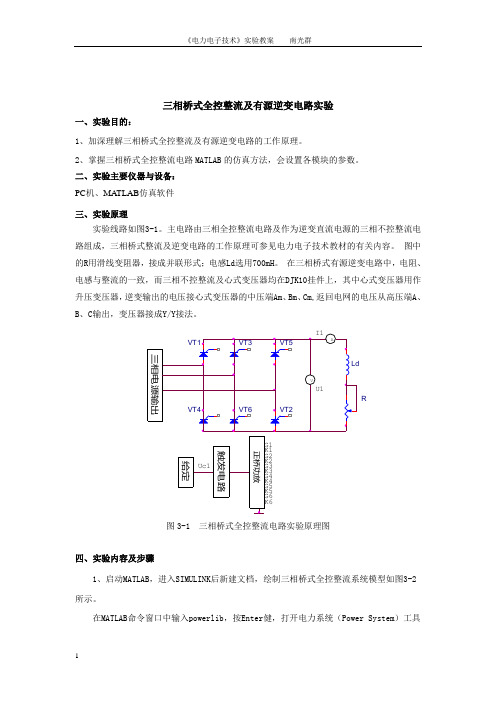

三相桥式全控整流及有源逆变电路实验一、实验目的:1、加深理解三相桥式全控整流及有源逆变电路的工作原理。

2、掌握三相桥式全控整流电路MATLAB 的仿真方法,会设置各模块的参数。

二、实验主要仪器与设备: PC 机、MATLAB 仿真软件 三、实验原理实验线路如图3-1。

主电路由三相全控整流电路及作为逆变直流电源的三相不控整流电路组成,三相桥式整流及逆变电路的工作原理可参见电力电子技术教材的有关内容。

图中的R 用滑线变阻器,接成并联形式;电感Ld 选用700mH 。

在三相桥式有源逆变电路中,电阻、电感与整流的一致,而三相不控整流及心式变压器均在DJK10挂件上,其中心式变压器用作升压变压器,逆变输出的电压接心式变压器的中压端Am 、Bm 、Cm,返回电网的电压从高压端A 、B 、C 输出,变压器接成Y/Y 接法。

R图3-1 三相桥式全控整流电路实验原理图四、实验内容及步骤1、启动MATLAB ,进入SIMULINK 后新建文档,绘制三相桥式全控整流系统模型如图3-2所示。

在MATLAB 命令窗口中输入powerlib ,按Enter 健,打开电力系统(Power System )工具箱,或在MATLAB的工具栏中,打开SIMULINK的库浏览器,单击SimPowerSystems进入电力系统工具箱。

从电源模块库(Electrical Sources)中选取交流电压源(Voltage Source),从电力电子器件模块库(Power Electronics)选取通用变换器桥模块(Universal Bridge),从元件模块库(Elements)中选取串联RLC负载(Series RLC Branch),从测量模块库(Measurements)选取电压测量(Voltage Measurement)、电流测量(Current Measurement),从连接器模块库(Connectors)选取接地(输入)(Groud input)、接地(输出)(Groud output)、总线(Bus Bar,vert),从Extra library 中的Control Blocks选取同步6脉冲触发器(Synchronized 6-Pulse Generator)。

《电力电子技术仿真实验》指导书

《电力电子技术实验》指导书合肥师范学院电子信息工程学院实验一电力电子器件仿真过程:进入MATLAB环境,点击工具栏中的Simulink选项。

进入所需的仿真环境,如图1.1所示。

点击File/New/Model新建一个仿真平台。

点击左边的器件分类,找到Simulink和SimPowerSystems,分别在他们的下拉选项中找到所需的器件,用鼠标左键点击所需的元件不放,然后直接拉到Model平台中。

图1.1实验一的具体过程:第一步:打开仿真环境新建一个仿真平台,根据表中的路径找到我们所需的器件跟连接器。

提取出来的器件模型如图1.2所示:图1.2第二步,元件的复制跟粘贴。

有时候相同的模块在仿真中需要多次用到,这时按照常规的方法可以进行复制跟粘贴,可以用一个虚线框复制整个仿真模型。

还有一个常用方便的方法是在选中模块的同时按下Ctrl键拖拉鼠标,选中的模块上会出现一个小“+”好,继续按住鼠标和Ctrl键不动,移动鼠标就可以将模块拖拉到模型的其他地方复制出一个相同的模块,同时该模块名后会自动加“1”,因为在同一仿真模型中,不允许出现两个名字相同的模块。

第三步,把元件的位置调整好,准备进行连接线,具体做法是移动鼠标到一个器件的连接点上,会出现一个“十字”形的光标,按住鼠标左键不放,一直到你所要连接另一个器件的连接点上,放开左键,这样线就连好了,如果想要连接分支线,可以要在需要分支的地方按住Ctrl键,然后按住鼠标左键就可以拉出一根分支线了。

在连接示波器时会发现示波器只有一个接线端子,这时可以参照下面示波器的参数调整的方法进行增加端子。

在调整元件位置的时候,有时你会遇到有些元件需要改变方向才更方便于连接线,这时可以选中要改变方向的模块,使用Format菜单下的Flip block 和Rotate block两条命令,前者改变水平方向,后者做90度旋转,也可以用Ctrl+R来做90度旋转。

同时双击模块旁的文字可以改变模块名。

高玉良《电路与模拟电子技术》第3版全部习题答案

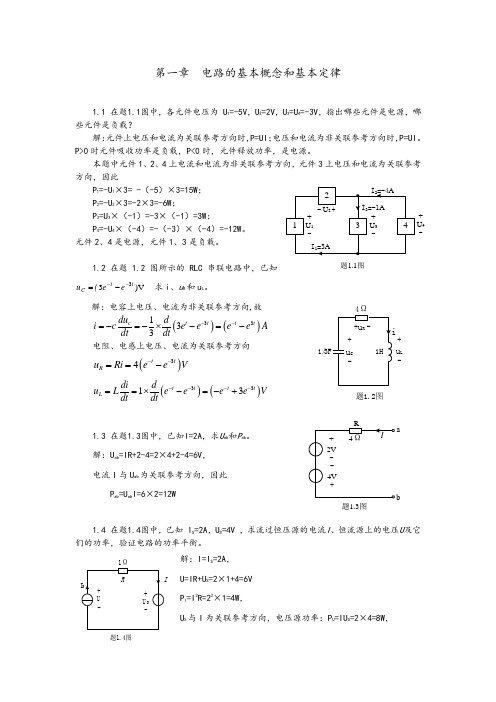

第一章 电路的基本概念和基本定律1.1 在题1.1图中,各元件电压为 U 1=-5V ,U 2=2V ,U 3=U 4=-3V ,指出哪些元件是电源,哪些元件是负载?解:元件上电压和电流为关联参考方向时,P=UI ;电压和电流为非关联参考方向时,P=UI 。

P>0时元件吸收功率是负载,P<0时,元件释放功率,是电源。

本题中元件1、2、4上电流和电流为非关联参考方向,元件3上电压和电流为关联参考方向,因此P 1=-U 1×3= -(-5)×3=15W ; P 2=-U 2×3=-2×3=-6W ; P 3=U 3×(-1)=-3×(-1)=3W ; P 4=-U 4×(-4)=-(-3)×(-4)=-12W 。

元件2、4是电源,元件1、3是负载。

1.2 在题 1.2图所示的RLC 串联电路中,已知)V 33t t C e e (u ---= 求i 、u R 和u L 。

解:电容上电压、电流为非关联参考方向,故()()33133t t t t c du di ce e e e A dt dt--=-=-⨯-=- 电阻、电感上电压、电流为关联参考方向()34t t R u Ri e e V --==- ()()3313t t t t L di du Le e e e V dt dt----==⨯-=-+1.3 在题1.3图中,已知I=2A ,求U ab 和P ab 。

解:U ab =IR+2-4=2×4+2-4=6V , 电流I 与U ab 为关联参考方向,因此P ab =U ab I=6×2=12W1.4 在题1.4图中,已知 I S =2A ,U S =4V ,求流过恒压源的电流I 、恒流源上的电压U 及它们的功率,验证电路的功率平衡。

解:I=I S =2A ,U=IR+U S =2×1+4=6V P I =I 2R=22×1=4W ,U S 与I 为关联参考方向,电压源功率:P U =IU S =2×4=8W ,+U 4-题1.1图ba题1.3图+u L-1/题1.2图题1.4图U 与I 为非关联参考方向,电流源功率:P I =-I S U=-2×6=-12W ,验算:P U +P I +P R =8-12+4=01.5 求题1.5图中的R 和U ab 、U ac 。

电力电子技术 仿真实验 实验一 单相桥式全控整流电路

《电力电子技术》仿真实验实验一单相桥式全控整流电路说明:1、为选修《电力电子技术》的工科本科生编写的实验指导书;2、课前安排了一节Matlab、Simulink入门课,让同学们仿真了单相桥式不可控整流电路;3、本指导书适用于新版本Matlab。

实验一单相桥式全控整流电路一、实验目的1、掌握单相桥式全控整流电路的工作原理;2、掌握单相桥式全控整流电路的仿真方法;3、了解不同类型负载输出波形的差异。

二、实验环境及器件仿真软件:Simulink所用器件如下表1所示(以Matlab2019b版本为例)。

表1 实验器件三、实验原理(a )电阻负载(b )阻感负载图1 单相桥式全控整流电路单相桥式全控整流电路是常用的单相整流电路之一,主电路由两对桥臂构成,晶闸管VT 1和VT 4组成一对桥臂,VT 2和VT 3组成另一对桥臂。

认为输入电压u2正半周时上端电压为正。

1、电阻负载如图1(a )所示,以一个电流周期为例,在正半周时某一时刻t ,触发VT 1和VT 4可导通流过电流,若交流电周期为T ,则VT 1和VT 4在T/2时刻,电压过零变负时关断。

在T/2+t 时刻触发VT 2和VT 3可以导通,VT 2和VT 3在T 时刻电压过零变正时关断。

整流电压的平均值为:2211cos sin d()0.92d U t t U πααωωπ+==⎰ 其中α为时刻t 对应的电角度,U 2为输入交流电的电压幅值,α的变化范围为0~180°。

2、电感电阻负载如图1(b )所示,VT 1和VT 4导通后,电压过零变负时,由于电感的作用,仍有电流流过VT 1和VT 4,VT 1和VT 4不会关断,直到在T/2+t 时刻触发VT 2和VT 3导通,反向电压使VT 1和VT 4关断。

同理,VT 2和VT 3导通后,电压过零变正时不会关断,直到VT 1和VT 4导通时承受反向电压关断。

整流电压的平均值为:d 221sin d()0.9cos U t t U παωωαπ+==⎰其中α为时刻t 对应的电角度,U 2为输入交流电的电压幅值,L 极大时,α的变化范围为0~90°。

《电力电子技术 第3版 》读书笔记思维导图

1.9 典型电力电 子器件的测试实 验

1.10 习题

第2章 交流-直流变换电路及 其仿真

2.1 晶闸管单相 可控整流电路

2.2 三相半波可 控整流电路

2.3 三相桥式全 控整流电路

2.4 三相桥式半 控整流电路

2.5 变压器漏抗 对整流电路的影

响

2.6 晶闸管相控 电路的驱动控制

2.7 交流-直流变 换电路的仿真

力电子变流电路。为强化高等职业教育的实践技能培养,《电力电子技术第3版》介绍了基于MATLAB的图形化仿 真实验内容。基本的教学内容均配有仿真实验实例另外还安排了课程设计等实践内容《电力电子技术第3版》内容 叙述详细,便于自学仿真实验指导循序渐进,便于初学者掌握。《电力电子技术第3版》的特色是提供了与理论分 析波形相对应的仿真实验波形和实物实验波形,有利于加强学生的感性认识。内容深入浅出、简明扼要、实用性 较强。和第2版相比,第3 数量的仿真实验内容。《电力电子技术第3版》适用的读者对象是电类相关专业的高职高专院校的学生,同时也可 供从事电力电子技术工作的工程技术人员参考。

6.2 课程设计任 务书

6.1 课程设计大 纲

6.3 晶闸管整流 器的工程设计指

导书

参考文献

读书笔记

谢谢观看

01

1.1 功 率二极管

02

1.2 晶 闸管

03

1.3 门 极可关断 晶闸管 (GTO)

04

1.4 电 力晶体管 (GTR)

06

1.6 绝 缘栅双极 型晶体管 (IGBT)

05

1.5 功 率场效应 晶体管 (PMOSFE...

1.7 其他新型电 力电子器件

1.8 典型电力电 子器件的MATLAB

电力电子技术仿真实验报告

电力电子技术仿真实验实验一三相桥式全控整流电路一:实验目的(1)加深理解三相桥式全控整流电路的工作原理(2)了解KC系列集成触发器的调整方法和各点的波形(3)掌握三相桥式全控整流电路MATLAB的仿真方法,会设置各模块的参数二:实验原理完整的三相桥式全控整流电路由整流变压器,6个桥式连接的晶闸管,负载,触发器和同步环节组成,6个晶闸管依次相隔60度触发,将电源交流电整流为直流电。

三:三相桥式全控整流电路仿真模型a.纯电阻负载电路1.设置仿真参数交流电压源的参数设置三相电源的相位互差120度,交流峰值相电压为100*sqrt(2)V,频率为60Hz 负载的参数设置R=45Ω,L=0H移相控制角值"alpha_deg"分别设为设为30,60, 120度2.仿真波形a: alpha_deg=30纯电阻负载两端的电压Vd1,Vd2晶闸管VT1的电压Uvt1每一相的相电流(iA,iB,iC)完整的波形注:iD为整流后的电流波形,Vd为整流后的电压波形b: alpha_deg=60纯电阻负载两端的电压Vd1,Vd2晶闸管VT1的电压Uvt1每一相的相电流(iA,iB,iC)完整波形c: alpha_deg=120纯电阻负载两端的电压Vd1,Vd2 晶闸管VT1的电压Uvt1每一相的相电流(iA,iB,iC)完整波形b.阻感负载电路1.设置仿真参数交流电压源的参数设置三相电源的相位互差120度,交流峰值相电压为100*sqrt(2)V,频率为60Hz 负载的参数设置R=45Ω,L=1H移相控制角值"alpha_deg"分别设为设为30,60, 90度2.仿真波形a: alpha_deg=30阻感负载两端的电压Vd1,Vd2晶闸管VT1的电压Uvt1每一相的相电流(iA,iB,iC)完整波形b: alpha_deg=60阻感负载两端的电压Vd1,Vd2 晶闸管VT1的电压Uvt1每一相的相电流完整波形c: alpha_deg=90阻感负载两端的电压Vd1,Vd2 晶闸管Vt1的电压Uvt1每一相的相电流完整波形四.功率因数的测定a.测量原理b.仿真模型c.仿真数据(1)感性负载alpha=0 alpha=30alpha=60 alpha=90 (2) 纯电阻负载alpha=0 alpha=30 alpha=90 alpha=60实验二单相正弦波脉宽调制逆变电路实验一.实验目的(1)了解电压型单相全桥逆变电路的工作原理(2)了解正弦波脉宽调制调频,调压的原理(3)研究单相全桥逆变电路控制触发的要求二.实验原理1.正弦波脉宽调制(SPWM)控制的基本原理(1)SPWM的概念工程实际中应用最多的是正弦PwM法(简称sPwM),它是在每半个周期内输出若干个宽窄不同的矩形脉冲波,每一矩形波的面积近似对应正弦波各相应每一等份的正弦波形下的面积可用一个与该面积相等的矩形来代替,于是正弦波形所包围的面积可用这N个等幅(Vd)不等宽的矩形脉冲面积之和来等效。

大学科目电力电子技术四组仿真实验

仿真实验1直流降压斩波电路1 .实验目的完成如下降压斩波电路的计算,然后通过仿真实验检验设计结果,并在此基 础上,研究降压斩波电路的工作特点。

设计题图Ll 所示的BUCk 变换器。

电源电压Vs=220V,额定负载电流11A, 最小负载电流1∙1A,开关频率20KHz 。

要求输出电压Vo=II0V ;要求最小负载 时电感电流不断流,且输出电压纹波小于1%。

计算输出滤波电感L 和电容C 的 最小取值。

(与第3章习题(1)中计算题2相同)图1.12 .实验步骤1)打开文件“EXPl_buck.mdl”,自动进入SimUlink 仿真界面,在编辑器窗口中 显示如图1.2所示的降压斩波电路的模型。

Buck DC DC Chopper图1.2降压斩波电路的模型2)根据上述题目中给出的电路参数及计算得出的滤波电感L 和电容C 的值配置 图1.2电路模型中各元件的参数:电源:U=220V脉冲发生器(PUlSe ):周期(period,s ) =50e-6 ;占空比(dutycycle,%) =50 电感 L:电感量(inductance,H ) = 1.25e-3L Z o=Ll-IlA : --------- F o =IlOVU - 220 VΛTI 147~220VFWDiode w≡pulse≡l scope电容C:电容量(capacitance,F) =1.25e-5电阻R:电阻值(resistance,ohms) =10记录此条件下的波形,在波形图上估算此时输出电压的纹波系数。

更改电阻参数,使负载电流为1.1A,记录此时的波形,并说明电感电流的特点。

在实验基础上,说明电感L和电容C取值的正确性。

3)观察占空比变化对输出电压的影响。

将电阻值恢复为10。

更改脉冲发生器中的周期参数,在占空比为20%, 40%, 60%, 80%时,观察波形,估计输出电压的值,并计算在不同占空比下的输出\ 输入电压比,说明占空比与变压比的关系。

电力电子学_第三版_第01章

第1章 电力电子变换和控制技术导论

5

3. 控制技术

• 模拟(连续)控制技术。 • 数字(离散)控制技术。 • 理论与技术的进步,促使数字控制技

术越来越多取代模拟控制技术。例: 变频器控制技术的发展史。 • 自动控制理论(含经典和现代)、现 代电机控制理论等等,是促进电力电 子技术不断发展的源泉之一。

对图(a)示开关电路中的四个开关器件进行实时、适式的高

频通、断控制,可以由变换器的输出端得到所需要的、任意波形的

周期性或非周期电压或电流。将此变换器的输出电压串接在电力线 路上即可补偿和调控电网线路电压,改变线路电流;将此变换器输 出的电流并联接入电网,即可补偿负载电流或控制电网电流。从而

调控系统有功和(或)无功功率。

串联、并联补偿器都能显著地改善电力系统的运行特性和运行 经济性。

第1章 电力电子变换和控制技术导论

32

阻抗补偿控制器

将图(b)所示的电感、电容或电阻经一个可控的开关器件S 并联接入或串联接入交流电网就构成了一个阻抗补偿控制器。对 开关器件进行实时、适式的通、断控制,就可以改变电网的等效 负载阻抗或等效线路阻抗,从而补偿控制电网、负载的电压、电 流、功率。

第1章 力电子变换和控制技术导论

26

开关型电力电子变换器的应用领域

开关型电力电子变换电源 开关型电力电子补偿控制器

第1章 电力电子变换和控制技术导论

27

开关型电力电子变换电源

电力系统中的直流远距离输电 直流电动机变速传动控制 交流电动机变速传动控制 变速恒频发电系统 电解、电镀等应用领域中的低压大电流可

控直流电源。 各 类 高 性 能 的 不 间 断 供 电 电 源 (UPS ,

电力电子技术课程设计——三相桥式全控整流电路的设计与仿真

电力电子技术课程设计——三相桥式全控整流电路的设计与仿真————————————————————————————————作者:————————————————————————————————日期:第一章绪言1.1设计背景目前,各类电力电子变换器的输入整流电路输入功率级一般采用不可控整流或相控整流电路。

这类整流电路结构简单,控制技术成熟,但交流侧输入功率因数低,并向电网注入大量的谐波电流。

据估计,在发达国家有60%的电能经过变换后才使用,而这个数字在本世纪初达到95%。

电力电子技术在电力系统中有着非常广泛的应用。

据估计,发达国家在用户最终使用的电能中,有60%以上的电能至少经过一次以上电力电子变流装置的处理.电力系统在通向现代化的进程中,电力电子技术是关键技术之一.可以毫不夸张地说,如果离开电力电子技术,电力系统的现代化就是不可想象的。

而电能的传输中,直流输电在长距离、大容量输电时有很大的优势,其送电端的整流阀和受电端的逆变阀都采用晶闸管变各种电子装置一般都需要不同电压等级的直流电源供电.通信设备中的程控交换机所用的直流电源以前用晶闸管整流电源,现在已改为采用全控型器件的高频开关电源。

大型计算机所需的工作电源、微型计算机内部的电源现在也都采用高频开关电源。

在各种电子装置中,以前大量采用线性稳压电源供电,由于高频开关电源体积小、重量轻、效率高,现在已逐渐取代了线性电源.因为各种信息技术装置都需要电力电子装置提供电源,所以可以说信息电子技术离不开电力电子技术。

近年发展起来的柔性交流输电(FACTS)也是依靠电力电子装置才得以实现的。

随着社会生产和科学技术的发展,整流电路在自动控制系统、测量系统和发电机励磁系统等领域的应用日益广泛。

常用的三相整流电路有三相桥式不可控整流电路、三相桥式半控整流电路和三相桥式全控整流电路,由于整流电路涉及到交流信号、直流信号以及触发信号,同时包含晶闸管、电容、电感、电阻等多种元件,采用常规电路分析方法显得相当繁琐,高压情况下实验也难顺利进行.Matlab提供的可视化仿真工具Simulink可直接建立电路仿真模型,随意改变仿真参数,并且立即可得到任意的仿真结果,直观性强,进一步省去了编程的步骤。

Proteus教程—电子线路设计、制版与仿真(第3版)第1章 Proteus快速入门

第1章 Proteus快速入门

2. 编辑窗口视野控制

学会合理控制编辑区的视野是元件编辑和电路连接进行前的首要工作。 编辑窗口的视野平移可用以下方法: 在原理图编辑区的蓝色方框内,把鼠标指针放置在一个地方后,按下“F5” 键,则以鼠标指针为中心显示图形。

当图形不能全部显示出来时,按住“Shift”键,移动鼠标指针到上、下、 左、右边界,则图形自动平移。

在弹出的对话框中选择“No”,选中“以后不再显示此对话框”复选框, 关闭弹出提示。

第1章 Proteus快速入门

本例所用到的元件清单如表1-1所示。

元件名 CAPACITOR

RES LAMP

SW-SPDT

BATTERY

表1-1 元 件 清 单

类 Capacitors

Resistors Optoelectronics

12V

第1章 Proteus快速入门

单击界面左侧预览窗口下面的“P”按钮,如图1-14所示,弹出“Pick Devices”(元件拾取)对话框,如图1-15所示。

ISIS 7 Professional的元件拾取就是把元件从元件拾取对话框中拾取到图 形编辑界面的对象选择器中。元件拾取共有两种办法。

第1章 Proteus快速入门

第1章 Proteus快速入门

Proteus 激励源的可编辑格式示例如图所示:

第1章 Proteus快速入门

2. 仿真工具—— 虚拟仪器 虚拟示波器(OSCILLOSCOPE)。 逻辑分析仪(LOGIC ANALYSER)。 计数器、定时器(COUNTER TIMER)。 虚拟终端(VIRUAL TERMINAL)。 信号发生器(SIGNAL GENERATOR)。 模式发生器(PATTERN GENERATOR)。 交直流电压表和电流表(AC/DC voltmeters/ammeters)。 SPI调试器(SPI DEBUGGER)。 I2C调试器(I2C DEBUGGER)。

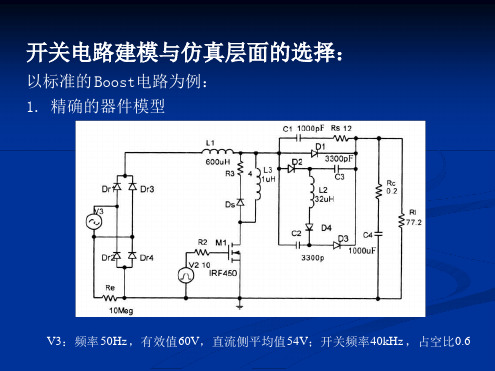

现代电力电子技术仿真4

300V

200V

100V

0V

-100V 0s V(D2:1)

10ms V(C1:2)

200V

20ms

30ms

40ms

50ms Time

60ms

70ms

80ms

90ms

100ms

100V

0V

-100V

99.90ms

99.91ms

V(D2:1) V(C1:2)

99.92ms

99.93ms

99.94ms

生 产样 机

子 电 路 模 型

系99.96ms

99.97ms

99.98ms

99.99ms 100.00ms

仿真时间: 5个周期680s

3. 忽略吸收电路的简化模型

200V

100V

0V

-100V 0s V(M1:d)

10ms V(C1:2)

150V

20ms

30ms

40ms

50ms Time

60ms

70ms

包 含吸 收 电路

比较

仿 真波 形

开环电路频域测试:输入输出 比较 开环电路频域仿真:输入输出

波形 、 阻抗 、 传递 函 数

波 形、 阻 抗、 传 递函 数

控 制 器设 计

闭环电路时域频域测试:输入 比较 闭环电路时域频域仿真:输入

输 出波 形 、阻 抗 、传 递 函数

输 出 波形 、 阻抗 、 传递 函 数

50V

0V

-50V

0s

150V

V(D1:1)

10ms V(D1:2)

20ms

30ms

40ms

50ms Time

60ms

电力电子仿真实验

《电力电子技术》仿真实验报告姓名: 学号:班级:专业: 电气工程及其自动化成绩:任课教师:实验一单相桥式全控整流仿真实验一.实验目的1.通过Matlab软件对单相桥式整流电路中阻性负载电路在不同的触发角情况下的工作特性进行分析。

2.掌握单相桥式全控整流电路原理以及阻性负载的工作特性;能够对仿真结果进行电路分析。

二.实验设备1.计算机一台;2.MATLAB软件三.实验内容1.单相桥式整流电路基本原理(1)晶闸管VT1和VT4组成一对桥臂,在u2正半周期承受电压u2,得到触发脉冲导通,当u2过零时关断;(2)VT2和VT3组成另一对桥臂,在u2正半周期承受电压-u2,得到触发脉冲导通,当u2过零点时关断。

2.仿真模型介绍模型参数设置交流电源参数脉冲信号发生器参数Pulse Generator的参数Pulse Generator1的参数示波器参数示波器五个通道信号依次是:通道晶闸管电流I a,晶闸管电压U a,电源电流i2,通过负载电流I d,负载两端的电压U d;电阻R=1Ω。

3.仿真波形分析触发角α=0。

时仿真波形触发角α=30。

时仿真波形触发角α=60。

时仿真波形触发角α=90。

时仿真波形在电源电压正半波(0~π)区间,晶闸管承受正向电压,脉冲UG在ωt=α处触发晶闸管VT1和VT4,晶闸管VT1和VT4开始导通,形成负载电流i d负载上有输出电压和电流。

在ωt=π时刻,U2=0,电源电压自然过零,晶闸管电流小于维持电流而关断,负载电流为零。

在电源电压负半波(π~2π)区间,晶闸管TV1和VT4承受反向电压而处于关断状态,晶闸管VT2和VT3承受正向电压,脉冲UG在ωt=α处触发,晶闸管VT2,VT3开始导通,形成负载电流i d,负载上有输出电压和电流。

四.思考题(思考题,可根据思考程度,自行添加。

红字部分,自行删除)1.增大触发角,对输出电压平均值有什么影响?Ud=0.9U2((1+cosα)/2)当α=0时,Ud=0.9U2当α=180时,Ud=0所以触发角越大,输出平均电压越小。

杨素行 第三版 模拟电子技术基础简明教程课件 第一章

1.1 半导体的特性 1.2 半导体二极管 1.3 双极型三极管(BJT) 1.4 场效应三极管

第一章 半导体器件

1.1 半导体的特性

1. 导体:电阻率 < 10-4 ·cm 的物质。如铜、

银、铝等金属材料。

2. 绝缘体:电阻率 > 109 ·cm 物质。如橡胶、

塑料等。

3. 半导体:导电性能介于导体和半导体之间的物 质。大多数半导体器件所用的主要材料是硅(Si)和锗 (Ge)。

在常温(300 K)下,

UT 26 mV

二极管加反向电压,即 U < 0,且 |U| >> UT ,则 I - IS。

二极管加正向电压,即 U > 0,且 U >> UT ,则

U

U

e UT 1 ,可得 I ISe UT ,说明电流 I 与电压 U

基本上成指数关系。

第一章 半导体器件

结论:

二极管具有单向导电性。加正向电压时导通,呈现 很小的正向电阻,如同开关闭合;加反向电压时截止, 呈现很大的反向电阻,如同开关断开。

空间电荷区正负离子之间电位差 UD —— 电位壁垒; —— 内电场;内电场阻止多子的扩散 —— 阻挡层。

4. 漂移运动 内电场有利 于少子运动—漂 移。

少子的运动 与多子运动方向 相反

图 1.2.1(b)

阻挡层

P

空间电荷区

N

内电场 UD

第一章 半导体器件 5. 扩散与漂移的动态平衡 扩散运动使空间电荷区增大,扩散电流逐渐减小; 随着内电场的增强,漂移运动逐渐增加; 当扩散电流与漂移电流相等时,PN 结总的电流 等于零,空间电荷区的宽度达到稳定。即扩散运动与 漂移运动达到动态平衡。

电力电子技术仿真作业1

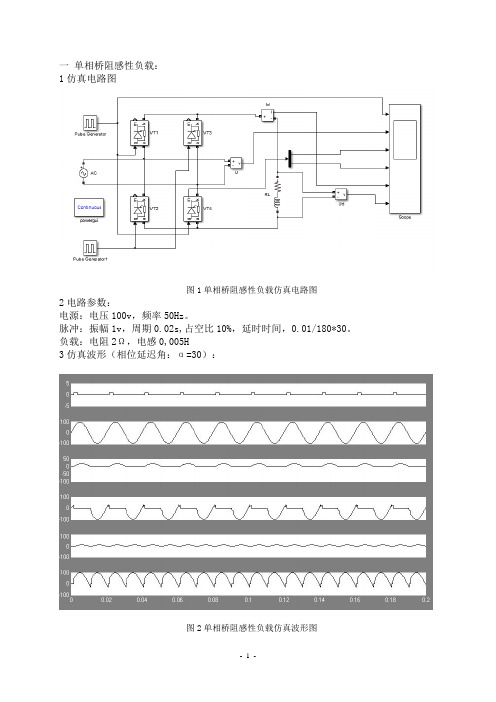

一单相桥阻感性负载:

1仿真电路图

图1单相桥阻感性负载仿真电路图

2电路参数:

电源:电压100v,频率50Hz。

脉冲:振幅1v,周期0.02s,占空比10%,延时时间,0.01/180*30。

负载:电阻2Ω,电感0,005H

3仿真波形(相位延迟角:α=30):

图2单相桥阻感性负载仿真波形图

1仿真电路图:

图3 三相半波可控整流阻感性负载仿真电路图

2电路参数:

电源:电压100v,频率50Hz,相位:A 30°B -90°C -210°。

脉冲:振幅1v,周期0.02s,占空比10%,延时时间A0.01/180*30 B0.01/180*150 C0.01/180*270。

负载:电阻2Ω,电感0,005H.

3仿真波形(相位延迟角:α=30°):

图4 三相半波可控整流阻感性负载仿真电波形图

1仿真电路图:

图5三相桥式全控整流电路电阻负载仿真电路图2电路参数:

电源:电压100v,频率50Hz。

脉冲:振幅1v,周期0.02s,占空比20%。

负载:电阻2Ω。

3仿真波形(相位延迟角:α=30°):

图6三相桥式全控整流电路电阻负载仿真电路图。

电力电子技术 第3版课件第4章

(2)交流调功电路或无触点开关电路对交流电源实现 通断控制,电路结构与相控交流调压类似。区别在于 调功电路仅在交流电过零时刻开关。在接通期间,负 载上承受的电压与流过的电流均是正弦波,仅仅表现 为负载通断。

交流调压和交流调功技术统称为交流开关控制技术 或交流电力控制技术。 (3)交-交变频电路也称直接变频电路(或周波变流 器),它不通过中间直流环节把电网频率的交流电直 接变换成不同频率的交流电的变换电路,包括相控式 交-交变频和矩阵式交-交变频。

4.2、交流调压电路

交流调压就是把固定幅值、频率的交流电变成幅值 可调的交流电。 (1)自耦变压器调压:输入输出电压波形如图4-1(a) 所示。 (2)相控式交流调压:用两只反并联晶闸管实现可 控双向开关,通过改变触发脉冲相位来调节输出电压, 如图4-1(b) 。 (3)斩控式交流调压:用全控型器件实现可控双向 开关,在图中阴影部分的时间内关断开关,在其他时 间内接通开关,如图4-1(c) 。

u

uu

uv

uw

(a) 0

t1 t 2 π

2π

t

ug (b)

61 2345

0

VT1 VT2 (c) VT3 VT4 VT5 VT6

(d)

VT1 VT2

VT3

VT4

VT5

VT6

(e)uRU

t

uu

0

u RU

t

u

uu

uv

(a) 0 图43 /-π9 π

uw 2π

ug 6 1 2 3 4 5 6 (b)

0

VT1 VT2 (c) VT3 VT4 VT5 VT6

ቤተ መጻሕፍቲ ባይዱ

u

uu

uv

uw

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CovSaveSingleToWorkspaceVar on

CovCumulativeVarName "covCumulativeData"

CovCumulativeReport off

CovReportOnPause on

AbsTol "auto"

FixedStep "auto"

InitialStep "auto"

MaxNumMinSteps "-1"

MaxOrder 5

ZcThreshold "auto"

ConsecutiveZCsStepRelTol "10*128*eps"

IgnoreBidirectionalLines off

ShowStorageClass off

ShowTestPointIcons on

ShowSignalResolutionIcons on

ShowViewerIcons on

SortedOrder off

TryForcingSFcnDF off

RecordCoverage off

CovPath "/"

CovSaveName "covdata"

CovMetricSettings "dw"

CovNameIncrementing off

CovHtmlReporting on

SaveTime on

StateSaveName "xout"

TimeSaveName "tout"

OutputSaveName "yout"

SignalLoggingName "logsout"

OutputOption "RefineOutputTimes"

PropName "DisabledProps"

}

Version "1.4.0"

BlockReduction on

BooleanDataType on

ConditionallyExecuteInputs on

InlineParams off

SampleTimeColors off

LibraryLinkDisplay "none"

WideLines off

ShowLineDimensions off

ShowPortDataTypes off

ShowLoopsOnError on

ExecutionContextIcon off

ShowLinearizationAnnotations on

ScopeRefreshTime 0.035000

OverrideScopeRefreshTime on

DisableAllScopes off

DataTypeOverride "UseLocalSettings"

ComputedModelVersion "1.29"

NumModelReferences 0

NumTestPointedSignals 0

}

SavedCharacterEncoding "GBK"

SaveDefaultBlockParams on

Model {

Name "Dx_sbb_dzfz"

Version 7.1

MdlSubVersion 0

GraphicalInterface {

NumRootInports 0

NumRootOutports 0

ParameterArgumentNames ""

MinMaxOverflowLogging "UseLocalSettings"

MinMaxOverflowArchiveMode "Overwrite"

BlockNameDataTip off

BlockParametersDataTip off

BlockDescriptionStringDataTip off

OutputTimes "[]"

Refine "1"

}

Simulink.OptimizationCC {

$ObjectID 4

Array {

Type "Cell"

Dimension 5

Cell "ZeroExternalMemoryAtStartup"

ZeroCrossAlgorithm "Non-adaptive"

AlgebraicLoopSolver "TrustRegion"

SolverResetMethod "Fast"

PositivePriorityOrder off

AutoInsertRateTranBlk off

Profile off

ParamWorkspaceSource "MATLABWorkspace"

AccelSystemTargetFile "accel.tlc"

AccelTemplateMakefile "accel_default_tmf"

AccelMakeCommand "make_rtw"

LoadInitialState off

SaveFinalState off

SaveFormat "Array"

SaveOutput on

SaveState off

SignalLogging on

InspectSignalLogs off

UpdateHistory "UpdateHistoryNever"

ModifiedByFormat "%<Auto>"

LastModifiedBy "Administrator"

ModifiedDateFormat "%<Auto>"

LastModifiedDate "Wed Sep 30 11:42:04 2015"

CovModelRefEnable "Off"

ExtModeBatchMode off

ExtModeEnableFloating on

ExtModeTrigType "manual"

ExtModeTrigMode "normal"

ExtModeTrigPort "1"

MaxConsecutiveZCs "1000"

ExtrapolationOrder 4

NumberNewtonIterations 1

MaxStep "auto"

MinStep "auto"

MaxConsecutiveMinStep "1"

RelTol "1e-3"

SolverMode "Auto"

Solver "ode23tb"

SolverName "ode23tb"

ShapePreserveControl "DisableAll"

ZeroCrossControl "UseLocalSettings"

ExternalInput "[t, u]"

FinalStateName "xFinal"

InitialState "xInitial"

LimitDataPoints on

MaxDataPoints "1000"

LoadExternalInput off

SampleTimeConstraint "Unconstrained"

InsertRTBMode "Whenemulink.DataIOCC {

$ObjectID 3

Version "1.4.0"

Decimation "1"

ToolBar on

StatusBar on

BrowserShowLibraryLinks off

BrowserLookUnderMasks off

Created "Fri Apr 12 14:43:23 2013"

Creator "Administrator"

ExtModeTrigLevel 0

ExtModeArchiveMode "off"

ExtModeAutoIncOneShot off

ExtModeIncDirWhenArm off

ExtModeAddSuffixToVar off

ExtModeWriteAllDataToWs off

ExtModeTrigElement "any"

ExtModeTrigDuration 1000