相位测量仪设计

低频数字式相位测量仪

低频数字式相位测量仪(C题)一、任务设计并制作一个低频相位测量系统,包括相位测量仪、数字式移相信号发生器和移相网络三部份,示用意如下:二、要求1、大体要求(1)设计并制作一个相位测量仪(参见图1)a.频率范围:20Hz~20kHz。

b.相位测量仪的输入阻抗≥100k。

c.许诺两路输入正弦信号峰-峰值可别离在1V~5V范围内转变。

d.相位测量绝对误差≤2°。

e.具有频率测量及数字显示功能。

f.相位差数字显示:相位读数为0o~,分辨力为°。

(2)参考图2制作一个移相网络a.输入信号频率:100Hz、1kHz、10kHz。

b.持续相移范围:-45°~+45°。

c.A'、B'输出的正弦信号峰-峰值可别离在~5V范围内转变。

2.发挥部份(1)设计并制作一个数字式移相信号发生器(图3),用以产生相位测量仪所需的输入正弦信号,要求:a.频率范围:20Hz~20kHz,频率步进为20Hz,输出频率可预置。

b.A、B输出的正弦信号峰-峰值可别离在~5V范围内转变。

c.相位差范围为0~359°,相位差步进为1°,相位差值可预置。

d.数字显示预置的频率、相位差值。

(2)在维持相位测量仪测量误差和频率范围不变的条件下,扩展相位测量仪输入正弦电压峰-峰值至~5V范围。

(3)用数字移相信号发生器校验相位测量仪,自选几个频点、相位差值和不同幅度进行校验。

(4)其它。

三、评分标准四、说明1、移相网络的器件和元件参数自行选择,也能够自行设计不同于图2的移相网络。

2、大体要求(2)项中,当输入信号频率不同时,许诺切换移相网络中的元件。

3、相位测量仪和数字移相信号发生器相互独立,不许诺共用操纵与显示电路。

相位测量仪报告

相位测量仪摘要:本设计以单片机和可编程逻辑器件FPGA为控制核心,实现数字信号的产生、逻辑信号的采集和示波器的显示。

系统主要由三个模块组成:信号发生,数据采集与波形显示。

本设计经过单片机产生逻辑信号,利用FPGA作为数据处理器和DAC控制器,能准确、清晰的在模拟示波器上显示出逻辑波形、触发标记、光标。

利用键盘输入和液晶显示,能实现逻辑预设和触发模式设置。

经验证,本方案完成了全部基本功能和扩展功能。

关键词:逻辑分析仪可编程逻辑器件单片机Abstract:The design of the microcontroller and FPGA programmable logic devices for the control of the core, digital signal generation, logic signal acquisition and oscilloscope display. System consists of three modules: signal, data acquisition and waveform display. After the microcontroller generates the logic signal design , as a data processor using FPGA and DAC controllers , accurate, clearly shows the logic waveforms. The use of keyboard and LCD display , and to achieve pre-trigger mode logic. Proven, the program completed all the basic features and extensions. Keywords:logical link control Programmable logic devices MCU一、方案设计与论证1、数字式移相信号发生器方案一:采用FPGA实现DDS直接频率合成技术。

相位式激光测距仪激光接收部分设计

相位式激光测距仪激光接收部分设计激光测距仪是一种测量目标物体距离的工具,其原理是利用激光束在空气中传播的特性,通过测量激光束的往返时间来计算出目标物体与测距仪的距离。

激光接收部分是激光测距仪的核心组成部分之一,其设计的好坏直接影响到测量结果的准确性和稳定性。

在设计激光接收部分时,需要考虑以下几个关键因素:1.激光接收器的选择:激光接收器是接收激光信号的关键部件,其性能直接影响到激光测距仪的灵敏度和测距范围。

常见的激光接收器有光电二极管(PD)和光电效应晶体管(APD)。

PD具有较高的响应速度和较低的噪声,适用于近距离测距场景;APD具有较高的增益和较低的噪声,适用于远距离测距场景。

2.光学系统的设计:光学系统包括透镜、滤波器等光学元件,其作用是将入射的激光束聚焦到激光接收器上。

在设计光学系统时需要考虑激光束的聚焦效果、散斑噪声等因素,以提高测距仪的测量精度和信噪比。

3.信号放大和滤波电路的设计:激光接收器输出的信号很弱,需要经过放大和滤波才能得到可信的测距信号。

放大电路可以采用运算放大器等电路实现,滤波电路可以采用RC滤波器或数字滤波器等实现。

通过合理设计放大和滤波电路,可以提高信号的噪声抑制和动态范围。

4.时间测量电路的设计:激光测距仪是通过测量激光束的往返时间来计算距离的,因此需要设计一个高精度的时间测量电路。

常用的时间测量电路有计数器、时钟等,可以通过采样和比较测量激光脉冲信号的上升沿和下降沿来计算出往返时间。

在设计激光接收部分时,还需考虑以下一些技术细节:5.温度补偿:激光测距仪的测量精度受到温度的影响,尤其是光学元件和电子元件的温度变化。

因此,需要设计温度补偿电路,通过测量环境温度并补偿光学和电子元件的参考值,提高测量精度。

6.光路对齐:激光测距仪的激光发射和接收部分需要在一条直线上对准,才能确保测量结果的准确性。

因此,需要设计一个精密的光路对齐机构,确保激光束的传输方向稳定。

7.防干扰设计:激光测距仪易受到外界光源干扰,导致测量结果偏差。

单片机频率相位测量仪的设计

发器清 零 ,否则 得 到 的 异 或 值 不 同 ,如 图 3所 示 ,a,b 经

页 )所示 .

CL P D电路描述 :首 先经 过 扫描 P ¨控 制 72 7 ( 45 2选 1 电路 ,选择 测 频还 是 测相 .如果 为 高 电平则 )

收稿 日期 :2) 一 O— 1 【6 8 O ( ) 作 者 简介 :韩 峰 (9 9 ,男 ,黑 龙 江 林 甸 县 人 ,副 教授 , 主要 从 事 电气 工 程 方 面 教 学 研 究 1 6 一)

维普资讯

第 8 年 3 期 2 0 第 9月 卷 0 6

— —

辽 宁 师 专 学 报

o r lo a ni a hes Cole e J u na fLio ng Te c r lg

V 18 No 3 o . . S p e .200 6

1 系统工作 原理

本设计 以 8C 2单 片机 和可 编程 逻辑器 件 ( P D)为 核心 ,构 成 低 频 信号 频 率 相 位测 量仪 .该仪 器 95 CL

具有移 相 、频 率 和 相 位 测 量 两 大 功 能 .移 相 电 路 由移 相 网 络 和 信 号 放 大 电路 组 成 ,对 固定 频 率 信 号 ( 0 ,1k ,1 Hz 1 0Hz Hz 0 k )可满 足 一 5 5的 相移 要 求 ;频 率 、相 位 测 量 电路 由 阻抗 变换 电路 、整形 电 4 ~4

图1系统 设 计总图

图3测nI 流程

搭成 的 2 4位计 数器 ,经 锁存器

锁存 ,等 待 单 片 机 读 出 ;如果 为低 电平 则 测 相 .测 相 时先 调 用了 测 频 的 程 序 但 并 不 显 示 , 而是存 起 来待 用 ,然 后 给 D触

CPLD低频数字相位测量仪的设计

包括数字移相信 号发生 器和相位 测量仪 2 部分 , 分别 完成移相信号的发生 、 频率 与相位差 的预置、 数字显示、 号的移相 以 信

及移相后信 号相位差和频率 的测量 与相识 等功能。 中数字 式移 相信号发生 器可 以产 生预置频率 的差值 ; 其 相位 测量仪可

以测量和显 示相位信 号的频率 、 位 差。 相

厂一

后, 将波形整形电路的2 0 ] 厂 厂 厂 厂 ] ]

图 1 波形变换 示意 图

的功能, 用以产生相位测量仪所需的输入正弦信号 。 其

技术 要 求 指标 : 率 范 围2 Hz~ 0 Hz 频 率 步进 为 频 0 2k ,

2H , 0 z 输出频率可预置; 相位差范围为0 3 9 , ~ 5 。相位差

( 具有设定保存功能。 5)

实现相位 、 频率的测量, 并且具有独 自的控制功能和数

字显示 功能。

11系统硬件 结构 .

首 先 将 被 测 2列 正

弦 信号 A 、 B经平 滑 滤 波

后 , 入 过 零 比较 电路 , 输

A

1系统硬件设计

总体要求 : ( ) 有相 位 测量 功 能 , 1具 即相 位 测量 仪 的 功 能 。 其

传 感 及 检 测 仪 表

C L 低频 数 字 相 位 测 量 仪 的设 计 PD

朱 红梅 , 美 君 潘

( 海西部矿 业铅业 摘

要: 绍 了一种基 于复杂的可编程逻辑 器件( L 和 高速 单片机s c8 c 8 介 CP D) T 9 5 的低频数字 相位 测量仪 。 该测量仪

京航 天航 空 大 学 出版 社 【] 白英 彩 . 型 计 算 机 常 用 芯 片 手 册 【 . 海 : 海科 学 3 微 M】 上 上

应用8051单片机IP设计相位测量仪

r eso n rc es .

K y e W o d : r q e c P a e r s F e u n y h s Me u e n S s e l OP 80 I I Co e s a r me t y t m S C; 5 P r

2 当待 测 脉 冲 由 高 电平 外接。 P 用F GA实 现 时 , 使 用 F GA片 内 动 3 位 计 数 器 计 数 , 可 P R0M 、 RAM资源 实现 。 变 为 低 电平 时 ( 由低 电 平 变 为 高 电平 ) 或 , 子技 术 、 业 自动 化 、 能 控 制 及 通 信 等 众 工 智 2 停 多 领域 。 因此 , 计一 个 高 精 度 的 相 位 差 测 设 ( ) 出 与输 入 (/ 口是 分 开 的 。 果 置 3 位 计 数 器 使 能 信 号 EN低 电 平 , 止 3输 I O) 如 2 并 必 量仪显得十 分重要。 当前 国 内 的 一 般 的 解 需 要 使 用 双 向 口功 能 , 须 外 接 一 些 电路 3 位 计 数 器 计 数 , 置 测 量 周期 结 束 信 号

S R为 高 电 平 , 到单 片机 读 取 脉 宽 计 数 T 直 值 然 后 复位 ( C R为 高 电平 ) 开 始 新 的 置 L ,

应用8051单片机IP设计相位测量仪

应用8051单片机IP设计相位测量仪摘要:本设计应用SOPC和8051单片机IP技术,设计一个高精度的相位差测量仪。

通过在FPGA中嵌入8051单片机IP来取代单片机+FPGA方案中的实际的单片机,既节省了成本又充分利用FPGA内部资源。

关键词:相位测量仪SOPC 8051单片机IPAbstract:The design of Frequency Phase Measurement System is presented based on 8051 IP Core and FPGA.8051 IP Core,which embed in the FPGA,to replace the extra 8051 of the existing MCU+FPGA solution,saving the cost and make full use of FPGA internal resources.Key Words:Frequency Phase Measurement System;SOPC;8051 IP Core相位差测量技术发展至今已深入到电子技术、工业自动化、智能控制及通信等众多领域。

因此,设计一个高精度的相位差测量仪显得十分重要。

当前国内的一般的解决方案是单片机+FPGA方案,其中FPGA完成高速的脉冲计数功能,而单片机则进行脉冲计数后的有关计算和LCD显示等的控制。

此方案中的FPGA内部资源往往利用不足,造成比较大的浪费。

本设计应用SOPC和8051单片机IP技术,通过在FPGA中嵌入8051单片机IP来取代单片机+FPGA方案中的实际的单片机。

既少用一个实际的单片机又充分利用FPGA内部资源,大大节省了硬件的成本。

1 8051单片机IP核简介常见的8051单片机IP有开源免费的和工业级收费的两类,一般都具有以下特点。

脉宽测量模块用来测量占空比待测信号的高、低电平脉宽时间,用VHDL语言设计,由FPGA实现。

毕业设计论文《低频数字式相位测量仪》

毕业设计论文《低频数字式相位测量仪》摘要该数字式相位测量仪以单片机 (89c52) 为核心 , 通过高速计数器 CD4040 为计数器计算脉冲个数从 , 而达到计算相位的要求 , 通过 8279 驱动数码管显示正弦波的频率,不采用一般的模拟的振动器产生 , 而是采用单片机产生 , 从而实现了产生到显示的数字化 . 具有产生的频率精确 , 稳定的特点 . 相移部分采用一般的 RC 移相电路 , 节省了成本。

一方案论证与比较 :1 常见正弦信号的测量方法 :方案一:采用模拟分离元件如二极管,三极管等非线性元件,实现频率的测量,检相的功能,使用起来方便,价格便宜,但采用分离元件由于分散性太大,不便于集成及数字化,而且测量误差大。

方案二:采用集成的检相器,检频器实现频率及相位的测量。

这种方法的实现框图如下:这种方法虽然可实现比较精确的测量,但由于模拟信号易受外界的干扰,不易调节,无法实现智能化,数字化的缺点,一般在要求较低的情况下使用。

方案三:此方案采用高速信号发生器产生 20MHz 的高频信号,其主要特点是采用 CD4040 高频计数器结合单片机,利用计数脉冲实现测量相位与频率的目标。

这种方法克服了模拟电路的缺点,实现了数字化与集成化。

本设计采用了这种方法。

这种方案的组成框图:二系统总体设计按照题目要求,我们设计的相位测量系统包括三部分:正弦波产生系统(包括频率调整电路),移相电路和相位显视系统,其总体框图如下:三各部分硬件电路设计及参数计算1、正弦波产生电路•方案一:利用 8038 芯片或 MAX038 可以实现压控的函数发生器通过改变少量的外围元件,可实现正弦波,方波,三角波,并可实现频率调节,但采用模拟器件由于元件分散性太大,即使使用单片函数发生器,参数也与外部元件有关,外接的电阻,电容对参数影响很大,因而产生的频率稳定度差,精度低,抗干扰能力差,调节困难,成本也高。

而且灵活性差,不能实现智能化。

数字式相位差测量仪的设计

目录绪论 (1)1 系统设计方案 (2)1.1 设计任务的分析 (2)1.1.1 设计主要内容及基本要求 (2)1.1.2 技术指标 (2)1.2 系统方案的选择 (2)1.3 系统的总体设计方案 (3)2 系统硬件电路的设计 (4)2.1 信号整形电路的设计 (4)2.1.1 LM339 的简介 (4)2.1.2 最简单的信号整形电路的设计 (4)2.1.3 采用了施密特触发器组成的信号整形电路的设计 (5)2.2 FPGA数据采集电路 (6)2.2.1 FPGA数据采集电路的功能分析 (6)2.2.2 FPGA数据采集电路的原理 (7)2.2.3 FPGA数据采集电路中各模块确定 (7)2.3 单片机数据运算控制电路的设计 (8)2.3.1 单片机数据运算控制电路的设计 (8)2.3.2 数据显示电路的设计 (9)3 软件部分的设计 (12)3.1 FPGA数据采集电路的VHDL语言程序设计 (12)3.1.1 VHDL语言的简介 (12)3.1.2 VHDL语言程序设计 (12)3.2 单片机数据运算控制电路的程序设计 (12)3.2.1 数据处理的技巧分析 (12)3.2.2 软件设计思路 (13)4 系统的仿真与调试 (17)4.1 FPGA数据采集电路的调试 (17)4.1.1 软件调试 (17)4.1.2 程序下载 (19)4.1.3 调试中的问题 (20)4.2 单片机数据运算控制电路的软件制作与调试 (20)4.2.1 操作过程 (20)4.2.2 问题分析 (21)4.3 系统的联合调试与验证 (21)结论 (22)参考文献 (23)附录一:元器件清单 (24)附录二:程序清单 (25)致谢 (46)数字式相位差测量仪的设计摘要本设计——数字式相位差测量系统使用FPGA和单片机相结合,构成整个系统的测控主体。

FPGA主要负责采集两个同频待测正弦信号的频率和相位差所对应的时间差,而两个同频待测正弦信号经过信号整形电路变成方波后送入FPGA数据采集电路中。

低频数字相位测量仪

、设计任务和技术要求1.1设计内容设计制作一个低频数字相位测量仪,要求使用单片机和 FPGA 来共同实现,FPGA 完成测量时间差,而单片机完成数据的读取、键盘控制和显示等功能。

1.2设计要求频率范围:20Hz~20kHz 。

相位测量仪的输入阻抗:仝 允许两路输入正弦信号峰峰值可分别在 1~5V 变化。

相位测量绝对误差W 2°。

具有频率测量及数字显示功能。

相位差数字显示,分辨力为 0.1 主芯片:Altera 的 FLEX10K10。

要求扩展键盘和显示接口电路,可以进行键盘控制以及显示等功能。

二、系统设计方案2.1方案论证根据系统的设计要求,本系统可分为三大基本组成部分:1. 数据采集电路数据采集电路主要是运用 FP GA/C PLD 采集两个同频待测正弦信号的频率和相位差所对应的时间差。

2. 数据运算控制电路数据运算控制电路主要是运用单片机读取FPGA/CPLD 采集到的数据,并根据这些数据计算待测正弦信号的频率及两路同频正弦信号之间的相位差。

3. 数据显示电路数据显示电路是通过功能键切换用LCD 液晶模块显示出待测信号的频率和相位差。

4. 整形电路由于FPGA 对脉冲信号比较敏感,而被测信号是周期相同、相位不同的两路正弦波信号, 为了准确地测出两路正弦波信号的相位差及其频率,我们需要对输入波形进行整形,使正弦 波变成方波信号,并输入 FPGA 进行处理。

整个系统的总体原理框图如图1) 2) 3) 4) 5) 6)7) 8)lOOkQ 。

2.1所示。

图2.1系统原理框图2.2程序设计框图图22程序设计流程图三、硬件电路图的设计与分析3.1 FPGA数据采集电路图3.1数据采集电路FPGA数据采集电路的功能就是实现将待测正弦信号的周期、相位差变为19位的数字量。

根据系统的总体设计方案,FPGA数据采集电路的输入输出信号有:CLK ――系统工作时钟信号输入端;A,B――两路被测信号输入端;EN ――单片机发出的传送数据使能信号;RSEL ――单片机发出的传送数据类型信号;DATA[18..O] ―― FPGA到单片机的数据输出口。

低频数字式相位测量仪

低频数字式相位测量仪设计报告目录1方案设计与论证2 1.1移相网络设计方案2 1.2相位测量仪设计方案3 2系统设计3 2.1总体设计32.1.1系统框图3 2.1.2模块说明4 2.2各模块设计及参数计算4 2.2.1移相网络设计及R、C参数设定4 2.2.2相位测量仪设计52.2.3软件系统63.结论64.参考文献75.附录7系统设计图7摘要本系统以单片机为核心,辅以必要的模拟电路,构成了一个基于具有高速处理能力的低频数字式相位测量仪。

该系统由相位测量仪和移相网络组成;移相网络能够产生-45~45°相位差的两路信号;相位测量仪能够测量出具有0°~359°的两路信号的相位差,绝对误差小于2°,具有频率测量及数字显示功能。

经过实验测试,以上功能均可以准确实现。

关键字:单片机移相相位差数字显示1方案设计与论证1.1移相网络设计方案本设计的核心问题是信号的模拟移相程控问题,其中包括波形相位以及波形幅度的程控。

在设计过程中,我们首先考虑了赛题中提供的方案。

如图1-1所示:V1VV2图1-1该模拟电路主要采用高、低通电路的临界截止点来产生极值相位的偏移。

当高、低通电路的截止频率等于输入信号频率时,根据其幅频特性,信号波形所产生的相位分别为45°和-45°,恰好满足赛题要求的连续相移范围-45°~45°的调节。

由于高、低通电路在截止点时会产生幅度的衰减,故电路在后级加了放大电路,且采用了电压串联负反馈的方式提高了输入阻抗并降低了输出阻抗,电路最后还设计有调幅装置,能够很好地满足A、B输出的正弦信号峰—峰值可分别在0.3V—5V范围内变化。

综上所述,该移相网络能够满足赛题的所有要求,且电路设计简单、易行,故我们直接采用了这种方式来产生模拟的相移输出。

1.2相位测量仪设计方案方案一:检相器可以利用正弦波形的正半周和负半周的对称特性。

基于单片机和CPLD的数字相位测量仪设计

测 量输 入 与输 出信 号 问 的相 差 △p以便 确 定 线性 控 制 的 范 围 。 ( , 常用 到的 一 般 测

量 工具 , 比如 在 电力 系统 中 电 网 并 网合 闸时 , 求 两 电 网 的电 信 要

号 相 同 , 就 要 求精 确 的 测 量 两工 频 信 号 之 间 的相 位 差 。 有 测 这 还

形, 电路 图如 图 2所 示 。 密 特触 发 器 在单 门限 电压 比较 器 的基 施

础 上 加 入 了 正反 馈 网 络 , 以 有 效提 高抗 干 扰 能 力 , 而 避 免 信 可 从

的 相位 。通 常所 谓 相 位 测量 是 指 对 两 个 同 频 率 信号 之 间 相 位 差

的 测量 。相 位 的 测 量很 重 要 , 测 某元 件 的阻 抗 Z 厶 因 此 如 = ,

姚 晖 李 伟 季上 满 沈科杰 胡 娅 ( 浙江理工大学信息电子学院, 浙江 杭州 30 1 ) 10 8

摘 要

介 绍 了数 字 式低 频 相 位 测量 仪 的 组成 、 作原 理 , 出 了一 种基 于单 片机 和 可编 程 逻辑 器件 的 低频 数 字相 位 测 量 仪 的 工 提 设 计 方 案。 系统 以 A 8 C 2单 片机 小 系统 及 Al r 司 的 E M7 2 S C8 — 5 C L 为核 心 , 频 率 为 2 H T9 5 t a公 e P 18 L 4 1 P D 对 0 z到 2 k z 0H 的 正 弦 波信 号 实现 精 确 测 频 、 相 , 用 以 8 7 测 并 2 9为 核 心 的键 盘 显 示 电路 给 以显 示 。 对 测 周 误 差进 行 了改进 分 析 。 设 计 还 该

Ke wors: a e m e s e, y d ph s a ur MCU, CPL f D,equ nc ,ror r e ye r

低频数字相位测量仪毕业设计毕业论文及文献综述[管理资料]

![低频数字相位测量仪毕业设计毕业论文及文献综述[管理资料]](https://img.taocdn.com/s3/m/d060522076a20029bc642dd6.png)

摘要本文设计的是低频数字相位测量仪的软件控制部分。

在设计中采用MCU与FPGA 相结合的方案,将软件部分系统分为控制数据采集处理和单片机控制显示两部分的软件设计,本部分分软件设计充分发挥单片机控制运算能力强的特点来对其各个模块进行软件编程。

数据的采集利用FPGA去完成,可以准确地采集到两个同频正弦信号的相位差所对应的时间差以及信号的周期,从而更好地提高系统的可靠性。

再根据单片机具有较强的运算、控制能力的特点,我们通过对单片机最小系统来进行编程以之完成读取FPGA的数据,并根据所读取的数据计算待测信号的频率及两路同频信号之间的相位差。

同时通过软件编程来实现功能键的切换,由显示模块显示待测信号的频率和相位差。

关键字:数据采集; 单片机; 频率; 相位差;ABSTRACTThis paper is designed to phase low-frequency digital measuring instrument. this design which uses the combination of The MCU and FPGA will be divided the hardware into two parts of data acquisition processing and MCU minimum system ,it give full use to the features of MCU-controlled computing for power , the FPGA data acquisition for high speed and resource-rich . we use the FPGA to complete collection of the data, so we can accurately collect the phrase difference between the two-phase sinusoidal signal ,corresponding to the time difference and the cycle of signal, so as to greatly improve the reliability of the system. Then according to characteristics of the shrapnel-strong operation and the ability to control, we use the minimum system of MCU to complete the reading of data FPGA, then according to the data read calculate the frequency of signals under test and the phase difference between the two-way same frequency signal. At the same time, through the switching of function keys ,the frequency and phase of signals under test Will be showed by moduleKeyword:Data; Acquisition; SCM; Frequency; phase目录绪论 (1)相位测量原理 (2)输入与采集 (2)频率的测量 (2)相位差对应的时间差的测量 (3)2 设计要求与设计方案 (4)设计要求 (4)设计方案 (4)设计思路 (4)各模块的作用 (4)设计方案 (4)3 整机电路原理 (6)MCU控制FPGA电路 (6)MCU控制显示电路 (7)整机电路原理 (8)4 软件设计 (10)MCU控制FPGA的软件设计 (10)MCU控制FPGA电路框图 (10)软件设计思路 (11)MCU控制FPGA各程序流程图 (11)MCU控制显示的软件设计 (13)显示软件设计 (13)单片机控制显示程序流程图 (14)5 程序设计 (15)单片机的源程序 (15)结论 (27)致谢 (28)参考文献 (29)绪论随着科学技术的突飞猛进的发展,电子技术广泛的应用于工业、农业、交通运输、航空航天、国防建设、科研、生产等国民经济的诸多领域中,而电子测量技术又是电子技术中进行信息检测的重要手段,在现代科学技术中占有举足轻重的作用和地位。

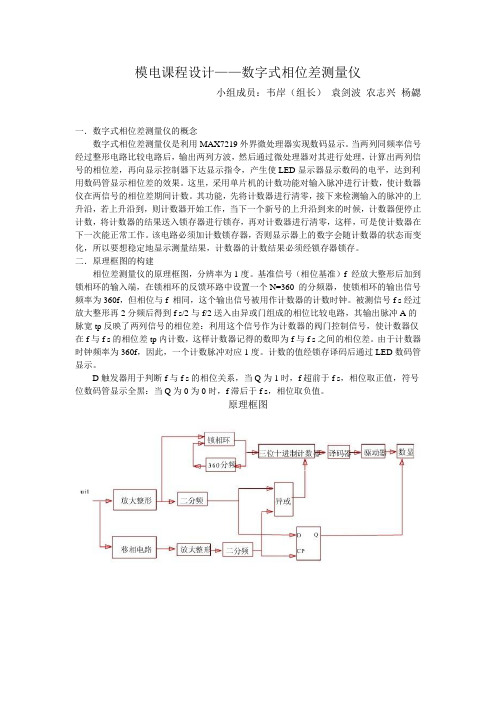

模电课程设计——数字式相位差测量仪

模电课程设计——数字式相位差测量仪小组成员:韦岸(组长)袁剑波农志兴杨勰一.数字式相位差测量仪的概念数字式相位差测量仪是利用MAX7219外界微处理器实现数码显示。

当两列同频率信号经过整形电路比较电路后,输出两列方波,然后通过微处理器对其进行处理,计算出两列信号的相位差,再向显示控制器下达显示指令,产生使LED显示器显示数码的电平,达到利用数码管显示相位差的效果。

这里,采用单片机的计数功能对输入脉冲进行计数,使计数器仪在两信号的相位差期间计数。

其功能,先将计数器进行清零,接下来检测输入的脉冲的上升沿,若上升沿到,则计数器开始工作,当下一个新号的上升沿到来的时候,计数器便停止计数,将计数器的结果送入锁存器进行锁存,再对计数器进行清零,这样,可是使计数器在下一次能正常工作。

该电路必须加计数锁存器,否则显示器上的数字会随计数器的状态而变化,所以要想稳定地显示测量结果,计数器的计数结果必须经锁存器锁存。

二.原理框图的构建相位差测量仪的原理框图,分辨率为1度。

基准信号(相位基准)f 经放大整形后加到锁相环的输入端,在锁相环的反馈环路中设置一个N=360 的分频器,使锁相环的输出信号频率为360f,但相位与f 相同,这个输出信号被用作计数器的计数时钟。

被测信号f s经过放大整形再2分频后得到f s/2与f/2送入由异或门组成的相位比较电路,其输出脉冲A的脉宽tp反映了两列信号的相位差:利用这个信号作为计数器的阀门控制信号,使计数器仅在f与f s的相位差tp内计数,这样计数器记得的数即为f与f s之间的相位差。

由于计数器时钟频率为360f,因此,一个计数脉冲对应1度。

计数的值经锁存译码后通过LED数码管显示。

D触发器用于判断f与f s的相位关系,当Q为1时,f超前于f s,相位取正值,符号位数码管显示全黑:当Q为0为0时,f滞后于f s,相位取负值。

原理框图三.电路原理图四.使用元件原理介绍(1)放大电路本设计采用的是LM324运算放大器,如下图:通过使用LM324运放器,我们可以使正弦波转变为方波。

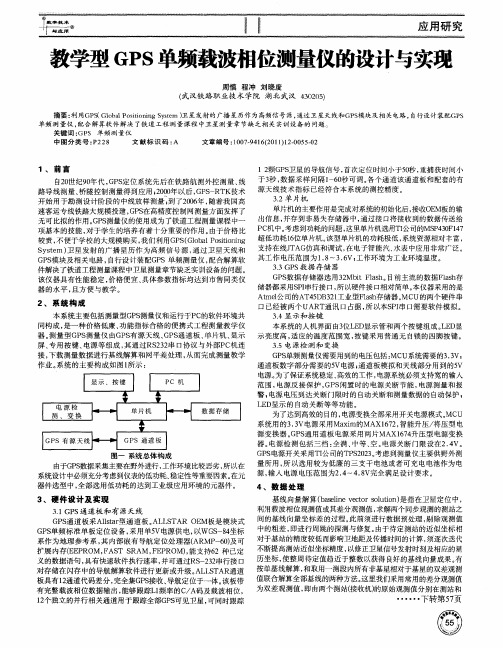

教学型GPS单频载波相位测量仪的设计与实现

12 P 卫星的导航信 号 , 颗G S 首次定位时间小于5秒 , 0 重捕 获时间小 于3 , 据采样 间隔卜 6 秒可调 。 秒 数 0 各个通道该通道板和配 套的有 自2 世纪9 年 代 , P 定位系统先后在铁 路航测外控 测量 、 0 0 GS 线 路导 线测量 、 隧控 制测量得到应用 ;0 0 以后 , P — K技术 源天线技术指 标 已经符合本 系统 的测控精 度。 桥 2 0年 G S RT 3 单 片机 . 2 开始 用于勘测设 计阶段的 中线放样 测量 ; 到了2 0 年 , 06 随着 我国高 单片机的主要作用, P 在高精度控 制网测量方面发挥 了 GS 出信息 , 并存到非易失存储器 中, 过接 口将接收 到的数据传送给 通 无可 比拟的作用 。 P  ̄ 量仪的使用成为 了铁道工程测量课程 中一 GSI ] C 考虑到功耗的 问题 , 这里单片机选用T 公司的MS 4 0 17 I P 3F 4 项基 本的技能 , 对于 学生的培养有着十分重要 的作用 。 由于价格 比 P 机 中。 超低功耗1位单片机 。 6 该型单片机的功耗极低 , 系统资源相对 丰富 , 较贵 , 不便于学校的大规模购买 , 我们 利用G S G o a P s i ig P ( lb 【 oio n tn 支持在线J AG T 仿真和调试 , 在电子智能汽、 水表 中应用非常广泛 。 S se 卫 星发射 的广 播 星历 作为高频 信号 源 , 过卫 星天线和 y tm) 通 其工作 电压 范围为 18 .V; . ~3 6 工作环境 为工业环 境温度。 GS P 模块及相 关电路 , 自行设计装] P  ̄G S单频测量仪 , 配合解算软 33G S 据 存 储 器 . P 数 件解决 了铁道工程测量课程 中卫 星测量章节缺乏 实训 设备 的问题 。 G S P 数据存 储器选用3 MbtF ah 目前 主流的数据F ah 2 i ls 。 ls 存 该仪器具 有性能稳定 , 价格便宜 、 体参 数指标均达到市售 同类仪 具 储器都 采用S I P 串行接 口, 以硬件接 口相对简单。 所 本仪器采用的是 器 的水平 , 方便与 教学 。 且 A me 司的AT 5 B 2 工业型Fah t l 公 4D 31 ls 存储器。 U的两个硬件 串 MC 2、 系 统 构 成 口已经被两个 UAR T通讯 口占据 , 以本S I 所 P 串口需要软件模 拟。 本系统主要包括测量型G S P 测量仪和运行于P 的软 件环 境共 C 34显 示 和 按 键 . 同构成 , 是一种价格 低廉 、 功能指标合格 的便 携式工程测量教学仪 本系统 的人机 界面 由3 E 位L D显示管和两个按键组成 。 E 显 LD 器。 测量型 G S P 测量 仪由G S P 有源 天线 、 P 通 道板 、 G S 单片机 、 显示 示亮度高 , 适应的温度范 围宽 , 按键采用普通无 自锁 的四脚按键。 屏、 专用按 键、 电源等组成 , 其通过RS 3 串 口协议与: 22 外部PC 机连 35电 源检 测 和 变 换 . 接, 下载测量数据进行基 线解算 和网平差处理 , 从而完成测量教学 GS P 单频测量仪需要用到的 电压 包括 : U系统需要 的3 3 MC .V; 作业 。 系统 的主要构成如 图l 所示 : 通道 板数字 部分需要的5 V电源 ; 通道板模拟和天线部分用到的5 V 电源 。 了保证系统稳定、 为 高效 的工作 , 电源系统必须支持宽的输入 范围 , 电源反接保 护 , P 闲置 时的 电源关断节能 , G S 电源测量 和报

基于DSP的低频数字式相位测量仪的设计

随着科学技 术的突飞猛进的发展, , 电 技 T 30 C 4 2 A 8S 2 MS 2 V 50 和 T 9 5 芯片的集成度高 、

智能 程 度 高 、功 能 强 大 ,使得 它实 现 起 来 比较

教 ,研 究方 向 为移 动 术 广 泛 的 应用 T工 、 、农 、 、交通 运 输 、航 I I

究网络 、系统的频率特性 中具有重 受意义。近 果。系统框 图如图 i 所示。

图 1低 频 数 字 式 相位 该 系统 以T 30 C 4 2 核心 , 待 测 MS 2 V 5 0 为 对

测量仪 系统框图

量信 号进行 采集 和处理 ,包括 栏彤和移 相电

路 ,把 采 集米 的 模 拟 信 号转换 为数 字 信 。其

湖南工学院 俞斌 贾雅琼 汤群芳 摘 要: 本 文提 出了一种 基于 T 3 0 C 4 2的低 频数字 式相位测 年来 ,随着科学技术的迅速发展 ,很多测量仪 MS 2 V 5 0

量仪 的设计方法。

逐渐 向 “ 智能仪器”和 “ 自动测试 系统”发展 , 这使得仪 器的使 _ 比较简单 ,功能越来越多。 } H

本低 频 数 字 式 相 位 测 量 仪 由 T 30 C 4 2 MS 2 V 5 0 、

关键 词 : DS ;低频 ;数字 式;相位 测量 ;S M P C

苯 06 文20 年

月2日收到。 俞斌 : 助

0 吉 |

AT8 2和 小 规 模 集 成 电 路 构 成 。 由 于 9S 5

通信、单片机和 DS 航天、国防建设 等国民经济的诸 多领域 中,而 简单 ,而且 ,具有体积小 、性价比高、性能稳 P

应 用。 电子 测量 技 术 又 是 电子 技 术 中进 行 信 息 检 测 的 定 的特 点 。

《相位法激光测距仪设计》

《相位法激光测距仪设计》摘要:一、引言二、相位法激光测距仪的原理与结构1.相位法测距原理2.激光测距仪的结构组成三、相位法激光测距仪的设计方法1.欠采样技术与同步检测原理2.晶体滤波器和直接数字频率合成计四、实验结果与分析1.系统整体结构和性能改进2.数字化与自动化程度的提高五、结论正文:一、引言激光测距仪是一种非接触式的测量仪器,它利用激光束测量目标物体与测量仪器之间的距离。

根据测距方法的不同,激光测距仪可分为相位法激光测距仪和脉冲法激光测距仪。

相位法激光测距仪通过检测发射光和反射光之间的相位差来测量距离,具有较高的测量精度和较远的测量范围。

因此,本文将重点介绍相位法激光测距仪的设计方法。

二、相位法激光测距仪的原理与结构1.相位法测距原理相位法激光测距仪的原理是利用激光器发出一束激光,经过调制后射向目标物体,然后通过接收器接收目标物体反射回的激光束。

由于激光在传播过程中会发生相位变化,因此通过检测发射光和反射光之间的相位差,可以计算出目标物体与测量仪器之间的距离。

2.激光测距仪的结构组成激光测距仪主要由激光器、调制器、发射器、接收器、相位检测器和数据处理器等组成。

激光器负责发射激光束,调制器负责对激光束进行调制,发射器负责将激光束射向目标物体,接收器负责接收目标物体反射回的激光束,相位检测器负责检测发射光和反射光之间的相位差,数据处理器负责对测量结果进行处理。

三、相位法激光测距仪的设计方法1.欠采样技术与同步检测原理为了降低数据处理的复杂程度,可以采用欠采样技术与同步检测原理改进测相方法。

欠采样技术是指在采样频率较低的情况下,通过增加采样时间来提高采样精度。

同步检测原理是指通过同步检测发射光和反射光的相位差,来消除环境因素对测量结果的影响。

2.晶体滤波器和直接数字频率合成计为了改进测距仪的滤波与调制手段,可以采用晶体滤波器和直接数字频率合成计(DDS)。

晶体滤波器具有较高的滤波性能和较低的功耗,可以有效地抑制干扰信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

获全国一等奖作品之一(华中科技大学)作者:缪学进刘云王学虎赛前辅导:王少荣文稿整理辅导:涂仁发摘要:本作品由相位测量仪、数字移相信号发生器和移相网络3个模块构成,分别由两块单片机独立地实现控制与显示功能。

采用DDS技术生成两路正弦波信号,并通过改变存储器中数据读取的起始地址来实现数字移相的功能,用φ—T变换技术来实现相位差的测量,使得显示分辨率精确到0.01°,测得的频率与相位差值送LCD进行显示,加入红外键盘以及语音播报的功能,使得系统具有智能化,人性化的特色。

一、方案论证与设计1.相位测量方案方案一:将被测的两路正弦波信号经比较器整形成方波信号,利用异或门电路进行鉴相处理;将得到的脉冲序列经过RC平滑滤波取出其直流分量,该直流电平的幅值与两路信号的相位差成正比;将此信号送入A/D转换器由单片机进行运算处理,从而计算出相位差值。

方案二:采用脉冲填充计数法,将正弦波信号整形成方波信号,其前、后沿分别对应于正弦波的正相过零点与负相过零点,对两路方波信号进行异或操作之后,输出脉冲序列的脉宽,脉宽可以反映两列信号的相位差,以输入信号所整形成的方波信号作为基频,经锁相环倍频得到的高频脉冲作为闸门电路的计数脉冲,由单片机对获取的计数值进行处理得到两路信号的相位差。

方案三:鉴相部分同方案二,将两路方波信号异或后与晶振的基准频率进行与操作,得到一系列的高频窄脉冲序列;通过两片计数器同时对该脉冲序列以及基准源脉冲序列进行计数,一路方波信号送入单片机外部中断口,作为控制信号控制两片计数器,得到的两路计数值送入单片机进行处理得相位差值。

对以上3种方案进行比较,方案一在低频段时,RC滤波电路的输出波动很大,难以达到要求的相位精度,而方案二在所测频率较高时,受锁相环工作频率等参数的影响/相位差测量的误差会比较大。

采用方案三由高精度的晶振产生稳定的基准频率,可以满足系统高精度、高稳定度的要求,2.频率测量方案方案一:用专用频率计模块,如ICM7216芯片来测量频率,其内部带放大整形电路,可以直接输入正弦信号;用一块高精度晶振和两个低温度系数电容构成10MHz振荡电路,其转换开关具有0.01、0.l、l、10s四种闸门时间,量程可以自动切换,待计数过程结束时显示测频结果。

方案二:利用可编程计数器来实现频率的测量,将被测信号转换为方波信号,再输入可编程计数器8254的某一路CLK端口,并将Gate端置为高电平,利用单片机产生的定时中断来控制8254的计数,最后计数值送入单片机处理并输出。

对以上方案进行比较,利用频率计模块来实现频率测量的方案中,ICM7216的外围硬件电路复杂,测频精度不够高;而方案二用单片机控制计数器工作,硬件简单,且频率测量精度高,这也是目前较为成熟的一种高精度测频方案。

因此,采用方案二来实现频率的测量。

3.数字移相信号发生器方案在数字移相信号发生器模块电路中,首先要生成相位测量仪所需要的两路不同相位的正弦波信号,目前DDS已经是很完善的一种数字信号产生方案,所以在该部分,我们主要对产生正弦波信号的数字移相方案进行论证。

方案一:将正弦波量化为一张数据表,分别存储于两片E2PROM之中,通过单片机控制计数器来对存储器中的数据进行寻址,并经过两片D/A转换芯片循环输出该数据表,当两路D/A转换芯片所获得的数据序列不同时,转换所得的两路正弦信号存在相位差,相位差值仪仅与数据地址的偏移量有关。

方案二:将参考正弦波转换为方波,以此信号为基准,延时后产生另一路同频率的方波,通过改变延时的长短来控制两个波形的相位差,最后通过波形变换电路将其还原为两路有相位差的正弦波输出。

综合以上两种方案,方案一采用2 KB的存储芯片2817存储量化的正弦波数据,通过单片机可以较精确地控制移相的大小,实现1°相位差步进,而且硬件电路较为简单;而方案二虽然也可以精确控制移相,但是,相对而言,硬件电路更为复杂,调试较为麻烦,因此,我们采用第一种方案来实现数字移相。

二、原理分析与硬件电路图根据赛题要求,该低频相位测量系统包括相位测量仪、数字式移相信号发生器和移相网络3个模块,由于3个模块相对独立,其中相位测量模块是重点。

以下分别对其进行原理分析电路设计。

1.相位差测量模块(1)原理分析输入两路同频率的正弦波信号,其波形表达式分别为当两路信号的频率相同时,相角差θ=φ1-φ2是一个与时间无关的常数。

如图2_ C1扩示,将此两路正弦波信号经过放大整形成两路占空比为50%的正方波信号f1、f2,经过异或门输出一个脉冲序列A,与晶振产生的基准脉冲波B进行与操作,得到调制后的波形C,在一定的时间范围内对B、C中脉冲的个数进行计数,分别得Nc、Nb,则其相位差计算公式为θ=Nc/Nb x 360°/2,采用多个周期计数取平均值的方式以提高测相精度,系统框图如图2-Cl-2所示。

(2)原理电路①前级放大整形电路。

两列正弦波信号经过一级电压跟随器以提高测量仪的输入阻抗,选用高精度、低漂移型运放TLE2074,使输入阻抗达到兆欧数量级,由LM311构成的迟滞比较器可以有效地避免在过零点时信号的干扰和抖动所引起的电压跳变,最后通过一级单门限电压比较器输出两路TTL电平信号,经异或门得到方波的脉冲序列。

该前级放大整形电路的基本原理如图2-Cl-3所示。

②相位差测量电路。

通过理论分析可知,基准频率越高,窄脉冲个数越多,相位差的测量也越精确,但受到8254极限工作频率的影响,最终选取8.000MHz的晶振,由单片机I /O口控制两片8254分别对两路脉冲进行计数,将8254内含的两路计数器进行级联以提高计数位数,对32位的计数结果进行浮点运算得相位差,其原理图如图2-Cl-4所示。

③相位极性判别电路。

图2-Cl-4所示的为相位测量电路,它只能给出相位差的大小,无法判断波形的超前或者滞后,因此,将波形整形电路的两路输出方波送入D触发器中进行相位极性判别,当V o超前vI,时,Q端输出高电平,反之输出低电平,极性判别的原理图如图2-C1-5所示。

2.数字式移相信号发生器模块(1)原理分析要实现数字移相,首先要生成两路正弦波信号,在目前的波形生成方案中,最常用的就是数字式直接频率合成技术( DDS),DDS的工作原理是:基于相位与幅度的对应关系,通过改变频率控制字来改变相位累加器的相位累加速度,然后在固定时钟的控制下取样,取样得到的相位值通过相幅转换得到的相位值所对应的幅度序列,通过D/A转换以及低通滤波之后输出正弦波信号。

基本框图如图2-C1-6所示。

相幅转换的方式选用查表法,将正弦波的量化数据存储于两片E2PROM之k中,通过控制读取存储器数据的地址差,改变输出波形的相位差,每个周期取样360个点,相位差步进为1°。

锁相环倍频的基频为900Hz,输出正弦信号的频率范围为5MHz-23kHz,实际频率步进值为2.5Hz。

原理框图如图2-Cl-7所示。

(2)原理电路如图2-C1-8所示,选用2KB的E2PROM存储器2817对正弦波信号的量化数据进行存储,由晶振电路产生基准频率的方波作为锁相环的基准时钟,配合可编程计数器8254进行倍频处理,倍频之后的信号控制计数器74HC4040进行循环计数,将计数器的输出作为存储器读取的地址,改变数据读取的地址即可改变输出波形的相位。

通过改变AD7524的基准电压V REF幅值来改变输出波形的峰-峰值大小。

因两路正弦波产生的原理相同,仅仅是数据读取的起始地址不同,图2-C1-9所示的是一路波形生成电路,另一路硬件电路与此相同。

三、软件设计与流程1.系统软件介绍软件部分采用模块化程序设计的方法编制,系统软件由主控制程序、液晶显示部分子程序,键盘服务子程序、语音提示部分子程序组成。

选用凌阳公司SPCE061A型16位单片机微控制器,其指令系统中提出了具有较高运算速度的16x16位乘法运算指令和内积运算指令,为其应用增添了DSP功能,可以进行数字信号处理,因此,系统可很便利地加入了语音模块。

在其编译环境下可以内嵌C语言,C函数与汇编函数可以很方便的相互调用,所以编程效率高而且可靠。

2.程序流程图相位测试模块流程图如图2-Cl-10所示。

数字移相信号产生流程图如图2-C1-11所示。

四、系统测试与误差分析1.测试环境时间2003年9月18日。

温度25°C。

2.测试仪器多功能数字万用表FLUKE17B工频电参数测试仪BS1905数字示波器TDS1002函数发生器/计数器CA164OP-20型3.测试方法硬件模块测试:数字移相信号发生器,通过红外键盘对输出两路信号的频率、相位差以及峰-峰值进行设置。

最后把产生的有相位差的两路信号分别接入相位测试电路进行相位差的测量。

软件模块测试:采用自下而上的调试方式,先进行模块测试程序的调试,待全部通过之后将所有的软件程序串接起来并结合硬件电路进行整体调试。

4.测试数据(l)相位差测量仪校准由于实验室只有50Hz工频相位测试仪,所以选取了50Hz频点进行测试,由此来对相位测量仪进行校准,数据如表2-Cl-1所示。

(2)相位差与幅度的校验根据题意要求,自选几个频点进行校验,如表2-C1-2~表2-Cl-5所示。

5.误差分析(l)相位测量电路的误差分析在相位测量过程中,受电子元器件性能的影响,在正弦波经过零检测电路整成方波的过程之中,两路信号不可能做到时延特性完全一致,前端放大电路以及过零检测电路会带来方波信号相对于输入信号的过零点偏移,所以得到的两个方波信号的相位差实际上是输入信号的相位差和两路过零比较电路相位差的综合相位差,由于是在一定的时间内对脉冲的个数进行计数,因此将引入截断误差,尤其当两路信号的相位差较小时,截断误差的存在将在很大程度上对相位测量的精度造成影响。

(2)数字式移相信号发生电路的误差分析在数字式移相信号发生电路中,由于锁相环的稳定度的影响,波形的微小振荡就会使得输出和设定值之间存在输出偏差,同时由于D/A转换过程中不可避免的存在量化误差,所以产生的波形幅值与频率将会与设定的预期值形成一定的误差。

由于通用板本身结构的限制,以及电路中两路信号的串扰等影响,都会使得系统存在一定的误差。

五、总结本系统实现了题目基本部分以及发挥部分的要求,相位测量仪的测量范围为:电压(峰-峰值);0. 2~30V,频率:2Hz~65kHz;显示分辨率为0.01°,测量的绝对误差在2°以内。

数字式移相信号发生器扩展到5Hz~23kHz,频率步进达到2.5Hz,相位差步进1°,幅值在0.1~5.5V范围内可调,人机交互接口采用双键盘(有线键盘+红外遥控键盘)、带语音提示的模式;由于单片机留有空闲的I/0 口,可以进一步对系统的功能进行扩展,比如,加入相位测量的自适应调节、加入波形的打印功能或者将语音播报的功能进一步完善等。