第2章 IC工艺扩散掺杂技术

第二章 扩散工艺

5、SiO2中的扩 散

对于常见的杂质,如B,P,As等,其在SiO2中的扩散系数比在 Si中的扩散系数小得多,因此,SiO2经常用做杂质扩散的掩蔽层

SiO2用做扩散掩蔽层的最小厚度估算公式:

影响SiO2的掩蔽效果的主要■

■ ■

扩散时间

2、杂质扩散机制

(1) 填隙扩散(Interstitial Diffusion Mechanism)

■ ■

填隙型杂质扩散很快 对硅掺杂水平无直接贡献

2、杂质扩散机制

(2) 直接交换式扩散(Interstitial Diffusion Mechanism)

本体原子

杂质原子

替位型杂质原子必须打破与周围本体原 子间的键合,才能进行直接交换式扩散。

■

MOS电容的C—V法

耗尽层宽度

2 (Vbi V ) W qNsub

A C W A2 qN sub 2 (Vbi V )

二极管电容

杂质浓度

8(Vbi V )3 N sub ( z ) 2 A q

dC( z ) dV

■

扩展电阻法 (1) 将样品磨出一个小角度斜面 (2) 将样品放在载片台上,用一对探针以预定压力与样品 表面接触,测量该电阻值。 (3) 将该电阻值与一个已知浓度的标准值进行比较, 从电阻率反推出载流子的分布。 主要问题 (1) 测量结果取决于点接触的重复性。 (2) 进表面测量比较困难。 (3) 测量样品与校准标准片比较接近。

杂质原子

扩散过程:

■

■

替位式杂质原子被自填隙本体原子推到填隙位置;

杂质原子占据另一个晶格位置,该晶格位置上的本体原子 被移开并成为自填隙原子。

注意:只有存在空位扩散时,才能发生推填隙扩散。

集成电路制造技术 第三章 扩散

3.3.1 恒定表面源扩散

x

N ( x ,t ) N s ( 1

2

2

)

Dt

exp( 2 )d

0

简化,N s [ 1 erf ( 2

Dt )] N serfc( 2

) Dt

―余误差分布

Dt―扩散长度;Ns= NSi(杂质在Si中的固溶度) erf(x)—误差函数(error function);

N t

dx

J2

J1

ΔJ

ΔJ dx

dx

D

2N 2x

dx

故

N t

2N D 2x

--扩散方程

3.3 扩散杂质的浓度分布

3.3.1 恒定表面源(浓度)扩散

(constant-surface-concentration) 定义: 扩散过程中,Si片表面杂质浓度始终不变

(等于杂质在Si中的溶解度)。 例如:预淀积工艺,箱法扩散工艺 初始条件:t=0,N(x,0)=0; 边界条件: N(0,t)=Ns , N(∞,t)=0; 解扩散方程,

D—扩散系数(cm2/s),

N (x,t) x

—浓度梯度

“-”从高浓度向低浓度扩散

J—扩散流密度:单位时间内通过单位面积的杂质数。

3.2 扩散系数与扩散方程

3.2.2 扩散系数

D=D0 exp(-ΔE/kT)

D0—表观扩散系数,既1/kT→ 0时的扩散系数

ΔE—激活能;间隙扩散:ΔE = Wi, 替位扩散:ΔE = Ws+ Wv

3.1.1 间隙式扩散

①定义—重金属杂质Ni,Fe,Cu,Ag,Au在晶格间的间隙 中运动(扩散)

②势垒—间隙位置的势能相对极小,相邻两间隙之间 是势能极大位置,必须越过一个势垒Wi。 ∵ f(Wi)∝exp(-Wi/kT) —玻尔兹曼统计分布

半导体制造工艺基础之扩散工艺培训课件(PPT 28页)

推进:高温过程,使淀积的杂质穿过晶体,在 硅片中形成期望的结深。

此阶段并不向硅片中增加杂质,但是高温下形成的 氧化层会影响推进过程中杂质的扩散,这种由硅表 面氧化引起的杂质浓度改变成为再分布。

目的是为了控制表面浓度和扩散深度。

• 激活:使温度稍微升高,此过程激活了杂质 原子。

的扩散速度特别快,造成结平面不平坦,PN结击穿。

(2) 表面玻璃层。硼和磷扩散之后,往往在硅片表面形成一层硼硅玻璃或磷硅玻 璃,此玻璃层与光刻胶的粘附性极差,光刻腐蚀时容易脱胶或产生钻蚀,而 且该玻璃层不易腐蚀。

(3) 白雾。这种现象在固一固扩散及液态源磷扩散经常发生。主要原因是淀积二 氧化硅层(含杂质源)时就产生了或在磷扩散时磷杂质浓度过高以及石英管 中偏磷酸产生大量的烟雾喷射在硅片表面,在快速冷却过程中产生。光刻时 容易造成脱胶或钻蚀。

方块电阻的检测

利用图中所示电路,将电流表所示电流控制在3毫安以内, 读出电压表所示电压,利用下式计算:

RS

CV I

式中常数C是由被测样品的长度L、宽度a、厚度d,以及

探针间距S来确定,常数C可由表查出。

扩散工艺

扩散常见的质量问题

(1) 合金点和破坏点:在扩散后有时可观察到扩散窗口的硅片表面上有一层白雾 状的东西或有些小的突起。 用显微镜观察时前者是一些黑色的小圆点,小圆点称为合金点; 后者是一些黄亮点、透明的突起,透明突起称为破坏点。杂质在这些缺陷处

(2)可以通过对扩散工艺条件的调节与选择,来控制扩散 层表面的杂质浓度及其杂质分布,以满足不同器件的要求。

(3)与氧化、光刻等技术相组合形成的硅平面工艺有利于改 善晶体管和集成电路的性能。

芯片扩散工艺

芯片扩散工艺芯片扩散工艺是集成电路制造过程中的重要环节之一,它直接影响着芯片的性能和可靠性。

本文将从芯片扩散工艺的定义、工艺步骤、工艺参数和应用领域等方面进行详细介绍。

一、芯片扩散工艺的定义芯片扩散工艺是指将掺杂源材料中的掺杂原子通过扩散过程引入到硅片表面或内部特定位置的一种技术。

通过扩散工艺,可以改变硅片的电学性质,实现不同功能和性能的芯片制备。

1. 准备工作:包括硅片清洗、掺杂源材料制备和掺杂源液体的制备等。

2. 掺杂源涂覆:将掺杂源液体均匀地涂覆在硅片表面。

3. 扩散过程:将涂覆了掺杂源液体的硅片放入高温炉中,在特定温度下进行扩散,使掺杂原子从掺杂源液体向硅片内部扩散。

4. 清洗工艺:将扩散后的硅片进行清洗,去除表面的杂质和残留物。

5. 其他工艺步骤:根据具体需求,可能还需要进行退火、腐蚀、沉积等工艺步骤。

三、芯片扩散工艺的参数1. 温度:扩散过程中的温度是一个重要的参数,它决定了掺杂原子的扩散速率和深度。

2. 时间:扩散时间也是一个关键参数,它决定了掺杂原子扩散的程度。

3. 掺杂浓度:掺杂源液体中掺杂原子的浓度决定了最终芯片的电学性质。

4. 扩散气氛:在扩散过程中,气氛的成分和压力也会对扩散效果产生影响。

四、芯片扩散工艺的应用领域1. 集成电路制造:芯片扩散工艺是集成电路制造过程中的核心环节,它决定了芯片的性能和功能。

2. 太阳能电池:芯片扩散工艺可以用于制备太阳能电池中的p-n结。

3. 传感器制造:芯片扩散工艺可以用于传感器的制造,改变其电学特性,实现不同的传感功能。

芯片扩散工艺是集成电路制造中不可或缺的一环。

通过合理选择工艺参数和优化工艺步骤,可以实现对芯片电学特性的精确控制,进而提高芯片的性能和可靠性。

随着科技的不断进步和创新,芯片扩散工艺也将不断发展,为各个领域的应用提供更加优质的芯片产品。

第2章 IC工艺扩散掺杂技术讲解

Si双极npn晶体管芯片的工艺流程

1、衬底制备,2、外延生长,

3、一次氧化,4、一次光刻,

5、基区扩散,6、二次氧化,

7、二次光刻,8、发射区扩散, n+

E

B

9、三次氧化,10、三次光刻, p

11、金属镀膜,12、反刻金属膜 n

13、背面镀膜,14、合金化 n+

C

Wafer fabrication (front-end)

2CS

Dt

– b)恒定杂质总量 Q 即:

Cx,tdx Q

0

Cx,0 0

C,t 0

d0,t 0

dx

– 可得: Cx,t

Q

Dt

exp

x2 4Dt

为一高斯分布;其表面浓度为:

CS C0,t

Q

Dt

– 3)结深xj 在PN结的扩散中,衬底材料中已有导电性 相反的杂质,其浓度为Csub。定义导电性转

– 3)其它扩散机制 a)直接交换 b)Kick-out机制 (page 45,

Kick-out机制的 扩散速率一般超 过替位式扩散 如:Ni等。

• 扩散系数的普遍表达式:

通常高阶电荷态的几率很小可以忽略 (P.43、44;Table:3.2, Example: 3.1) • 而某一种扩散系数可以表达为:

x 由质量守恒,得 C J ,

t x

因而,

Cx,

t

t

D

2Cx,

x 2

t

Fick’s Second Law

– 2)两种边界条件

– a)恒定表面源浓度

即:C0,t CS C,t 0

可得:

第二章扩散

本体原子

杂质原子

不需要自填隙本体原子来推动扩散过程的进行

3、Fair空位模型:

建立在空位扩散机制的基础上

1)“空位电荷":中性空位俘获电子,使其带负电;中性空位 的邻位原子失去电子,可使空位带正电。 2)空位模型:总扩散率是所有荷电状态的空位的扩散率的加权 总和,加权系数是这些空位存在的概率。 带电空位的数量 总扩散率表达式:

■

硅中杂质的扩散率曲线(低浓度本征扩散):

■ 中性空位的扩散率:

其中,E0a是中性空位的激活能(eV);

D00是一个与温度无关的系数,取决于晶格结构和振动频率。(cm2/s)

■

如果必须考虑带电空位的扩散率,则扩散率就是位置的函

数,因而费克第二定律方程必须采用数值方法来求解。

4、费克第二定律的分析解

1、横向扩散:杂质在纵向扩散的同时,也进行横向的扩散

■

一般横向扩散长度是纵向扩散深度的0.75 - 0.85;

横向扩散的存在影响IC集成度,也影响PN结电容。

■

2、内建电场的影响

高温下杂质处于离化状态,杂质离子与电子(空穴)同时向低浓 度方向扩散。电子(空穴)扩散速度快,形成空间电荷层,建立 一自建电场,使离子运动形式为扩散+漂移。 有效扩散系数Deff

费克简单扩散方程 1) 第一种边界条件:(预淀积扩散) 在任何大于零的时刻,表面的杂质浓度固定

此时扩散方程的解为: 被称为特征扩散长度(pm); Cs是固定的表面杂质浓度(/cm3) 预淀积扩散又被称为恒定表面源(浓度)扩散;在实际工艺中, Cs的值一般都是杂质在硅中的高浓度,与温度有关。

2、杂质扩散机制

(3) 空位扩散(vacancy-assisted Diffusion Mechanism)

2、半导体工艺原理-扩散

薄层电阻Rs(方块电阻) 表面浓度:扩散层表面的杂质浓度。

扩散层质量参数

方块电阻

方块电阻是标志扩散层质量的另一个重要参数, 一般用R□或Rs表示,单位是Ω/□ 。

2、恒定杂质总量扩散

扩散开始时,表面放入一定量的杂质源,而在以后的扩散

过程中不再有杂质加入。假定扩散开始时硅片表面极薄一层内

单位面积的杂质总量为 QT ,杂质的扩散长度远大于该层厚度,

则杂质的初始分布可取为 函数,扩散方程的初始条件和边界

条件为

0 N (x, t)dx QT

N (,t) 0

2 NS1

D1t1 D2t2

exp

x

2 j

4 D2t2

NB

即可解得

xj 2

D2t2

ln

2 NS1

NB

1

D1t1 D2t2

2

A

D2t2

掺杂分布控制:

3.3 简单理论的修正

前面得出的扩散后的杂质分布是采用理想化假设的结果, 而实际分布与理论分布之间存在着一定的差异,主要有:

1、二维扩散(横向扩散) 实际扩散中,杂质在通过窗口垂直向硅中扩散的同时,也 将在窗口边缘沿表面进行横向扩散。考虑到横向扩散后,要得 到实际的杂质分布,必须求解二维或三维扩散方程。横向扩散 的距离约为纵向扩散距离的 75% ~ 80% 。由于横向扩散的存在, 实际扩散区域大于由掩模版决定的尺寸,此效应将直接影响到 VLSI 的集成度。

2、杂质浓度对扩散系数的影响

前面的讨论假定扩散系数与杂质浓度无关。实际上只有当 杂质浓度比扩散温度下的本征载流子浓度 ni(T) 低时,才可认 为扩散系数与掺杂浓度无关。在高掺杂浓度下各种空位增多, 扩散系数应为各种电荷态空位的扩散系数的总和。

半导体工艺原理—扩散掺杂工艺(2013520)(贵州大学)

讨论晶体中杂质浓度与扩散时间的关系,又称第二Fick定 律。

22

第二扩散定律

C ds x Js J dJ s

t

CJ

DC x

t x

x

C t

D

2C x2

dx

J

J+dJ

S

x x+dx

23

扩散杂质的分布

本征扩散系数: 非本征扩散系数:

Di Di0DiDiDi2Di0

2

DeDi0Dinpi Dinni Di2nni

34

发射区推进效应

e

b

P扩散

n p

n

xbc

掺B δ

掺P

也称为发射区陷落效应。B扩散的增强是由于磷与空 位相互作用形成的PV对,发生分解所带来的复合效应 。

35

氧化增强扩散(OED)

D

2C x2

边界条件为:C(0,t)=Cs

C(∞,t)= 0

初始条件为:C(x,0)=0,x>0

恒定表面源扩散杂质分布情况

C(x,t)

Cs

t1

t2 t3

CB

0

x

xj1 xj2 xj3

Cx,tCserfcx2 Dt

25

恒定表面源扩散

结深

xj

2e

rf1cC CsB

Dt A Dt

杂质数量

Q Cx,tdx2Cs

41

扩散设备与工艺

扩散设备多是炉丝加热的热壁式扩散炉。和氧化炉相类似。 根据扩散源的不同有三种扩散工艺:固态源扩散,液态源扩

散,气态源扩散。 选择源必需满足固溶度、扩散系数要求。 选择好掩蔽膜。

第二章 掺杂技术

e

dE --电子阻挡能量损失率 e dR

二. 能量损失模型

3.注入能量与阻挡本领(模型)关系

临界能量(交叉能量)Ene: Sn(E)=Se(E)处的能量. ①低能时(E0< Ene),以核阻挡为主; 高能时(E0> Ene),以电子阻挡为主. ②Ene随注入离子原子量的增加而增大.

5.扩散层质量参数

⑤击穿特性 理想pn结反向I-V特性:曲线平直,有明显拐点, 漏电流小. 几种典型的异常击穿 a.软击穿 特点:无明显拐点 原因:PN结处的晶格缺陷及杂质沾污形成复合中心,成为 PN结的漏电流通道,使反向漏电流随反向电压的增 高而增大.

5.扩散层质量参数

b.背靠背击穿 特点:反向饱和电流大,几百μA-几mA 原因:表面沟道效应 c.分段击穿 特点:较低电压下有第一个击穿点. 原因:层错,光刻图形边缘不整齐. d.低压硬击穿 特点:有明显拐点,但在远低于理论值. 原因:PN结有较大局部尖峰;基区过窄;外延层过薄.

5.扩散层质量参数

包括:结深XJ ,方块电阻R□(RS) ,表面浓度 NS ,击穿电压BV等. ①结深Xj 定义:pn结的几何位置与扩散层表面的距离. 设,衬底的杂质浓度为NB,即N(XJ ,t)=NB,得 xj N B = N s erfc( ) 2 Dt

5.扩散层质量参数

NB 恒定源结深: x j = 2 Dt erfc ( N ) ,余误差分布 S

1.恒定表面源扩散

N ( x ,t ) = N s ( 1 2

x 2 Dt

简化,得

π

)

x

exp( λ 2 )dλ ∫

0

N ( x , t ) = N s [ 1 erf (

2 Dt

半导体制造工艺之扩散原理概述

半导体制造工艺之扩散原理概述引言半导体器件是现代电子化工程的重要组成部分,而半导体制造工艺中的扩散过程是其中的核心步骤之一。

扩散是指将外部杂质或原子通过加热和蒸发的方式引入半导体晶体内部,从而改变其导电性能的过程。

本文将概述半导体制造工艺中的扩散原理,包括扩散的定义、分类、扩散过程的主要步骤以及应用。

扩散的定义和分类扩散在半导体制造加工中是用于改变材料电学特性和形成器件结构的重要工艺。

它通过在半导体材料中掺杂外部杂质或原子,改变其禁带宽度、导电性能和晶格结构,从而实现对器件特性的控制。

根据掺杂的原子种类和结构变化,扩散可以分为以下几类:1.硼扩散(Boron diffusion):将硼原子引入到半导体材料中,可以增加材料的p型掺杂浓度。

2.磷扩散(Phosphorus diffusion):将磷原子引入到半导体材料中,可以增加材料的n型掺杂浓度。

3.氮扩散(Nitrogen diffusion):将氮原子引入到半导体材料中,可以改变半导体材料的特性,如降低材料的电阻率和增加材料的硬度。

4.氢扩散(Hydrogen diffusion):将氢原子引入到半导体材料中,可以提高材料的电阻率。

5.金属扩散(Metal diffusion):在半导体材料中引入金属原子,可以改变材料的特性,如增强导电性能或改变器件结构。

扩散过程的主要步骤扩散过程是一个涉及多个步骤的复杂过程,主要包括以下几个步骤:清洗在扩散之前,半导体晶体需要进行清洗,以去除表面的污染物和杂质,保证扩散过程的准确性和稳定性。

清洗步骤可以使用化学清洗方法或物理清洗方法,如溶剂洗涤、超声波清洗等。

预处理预处理步骤是为了提高扩散效果和降低生产成本而进行的一系列处理。

包括表面氧化、蚀刻、离子注入等工艺,以提高扩散层的质量和一致性。

掺杂掺杂是扩散过程中的核心步骤,通过向半导体晶体中注入外部杂质,改变材料的导电性能。

掺杂过程中需要控制掺杂浓度和深度,以满足器件设计要求。

IC制造工艺-掺杂

热扩散掺杂

填隙扩散

• 填隙扩散时,填隙硅原子取代了 替位杂质原子的位置,将杂质原 子推到填隙位置

热扩散掺杂

• 杂质原子可能被空位俘获,成为填隙 杂质。这种机制称为Frank-Turnbull机 制

• 杂质原子也可能取代原晶格位置中的 硅原子。这种机制称为挤出机制

• 通过测量霍尔电压,可以直接测量出 总的载流子浓度

• 霍尔效应可以同时测量载流子类型、 迁移率和薄层浓度

热扩散掺杂

扩展电阻分布测量

• 将样品打磨出斜角 • 通过探针测量不同深度的

接触电阻 • 和一个电阻——浓度校准

标准值进行比较,就可得 到载流子分布曲线

热扩散掺杂

二次离子质谱法(SIMS)

• 样品中的杂质将氦离子背散 射出来

• 背散射氦离子带有的能量取 决于杂质的质量和杂质在晶 体中的深度

• 背散射出来的氦离子被收集 并进行能量分析,可以确定 圆片内化学组分在深度方向 的分布情况

热扩散掺杂

• 和RBS分析法相比,SIMS分析法精度高,但所需花费的时间和成 本也高。测量厚度超过1um的样品可能要花费4~8小时时间

• SIMS对百万分之一的杂质 浓度敏感

• Wafer放入装置,并将系统 抽到高真空状态

• 用一束离子束照射样品 • 高能离子撞击样品表面并

破坏表面晶格结构,将材 料溅射出来 • 用质谱仪收集并分析杂质 含量,便可找散射法(RBS)

• 用氦离子以接近法线的方向 入射到样品上

离子注入

离子注入的问题

• 注入倾斜角使得源/漏区不能 与沟道区相连

离子注入

离子注入的问题

• 在简单静电扫描系统中,遮挡 问题显得更加严重

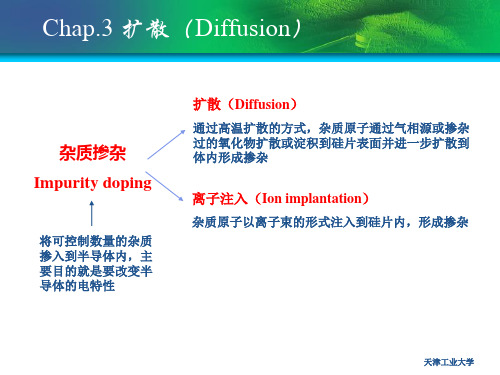

硅集成电路工艺——扩散(Diffusion)

天津工业大学

§3.1 杂质扩散机构(机理,机制)

间隙式扩散: 间隙式扩散:

间隙式杂质从一个间隙位置运动 到另一个间隙位置 间隙位置: 间隙位置: 势能min 势能 相邻两间隙位置: 势能 相邻两间隙位置: 势能max 势垒高度: 势垒高度:Wi=0.6~1.2 eV 主要与晶格结构与晶向有关, 主要与晶格结构与晶向有关,原 子 密度越大,间隙越小, 密度越大,间隙越小, Wi就越大 就越大 运动条件: 运动条件:E> Wi 跳跃率: 跳跃率:Pi=V0 exp(-Wi/kT)

天津工业大学

两步扩散

两步扩散(控制表面浓度,杂质数量,结深等指标) 两步扩散(控制表面浓度,杂质数量,结深等指标)

预扩散(预淀积) 预扩散(预淀积) (predeposition)

主扩散(再分布) 主扩散(再分布) (drive-in)

天津工业大学

§3.4 影响杂质分布的其他因素

硅中点缺陷 杂质浓度对扩散系数的影响 氧化增强扩散 发射区推进效应 二维扩散 电场效应 热氧化过程中的杂质再分布 硅片晶向的影响

天津工业大学

§3.2 扩散系数与扩散方程

菲克(Fick)第一定律: 第一定律: 菲克 第一定律 J= -D[əC(x,t)/ əx]

杂质的扩散流密度正比于 杂质浓度梯度, 杂质浓度梯度,比例系数 D定义位杂质在基体中的 定义位杂质在基体中的 扩散系数

扩散系数: 扩散系数: J(x,t)=C(x-a/2,t)PvaC(x+a/2,t)Pva D=a²Pv =a²v0exp[-(Ws+Wv)/kT] =D0exp(-∆E/kT)

Chap.3 扩散(Diffusion)

扩散( 扩散(Diffusion) )

扩散工艺-半导体制造

扩散工艺前言:扩散部按车间划分主要由扩散区域及注入区域组成,其中扩散区域又分扩散老区和扩散新区。

扩散区域按工艺分,主要有热氧化、扩散、LPCVD、合金、清洗、沾污测试等六大工艺。

本文主要介绍热氧化、扩散及合金工艺。

目录第一章:扩散区域设备简介……………………………………第二章:氧化工艺第三章:扩散工艺第四章:合金工艺第一章:扩散部扩散区域工艺设备简介炉管设备外观:扩散区域的工艺、设备主要可以分为:类别主要包括按工艺分类热氧化一氧、二痒、场氧、Post氧化扩散推阱、退火/磷掺杂LPCVD TEOS、SI3N4、POL Y清洗进炉前清洗、漂洗合金合金按设备分类卧式炉A、B、C、D、F、H、I六台立式炉VTR-1、VTR-2、VTR-3 清洗机FSI-1、FSI-2炉管:负责高温作业,可分为以下几个部分:组成部分功能控制柜→对设备的运行进行统一控制;装舟台:→园片放置的区域,由控制柜控制运行炉体:→对园片进行高温作业的区域,由控制柜控制升降温源柜:→供应源、气的区域,由控制柜控制气体阀门的开关。

FSI:负责炉前清洗。

第二章:热氧化工艺热氧化法是在高温下(900℃-1200℃)使硅片表面形成二氧化硅膜的方法。

热氧化的目的是在硅片上制作出一定质量要求的二氧化硅膜,对硅片或器件起保护、钝化、绝缘、缓冲介质等作用。

硅片氧化前的清洗、热氧化的环境及过程是制备高质量二氧化硅膜的重要环节。

2. 1氧化层的作用2.1.1用于杂质选择扩散的掩蔽膜常用杂质(硼,磷,砷等)在氧化层中的扩散系数远小于在硅中的扩散系数,因此氧化层具有阻挡杂质向半导体中扩散的能力。

利用这一性质,在硅上的二氧化硅层上刻出选择扩散窗口,则在窗口区就可以向硅中扩散杂质,其它区域被二氧化硅屏蔽,没有杂质进入,实现对硅的选择性扩散。

1960年二氧化硅就已被用作晶体管选择扩散的掩蔽膜,从而导致了硅平面工艺的诞生,开创了半导体制造技术的新阶段。

同时二氧化硅也可在注入工艺中,作为选择注入的掩蔽膜。

扩散PPT

集成电路工艺原理

第八讲 扩散原理 2

1

第一讲 第二讲 第三讲 第四讲 第五讲 第六讲 第七讲 第八讲

前言 实验室净化及硅片清洗 光刻原理 1 光刻原理 2 热氧化原理 1 热氧化原理 2 扩散原理 1 扩散原理 2

第九讲 第十讲 第十一讲 第十二讲 第十三讲 第十四讲 第十五讲 第十六讲 第十七讲

集成电路工艺原理

第八讲 扩散原理 2

18

1 )OED:对于原子B或P来说,其在硅中的扩散可以 通过间隙硅原子进行。氧化时由于体积膨胀,造成大 量Si间隙原子注入,增加了B和P的扩散系数。

(1+2)Si+2OI+2V↔SiO2+2I+stress

A+I AI

372.065.1.01

集成电路工艺原理

影响杂质分布的其他因素

3

Fick’s Laws: Only valid for diffusion under special conditions Simplification !

372.065.1.01

集成电路工艺原理

第八讲 扩散原理 2 1、电场效应(Field effect)——非本征扩散

电场的产生:由于载流子 的迁移率高于杂质离子, 二者之间形成内建电场。 载流子领先于杂质离子, 直到内建电场的漂移流与 扩散流达到动态平衡。

4

372.065.1.01

集成电路工艺原理

第八讲 扩散原理 2

所以,杂质流由两部分组成:

5

Ftotal Fdiffusion Fdrift

C D EC x

372.065.1.01

集成电路工艺原理

第八讲 扩散原理 2

2)非本征掺杂

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

– 有氧时应是什么情况?

在氧气氛中再分布时: 1)边界向内移动, 2)杂质在界面分凝。

P型杂质的耗尽和N型杂质的堆积效应(Pile-up)

3)界面空位对扩散系数的影响(p47~48)

预淀积和再分布工艺步骤小结

掺杂工艺与参数变化小结

– 2.2. 实际工艺中的扩散源、扩散方法和应用 – 2.2.1. 杂质源(p60~61)

– 4)完整的工艺流程图

– 5)杂质源、扩散方式和设备。(固态源=固相扩散?) – 6)扩散结果的测试的主要物理内容、方法和方法的特

点。

– 7)扩散质量对PN Junction的I~V特性的影响。 – 8)为什么有些IC工艺书不介绍扩散工艺?

– NPN中磷扩散时的发射区下陷

– 氧化和分凝对结深的影响

– 2.4.2. 方块电阻RS

(p52~53)

RS

l lxj

xj

• 一般有: qN

由于扩散层的杂质分布不均匀,因此:

1

xj

qN (x)dx

xj 0

q

xj

N (x)dx

q

Q

xj 0

xj

Q为扩入的杂质总量

–

所以:

RS

1

– 测量:四探针法

• 3)恒定表面源扩散时的CS由什么决定?

– 3)高杂质浓度及空位性缺陷的场助增强扩 散作用(?) 可以有:Deff=2D,(N>>ni)

– 2.1. 4. PN结制造中的扩散工艺(p.44-45)

– 1)目标:有确定的表面浓度CS,有确定的杂 质总量Q,有确定的结深xj。

– 2)常规工艺:先在恒定表面源的情况下扩散 一短时间t1,使其在近表面处有一杂质总量 为Q1的高浓度薄层,这一过程通常在氮气氛 中进行,并被称为“预沉积扩散” (predeposition);再在除去外部杂质源的情况 下,在温度稍高的条件下使总量为Q1的杂质 继续向内扩散,进行杂质的“再分

4PCl5 5O2 2P2O5 10Cl2

PCl5对Si有 腐蚀作用

– 2.2.3. 固态源 – 1) B源: BN

4BN 3O2 2B2O3 N2 2B2O3 3Si 3SiO2 4B

与液态源不一样 的是B2O3生在 BN上。

– 2)P源:P2O5 液态源和固态源都是汽—固扩散

– 1)杂质扩散有多种机制,有时会是几种机制共存。即 使对于同一种杂质和衬底材料,扩散机制也可能受温度 (?)、杂质浓度(?) 、外界气氛(?)等因素的影

响。

Ea

D D0e kT Deff

– 2)扩散工艺的目标:确定的表面浓度?、结深?和分 布?

– 3)两种扩散方法(Pre-deposition和Drive-in)的特点; 实验控制原理;通常的实际工艺情况(氧、增强扩散、 横向扩散)和对结果的影响;

• 先在硅表面淀积一层掺杂“SiO2“作为杂质源

2)氧化硅涂源扩散 3)纸片源

– 2.3. Diffusion in SiO2 1)扩散系数

2)作为选择性扩散的掩蔽膜

N SiO2 (dox,min ) / N sub 1/1000

– 2.4. 扩散层的质量分析与检测

• 陪片评估!

– 2.4.1 . 结深xj

RS

1

xj

q N(x)dx

0

方块电阻不变化

RS、NS、xj三者是相 关的,与分布有关。

– 实际工艺中对RS、NS、xj的调控原理?

– 测量: 1)单探针:

Rsp = 4r (ohms)

Probes

Rsp

Direction of measurements

t

Beveled surface

r

P B

Wafer handler controller

Temperature controller

Three-zone heater

Heater 1

Heater 2

Heater 3

Microcontroller

Quartz process chamber Gas

panel

Gas flow controller

RS

CV I

C为与样品长度、宽度、厚度、探针间距有 关的修正常数。

Four Point Probe

s =

V I

x 2s (ohms-cm)

Constant current source

I

R

Voltmeter V

Wafer

Figure 7.3

– 2.4.3. 杂质分布N(x)与表面杂质分布NS

方块电阻变化

局域掺杂和热处理技术 (p。37)

第二章:扩散掺杂技术 第三章:热氧化技术 第四章:离子注入技术 第五章:快速热处理技术

第二章:扩散掺杂技术

P B

• 基本内容! • 1) 杂质在材料中的扩散机制,和影响扩

散系数的几种因数。

• 2)常见的几种施主和受主杂质以及一些 金属杂质在Si中的扩散。

• 3)扩散源和扩散系统。 • 4)实际的扩散工艺。 • 5)扩散工艺的质量检控和分析。

– 2.4.4. 扩散工艺对PN结击穿电压的影响 1)软击穿: 结边缘沾污“并联电阻”漏电 2)“靠背椅”击穿:表面沟道漏电 3)分段击穿:局部穿通 4)低压(硬)击穿:大面积穿通 5)二次击穿:热击穿

– 2.4.5. 横向扩散

– 2.4.6. 应用实例

1)硼预扩散

Si (111)

条件:T=950°C;t=25min;

x 由质量守恒,得 C J ,

t x

因而,

Cx,

t

t

D

2Cx,

x 2

t

Fick’s Second Law

– 2)两种边界条件

– a)恒定表面源浓度

即:C0,t CS C,t 0

可得:

一余误差分布。

C

x,

t

CS

erfc

2

其杂质总量为:

Q

x

Dt

C

0

x,

t

dx

0

CS

erf

c

2

x Dt

dx

布”(drive-in),这一过程通常在氧气氛中进

行。

(可否不用氧?实际工艺中还要复杂!)

预扩散时的表面浓 度由固溶度决定!

– 3)再分布后的杂质总量、分布和结深 在无氧气氛时,

Q1 2CS1

D1t1

CS2

Q2

D2t2

Q1 2CS1

D2t2

D1t1 D2t2

由于预沉积时间短且温度低,可以认为有 xj1<<xj2,因而,C(x,t)仍为高斯分布。

2) C-V法: (p55)

1 C(V )2

2(V Vbi )

A2 qN sub

Nsub (z)

8(V Vbi

A2q

)3

dC( z) dV(V Vbi ) C 2 A2qNsub

3)SIMS:(Secondary Ion Mass Spectroscopy)

• 考题:

• 1)设计一个实验来测定某杂质在硅中的 扩散率和扩散激活能。

• 2)在一1100°C的硼扩散工艺中,要求 结深为1m,其误差不超过2%。问:1) 若保证温度精确控制下,扩散时间的误 差应低于多少?2)若保证时间精确控制 下,扩散温度的误差应低于多少?(取 A=5,D0= 0.76cm2/s,E0= 3. 46eV)

Si双极npn晶体管芯片的工艺流程

1、衬底制备,2、外延生长,

3、一次氧化,4、一次光刻,

5、基区扩散,6、二次氧化,

7、二次光刻,8、发射区扩散, n+

E

B

9、三次氧化,10、三次光刻, p

11、金属镀膜,12、反刻金属膜 n

13、背面镀膜,14、合金化 n+

C

Wafer fabrication (front-end)

x j A Dt A 2erf 1(1 NB )

NS A 2(ln NS )1/ 2

NB

– 结论:影响结深的主要因素是温度

– 结深的测量: 1)单探针(扩展电阻): 2)染色法: (p53~54) 如:CuSO4•5H2O:48%HF 光照下n区染上铜

– 工艺中的累积高温过程的扩散 Dt(最终)= Diti

2CS

Dt

– b)恒定杂质总量 Q 即:

Cx,tdx Q

0

Cx,0 0

C,t 0

d0,t 0

dx

– 可得: Cx,t

Q

Dt

exp

x2 4Dt

为一高斯分布;其表面浓度为:

CS C0,t

Q

Dt

– 3)结深xj 在PN结的扩散中,衬底材料中已有导电性 相反的杂质,其浓度为Csub。定义导电性转

– 3)其它扩散机制 a)直接交换 b)Kick-out机制 (page 45,

Kick-out机制的 扩散速率一般超 过替位式扩散 如:Ni等。

• 扩散系数的普遍表达式:

通常高阶电荷态的几率很小可以忽略 (P.43、44;Table:3.2, Example: 3.1) • 而某一种扩散系数可以表达为:

固溶度和扩散系数也是 在工艺中对杂质选择时 应考虑的因素

– 2.2.2. 液态源 – 1) B源: (如:硼酸三甲脂)

B(CH3O)3 B2O3 CO2 C H2O 2B2O3 3Si 3SiO2 4B

– 2) P源: (三氯氧磷POCl3)(POCl)

5POCl3 3PCl5 P2O5 2P2O5 5Si 5SiO2 4P

Q

0

N

x,

t

dx