共模电感的设计

共模电感 参数

共模电感参数

共模电感参数对于电路设计和电磁兼容性至关重要。

共模电感是一种用于抑制共模干扰的元件,它能够有效地降低电路中的共模噪声,提高系统的抗干扰能力。

在设计共模电感参数时,需要考虑电感值、频率特性、尺寸、材料等因素,以确保其在电路中的有效性和稳定性。

共模电感的电感值是一个关键参数。

电感值的选择应根据具体的电路设计需求来确定。

一般来说,较大的电感值可以提供更好的共模抑制效果,但也会增加电路的成本和尺寸。

因此,在实际设计中需要权衡各方面的因素,选择适当的电感值。

共模电感的频率特性也是需要考虑的重要参数。

不同频率下,共模电感的阻抗特性会有所不同,因此需要根据工作频率来选择合适的共模电感。

一般来说,共模电感在高频下的阻抗应该较低,以确保其在高频环境下能够有效地抑制共模干扰。

共模电感的尺寸和材料也会影响其性能。

尺寸较大的共模电感通常具有较高的电感值和较低的电阻,但也会增加电路的体积和重量。

而选择合适的材料可以提高共模电感的工作稳定性和抗干扰能力,同时也可以降低电路的损耗和热量。

总的来说,共模电感参数的选择需要综合考虑电路设计需求、工作频率、成本和体积等因素。

合理选择共模电感的参数可以有效提高

系统的抗干扰能力,保障电路的稳定性和可靠性。

在实际应用中,设计人员应该根据具体情况进行调整和优化,以获得最佳的性能表现。

共模电感作为电磁兼容性设计中的重要元件,将继续发挥着重要的作用,帮助电路系统实现更好的抗干扰能力和稳定性。

multisim中共模电感

multisim中共模电感Multisim是一款功能强大的电子仿真软件,它可以模拟各种电路设计。

其中的共模电感被广泛应用于各种电子设备中。

本文将介绍共模电感在Multisim中的应用。

一、共模电感的定义共模电感指的是,两个线圈的磁性耦合,使它们以某种方式联系在一起的电感器件。

共模电感是代替传统的两个不同的电感器件的,能够将其功能集成到一个组件中。

这样做能够节省空间并减少成本。

共模电感中,一个线圈是传播被耦合的信号的主导元件,而另外一个线圈则是用来作为整个装置中共模信号的引线。

二、共模电感的使用及原理1、电磁学原理共模电感是由两个线圈通过磁性耦合形成的一个部件。

其一个线圈称为主要线圈,而另一个称为副次线圈。

主要线圈与电路的部件连接,副次线圈则耦合到另一个线路中。

当主要线圈中的电流发生变化时,它会产生一个变化磁场。

然后,这个变化磁场进一步耦合到副次线圈中,并且它也会产生一个电动势,改变副线圈的电流。

这种现象称为互感,表示为Lm。

它可以通过下面的公式来计算:$ L_m=M \times \sqrt{L_1 \times L_2}$其中L1和L2是主线圈和副次线圈的电感,而M是它们之间的系数。

2、电路上的共模电感共模电感器件在电路上的作用是,可以用来阻止共模干扰。

共模干扰指的是,要度过一条电缆上传达的信号,才能传达另一条电缆。

共模电感通过对这个信号的有效地隔离,来解决这个问题。

例如,共模电感器件常常被应用于地线的设计中。

它们可以用于电缆和电子元件之间的通信,以防止在通讯过程中出现共模干扰。

共模电感器件还可以在设计中避免电流环路过大,同时也可以阻止共模电流的流动,从而防止干扰另一个回路。

三、Multisim中共模电感的应用在Multisim中,使用共模电感器件的步骤如下:1、打开Multisim软件,在底部工具栏中选择元器件库。

2、在元器件库中,找到“Inductor_Mutual”元器件,并将其拖动到电路工作区中。

共模电感设计共模电感设计方案共模电感设计案例

共模电感设计共模电感设计方案共模电感设计案例共模电感设计是指在电路中采用共模电感来抑制共模噪声、提高信号品质和抗干扰能力的一种方法。

共模电感是一种特殊的电感元件,它在电路中起到滤波、隔离和阻抗匹配的作用。

本文将介绍几种常见的共模电感设计方案,并给出一些实际的共模电感设计案例。

1.单线圈共模电感设计方案:单线圈共模电感是一种简单的共模滤波器,它由一根绕线构成。

该共模电感一端接地,另一端与共模信号相连接。

单线圈共模电感的阻抗主要与其电感值和频率有关。

在设计时,可以选择合适的电感值和线圈长度,使其产生滤波效果,抑制共模噪声。

2.磁组件共模电感设计方案:磁组件共模电感由多个线圈和铁芯组成。

铁芯的存在可以增加线圈的感应效果,提高共模电感的阻抗。

在设计时,可以根据需要选择合适的铁芯材料、线圈匝数和电感值,以满足共模滤波的需求。

3.三相共模电感设计方案:三相共模电感适用于三相电路中的共模抑制。

三相电路中,共模电感一般由三个线圈组成,每个线圈对应一个相位。

通过适当的线圈匝数和电感值的选择,可以实现对三相共模信号的滤波和抑制。

案例1:手机通信模块共模电感设计手机通信模块中,常常存在大量的共模噪声。

为了提高通信质量,需要设计合适的共模电感来滤除这些噪声。

设计方案:采用单线圈共模电感,电感值选择5μH,线圈匝数为100匝。

根据手机通信频率范围,选择合适的线径和绕线长度。

通过电磁场仿真和实际测试,验证共模电感的滤波效果,得到满意的结果。

案例2:工业控制系统中的共模电感设计工业控制系统中,电机和传感器的共模噪声较大,容易影响系统的稳定性和准确度。

为了解决这个问题,需要设计合适的共模电感。

设计方案:采用磁组件共模电感,由多个线圈和铁芯组成。

根据系统要求和噪声特点,选择合适的铁芯材料和线圈匝数。

通过电磁场仿真和实际测试,得到满意的共模滤波效果。

共模电感

共模电感(Common mode Choke),也叫共模扼流圈,常用于电脑的开关电源中过滤共模的电磁干扰信号。

在板卡设计中,共模电感也是起EMI滤波的作用,用于抑制高速信号线产生的电磁波向外辐射发射。

目录导线)为例,所谓串模干扰,指的是两条走线之间的干扰;而共模干扰则是两条走线和PCB地线之间的电位差引起的干扰。

串模干扰电流作用于两条信号线间,其传导方向与波形和信号电流一致;共模干扰电流作用在信号线路和地线之间,干扰电流在两条信号线上各流过二分之一且同向,并以地线为公共回路.共模电感如果板卡产生的共模电流不经过衰减过滤(尤其是像USB和IEEE 1394接口这种高速接口走线上的共模电流),那么共模干扰电流就很容易通过接口数据线产生电磁辐射——在线缆中因共模电流而产生的共模辐射。

美国FCC、国际无线电干扰特别委员会的CISPR22以及我国的GB9254等标准规范等都对信息技术设备通信端口的共模传导干扰和辐射发射有相关的限制要求。

为了消除信号线上输入的干扰信号及感应的各种干扰,我们必须合理安排滤波电路来过滤共模和串模的干扰,共模电感就是滤波电路中的一个组成部分。

共模电感实质上是一个双向滤波器:一方面要滤除信号线上共模电磁干扰,另一方面又要抑制本身不向外发出电磁干扰,避免影响同一电磁环境下其他电子设备的正常工作。

图2是我们常见的共模电感的内部电路示意图,在实际电路设计中,还可以采用多级共模电路来更好地滤除电磁干扰。

此外,在主板上我们也能看到一种贴片式的共模电感(图3),其结构和功能与直立式共模电感几乎是一样的。

编辑本段共模电感工作原理为什么共模电感能防EMI?要弄清楚这点,我们需要从共模电感的结构开始分析。

共模电感的滤波电路,La和Lb就是共模电感线圈。

这两个线圈绕在同一铁芯上,匝数和相位都相同(绕制反向)。

这样,当电路中的正常电流流经共模电感时,电流在同相位绕制的电感线圈中产生反向的磁场而相互抵消,此时正常信号电流主要受线圈电阻的影响(和少量因漏感造成的阻尼);当有共模电图2 图3流流经线圈时,由于共模电流的同向性,会在线圈内产生同向的磁场而增大线圈的感抗,使线圈表现为高阻抗,产生较强的阻尼效果,以此衰减共模电流,达到滤波的目的。

pcb 共模电感走线

pcb 共模电感走线

PCB共模电感走线是指在PCB设计中,针对共模电感的走线布局。

共模电感是一种用于抑制共模干扰的元件,它通常用于电路中

的滤波器和抑制噪声。

在PCB设计中,正确的走线布局对于共模电

感的性能和整个电路的稳定性至关重要。

首先,对于共模电感的走线布局,需要考虑电感的位置和连接。

在PCB布局中,应尽量将共模电感与其他信号线隔离,以减少干扰。

同时,共模电感的两个端子应尽量靠近需要进行共模抑制的信号源

和接收器,以最大程度地提高抑制效果。

其次,需要考虑走线的长度和走线方式。

对于共模电感的走线,应尽量缩短走线长度,减少走线的环路面积,以减小共模电感的感

受面积,从而减少干扰。

此外,采用宽一些的走线,可以降低走线

的电阻和电感,有利于减小共模电感对信号的影响。

此外,还需要考虑共模电感与其他元件的布局关系。

在PCB设

计中,应尽量避免共模电感与高频元件或其他可能产生干扰的元件

靠得太近,以免相互影响,影响整个电路的性能。

最后,对于共模电感的走线布局,还需要考虑接地。

良好的接地设计可以有效减少共模电感的干扰,因此在PCB设计中,应合理规划接地,确保共模电感的接地连接良好,减少共模干扰的影响。

综上所述,对于PCB共模电感的走线布局,需要考虑电感位置和连接、走线长度和方式、与其他元件的布局关系以及接地设计等多个方面,以确保共模电感的性能和整个电路的稳定性。

共模电感设计计算

共模电感设计计算

共模电感是一种用于电路中抑制共模干扰的元件。

在设计共模电感时,我们需要考虑电路的工作频率、信号大小和所需的共模抑制能力。

首先,确定工作频率。

工作频率是指电路中信号的频率,通常以赫兹(Hz)为单位。

在设计共模电感时,需要知道电路中的信号频率,以便选择合适的电感值。

其次,确定信号大小。

信号大小是指电路中的共模信号的幅值。

在设计共模电感时,需要知道共模信号的最大值,以便选择合适的电感值来实现所需的共模抑制能力。

然后,计算所需的共模电感值。

共模电感的值通常以亨利(H)为单位。

可以使用以下公式来计算所需的共模电感值:

L = Vcm / (2πfIm)

其中,L是所需的共模电感值,Vcm是共模信号的幅值,f是工作频率,Im是电路中的最大共模电流。

最后,选择合适的共模电感。

根据计算所得的共模电感值,选择最接

近的标准电感值来实现所需的共模抑制能力。

在选择电感时,还需考虑电感的最大电流承受能力和尺寸限制。

总结起来,设计共模电感需要确定工作频率和信号大小,然后使用公式计算所需的共模电感值,并选择合适的标准电感来实现所需的共模抑制能力。

共模电感的设计

共模电感的设计共模电感设计就是对共模电感的性能有着决定性的作用,共模电感设计的具体方法是怎样的?下面为你详细讲解共模电感设计。

在了解共模电感设计前,我们先来认识一下共模电感。

共模电感(Common mode Choke),也叫共模扼流圈,常用于电脑的开关电源中过滤共模的电磁干扰信号。

在板卡设计中,共模电感也是起EMI滤波的作用,用于抑制高速信号线产生的电磁波向外辐射发射。

共模电感设计,磁芯选材是最开始也是最重要的一步。

对于大多数产品来讲,共模电感的磁芯都选用铁氧体(镍锌系和锰锌系)。

锰锌系磁芯有很多种形状:环形,E形,罐形,RM形及EP形等等。

但对于大多数共模电感都是使用环形磁芯。

主要是有以下两种好处:第一:环形磁芯比较便宜。

因为环形只有一个就可制作,而其他形状的磁芯必须有一对才能构成共模电感所需,且在成型时,因考虑两磁芯的配对问题,还须增加研磨工序(如镜面磁芯)才能得到较高的磁导率。

对于环形磁芯却不需如此。

第二:与其它形状磁芯相比环形磁芯有较高的有效磁导率。

因为两配对磁芯在装配时,无论怎样作业都不可消除气隙的现象,故有效磁导率比只有单一封闭形磁芯要低。

环形磁芯有一缺点:绕线成本较高。

因其他形状磁芯有一配套线架在使用,绕线都可以机器作业,而环形磁芯只可以手工作业或机器(速度较低)作业。

但通常情况下,共模电感圈数较少(小于30圈),故绕线成本比较少。

共模电感设计考虑的基本参数:共模电感设计所需的基本参数为:输入电流,阻抗及频率。

输入电流决定了绕组所需的线径。

在计算线径时,电流密度通常取值为400A/cm3。

但此取值须随电感温升的变化。

通常情况下,绕组使用单根导线作业,这样可削减高频噪声及趋肤效应损失。

电感大家都知道,但值得一提的是,设计时须注意磁芯,磁芯材质及所需的圈数。

首先,设计第一步是磁芯型号的选取,如果有规定电感空间,我们就按此空间来选取合适的磁芯型号,如没有规定,通常磁芯型号的随意选取;第二步是计算磁芯所能绕最大圈数。

共模电感的工作原理与设计

共模电感的工作原理与设计共模电感是电感的一种特殊形式,它具有类似于普通电感的电感性质,同时还能阻止共模信号通过。

共模电感在电子电路中起到抑制共模噪声的作用,提高信号质量。

1.电磁感应:当通过共模电感的两个导线中流过的电流方向相同时(即共模模式),会形成一个磁场。

这个磁场会导致导线中的电流方向相同,产生感应电动势。

2.感应电动势:感应电动势产生的目的是阻碍共模信号通过,从而抑制共模噪声。

共模电感的设计初衷是使产生的感应电动势尽可能大,从而能有效地阻止共模信号通过。

3.互感:共模电感的两个线圈之间会产生一定的互感,通过调整线圈的匝数、形状和位置等参数,可以改变共模电感的特性。

设计共模电感时,需要考虑以下几个因素:1.线圈的材料和大小:线圈的大小和材料会影响共模电感的特性。

线圈的材料一般选用导磁性能较好的材料,如铁氧体等。

线圈的大小一般根据电路的需求确定,过小会影响共模电感的效果,过大则会增加电路的体积和成本。

2.匝数:线圈的匝数也是影响共模电感的重要因素。

匝数的多少会影响感应电动势的大小。

一般来说,匝数越多,感应电动势越大,共模信号的抑制效果越好。

3.线圈的构造:线圈的形状和结构也会影响共模电感的效果。

合理的线圈结构能提高共模电感的工作效率和性能。

一般常用的线圈结构有圆柱形、长方形等。

4.线圈的位置:线圈的位置也会影响共模电感的效果。

位置的选择应该根据具体的电路需求来确定,一般来说,距离电源或信号源较近的位置可以增加共模电感的效果。

综上所述,共模电感通过电磁感应的原理,产生感应电动势阻止共模信号通过,从而提高信号质量。

设计共模电感时需要考虑线圈的材料、大小、匝数、构造和位置等因素,以达到最佳的抑制共模噪声的效果。

emc 共模电感参数选取

emc 共模电感参数选取在电磁兼容(EMC)设计中,共模电感的参数选择非常重要。

共模电感是一种在共模信号传输中用来抑制干扰的被动元件。

选择合适的共模电感参数能够有效提高系统的EMC性能,降低电磁辐射和敏感性。

首先,选取合适的电感值是至关重要的。

电感值的选择应该基于系统的特性和所需的抑制效果。

一般来说,较大的电感值可以提供更好的共模抑制。

然而,过大的电感值可能会引入额外的损耗和不必要的成本。

因此,在选择电感值时需要综合考虑多种因素,包括系统的频率范围、信号的幅度和带宽等。

其次,电感的电流饱和值也是一个需要考虑的参数。

共模电感在使用过程中会承受一定的电流,如果电流超过了电感的饱和电流,电感的性能可能会发生变化,导致共模抑制效果下降。

因此,在选择共模电感时,需要确保其饱和电流大于系统中的最大共模电流。

此外,电感的串联电阻也是一个需要考虑的因素。

串联电阻会产生额外的电压降,在一些要求电压幅度较小的系统中,这可能会对信号传输造成一定的干扰。

因此,在选择共模电感时,应当尽量选择串联电阻较小的型号。

最后,选择合适的封装方式也是非常重要的。

共模电感常见的封装方式有SMD贴片和插件式等。

在选择封装方式时,需要考虑到系统的布局和尺寸限制。

SMD贴片方式封装可以节省空间和提高布局灵活性,但对于一些高功率应用,插件式封装可能更为适合,因为它可以提供更好的散热性能。

综上所述,共模电感的参数选取对于系统的EMC性能至关重要。

在实际设计中,应综合考虑电感值、电流饱和值、串联电阻以及封装方式等因素,选取合适的共模电感,以提高系统的抗干扰能力,保证系统的可靠性和稳定性。

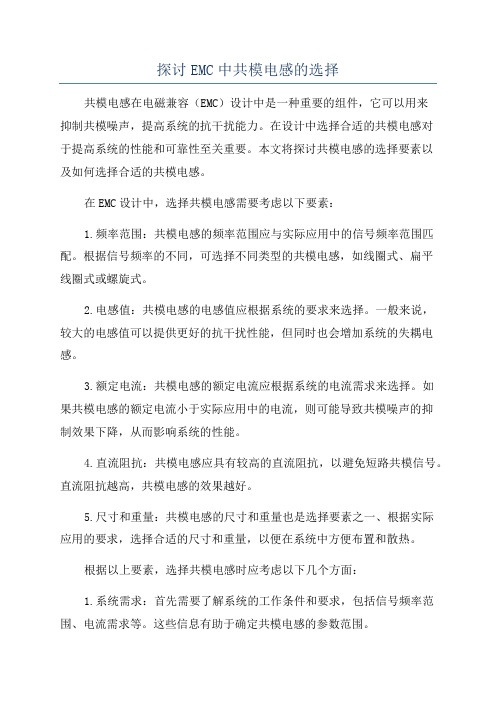

探讨EMC中共模电感的选择

探讨EMC中共模电感的选择共模电感在电磁兼容(EMC)设计中是一种重要的组件,它可以用来抑制共模噪声,提高系统的抗干扰能力。

在设计中选择合适的共模电感对于提高系统的性能和可靠性至关重要。

本文将探讨共模电感的选择要素以及如何选择合适的共模电感。

在EMC设计中,选择共模电感需要考虑以下要素:1.频率范围:共模电感的频率范围应与实际应用中的信号频率范围匹配。

根据信号频率的不同,可选择不同类型的共模电感,如线圈式、扁平线圈式或螺旋式。

2.电感值:共模电感的电感值应根据系统的要求来选择。

一般来说,较大的电感值可以提供更好的抗干扰性能,但同时也会增加系统的失耦电感。

3.额定电流:共模电感的额定电流应根据系统的电流需求来选择。

如果共模电感的额定电流小于实际应用中的电流,则可能导致共模噪声的抑制效果下降,从而影响系统的性能。

4.直流阻抗:共模电感应具有较高的直流阻抗,以避免短路共模信号。

直流阻抗越高,共模电感的效果越好。

5.尺寸和重量:共模电感的尺寸和重量也是选择要素之一、根据实际应用的要求,选择合适的尺寸和重量,以便在系统中方便布置和散热。

根据以上要素,选择共模电感时应考虑以下几个方面:1.系统需求:首先需要了解系统的工作条件和要求,包括信号频率范围、电流需求等。

这些信息有助于确定共模电感的参数范围。

2.厂家性能数据:对不同品牌和型号的共模电感进行调查和对比,了解它们的性能数据,如额定电流、电感值、直流阻抗等。

这些数据可用于筛选出符合系统要求的共模电感。

3.仿真和实验验证:根据系统要求,可以使用电磁场仿真软件进行电磁兼容分析,评估不同共模电感的抗干扰性能。

同时,还可以进行实验验证,对比不同共模电感的效果,选择最佳的共模电感。

4.成本和可靠性:在选择共模电感时,还需要考虑成本和可靠性。

成本包括购买成本和系统维护成本,可靠性包括共模电感的寿命和可靠性指标。

总之,选择合适的共模电感是EMC设计中很关键的一步。

需要根据系统要求和性能数据,结合仿真和实验验证,综合考虑成本和可靠性等因素,选择最佳的共模电感。

非常详细的共模电感及滤波器的设计!(转载)

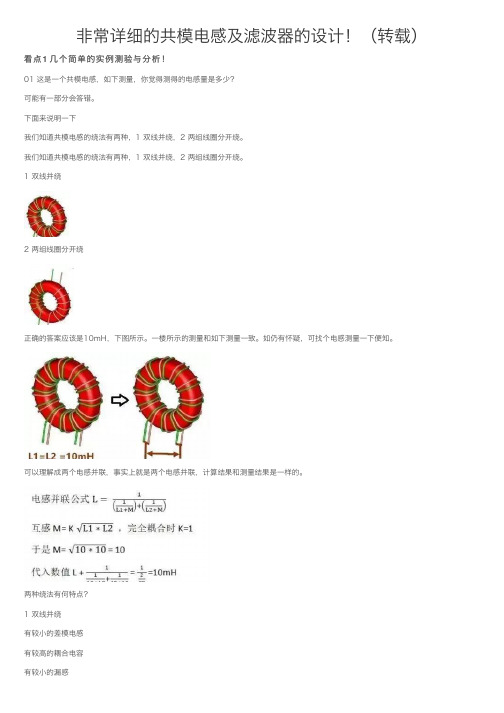

⾮常详细的共模电感及滤波器的设计!(转载)看点1 ⼏个简单的实例测验与分析!01 这是⼀个共模电感,如下测量,你觉得测得的电感量是多少?可能有⼀部分会答错。

下⾯来说明⼀下我们知道共模电感的绕法有两种,1 双线并绕,2 两组线圈分开绕。

我们知道共模电感的绕法有两种,1 双线并绕,2 两组线圈分开绕。

1 双线并绕2 两组线圈分开绕正确的答案应该是10mH,下图所⽰。

⼀楼所⽰的测量和如下测量⼀致。

如仍有怀疑,可找个电感测量⼀下便知。

可以理解成两个电感并联,事实上就是两个电感并联,计算结果和测量结果是⼀样的。

两种绕法有何特点?1 双线并绕有较⼩的差模电感有较⾼的耦合电容有较⼩的漏感2 两组线圈分开绕有较⼩的耦合电容有较⾼的漏感因此要根据实际应⽤情况选择绕法。

02 再看看这样测量出来的电感量是多少?为什么?有的⼈可能会回答0mH,有的⼈可能会回答20mH,有的⼈可能会回答10mH。

不过很遗憾都不是,正确的答案L=40mH。

如下图,按右⼿法则已标上电流⽅向和磁通⽅向,从图中可以看出两个线圈的磁通的⽅向是相同的,也就是说磁通是增加的不是相互抵消。

根据磁环电感量计算公式式中:N = 圈数, Ac = 截⾯积, 分母 Mpl = 磁路长度。

注意 N 有平⽅的,⼀组线圈的圈数是N, 则两组线圈的圈数是 2N,将2N代⼊到公式中分⼦有 4N2, 也就是说电感量为 4 倍。

本例则为40 mH。

03 再看看这样测量得到的电感量应该是多少?这样测得的是什么电感量?这个估计很多⼈都知道是0mH,没错,理想状态下就是 0mH。

实际共模电感总有漏感、或差模电感成份,因此按此连接测量得到的数值就是漏感或者叫差模电感。

共模电感中漏感和差模电感是⼀回事,可以称漏感也可称差模电感。

⼀般做得好点的漏感在1-2%左右。

但有时候会特意将差模电感和共模电感做在⼀起,这时候的差模电感量就按实际需要做了。

看点2 共模电感“Z”字形符号是代表什么?共模电感的这个符号应该很常见吧,但是符号中的的 “Z” ⼀样的符号该怎么读?估计很少有⼈知道。

片式叠层共模电感,带esd

片式叠层共模电感,带esd

片式叠层共模电感是一种用于电路中的电感器件,常见于射频和通信电路中。

它具有多层叠放的结构,能够在较小的体积内提供较大的电感值,有利于节省电路板空间。

共模电感是指在两个电流引线之间产生的电感,它可以有效地抑制共模干扰信号,提高电路的抗干扰能力。

带ESD的共模电感则在传统共模电感的基础上加入了ESD(静电放电)保护功能。

ESD保护是指在静电放电事件发生时,通过合适的保护措施来保护电路不受损害。

在现代电子设备中,由于静电对电子元器件的破坏是一个常见且严重的问题,因此在设计电路时加入ESD保护功能显得十分重要。

从电路设计的角度来看,片式叠层共模电感带ESD的设计需要考虑多方面的因素,包括电感值的选择、尺寸和布局的优化、ESD 保护电路的设计等。

此外,还需要考虑材料的选择、工艺的优化等因素,以确保共模电感在实际电路中能够发挥良好的性能。

从应用角度来看,片式叠层共模电感带ESD广泛应用于移动通信设备、射频前端模块、无线路由器、蓝牙设备等电子产品中,能

够有效地提高设备的抗干扰能力和稳定性,提升产品的可靠性和性能。

总的来说,片式叠层共模电感带ESD是一种在现代电子设备中应用广泛的电感器件,它在电路设计和应用中都具有重要的作用,能够提高电路的性能和稳定性,保护电子设备免受静电等外部干扰的影响。

cmc 共模电感

cmc 共模电感CMC共模电感是一种用于滤波和抑制共模干扰的电子元件。

在现代电子设备中,共模干扰是一个常见的问题,它会导致信号的失真和设备的不稳定。

CMC共模电感通过阻断共模信号的传输路径,有效地减少共模干扰。

我们来了解一下什么是共模干扰。

在电子设备中,信号通常分为差模信号和共模信号。

差模信号是指在两个信号线上的电压或电流之间的差异,而共模信号则是指两个信号线上的电压或电流之间的共同变化。

共模干扰是指在信号传输过程中,由于设备或线路的不完美导致的共模信号的泄漏或干扰。

共模干扰会导致信号的失真、噪音的增加以及设备的不稳定。

为了解决共模干扰问题,工程师们设计了各种滤波器和抑制器。

其中,CMC共模电感是一种非常常用的元件。

CMC共模电感通常由一个或多个线圈组成,它们被串联在信号线上。

当信号通过时,差模信号会通过线圈而共模信号则会被阻断或削弱。

这样,CMC共模电感起到了滤除共模干扰的作用。

CMC共模电感的工作原理是利用线圈的电磁感应性质。

当信号通过线圈时,线圈内会产生一个磁场。

差模信号会在线圈中产生感应电动势,从而通过线圈。

而共模信号则由于信号线的对称性而被线圈削弱或阻断。

这是因为共模信号在线圈两侧产生的感应电动势大小相等,方向相反,从而相互抵消。

CMC共模电感的设计需要考虑多个因素。

首先是电感值的选择。

电感值的选择应根据具体的应用场景和要求来确定。

一般来说,电感值越大,对共模信号的抑制效果越好。

但是过大的电感值可能会导致差模信号的损耗,影响信号的传输。

因此,需要在共模抑制效果和差模损耗之间进行权衡。

其次是电感线圈的材料和结构。

电感线圈通常由导电材料制成,如铜线或铁氧体。

结构上,可以选择单线圈、多线圈或双线圈结构,以满足不同的需求。

CMC共模电感的应用非常广泛。

它可以用于各种设备和系统,如电源、通信、音频和视频设备等。

在这些设备中,共模干扰往往是一个严重的问题,会导致信号的失真和设备的不稳定。

通过使用CMC 共模电感,可以有效地减少共模干扰,提高设备的性能和可靠性。

共模电感设计共模电感设计方案共模电感设计案例

共模电感设计共模电感设计方案共模电感设计案例共模电感设计是在电路中使用的一种特殊类型的电感器件。

它的主要作用是抑制共模干扰信号,并提供电路中所需的功率传输和信号滤波。

共模电感的设计需要考虑一系列因素,包括电感值的选择、磁芯材料的选取、绕线方式以及尺寸和电流的限制等。

下面以设计一个高性能的共模电感为例,介绍共模电感设计的一般原则和过程。

共模电感的设计方案需要根据具体的应用需求进行确定。

在实际设计中,电感的值会根据工作频率、电流和共模信号的范围等因素进行选择。

通常情况下,可以通过仿真软件或公式计算来估算所需的电感值。

共模电感的磁芯材料的选取也非常重要,它直接影响到电感器件的性能。

常见的磁芯材料包括铁氧体、磁性材料和多层陶瓷等。

选取磁芯材料时,需要考虑到工作频率范围、饱和磁感应强度和损耗等因素。

绕线方式是共模电感设计中另一个重要的因素。

常见的绕线方式包括单层绕线、多层绕线和扁平线圈等。

选择合适的绕线方式可以提高电感器件的效能,减小损耗和体积。

尺寸和电流的限制是共模电感设计中需要特别注意的问题。

尺寸的选择需要考虑到电感器件在实际应用中的安装空间限制,同时要保证足够的绕线长度。

电流是决定共模电感器件能否正常工作的关键因素,因此需要根据电路中的电流要求来选择合适的电感器件。

下面是一个具体的共模电感设计案例:假设我们需要设计一个用于直流电源的共模电感,工作频率范围为10kHz到100kHz,电流为5A,电感值为10uH,尺寸限制为直径为10mm,高度为15mm。

首先,根据工作频率范围和电感值,可以通过公式计算得到所需的磁芯面积。

然后,根据绕线长度和电流要求,可以计算出所需的导线截面积。

接下来,选择合适的磁芯材料和绕线方式,并根据尺寸限制确定最终的设计。

在实际制造过程中,可以通过计算机辅助设计软件进行电感器件的建模和优化,以获得最佳的设计方案。

此外,还需进行一系列的实验测试和性能验证,以确保设计的共模电感能够满足预期的要求。

共模电感设计范文

共模电感设计范文

(包括计算过程)

一、选定参数

此项目的要求是设计一个带有共模电感的电路。

在设计该电路之前,

需要确定其参数,包括电感L,共模电感Lcm,频率f,电压V,电流I,

以及抗干扰能力要求。

1.电感L:300μH

2. 共模电感Lcm:200μH

3.频率f:10MHz

4.电压V:5V

5.电流I:1A

6.抗干扰能力要求:可以抵抗100V/μs以下的电压波动

二、电感的计算

1.首先需要计算定子芯线的绕线数N,定子芯线受到的电流和定子线

圈截面积S进行计算,公式为:

N=I×I∕I=1A×300μH÷(π×2×10-6)I=381.4

2.根据计算出来的绕线数N的值,用下面的公式计算出定子线圈截面

积S:

I=I×I∕I=1A×300μH÷381.4=7.94×10−6I

3.计算出定子线圈截面积S后,就方便计算定子线圈半径R,公式为:

I=√I∕π=√7.94×10−6I÷π=2.51×10−3I

4. 由于共模电感Lcm为200μH,因此它的绕线数Ncm、定子芯线截面积Scm、定子线圈半径Rcm也可以用上述同样的公式计算出来:Ncm=1A×200μH÷(π×2×10-6)I=254.3

Scm=1A×200μH÷254.3=7.94×10−6I

Rcm=√7.94×10−6I÷π=2.51×10−3I

三、计算共模电感

1.首先需要计算出各自线圈的抗阻阻抗Z,公式为:。

共模电感的设计范文

共模电感的设计范文共模电感是一种用于滤除电源电路中的共模干扰的重要元件。

在现代电子设备中,由于电路的复杂性和器件的密集度增加,共模干扰的抑制变得越来越重要。

共模电感作为一种专门设计用于滤除共模干扰的元件,被广泛应用于各种电子设备中。

首先,确定共模电感的额定电流。

额定电流是指共模电感能够承受的最大电流。

在设计过程中,需要根据实际应用情况和要求,确定共模电感的额定电流。

其次,确定共模电感的频率响应。

频率响应是指共模电感在不同频率下的阻抗特性。

在设计共模电感时,需要根据应用需求,选择适合的频率响应特性。

通常情况下,共模电感的频率响应应该是平滑的,在设计过程中需要对频率响应进行仿真和测试,以确保其满足设计要求。

然后,确定共模电感的电感值。

电感值是指共模电感的电感大小。

在设计过程中,需要根据共模干扰的大小和要求,选择适当的电感值。

一般情况下,共模电感的电感值应该尽可能大,以提高滤除共模干扰的效果。

最后,选择适合的材料。

共模电感的材料选择直接影响其性能和工作温度范围。

一般情况下,常用的共模电感材料有铁氧体、磁性材料等。

在设计过程中,需要根据实际应用需求,选择适合的材料。

在共模电感的设计过程中,还需要考虑其他因素,如尺寸、结构、成本等。

根据不同应用需求和要求,可以选择不同的设计方案。

为了确保设计的准确性和可靠性,可以进行仿真和测试,并根据测试结果进行优化和修改。

综上所述,共模电感是一种用于滤除电源电路中共模干扰的重要元件。

设计共模电感需要考虑多个因素,包括额定电流、频率响应、电感值、材料选择等。

在设计过程中,需要根据实际应用需求和要求,选择适合的设计方案。

通过仿真和测试,可以优化和修改设计,确保其准确性和可靠性。

电源共模电感布线要求

电源共模电感布线要求

1. 路线布置,电源共模电感应尽量靠近电源端和负载端,以最

大限度地减少共模干扰的影响。

同时,应尽量避免与高频干扰源的

布线路径重叠,以减少外部干扰对电源共模电感的影响。

2. 地线布置,在布线时需要注意良好的接地设计,尽量减小接

地回路的环路面积,减少接地回路对共模电感的影响。

同时,要避

免共模电感与其他传输线路或信号线路共用接地线,以减少共模干

扰的传播。

3. 屏蔽和隔离,在布线设计中,可以考虑采用屏蔽电缆或屏蔽

罩等措施,对电源共模电感进行屏蔽和隔离,减少外部干扰的影响。

4. 线路长度和走向,尽量减小电源共模电感的线路长度,以减

少线路的电感和电阻对共模抑制的影响。

同时,要避免电源共模电

感与高频信号线路平行布线,以减少串扰。

总之,电源共模电感布线要求主要是为了减少共模干扰的影响,提高系统的抗干扰能力。

在实际布线设计中,需要综合考虑电路的

特性和外部环境的影响,采取合适的措施来保证电源共模电感的有效工作。

共模电感的设计范文

共模电感的设计范文共模电感是指在通信电路、电源电路以及模拟电路中用于抑制共模干扰的一种电子元件。

共模干扰是指在电路中出现的由于信号线、地线等共同模式传导引起的干扰信号,常常会对电路的稳定性和指标产生显著的负面影响。

因此,共模电感的设计和应用成为了电子工程领域的重要课题。

共模电感通常由一个或多个线圈组成,其工作原理类似于传统的电感。

共模电感的设计需要考虑到电路的工作频率、共模信号的幅度、电流负载、对地电容和电感的电气参数等因素。

设计共模电感的第一步是确定电路的工作频率。

共模电感通常用于抑制从电源线、信号线等共模传导的高频干扰信号。

因此,选择合适的共模电感需要考虑到工作频率的范围以及对共模干扰的抑制效果。

其次,设计共模电感需要考虑到共模干扰信号的幅度。

共模干扰信号的幅度对共模电感的设计和选型有着重要的影响。

一般来说,干扰信号的幅度越大,所需的共模电感的电感值就越大。

此外,电流负载也是设计共模电感时需要考虑的因素之一、电路的负载电流越大,所需的共模电感的电流容量就越大。

因此,对电流负载的准确评估对共模电感的设计非常重要。

对地电容也是共模电感设计中需要考虑的因素之一、共模电感通常与地线相接,对地电容对共模电感的性能有着显著的影响。

因此,设计共模电感时需要合理地选择电感线圈的材料、绕制方式和结构等参数,以尽量减小对地电容的影响。

最后,电感的电气参数也是共模电感设计中不可忽视的因素。

电气参数包括电感值、电流容量、电阻、电感的Q值等。

这些电气参数决定了共模电感的性能和可靠性。

在共模电感的设计过程中,通常会利用电磁场仿真软件进行模拟分析和优化设计。

通过优化设计,可以得到满足电路要求的共模电感方案,从而提高整个电路的抗干扰能力和稳定性。

总之,共模电感的设计需要考虑到多个因素,包括电路的工作频率、共模干扰信号的幅度、电流负载、对地电容和电感的电气参数等。

通过合理的设计和选择,可以有效地抑制共模干扰,提高电路的抗干扰能力和稳定性。

共模电感设计

共模电感设计选择共模滤波电感规格不是一件困难和令人困惑事情。

用一个标准滤波器平面图可以用来实现一个相对简单直接设计过程。

预设平面模型滤波器元件参数很容易被修改,从而,达到符合设计要求。

常规共模电感线性滤波器防止过度噪声从AC线传导到正在工作电子设备。

通常AC线为防护重点。

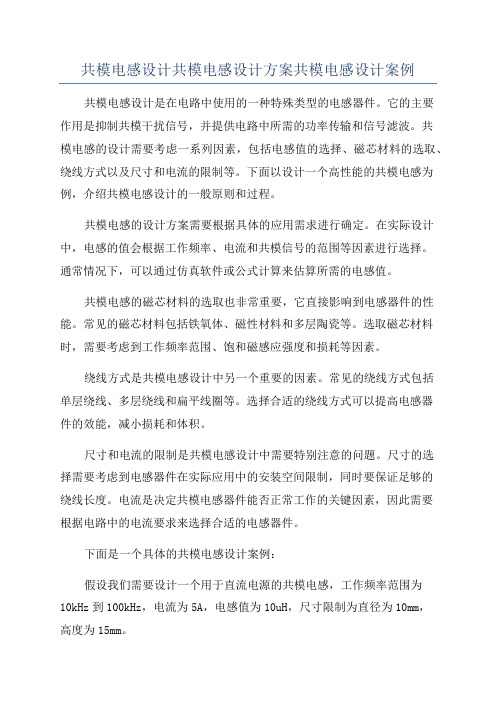

图示-1所示,共模滤波器及AC线之间接阻抗匹配电路,后面再接开关变换器。

共模噪声(大地为参考在两根线上同时产生噪声大小相等方向相同)方向是从负载流向滤波器,流向两条AC线上共模噪声已经被充分地衰减了。

其结果是从滤波器输出到AC线共模噪声经过阻抗匹配电路衰减得非常微弱了。

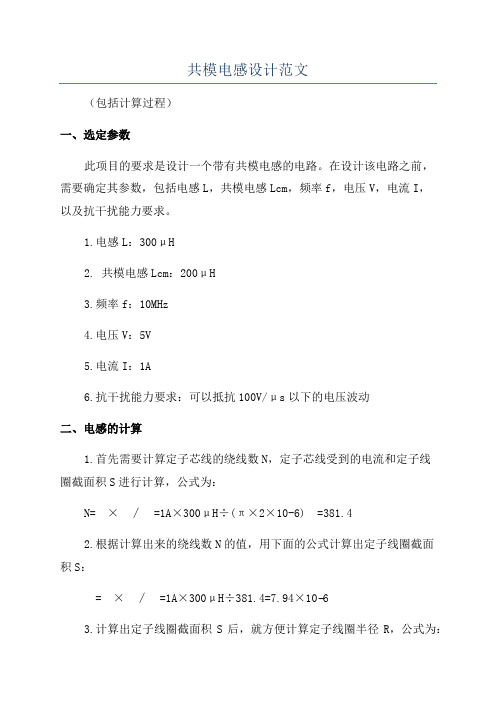

共模滤波器设计本质上是设计两个相同差分滤波器,每个分别作用于同一个磁心,两边耦合是两个极性一致电感。

对于一个差分输入电流(从(A)到(B)通过L1和从(B)到(A)通过L2),两电感间磁通(大小相等方向相反)耦合为零。

任何电感通过差模信号时,两个扼流圈未能耦合。

它们作为独立元件,只有漏感响应差模信号:这个漏感会衰减差模信号。

当电感L1和L2,通过相对于大地方向相同完全一样信号(共模型号),每个扼流圈在同一个磁心上出力是非零磁通。

对于共模信号电感作为独立元件运行相互间产生互感:互感作用使共模信号变弱。

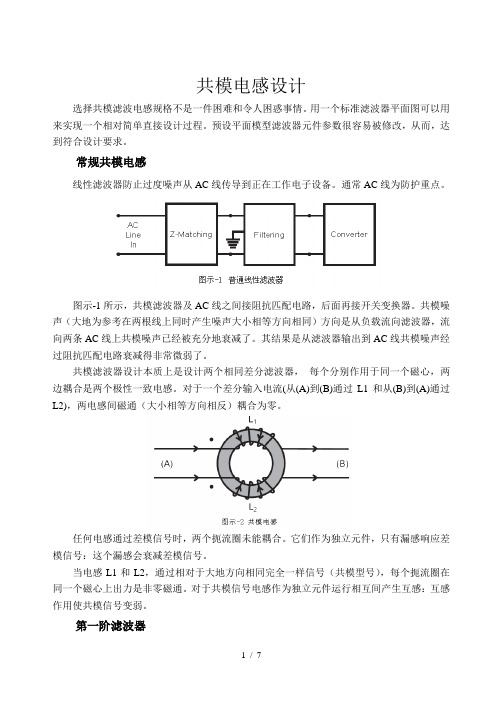

第一阶滤波器最简单、最昂贵滤波器设计是一阶滤波器。

这种类型滤波器采用单一电抗结构存储某一频率段能量,使这些能量未能传递出去。

就一个低通共模滤波器来说,一个共模电感电抗元件会被采用。

所要求扼流圈电感量可以简单地采取负载电阻除以衰减频率(包含以上频率)角频率。

譬如,要衰减4000Hz以上频率到50Ω负载里面需要一个1.99mH(50/ (2π×4000) )电感。

由此产生共模滤波器结构如图示-3:在4000Hz衰减将是3dB,并以6dB每倍频程增加。

因为主要电感依赖一阶滤波器,实际变化中,扼流圈电感是必须被考虑。

例如,正常电感测量误差为±20%,那个在4000Hz 频率名义上3dB,实际衰减得频率范围从3332Hz到4999Hz。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

One of the critical factors involved in the operation of higher order filters is the attenuating character at the corner frequency. Assuming tight coupling of the filter components and reasonable coupling of the choke itself (conditions we would expect to achieve), the gain near the cutoff point may be very large (several dB); moreover, the time response would be slow and oscillatory. On the other hand, the gain at the crossover point may also be less than the presumed -3 dB (3 dB attenuation), providing a good transient response, but frequency response near and below the corner frequency could be less than optimally flat. In the design of a second order filter, the damping factor (usually signified by the Greek letter zeta (ζ )) describes both the gain at the corner frequency and the time response of the filter. Figure (5) shows normalized plots of the gain versus frequency for various values of zeta.

20

RL

The First Order Filter

The simplest and least expensive filter to design is a first order filter; this type of filter uses a single reactive component to store certain bands of a spectral energy without passing this energy to the load. In the case of a low pass common mode filter, a common mode choke is the reactive element employed. The value of inductance required of the choke is simply the load in Ohms divided by the radian frequency at and above which the signal is to be attenuated. For example, attenuation at and above 4000 Hz into a 50⏲ load would require a 1.99 mH (50/(2π x 4000)) inductor. The resulting common mode filter configuration would be as follows:

General

Line filters prevent excessive noise from being conducted between electronic equipment and the AC line; generally, the emphasis is on protecting the AC line. Figure 1 shows the use of a common mode filter between the AC line (via impedance matching circuitry) and a (noisy) power converter. The direction of common mode noise (noise on both lines occurring simultaneously referred to earth ground) is from the load and into the filter, where the noise common to both lines becomes sufficiently attenuated. The resulting common mode output of the filter onto the AC line (via impedance matching circuitry) is then negligible.

Document 191-1

Revised 7/10/97

Document 1Байду номын сангаас1-2

to be specified as a minimum requirement, thus insuring that the crossover frequency not be shifted too high. However, some care should be observed in choosing a choke for a first order low pass filter because a much higher than typical or minimum value of inductance may limit the choke’s useful band of attenuation.

Document 191-1

CommonModeFilterDesignGuide

Introduction

The selection of component values for common mode filters need not be a difficult and confusing process. The use of standard filter alignments can be utilized to achieve a relatively simple and straightforward design process, though such alignments may readily be modified to utilize pre-defined component values. Any inductance encountered by the differential signal is then the result of imperfect coupling of the two chokes; they perform as independent components with their leakage inductances responding to the differential signal: the leakage inductances attenuate the differential signal. When the inductors, L1 and L2, encounter an identical signal of the same polarity referred to ground (common mode signal), they each contribute a net, non-zero flux in the shared core; the inductors thus perform as independent components with their mutual inductance responding to the common signal: the mutual inductance then attenuates this common signal.

L1

50 Ω

(A)

(B)

Figure 3. A first order (single pole) common mode filter

L2

Figure 2. The common mode inductor

For a differential input current ( (A) to (B) through L1 and (B) to (A) through L2), the net magnetic flux which is coupled between the two inductors is zero.

Second Order Filters

A second order filter uses two reactive components and has two advantages over the first order filter: 1) ideally, a second order filter provides 12 dB per octave attenuation (four times that of a first order filter) after the cutoff point, and 2) it provides greater attenuation at frequencies above inductor self-resonance (See Figure 4).

The attenuation at 4000 Hz would be 3 dB, increasing at 6 dB per octave. Because of the predominant inductor dependence of a first order filter, the variations of actual choke inductance must be considered. For example, a ±20% variation of rated inductance means that the nominal 3 dB frequency of 4000 Hz could actually be anywhere in the range from 3332 Hz to 4999 Hz. It is typical for the inductance value of a common mode choke