基于DSP的过采样技术

毕业设计 论文 基于DSP的交流采样系统

论文题目: 基于DSP的交流采样系统专业:学生: (签名)______________指导教师: (签名)______________摘要交流采样是电网进行微机保护的重要一步,交流采样方法的优劣直接影响到微机保护的效果。

本系统应用DSP制作交流采样电路,使其实现高速、准确的交流采样,通过软件控制实现模拟微机保护跳闸功能。

本文介绍了应用DSP实现对交流信号的采样硬件电路设计,论文总共分为四个部分。

(1)介绍交流采样的基本结构,设计思路,并分析目前交流采样的几种方式;(2)通过对交流采样对象的分析,确定采样的参数大小并设计基于F2812的采样电路;(3)运用CCS3.1利用设计的程序对采样电路进行试验,得出电路的误差并进行分析;(4)通过上述设计,能够完成对交流信号的采集、处理并将所需数值显示出来。

满足设计要求。

由于时间、水平有限,本系统没有实现与计算机的数据通信,将在日后工作与学习中进一步完善。

关键词:交流采样,DSP,微机保护Thesis topic:Professional:Undergraduate Students: (Signed )_____________Instructor: (Signed )______________ABSTRACTThe exchange sampling is the electrical network carries on the microcomputer to protect importantly one step, the exchange sampling method's protects fit and unfit quality immediate influence the effect which to the microcomputer. This system applies the DSP manufacture exchange sampling circuit, causes it to realize high speed, the accurate exchange sampling, realizes the simulation microcomputer protective trip function through the software control.This article introduced realizes using DSP to exchanges the signal sampling hardware circuit design, the paper altogether divides into four parts. (1) introduced that the exchange sampling the basic structure, the design mentality, and analyzes the present exchange sampling several ways; (2) through to exchanges the sampling object analysis, the definite sampling's parameter size and designs based on the F2812 sampling circuit; (3) carries on the experiment using CCS3.1 using the design procedure to the sampling circuit, obtains electric circuit's error and carries on the analysis; (4) through the above design, can complete to exchanges signal gathering, processing and will need the value to demonstrate, satisfies the design requirements.Because the time, the level are limited, this system has not realized with computer's data communication, will be working in the future and in the study further consummates.KEY WORDS: Exchange sampling, DSP, microcomputer protection目录第一章绪论 (1)1.1研究背景与意义 (1)1.2研究现状 (1)1.3课题的总体设计思路 (2)第二章交流采样系统的器件介绍 (3)2.1 DSP芯片介绍 (3)2.1.1 DSP的特点 (3)2.1.2 DSP TMS320 F2812芯片的技术指标 (4)2.1.3 DSP F2812开发板的管脚功能说明 (4)2.2 运算放大器LM324介绍 (6)2.2.1 LM324工作原理 (6)2.2.2 LM324的引脚、结构及其典型运用 (8)2.3开关式稳压电源芯片LM2596介绍 (12)2.3.1 LM2596的特点 (12)2.3.2 LM2596的引脚及主要性能参数 (13)2.4 稳压芯片TL431介绍 (14)2.4.1 TL431工作原理 (14)2.4.2 TL431的引脚和其主要性能参数 (15)2.5 LED八段数码管显示器 (15)2.5.1 LED数码管的分类 (15)2.5.2数码管驱动方式 (16)2.5.3数码管的显示段码 (17)2.6 74LS164移位寄存器介绍 (18)2.6.1 74LS164工作原理 (18)2.6.2 74LS164的引脚及级联 (18)第三章基于DSP的交流采样系统硬件的总体设计方案 (20)3.1 硬件电路设计思路 (20)3.2 总体电路的布局 (20)3.3 电流互感器、电压互感器电路的设计 (21)3.4运放电路的设计 (21)3.4.1 跟随电路 (22)3.4.2 二阶低通有源滤波电路 (22)3.4.3 偏置电路 (24)3.4.4 反相电路 (25)3.5 TL431 5V偏置电压产生电路的设计 (25)3.6 LM2596 5V电源的设计 (26)3.7 继电保护电路的设计 (27)3.8 合闸电路的设计 (27)3.9 数码管显示电路的设计 (28)3.10 系统软件的设计 (28)第四章系统的硬件调试和系统测试 (30)4.1 系统硬件的调试 (30)4.1.1 采样电路的调试 (30)4.1.2显示电路的调试 (30)4.1.3 继电保护电路的调试 (30)4.2系统误差分析 (31)4.3调试过程中存在的问题及解决方法 (39)结束语 (40)致谢 (41)参考文献 (42)附录 (43)第一章绪论1.1研究背景与意义电力系统在运行中,可能发生各种故障和不正常运行状态,最常见同时也是最危险的故障是发生各种形式的短路。

基于DSP的新型SPWM采样方法

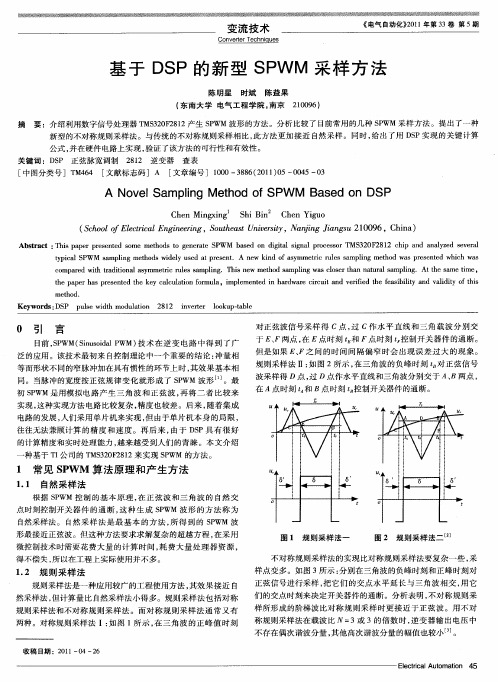

规则采样法 Ⅱ: 图 2所示 , 如 在三 角波 的负 峰时刻 t对 正弦信 号 o

波采样得 D点 , D点作水平 直线和三角波分别交 于 A、 过 B两点 , 在 A点 时刻 t和 日点时刻 t控 制开关器件 的通断 。 A B

“ n

初 S WM是用模拟 电路 产 生 三角波 和 正 弦波 , P 再将 二 者 比较来 实现 , 这种实现方法 电路 比较复杂 , 精度也较差 。后 来 , 随着集成 电路 的发展 , 人们采用单片机来实现 , 由于单 片机 本身 的局 限 , 但 往往无法兼顾计 算 的精度 和 速度 。再 后来 , 由于 D P具 有 很好 S 的计算精度和实 时处理能力 , 越来越受 到人们 的青睐 。本 文介绍

t e p p rh sp e e t d t e k y c lu a in f r l ,i l me t d i a d a e cr uta d v r e h e sbl y a d v l i ft i h a e a r s n e e a c lt o mu a mp e n e n h r w r i i n e i d t e f a i i t n a i t o s h o c i f i dy h

A v l m pig Me h d O W M s d O No e Sa l t o fSP n Ba e n DSP

Ch n M i x n e ng i g Sh n iBi Ch n Yiu e g o

( colfEetcl n i e n , o tes U i r t, Sh o o l r a gn r g S uhat nv sy ci E ei ei

变 流 技 术

Co v re e h i u s n et rT c nq e

交流采样技术及其DSP实现方法

交流采样技术及其DSP实现方法摘要:本文提出了对电力系统参数进行交流采样的设计思想,结合实例介绍以TMS320C240DSP与高速14位A/D转换器AD7863构成的数据采集系统,给出了采样算法、硬件电路及软件流程等。

关键词:交流采样 DSP 锁相环1.引言目前,交流电参量的采样测量方法主要有两种:直流采样法和交流采样法。

直流采样法是采样经过整流后的直流量,对采样值只需作一次比例变换即可得到被测量的数值,软件设计简单,计算方便。

但直流采样法存在一些问题:测量精度直接受整流电路的精度和稳定性的影响;整流电路参数调整困难且受波形因素影响较大;此外,用直流采样法测量工频电压、电流是通过测量平均值来求出有效值的,当电路中谐波含量不同时,平均值与有效值之间的关系也将发生变化,给计算结果带来了误差。

因此,要获得高精度、高稳定性的测量结果,必须采用交流采样技术。

交流采样技术是按一定规律对被测信号的瞬时值进行采样,再按一定算法进行数值处理,从而获得被测量的测量方法。

该方法的理论基础是采样定理,即要求采样频率为被测信号频谱中最高频率的2倍以上,这就要求硬件处理电路能提供高的采样速度和数据处理速度。

目前,高速单片机、DSP及高速A/D转换器的大量涌现,为交流采样技术提供了强有力的硬件支持。

交流采样法包括同步采样法、准同步采样法、非同步采样法等几种,本文介绍的是同步采样法。

同步采样法就是整周期等间隔均匀采样,要求被测信号周期T与采样时间间隔Δt及一周内采样点数N之间满足关系式T=N·Δt,即:采样频率为被测信号频率的N倍。

根据提供采样信号方式不同,同步采样法又分为软件同步采样法和硬件同步采样法两种。

硬件同步采样法是由专门的硬件电路产生同步于被测信号的采样脉冲。

它能克服软件同步采样法存在截断误差等缺点,测量精度高。

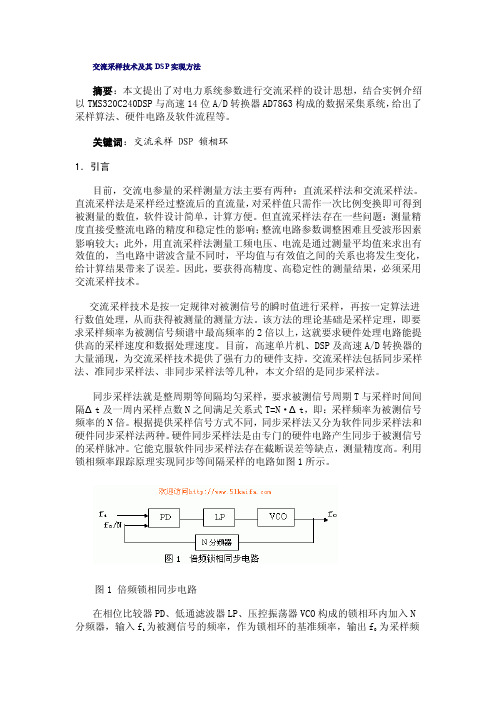

利用锁相频率跟踪原理实现同步等间隔采样的电路如图1所示。

图1 倍频锁相同步电路在相位比较器PD、低通滤波器LP、压控振荡器VCO构成的锁相环内加入N 分频器,输入f i为被测信号的频率,作为锁相环的基准频率,输出f0 为采样频率。

基于DSP的跟踪频率变化的交流采样技术

基于DSP的跟踪频率变化的交流采样技术TMS320F240 在沟通采样系统中,通常是一个周波采样64点或128点的电量值,然后对这些数据举行处理。

假如电网频率恒定,则采样间隔t=T/N(T为周期,N为采样点),而电网的频率通常有一定的波动,所以要不断调节采样间隔。

在系统中,普通采纳过零触发和单片机的外部中断来检测电量周波的开头和结束时光,再利用内部定时器计算出周期和采样间隔,在采样间隔定时中断程序中启动一次采亲。

这种计划有两个缺点:其一,电路实现复杂;其二,精度不高,由于要考虑中断能否实时响应。

过零触发电路产生的中断响应具有不确定性。

我们在用法TMS320F240 开发沟通采样系统时,巧妙地利用该款DSP的定时器、捕捉器和不中屏蔽中断(NMI)实现了跟踪频率变幻的沟通采样。

1 NMI中断、定时器、捕捉器的容易分析(1)NMI中断 TMS320F24X系列有一个不行屏蔽中断(NMI)引脚。

当该引脚有跳变信号时(可编程为升高沿或下降沿触发),立刻进入中断程序,可以用于紧张大事的处理。

本文中用于跟踪被测电量的频率。

(2)定时器介绍TMS320F240有3个通用定时器,每个通用定时器有6种计数方式:①停止/保持模式,模式0;②单增计数模式,模式1;③延续增计数模式,模式2;④定向增/减计数模式,模式3;⑤单增/减计数模式,模式4;⑥延续增/减计数模式,模式5。

设fc是CPU的时钟频率,则定时时光t=脉冲个数/(fc/分频系数),脉冲个数与定时周期寄存器的值或比较寄存器的值有关。

工作过程是:①按照CPU的频率、定时时光确定计数寄存器的初值TxNT、周期寄存器的初值TxPER、比较寄存器的初值TxCMP。

②启动定时器计数。

③计数到比较寄存器的值发生比较匹配中断,同时使TxCMP引脚发生跳变。

本文中利用T3CPU的跳变去启动一次A/D转换。

④计数到周期寄存器的值发生周期匹配中断。

定时器一旦开头工作就不受程序影响,精确性高,保证每隔固定间隔举行采样。

一种基于DSP的三相交流采样技术

● 6通道 1 一b t 次逼近型 ADC, 6 i逐 最大吞吐率 为 2 0 S/s 5k ; ● AV c范围为 4 7 V- . 5 片上有 2 5 c .5 5 2 V, .V基

性 高等优点 , 而且 具有一 定 的实 用价值 。

制 造 的型 模 / 数 转 换 器 , 实 时采 样 系 统 中 多 通 道 在

模 / 数 转 换 器 提 高 了 同步 采 样 的数 字 信 号 处 理 的速 度和精度 。

AD7 5 6 6的主要 特性如 下 :

2,芯片特点

2 1 MS 2 F 8 片的特点 . T 3 0 2 1 芯 2

提 出了一种高性能数字信号处理器 TMS 2 F2 2与 3 0 8 1

2 2 A 7 5 芯 片特点 . D 5 6

AD7 5 采用 先进 的工业 C 6 6是 MOS i MOS 工艺 (C )

AD转换芯片 AD7 5 6 6够成 的并行的数据转换采集 系统 。 与同类的系统相 比, 它具有精 度高 、实时响应 快 、可靠

电气 传 动

Elc r a v s e ti IDr e c i

● 有并行和 串行接 口, S I 与 P /QS I/ Wie P r /DS P兼容 的高速 串行接 口; ● 可通过 引脚或软件方 式设 定输入 电压 范围 ( ±

交流采样的采样速率要求高程序计算量相对较大但是它的采样图2信号调理电路值所含信息量大可以通过不同的算法获取所需的多种信息如有效值相位谐波分量等其实时性好且32限幅电路随着dsp技术的发展高速实时数据处理成为可能使在模数转换中如果ad转换器损坏检测和控交流采样成为目前主要的使用方式

基于DSP的数据采集及FFT实现

基于DSP的数据采集及FFT实现基于数字信号处理器(DSP)的数据采集和快速傅里叶变换(FFT)实现在信号处理和频谱分析等领域具有广泛的应用。

通过使用DSP进行数据采集和FFT实现,可以实现高速、高精度和实时的信号处理。

首先,数据采集是将模拟信号转换为数字信号的过程。

数据采集通常涉及到模拟到数字转换器(ADC),它将模拟信号进行采样并进行量化,生成离散的数字信号。

DSP通常具有内置的ADC,可以直接从模拟信号源获取数据进行采集。

采集到的数据可以存储在DSP的内存中进行后续处理。

数据采集的关键是采样频率和采样精度。

采样频率是指在单位时间内采集的样本数,它决定了采集到的频谱范围。

采样频率需要满足奈奎斯特采样定理,即至少为信号最高频率的2倍。

采样精度是指每个采样点的位数,它决定了采集到的数据的精确程度。

常见的采样精度有8位、16位、24位等。

在数据采集之后,可以使用FFT算法对采集到的数据进行频谱分析。

FFT是一种用于将时间域信号转换为频域信号的算法,它能够将连续时间的信号转换为离散频率的信号。

FFT算法的核心是将复杂度为O(N^2)的离散傅里叶变换(DFT)算法通过分治法转化为复杂度为O(NlogN)的算法,使得实时处理大规模数据成为可能。

在使用DSP进行FFT实现时,可以使用DSP芯片内置的FFT模块,也可以通过软件算法实现FFT。

内置的FFT模块通常具有高速运算和低功耗的优势,可以在较短的时间内完成大规模数据的FFT计算。

软件算法实现FFT较为灵活,可以根据实际需求进行调整和优化。

通常,FFT实现涉及到数据的预处理、FFT计算和结果后处理。

数据的预处理通常包括去除直流分量、加窗等操作,以减小频谱泄漏和谱漂的影响。

FFT计算是将采集到的数据通过FFT算法转换为频域信号的过程。

结果后处理可以包括频谱平滑、幅度谱归一化、相位分析等。

通过合理的数据预处理和结果后处理,可以获得准确的频谱信息。

除了基本的数据采集和FFT实现,基于DSP的数据采集和FFT还可以进行其他扩展和优化。

基于DSP和ADS8364的高速数据采集处理系统.

基于DSP和ADS8364的高速数据采集处理系统随着现代科学技术的发展和计算机技术的普及,高速数据采集系统已应用于越来越多的场合,如通信、雷达、生物医学、机器人、语音和图像处理等领域。

本文介绍的数据采集处理系统采用CPLD控制ADS8364完成数据的A/D转换,转换后的数据预先存储到FIFO中,再经DSP进行前端的数字信号处理后,通过USB总线传给上位机,并在上位机上进行存储、显示和分析等。

该系统完全可以满足信号采集处理对高精度及实时性的要求。

1 系统原理数据采集处理系统主要由前端信号调理电路、ADC芯片ADS8364、CPLD 芯片EPM3128A、DSP芯片TMS320F2812、USB芯片CY7C68013及其外围电路组成。

系统原理框图如图l所示。

系统主要完成的任务为:DSP接收上位机通过USB总线发送的命令,完成系统工作参数的设置,并通过模拟地址/数据总线与CPLD进行通信,向CPLD发送控制命令;对外部的多路模拟量输入进行信号调理,在CPLD控制下进行单通道或多通道A/D转换,将采集到的数据存储在一片FIFO芯片中;当FIFO中存储的数据半满时,对DSP产生一个中断信号,DSP收到此中断信号后,取出FIFO中的部分数据,进行前端数字信号处理,将处理完毕的数据通过USB总线传给上位机;上位机实现各种图形界面操作和后端信号处理,对所采集的信号进行分析。

系统可对输入的多路模拟信号进行同步采样,这就使得采集到的数据不仅含有模拟信号的幅度特性,同时还保持不同模拟信号之间的相位差异;采样频率可以预置,以适应不同速率的采样要求。

2 系统硬件系统硬件包括信号调理模块、A/D转换模块、DSP处理器模块、CPLD 逻辑控制模块以及USB通信模块。

2.1 信号调理模块的设计外部的多路模拟量输入信号往往是微弱的传感器信号,信号的幅值较小,为了方便且不失一般性,假定其幅值范围为O~25mV。

ADS8364待转换的模拟输入电压范围应保持在AGND-0.3V和AVDD+O.3V之间。

基于DSP的过采样技术

基于DSP的过采样技术1 引言模数(AD)转换通常是数字信号处理应用中的第一步,依据应用的不同,对模数转换器(ADC)也有不同的要求,衡量模数转换器的最重要的标准是它的转换速率、分辨率和精度。

应用过采样技术,再加上适当的数字滤波和抽取,就可以得到比原有的ADC更高的分辨率。

在数字信号处理器(DSP)中应用过采样技术需要快速ADC以非常快的速度来采样模拟信号,并且需要快速DSP来执行数字低通滤波和抽取。

TI公司出品的DSP芯片TMS320LF2407采用3.3V供电,30MIPS的执行速度使得指令周期缩短至33ns,内置有10位的AD转换器,最小转换时间为500ns(详见TI公司的资料:TMS320LF/LC240x DSPController,Systemand Peripherals,2000),这些为在DSP中应用过采样技术创造了条件。

2 过采样降低对模拟抗混叠滤波器的限制在采样过程中首要的问题是采样频率的选择,Nyquist采样定理指出:若连续信号x(t)是有限带宽的,其频谱的最高频率为fc,对x(t)采样时,若保证采样频率fs≥2fc,那么,就可由采样信号恢复出x(t)。

在实际对x(t)作采样时,首先要了解x(t)的最高截止频率fc,以确定应选取的采样频率fs。

若x(t)不是有限带宽的,在采样前应使用抗混叠(anti-aliasing)滤波器对x(t)作模拟滤波,以去掉f>fc的高频成分。

因此,在AD转换前就需要模拟低通滤波器具有尖锐的滚降特性,来限制模拟信号的频谱。

一个理想的滤波器应能让所有低于fs/2的频率通过,而完全阻隔掉所有大于fs/2的频率。

通常,滤波器和采样频率的选择是将我们感兴趣的频带限制在DC和fs/2之间。

用更高的采样频率可以降低对低通滤波器的限制,图1所示为以2倍的原采样频率对模拟信号进行采样,在这种情况下,滤波器的截频为fs/2,阻带的起始频率为fs,这样就可以让所有我们感兴趣的频率通过,而抑制掉所有高于fs 的频率。

过采样原理

过采样原理

过采样技术是数字信号处理(DSP)中一种常见的技术,可以提

高数字信号处理系统的性能和精度。

过采样是一种以某种程度减轻抽样和再构建等信号失真的有效方法,它可以改变信号处理系统的性能,在带宽有限的应用场景下,使用过采样技术可以有效地抑制抽样失真,提高系统的性能和精度。

过采样是一种增加额外元素来满足实际数据处理所需要的精度

的技术。

由于必须满足实际数据处理要求的高精度,因此,过采样技术能够有效地增加信号处理精度,从而改善信号处理系统的性能。

过采样的精度改进是由两部分因素:抗混叠以及抗噪声。

过采样可以有效地减少抽样产生的混叠,它将信号失真的源降低到零,从而提高信号处理精度。

此外,它也能有效地抑制外部噪声,减少噪声干扰,也能提高信号处理精度。

在实际应用中,过采样原理是用来提高采样率的过程。

例如,如果一个信号的采样率为1000 Hz,为了提高信号的采样精度,可以使用过采样原理,将这个信号的采样率提高到2000 Hz,从而增加信号处理的精度。

此外,由于过采样技术具有抗混叠和抗噪声的优势,因此它广泛应用于高精度的数字信号处理,特别是实时双向传输和自动化等应用领域。

综上所述,过采样原理是数字信号处理领域中一种常用的技术,它能够有效地改善被抽样信号的精度,抑制外部噪声,提高信号处理

系统的性能和精度,广泛应用于高精度的数字信号处理中。

基于DSP的高速多通道同步数据采集系统

基于DSP的高速多通道同步数据采集系统摘要:本文介绍了一种基于DSP的高速多通道同步数据采集系统。

该系统采用高精度的ADC和FPGA作为数据采集和处理的核心部件,通过DMA传输实现了多通道同步数据采集,并可以通过网络接口将采集的数据实时传输到上位机。

实验结果表明,该系统具有高精度、高速率和高可靠性等优点,可以满足对多通道同步数据采集的高要求。

关键词:DSP;高速多通道;同步数据采集;DMA传输;网络接口1. 引言在科学研究、医学诊断、工业控制等领域中,对数据采集系统的要求越来越高。

随着科学技术的不断发展,现代数据采集系统的要求也变得越来越高。

要求数据采集速度快、采集精度高、可靠性强、系统稳定性好。

因此,如何设计一种高速、高精度、高可靠性的多通道同步数据采集系统成为研究的热点之一。

2. 系统框架基于上述需求,本文设计了一种基于DSP的高速多通道同步数据采集系统。

该系统的部件结构如下图所示:其中,ADC为数据采集部分,FPGA为数据处理部分,DSP为数据管理和传输部分。

3. 数据采集部分数据采集部分采用高精度的ADC为核心部件。

该ADC采用的是16位的Sigma-Delta型ADC,采样率可达到100kSPS,可以满足多通道高速同步采集的要求。

为了实现多通道同步采集,采集部分还需要将多个通道的信号进行采集,并进行同步处理。

实现该功能需要向FPGA发送同步信号。

为了避免信号在传输过程中的延迟造成的误差,我们使用了双向同步FIFO,并设置了一些额外的同步逻辑来确保采集的信号可以达到很高的同步精度。

4. 数据处理部分数据处理部分采用FPGA作为核心部件。

该FPGA可以对采集到的数据进行在线实时处理。

在此过程中,FPGA实现了信号滤波、频率分析、功率谱分析、时域分析等多种功能。

这些功能可以满足不同领域的数据处理要求。

5. 数据管理和传输部分数据管理和传输部分采用DSP作为核心部件。

DSP主要负责管理数据的存储和传输。

过采样技术在DSP中的应用

过采样技术在DSP中的应用

马玲;卢海英

【期刊名称】《沈阳工程学院学报(自然科学版)》

【年(卷),期】2009(005)001

【摘要】在测量精度要求较高的地方通常采用高分辨率的片外ADC来实现,但却增加了产品的成本.而采用过采样方法,既可以不采用片外ADC,又能提高ADC测量的分辨率和信噪比,不仅很好地控制了产品成本,又提高了产品的性能.分析了2种使用过采样率的方法--白噪声法和三角波法,通过分析可以看出,采用这2种方法不仅可以实现利用较廉价的低档次的ADC芯片获得昂贵芯片才能得到的精度指标;而且使用三角渡过采样方法,还可以实现耗费较少的硬件和软件资源.介绍了实现整个采集过程的硬件构成和软件的实现过程.

【总页数】3页(P81-83)

【作者】马玲;卢海英

【作者单位】沈阳工程学院计算中心,沈阳,110136;沈阳市人才中心,沈阳,110004【正文语种】中文

【中图分类】TN850.8

【相关文献】

1.过采样技术在基于DSP的智能断路器设计中的应用 [J], 王新波;马永浓;宋矿利;程博;张浩

2.非减性Dither与过采样技术在低频模拟采集系统中的应用 [J], 逯宏超;赵冬青;

储成群;焦新泉

3.过采样技术在通信信号处理中的应用 [J], 龙雄

4.动态过采样技术在分布式光纤温度传感器中的应用 [J], 孙偲晟

5.过采样技术在通信信号处理中的应用探讨 [J], 胡秋阳

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP的交流采样电路设计

西安科技大学综合实验报告学院: 电气与控制工程学院专业名称: 测控技术与仪器设计题目: DSP交流采集电路设计组员:侯春慧张娜张珍珍张小红姓名:张珍珍学号: 0706070111指导教师: 高瑜目录1.实验目的2.实验内容3.实验原理4.实验步骤5.实验原理图6.实验程序7.实验结果8.问题解决9.心得体会基于DSP的交流采样电路设计一、实验目的1、通过此次试验,让同学们能够好好复习以前学过的知识,主要是如何采集交流电量并处理得到我们需要的实测数据,一边与后面的分析预测等内容;2、通过此次试验,能够让同学们更加熟悉继电保护的原理以及实际中的应用方法和实现手段,更便于大家理解;3、通过此次试验,让同学们对于DSP了解更加深刻,不知是要在原理上懂得,更要学会应用它,能够利用DSP进行一些简单的编程;4、通过此次试验,培养大家的实际动手能力以及小组合作能力,为今后的职业发展做一个小小的实践;二、实验内容通过电网采集电压信号,根据电压信号变化,控制灯泡的跳闸控制。

三、实验原理交流采样技术是按一定规律对被测信号的瞬时值进行采样,再按一定算法进行数值处理,从而获得被测量的测量方法。

该方法的理论基础是采样定理,即要求采样频率为被测信号频谱中最高频率的2倍以上,这就要求硬件处理电路能提供高的采样速度和数据处理速度。

目前,高速单片机、DSP及高速A/D转换器的大量涌现,为交流采样技术提供了强有力的硬件支持。

交流采样法包括同步采样法、准同步采样法、非同步采样法等几种。

此次试验是通过互感器来对电压数据进行采集,再进过偏置等的处理,处理到数值范围为0~3V,再输入到DSP通过其内部所含的DA装换,将采样数据进行处理、数值分析、比较,如果处理后的数值大于给定的整定值则通过对GPIO端口的控制实现输出跳闸信号,作用于继电器。

四、实验步骤1、按要求设计交流采集电路原理图;2、根据原理图焊接板子;3、验证硬件的采样输出波形是否满足0~3V要求,跳闸回路是否准确;4、经老师检查认可后,通电进行系统调试。

基于DSP+FPGA的高速采样系统设计

基于DSP+FPGA的高速采样系统设计对飞轮转子位移信息的采样检测是保证飞轮储能系统(FESS)高速、稳定运行的关键。

利用数字信号处理器(DSP)的计算能力和现场可编程门阵列(FPGA)的并行处理能力,采用主从设计方式,提出一种基于DSP和FPGA的多通道、高速采样系统的实现方法;阐述了系统的模块功能、硬件布局、软件设计以及对高速AD芯片THS1207的控制方式。

实验证明了设计的系统能够实现多通道、高速采样的要求。

标签:数字信号处理器;现场可编程门阵列;THS1207芯片;高速采样一、各模块器件选型由上述分析,设计中,AD采样模块选用TI公司生产的高速AD采样芯片THS1207。

每片THS1207包含4个采样通道,因此,本文选用2片THS1207协同控制,同步采样。

运算控制模块选取时,考虑到基于数字信号处理器(digitalsignalprocessor,DSP)和现场可编程门阵列(fieldprogrammablegatearray,FPGA)的特点,为了保证采样和控制运算的实时性,本文提出了一种DSP和FPGA主从设计的多通道高速采样系统。

FPGA作为DSP的协处理器,实现对AD芯片的控制和采集数据的缓存,DSP通过扩展的直接存储器访问(extendeddireetmemoryaccess,EDMA)读取FPGA缓存的采样数据,实现对采样数据的运算处理。

选用32位高速浮点型DSP芯片TMS320C6713,拥有强大的浮点计算能力。

FPGA芯片选用EP3C25Q240,其拥有24624门逻辑单元,66门18×18乘法器,4个锁相环单元以及最多达215个可供用户使用的I/O引脚,完全满足本设计的需要。

二、系统性能要求2.1 根据飞轮转子的结构和性能特点设置采样模块性能要求为:5个采样通道,0.1%采样精度。

采样速度设计,假定飞轮转速为105r/min,每转采样128点,则相邻两个采样点之间的时间间隔应小于4.69μs。

基于DSP捕获口的交流信号采样

基于DSP捕获口的交流信号采样 基于DSP捕获口的交流信号采样 DSP

08006305 周婷婷

一、硬件电路设计

1.信号调理电路

滤波电路传递函数

Vin Rs 1 = 2.09V RIN Rt Ct

最终电路的实物图:

4.电平转换 使用74LVC14进行5V到3.3V的电平转换,同时对输出的波形进行整 形。最后输入到DSP的捕获口即可。输入到CAP的波形如下:

二、软件设计 在整个的程序设计中,共涉及到两个中断的使用,分别为定时器T3 和捕获口CAP1的中断。 定时器的T3的周期为采样保持的周期,也就是采样控制信号的周期, 每个采样保持周期结束之后,计算在这个周期中的多次捕获口获得计数值 的平均值,以期获得比较精准的频率数值。 而捕获口的中断则用于读取每两次有效沿之间的计数值差,可以通 过频率计算出周期,进而计算得到频率值。

最终得出的数据为呈现出正弦变化,并且数值在-311~311之间,有 误差,但是误差较小。根据分析可能是电流互感器的失真造成的,用示波 器观察,在电流互感器的副边测量的电压不再正负对称,同时也有可能是 市电电路中存在多次谐波的可能。

三、方案论证 对于采样数据的正确性,通过使用软件计算交流电的有效值和万用表的 测量进行比较可以获得结论。软件实现有效值的计算公式如下:

Vout

1 + RCs = 2 2 2 Vi R C s + 3RCs + 1

ቤተ መጻሕፍቲ ባይዱ

2.采样保持电路

3.压频转换 在比较了几款压频转换芯片 之后,决定选用LM331芯片 作为压频转换芯片,它的工 作输出频率范围在1Hz到 100KHz之间,转换的非线 性度达到万分之一,性价比 很高,故而选择之。

基于DSP的交流采样技术的研究的开题报告

基于DSP的交流采样技术的研究的开题报告一、项目背景及研究意义交流信号的数字化采集是数字信号处理中的基本问题,采集方式涉及到采样周期、采样频率等问题,把交流信号转换为数字信号后,使其变得易于数字信号处理器(DSP)处理及储存,且随着DSP技术的逐步发展,采样电路转向数字采样电路已成为大势所趋。

该研究项目主要研究基于DSP的交流采样技术,能够实现对各种交流信号的高精度采集,具有广泛的应用前景,例如,在音频信号处理、机器人控制等领域都有着广泛的使用,同时还能够提高工业自动化、家庭自动化等领域的效率、精度。

二、研究内容及技术路线本研究将基于DSP的交流采样技术进行研究,其主要内容包括:1. DSP的原理研究,理解DSP工作原理以及数据传输机制等。

2. 交流信号采集技术研究,了解交流信号的基本特性和采样原理,以及电路设计和参数选择等。

3. 交流采样算法研究,研究信号重构和数字化处理等方面的算法。

技术路线如下:1. 完成对DSP原理的学习和掌握,包括基本的芯片架构、函数库、寄存器配置等相关知识。

2. 认真研究交流信号采样原理和方法,分析交流信号的特性、传输方法和信号处理方法,并选择合适的采样器来实现采样功能。

3. 研究适用于DSP的交流采样算法,包括基于插值算法的信号重构、滤波器设计等。

4. 按照上述路线开发交流采样系统、测试算法的稳定性、均匀性、精度和效果等指标。

三、项目预期成果1. 该项目开发实验一套基于DSP的交流采样系统,实现交流信号的高精度采集。

系统在精度、效率等方面均可与现有商用采样系统媲美,并具备良好的可扩展性、灵活性和可维护性。

2. 提出一种新型的交流采样算法,能够快速且准确地对交流信号进行采样,并提高信号处理的速度和质量。

3. 实验与应用验证,该研究成果适用于音频信号处理、机器人控制、工业自动化、家庭自动化等领域,提高了交流信号采集与处理的精度、效率,进一步促进了数字信号处理领域的发展。

基于DSP的高速AD采集技术研究

基于DSP的高速AD采集技术研究一、引言数字信号处理已经成为各种现代控制系统的基础组成部分,需要各种传感器实时采集数据并进行处理。

高速AD采集技术是数字信号处理中不可缺少的一部分,通过使用这一技术,可以获得高速信号的精确数字表示。

其中的DSP技术可以使AD采集信号更准确、更灵活、更可靠。

本文将讨论基于DSP的高速AD采集技术,并介绍应用于该技术前的需求分析、硬件平台和软件设计的设计原则及方案。

二、前置需求分析在进行市场需求分析时,首先需要澄清AD转换器的类型,如采用高速PAM、Delta-SIGMA、SAR类型等。

这取决于所需的带宽和制噪能力。

高速PAM型AD转换器适用于高速采样和窄带传输,Delta-SIGMA的转换速度适中,制噪能力较高,广泛应用于无线通讯设备中。

SAR型转换器的转换速度可达到每秒数百兆赫,制噪能力很弱,但成本是最低的。

对于高速AD采集技术的要求之一是快速数据处理能力。

常用的方案是基于FPGA硬件设计方案和基于DSP硬件处理方案,本文重点关注DSP技术应用于该流程中实现高精准度和高速数据处理。

三、硬件平台及软件设计基于DSP处理采集数据可以更方便地实现高速AD采集处理,由于DSP的先进性和灵活性,使它能够应用于多种类型的信号处理任务。

在进行硬件平台的设计中,广泛应用FPGA进行高速数据缓存,此外,还可以同时采用SDRAM存储。

在设计FPGA和DSP硬件平台之前,必须考虑以下几个因素:1. 应用的速度:需确定高速采样频率及数据流的处理速度。

2. 采用的接口类型:为接驳采样或传感器而且必须确定合适的接口类型,并优化输入于输出速度及时延时间等。

3. 存储器结构:选用合适的存储器结构进行数据的缓存。

4. 电源相关要求:需满足高精度要求,其安装需要特殊的混频器。

5. 小型化和远离电场的要求:在实现高速AD采集处理的过程中需为电子电磁干扰(EMI)设定防止或减轻的措施,以保证数据的可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用更高的采样频率可以降低对低通滤波器的限制,图1所示为以2倍的原采样频率对模拟信号进行采样,在这种情况下,滤波器的截频为fs/2,阻带的起始频率为fs,这样就可以让所有我们感兴趣的频率通过,而抑制掉所有高于fs的频率。但这样做违反了Nyquist采样定理,所以还需要用ADC后的数字滤波器来将信号的频率限制到fs/2以下。采用了过采样后的这种抗混迭滤波器可以得到简化,允许的通带到阻带的过渡区很宽。

5.3 数据采集

AD转换完成后产生中断,在中断服务子程序中读出每次转换的结果,作为数字低通滤波的输入。

5.4 数字滤波

采用FIR结构的滑动平均滤波器(MovingAverage Filter),滑动平均滤波器的Z变换为:

从输入xi计算输出yi的表达式为:

5.5 抽取

抽取过程将以K倍来降低最后的数据率。一般来说,抽取操作是和数字滤波结合在一起的,即,只需在数字滤波中计算每K个输出值。

5.6 中断服务程序

在中断服务程序中执行以下几个操作:调整PWM占空比、读出AD转换值、数字滤波(其中包括抽取)。

6 结束语

本文从分析过采样的频谱特性出发,分析了过采样技术的原理、用DSP实现过采样的方法以及软件上的实现,随着DSP在各种信号处理领域中的广泛应用,过采样技术在其中的应用也将日益广泛,因此,本文也有助于进一步发展利用过采样技术。

3 过采样提高信噪比

经模拟滤波后,模拟信号被采样并转换成数字值,因为数字域仅包含有限的字长,若要用它来表示连续信号,就要引入量化误差,最大量化误差为±0.5LSB。因为一个N位的ADC的输入范围被分成2N个离散的数值,每一个数值由一个N位的二进制数表示,所以,ADC的输入范围和字长N是最大量化误差的一个直接表示,也是分辨率的一个直接表示。代表数字值的字长决定了信噪比,因此通过增加信噪比可以增加转换的分辨率。加入三角波信号可提高信噪比(详见TI公司的资料:Oversampling Techniques Using theTMS320C24x Family,June 1998)。

基于DSP的过采样技术

1 引 言

模数(AD)转换通常是数字信号处理应用中的第一步,依据应用的不同,对模数转换器(ADC)也有不同的要求,衡量模数转换器的最重要的标准是它的转换速率、分辨率和精度。应用过采样技术,再加上适当的数字滤波和抽取,就可以得到比原有的ADC更高的分辨率。

在数字信号处理器(DSP)中应用过采样技术需要快速ADC以非常快的速度来采样模拟信号,并且需要快速DSP来执行数字低通滤波和抽取。TI公司出品的DSP芯片TMS320LF2407采用3.3V供电,30MIPS的执行速度使得指令周期缩短至33ns,内置有10位的AD转换器,最小转换时间为500ns(详见TI公司的资料:TMS320LF/LC240x DSPController,Systemand Peripherals,2000),这些为在DSP中应用过采样技术创造了条件。

5 过采样的软件实现

实现过采样的DSP软件包括以下6个主要模块。

5.1 外设初始化

采用EVA模块的TIMER1来启动ADC转换并且提供PWM输出,TIMER1工作于连续增计数模式,周期寄存器的值等于AD转换速率,由周期匹配事件来启动AD转换。

5.2 三角波信号产生

因为有了高采样速率,输入信号的变化相对来说比较缓慢,图2中,输入信号为0.6 LSB,一个典型的AD转换器将采样这个信号并把它转换成1 LSB。当样值。0和1出现的比例就表示了这个在0和1 LSB之间的实际值。

图2中的采样因子K为16,采样值为0.563,得到了比原转换结果更小的量化误差。使用三角波调制过采样技术所增加的信噪比可以表示为:

2 过采样降低对模拟抗混叠滤波器的限制

在采样过程中首要的问题是采样频率的选择,Nyquist采样定理指出:若连续信号x(t)是有限带宽的,其频谱的最高频率为fc,对x(t)采样时,若保证采样频率fs≥2fc,那么,就可由采样信号恢复出x(t)。在实际对x(t)作采样时,首先要了解x(t)的最高截止频率fc,以确定应选取的采样频率fs。若x(t)不是有限带宽的,在采样前应使用抗混叠(anti-aliasing)滤波器对x(t)作模拟滤波,以去掉f>fc的高频成分。

用该法产生的信噪比和分辨率的增加见表1。

使用增加三角波信号的过采样每加一倍过采样速率,就可以增加6 dB的分辨率。然而这种方法需要输入信号与三角波信号不相关,如果不能做到这一点,那信号在一个过采样周期内变化不能超过±0.5 LSB。

4 用TMS320LF2407来实现过采样

图3为利用TMS320LF2407来实现过采样,虚线框部分都可以用LF2407来实现。PWM信号输出可以用来产生三角波信号,数字滤波和抽取用软件来实现。

图4为三角波信号产生以及与输入信号叠加的电路图。PWM信号的占空比在0和100%之间。R3和C1作为积分器产生一个0到3V之间的三角波信号输入到运放。输出信号连至ADC的输入。

由前面论述可知,三角波信号由PWM信号产生,PWM信号的占空比由编程TIMER1的比较寄存器(T1CMPR)决定。为了得到三角波信号,T1CMPR中的值需要由某一步长(STEP)来不断地增加和减少,而这一步长由定时器周期寄存器(T1PR)和过采样因子(K)决定,其计算公式如下:

用一标志(FLAG)表示三角波的上升或下降,它用来决定比较寄存器中的值被STEP增加还是减少了。CURRENT代表当前定时器比较寄存器中的值。用软件改变PWM占空比的流程。

如果输入信号在两个量化步长q1与q0之间,则它将被量化成q1或q0。当增加一个适当的三角波信号,并高速采样,将会量化出一系列的q1与q0,这两个值出现的比例就代表了此输入信号在两个量化步长之间的相对位置。要应用这种方法得到比较好的效果,三角波信号的幅度必须为(n+0.5)LSB,其中,n=0,1,2,...。