信号与信息处理研究生实验4桶形移位器

计算机组成原理-实验四-移位控制实验

实验四移位控制实验一、实验目的(1)了解移位寄存器芯片(74LS299)的逻辑功能。

(2)掌握移位寄存器数据的载入、左移、右移的方法。

(3)掌握移位寄存器工作模式的设置,观察在不同工作模式下移位寄存器的逻辑功能。

二、实验原理移位操作时算术逻辑运算部件ALU众多操作中的一种,74LS181算数逻辑运算芯片不带位移功能,需要在其他芯片的配合下才能实现移位操作。

实验台选用74LS299作为移位部件,与74LS181组成具有移位功能的算术逻辑运算部件(ALU UNIT)。

移位操作有很重要的逻辑意义,对一个数据左移一个二进制位就相当于进行了一次乘2操作(Si+1=Si×2),左移和算数加结合可实现算数乘操作;右移一个二进制位就相当于进行了一次除2操作(Si+1=Si÷2),右移和算数减的结合可实现算数除操作。

1.芯片74LS299的逻辑功能4LS299是一种数据宽度为8为的多功能移位寄存器芯片,片内含有8为寄存器D7—D0,与普通寄存器芯片不同之处是D7—D0与I/O6—I/O0除了一一对应输出外还可有左右移位输出。

左移时D0对应I/O1、D1对应I/O2……以此类推;右移时D7对应I/O6、D6对应I/O5……也以此类推。

对于输出、左右移位输出功能的选择,由S1、S0的功能控制端决定。

芯片封装在具有20引脚的封装壳中,封装型式见图2-5。

S1图 2-5 74LS29974LS299芯片的主要引脚有:(1)IO7—IO0:数据输入/输出端,芯片的输入/输出共用一个引脚,不同于74LS181输入、输出端引脚是分开的。

(2)S0、S1:功能控制端,控制左移、右移等逻辑功能。

(3)OE1、OE2:输出使能端,低电平时,IO7-IO0处于输入状态,高电平时,IO7-IO0处于输入状态。

(4)CP:时钟输入端,数据的输入、位移需要在时钟脉冲的同步控制下动作。

(5)M:清零端,低电平有效,清零位移寄存器。

移动实验四 位同步提取实验

实验四位同步提取实验一、实验目的1、掌握用数字环提取位同步信号的原理及对信息代码的要求。

2、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验器材1、移动通信原理实验箱一台2、20M双踪示波器一台三、实验记录1、安装好发射天线和接收天线。

2、插上电源线,打开主机箱右侧的交流开关,再按下开关POWER301、POWER302、POWER401和POWER402,对应的发光二极管LED301、LED302、LED401和LED402发光,CDMA系统的发射机和接收机均开始工作。

3、发射机拨位开关“信码速率”、“扩频码速率”、“扩频”均拨下,“编码”拨上,接收机拨位开关“信码速率”、“扩频码速率”、“跟踪”均拨下,“调制信号输入”和“解码”拨上。

此时系统的信码速率为1Kbit/s,扩频码速率为100Kbit/s。

将“第一路”连接,“第二路”断开,这时发射机发射的是第一路信号。

将拨码开关“GOLD3置位”拨为与“GOLD1置位”一致。

4、根据实验二中步骤8~11的方法,调节“捕获”和“跟踪”旋钮,使接收机与发送机GOLD码完全一致。

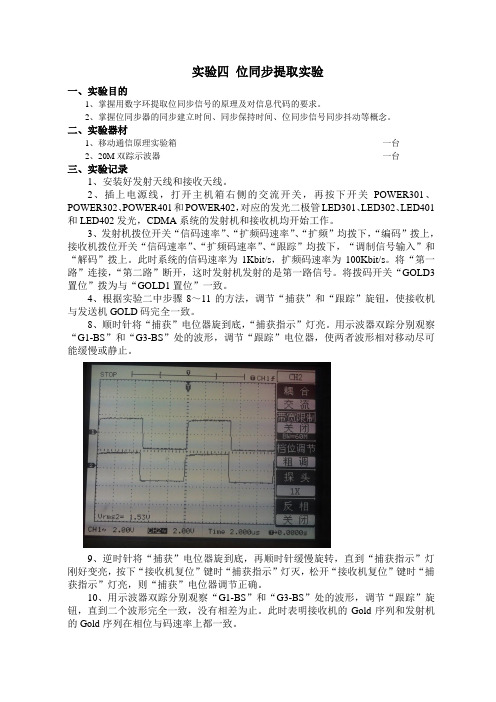

8、顺时针将“捕获”电位器旋到底,“捕获指示”灯亮。

用示波器双踪分别观察“G1-BS”和“G3-BS”处的波形,调节“跟踪”电位器,使两者波形相对移动尽可能缓慢或静止。

9、逆时针将“捕获”电位器旋到底,再顺时针缓慢旋转,直到“捕获指示”灯刚好变亮,按下“接收机复位”键时“捕获指示”灯灭,松开“接收机复位”键时“捕获指示”灯亮,则“捕获”电位器调节正确。

10、用示波器双踪分别观察“G1-BS”和“G3-BS”处的波形,调节“跟踪”旋钮,直到二个波形完全一致,没有相差为止。

此时表明接收机的Gold序列和发射机的Gold序列在相位与码速率上都一致。

11、用示波器双踪分别观察GOLD1和GD-TX处的波形,二者的波形应完全一致。

5、根据实验四中步骤6~7的方法,调节“频率调节”旋钮,恢复出相干载波。

(完整word版)实验四 移位运算器实验

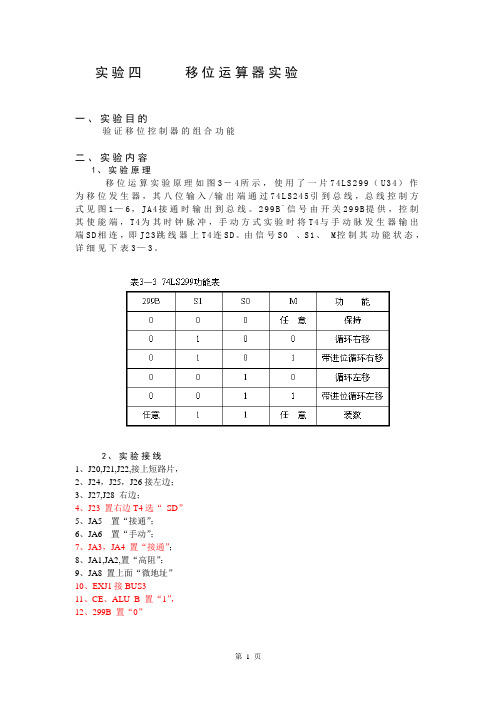

实验四移位运算器实验一、实验目的验证移位控制器的组合功能二、实验内容1、实验原理移位运算实验原理如图3-4所示,使用了一片74L S299(U34)作为移位发生器,其八位输入/输出端通过74L S245引到总线,总线控制方式见图1—6,J A4接通时输出到总线。

299B`信号由开关299B提供,控制其使能端,T4为其时钟脉冲,手动方式实验时将T4与手动脉发生器输出端S D相连,即J23跳线器上T4连S D。

由信号S0、S1、M控制其功能状态,详细见下表3—3。

2、实验接线1、J20,J21,J22,接上短路片,2、J24,J25,J26接左边;3、J27,J28 右边;4、J23 置右边T4选“SD”5、JA5 置“接通”;6、JA6 置“手动”;7、JA3,JA4 置“接通”;8、JA1,JA2,置“高阻”;9、JA8 置上面“微地址”10、EXJ1接BUS311、CE、ALU_B 置“1”,12、299B 置“0”3、实验步骤⑴ 连接实验线路,仔细查线无误后接通电源。

⑵ 置数,具体步骤如下:⑶ 移位,参照上表改变S 0、 S 1、 M 、 299B 的状态,按动手动脉冲开关以产生时钟脉冲T 4,观察移位结果。

四、实验数据Q08I/O 07I/O 113I/O 26I/O 314I/O 45I/O 515I/O 64I/O 716Q717OE12OE13S01S119CLK 12CLR 9DS011DS718U3474LS299299B`S0S1VCC GN DAQ0AQ7T4UN1A 74LS08UN1B 74LS08UN2A 74LS32UN2B 74LS32UN2C 74LS32UN3A 74LS04MQCY321654321218109654R4910KVCCCLK11D12S D10C D13Q9Q8UN5B 74LS74UN4BUN4C299B`UN1D 74LS08UN1A 74LS08UN1B 74LS08UN1C 74LS08AQ7AQ0UN3B 74LS32UN4DUN4EART4MS0S1CN 4QCYUN2C 74LS08CYUN2A 74LS08UN3BUN3A 74LS3274LS32CY561233124312345645910811101112138910456LZ D0-LZD 7图3-4BU SD0--D 7KD7-KD0 = 00110101299B S1 S0 M 功能状态0 0 0 任意保持001101010 1 0 0 循环右移00110101->10011010->01001101 ... ->001101010 1 0 1 带进位循环右移00110101->00011010->10001101->01000110->10 100011->01010001->10101000->11010100->0110 1010->001101010 0 1 0 循环左移00110101->01101010->11010100 ... ->001101010 0 1 1 带进位循环左移00110101->01101011->11010110->10101100->01 011001->10110011->01100110->11001101->1001 1010->00110101任意 1 1 任意装数11111111实验心得:通过本次实验我们对移位运算器有了更深的认识。

数字电路与数字逻辑实验4-移位寄存器及应用

2、多功能移位寄存器-74LS194

多功能寄存器具有并行置数、左移、右移、保持的功能。

S1S0 =00: 保持

S1S0 =01:右移

S1S0 =10: 左移

S1S0 =11: 置位

三、实验内容

1、用74LS194设计扭环型计数器

扭环形计数器:用n位的移位寄存器所构成的具有2n种状态的 计数器,也称为约翰逊计数器。

1

DIL Q0

DIR Q 0 Q 1 Q 2 Q 3 S 0

0

DIL 74LS194 S1 1

CP CP D0 D1 D2 D3 RD

Q0Q1Q2Q3

××××

0000Βιβλιοθήκη 00010011左移

复位

0111

1000

1100

1110

1111

2、用74LS194设计00011101序列信号发生器

⑴ 序列信号的循环长度 M=8,确定移位寄存器位数 n, 2n-1<M≤2n,。故 n=3,选定为 3 位。

设备型号 THM—7

ESCORT 3136A

TBS1102B AFG3000C

数量 一台 一台 一台 一台

备注

⑵ 确定移位寄存器的 M个独立状态。将序列码 00011101按 照每 3 位一组,划分为 8个状态,状态转换图如下:

⑶ 根据 M个不同状态列出移位寄存器的状态表和反馈函 数表,求出反馈函数 F 的表达式。

⑷ 设计电路

利用双四选一数据选择 器74LS153实现组合电路, 具体电路如右图所示。

CP端输入1KHz,VP-P=4V, 直流偏置=2v的方波信号, 用示波器观察CP信号和F输 出信号。

⑸ 实验结果

反馈移位型序列信号发生器的设计实验报告

反馈移位型序列信号发生器的设计实验报告一、实验目的本实验旨在通过搭建反馈移位型序列信号发生器的电路,实现对特定频率的信号进行发生和输出。

同时,借助实验过程中的观测和分析,深入研究反馈移位型序列信号发生器的工作原理和特性。

二、实验原理反馈移位型序列信号发生器的核心原理是利用反馈电路实现信号的周期性变化。

具体来说,电路中包括一定数量的延时器和异或门,每经过一个延时器,信号就会向后移动一个时刻。

同时,异或门则负责将当前信号和之前的信号进行异或运算,实现信号的周期性变化。

通过不断调整延时器的数量和时间,可以实现对特定频率的信号进行发生和输出。

三、实验步骤1.搭建反馈移位型序列信号发生器电路。

2.将正弦波信号输入到反馈移位型序列信号发生器电路中。

3.通过示波器观测反馈移位型序列信号发生器输出的信号,并记录其频率和幅度。

4.根据观测结果,调整延时器数量和时间,实现对特定频率的信号进行发生和输出。

5.重复步骤3和4,直至输出信号符合实验要求。

四、实验结果与分析通过反馈移位型序列信号发生器的电路搭建和实验操作,我们成功实现了对特定频率的信号进行发生和输出。

其中,延时器数量和时间的调整是关键步骤之一。

在实验过程中,我们发现增加延时器数量可以使输出信号的频率更低,而增加延时器时间则会让输出信号的频率更高。

我们还观测到了反馈移位型序列信号发生器的输出信号具有周期性,并且幅度随着时间的增加而逐渐降低。

这是由于信号在电路中传播时,经过多次异或运算后逐渐衰减所导致的。

五、实验总结通过本次实验,我们深入了解了反馈移位型序列信号发生器的工作原理和特性,并成功实现了对特定频率的信号进行发生和输出。

在实验过程中,我们需要注意调整延时器数量和时间,以实现对输出信号频率的控制。

此外,我们还应该注意观测输出信号的周期性和幅度变化,以深入了解电路的工作特性。

本次实验为我们深入了解反馈移位型序列信号发生器的原理和特性提供了重要的实践机会,也为我们今后的学习和研究奠定了基础。

环形移位电路实验报告

环形移位电路实验报告实验名称:环形移位电路实验实验目的:1. 了解环形移位电路的基本原理和特性;2. 熟悉环形移位电路的实验方法和步骤;3. 掌握环形移位电路的实验操作技巧;4. 分析环形移位电路的实验现象和原因。

实验仪器设备:1. 环形移位电路实验装置;2. 数字示波器;3. 信号发生器;4. 电压表。

实验原理:环形移位电路是由若干个触发器构成的一种序列电路,每个触发器的输出与下一个触发器的输入相连,最后一个触发器的输出又与第一个触发器的输入相连,形成一个闭合的环形线路。

在环形移位电路中,输入信号从一个触发器输入后,经过每个触发器按特定规则环形地向下一个触发器传递,直至回到初始触发器。

实验步骤:1. 将环形移位电路实验装置接通电源,并将信号发生器和示波器接入电路。

2. 设置信号发生器的频率和幅度,并将输出信号接入环形移位电路的输入端。

3. 使用示波器观察环形移位电路中各触发器的输出波形,并记录波形数据。

4. 改变信号发生器的频率和幅度,再次观察和记录波形数据。

5. 结束实验,关闭电路设备。

实验结果:根据实验步骤记录的波形数据,可以观察到以下实验现象:1. 当输入信号的频率较小时,触发器的输出波形基本保持不变,仅在每个时钟周期后发生微小的移位;2. 随着输入信号频率的增加,触发器的输出波形开始出现明显的移位,且移位速度逐渐加快;3. 当输入信号的频率达到一定值时,触发器的输出波形从线性移位变为环形移位,即每个时钟周期后回到初始状态;4. 随着输入信号频率的继续增大,触发器的输出波形维持在环形移位状态,且移位速度不再改变。

实验分析:根据实验结果可以得出以下分析结论:1. 环形移位电路的移位速度与输入信号的频率相关,当频率较低时,移位速度较慢,当频率逐渐增大时,移位速度加快;2. 当输入信号的频率达到一定值时,触发器的输出波形出现了环形移位现象,说明该环形移位电路具备了循环移位的特性;3. 在环形移位电路中,触发器的移位方式是按照一定的规则依次传递,最后回到初始状态,形成了一个闭合的移位环。

信号变换应用实验报告(3篇)

第1篇实验目的1. 理解并掌握信号变换的基本原理和方法,包括傅里叶变换、拉普拉斯变换和Z 变换。

2. 通过实验,加深对信号变换在实际应用中的理解,如信号处理、系统分析等。

3. 学习使用MATLAB等工具进行信号变换的计算和分析。

实验原理信号变换是信号处理领域的重要工具,它可以将信号从时域转换为频域或其他域,便于分析、处理和设计。

本实验主要涉及以下几种信号变换:1. 傅里叶变换(FT):将时域信号转换为频域信号,揭示信号的频率成分。

2. 拉普拉斯变换(LT):将时域信号转换为复频域信号,适用于分析线性时不变系统。

3. Z变换(ZT):将离散时间信号转换为Z域信号,适用于分析离散时间系统。

实验器材1. MATLAB软件2. 示波器3. 信号发生器4. 连接线实验步骤1. 傅里叶变换实验- 使用MATLAB生成一个正弦波信号,采样频率为1000Hz,采样点数为1024。

- 对该信号进行傅里叶变换,观察频谱图。

- 改变采样频率和采样点数,观察频谱图的变化。

2. 拉普拉斯变换实验- 使用MATLAB生成一个指数衰减信号。

- 对该信号进行拉普拉斯变换,观察复频域图。

- 分析拉普拉斯变换的结果,解释信号的特性。

3. Z变换实验- 使用MATLAB生成一个离散时间信号。

- 对该信号进行Z变换,观察Z域图。

- 分析Z变换的结果,解释信号的特性。

4. 信号变换在系统分析中的应用- 使用MATLAB设计一个简单的模拟滤波器。

- 对滤波器进行傅里叶变换,观察滤波器的频率响应。

- 分析滤波器的性能,如通带、阻带、截止频率等。

实验结果与分析1. 傅里叶变换实验- 频谱图显示正弦波的频率成分与采样频率有关。

- 改变采样频率和采样点数,频谱图发生相应的变化。

2. 拉普拉斯变换实验- 复频域图显示指数衰减信号的极点和零点。

- 分析结果,可以确定信号的衰减速度和稳态值。

3. Z变换实验- Z域图显示离散时间信号的极点和零点。

- 分析结果,可以确定信号的稳定性、收敛速度等特性。

信号分析与处理实验四个

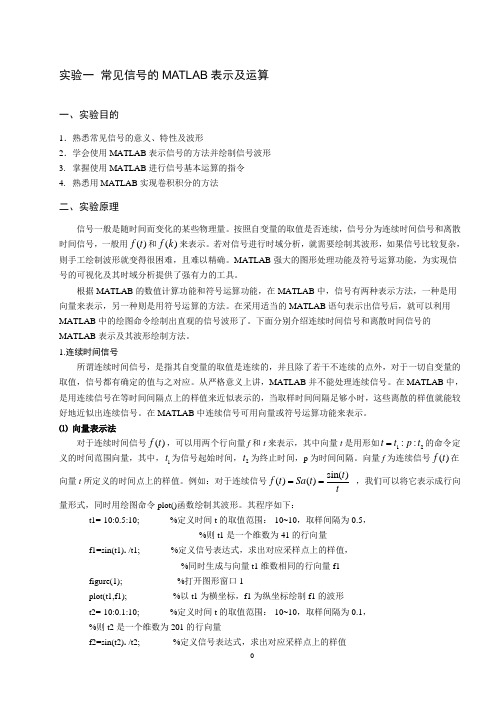

实验一 常见信号的MATLAB 表示及运算一、实验目的1.熟悉常见信号的意义、特性及波形2.学会使用MATLAB 表示信号的方法并绘制信号波形 3. 掌握使用MATLAB 进行信号基本运算的指令 4. 熟悉用MATLAB 实现卷积积分的方法二、实验原理信号一般是随时间而变化的某些物理量。

按照自变量的取值是否连续,信号分为连续时间信号和离散时间信号,一般用()f t 和()f k 来表示。

若对信号进行时域分析,就需要绘制其波形,如果信号比较复杂,则手工绘制波形就变得很困难,且难以精确。

MATLAB 强大的图形处理功能及符号运算功能,为实现信号的可视化及其时域分析提供了强有力的工具。

根据MATLAB 的数值计算功能和符号运算功能,在MATLAB 中,信号有两种表示方法,一种是用向量来表示,另一种则是用符号运算的方法。

在采用适当的MATLAB 语句表示出信号后,就可以利用MATLAB 中的绘图命令绘制出直观的信号波形了。

下面分别介绍连续时间信号和离散时间信号的MATLAB 表示及其波形绘制方法。

1.连续时间信号所谓连续时间信号,是指其自变量的取值是连续的,并且除了若干不连续的点外,对于一切自变量的取值,信号都有确定的值与之对应。

从严格意义上讲,MATLAB 并不能处理连续信号。

在MATLAB 中,是用连续信号在等时间间隔点上的样值来近似表示的,当取样时间间隔足够小时,这些离散的样值就能较好地近似出连续信号。

在MATLAB 中连续信号可用向量或符号运算功能来表示。

⑴ 向量表示法对于连续时间信号()f t ,可以用两个行向量f 和t 来表示,其中向量t 是用形如12::t t p t =的命令定义的时间范围向量,其中,1t 为信号起始时间,2t 为终止时间,p 为时间间隔。

向量f 为连续信号()f t 在向量t 所定义的时间点上的样值。

例如:对于连续信号sin()()()t f t Sa t t== ,我们可以将它表示成行向量形式,同时用绘图命令plot()函数绘制其波形。

移相信号实验报告

一、实验目的1. 理解移相信号的概念和原理。

2. 掌握移相信号的实现方法。

3. 通过实验验证移相信号在信号处理中的应用。

二、实验原理移相信号是一种通过对原始信号进行时间轴上的平移操作而得到的信号。

在移相信号中,信号的相位发生变化,但振幅和频率保持不变。

移相信号在通信、信号处理等领域有着广泛的应用。

三、实验设备1. 移信源信号发生器2. 信号分析仪3. 数据采集卡4. 计算机及实验软件四、实验步骤1. 设置移信源信号发生器:- 选择合适的频率和振幅。

- 设置移信源信号发生器产生一个正弦波信号。

2. 采集原始信号:- 将移信源信号发生器的输出端连接到数据采集卡的输入端。

- 打开实验软件,开始采集原始信号。

3. 实现移相信号:- 使用实验软件中的移相功能,将原始信号进行时间轴上的平移操作。

- 设置移相的角度,可以是正角度(右移)或负角度(左移)。

4. 采集移相信号:- 采集移相后的信号,并存储在计算机中。

5. 分析信号:- 使用信号分析仪对原始信号和移相信号进行时域和频域分析。

- 比较两种信号的振幅、频率和相位变化。

6. 结果验证:- 通过对比分析,验证移相信号在时域和频域上的变化。

- 分析移相信号在实际应用中的优势。

五、实验结果与分析1. 时域分析:- 在时域上,移相信号与原始信号相比,相位发生了变化。

- 通过设置不同的移相角度,可以观察到信号在时间轴上的平移。

2. 频域分析:- 在频域上,移相信号与原始信号的频率和振幅保持一致。

- 移相操作不会改变信号的频率成分。

3. 实验结论:- 通过实验验证了移相信号在时域和频域上的变化规律。

- 移相信号在实际应用中具有重要作用,如通信、信号处理等。

六、实验总结1. 通过本次实验,我们对移相信号的概念和原理有了更深入的了解。

2. 掌握了移相信号的实现方法,并能够通过实验验证其应用。

3. 实验结果表明,移相信号在信号处理领域具有广泛的应用前景。

七、实验建议1. 在实验过程中,注意移相角度的设置,以便观察不同移相角度下的信号变化。

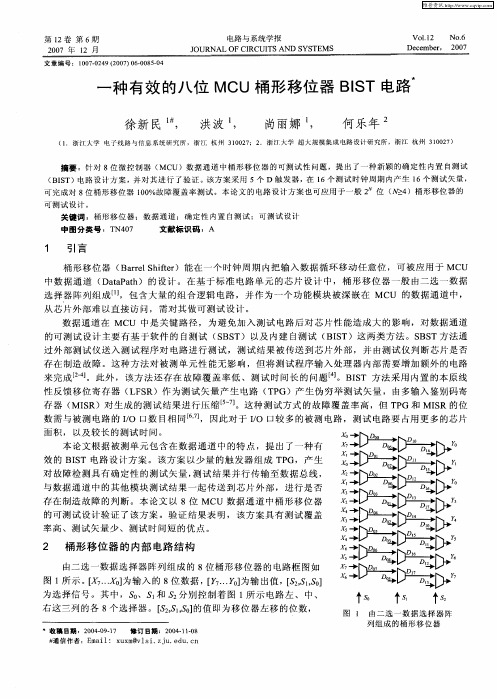

一种有效的八位MCU桶形移位器BIST电路

2 桶 形移 位器 的内部 电路 结构

由二选 一数 据 选 择 器 阵列 组 成 的 8位 桶 形 移 位 器 的 电路 框 图 如

面 积 , 以及 较 长 的测 试 时 间 。

本 论 文 根 据 被 测 单 元 包 含 在 数 据 通 道 中 的特 点 ,提 出 了一 种 有

效 的 BIT 电路 设 计 方 案 。该 方 案 以少 量 的触 发器 组 成 T G,产 生 S P

对 故 障 检 测 具 有 确 定 性 的测 试 矢 量 , 试 结 果 并 行 传 输 至 数 据 总 线 , 测 与数 据 通 道 中 的 其 他 模 块 测 试 结 果 一 起 传 送 到 芯 片外 部 ,进 行 是 否 存 在 制造 故 障 的判 断 。本 论 文 以 8位 MC 数 据 通 道 中桶 形移 位 器 U

Vo11 .2

N o. 6

D e e b r 2 7 cm e, 00

一

种 有 效 的 八 位 MCU桶 形 移 位 器 B S 电路 T I

徐新 民 , 洪 波 , 尚丽娜 , 何 乐年 2

( .浙 江 大 学 电 予线 路 与 信 息 系 统 研 究 所 , 浙江 杭 '3 0 2 ;2 1 I 10 7 .浙 江 大 学 超 大 规 模集 成 电路 设 ’ 究 所 ,浙 江 杭 州 3 0 2 ) 1 研 10 7

*是 过外 部 测试 仪送 入 测 试 程序 对 电路 进 行 测 试 ,测 试 结 果 被 传送 到 芯 片 外 部 ,并 由测 试 仪 判 断 芯 片 否

DSP技术及应用考试复习资料(按题型分)要点

一、填空题1.命令文件用.cmd扩展名表示。

2.TMS320LF2407 DSP共有144引脚。

3.与C语言相比,汇编语言的可移植性较差4. 在数的定标中,如果采用Q表示法,一个Q8定点数的精度为1/165. TMS320LF2407 DSP内部含有8 个辅助寄存器。

6.TMS320LF240X DSP微处理器采用的是哈佛结构7. 采用DSP进行数字信号处理属于软硬件结合实现方法。

8. 一般情况下,下列器件在工作时,功耗最小的是小液晶块9. TMS320LF2407 DSP中,累加器的位数为:32位10.可编程数字信号处理器简称DSP11.看门狗的作用是PC受到干扰而跑飞时产生复位12.TMS320LF240X DSP有1个累加器。

13.输出比较功能一般用于在规定的时刻输出需要的电平14. TMS320LF240X DSP共有86条指令,分为6大类。

15.一般情况下,TMS320LF240X系列DSP内的用户程序存储在Flash存储器中16. TMS320LF240X DSP具有 4 个通用定时器,都采用16位计数器,计数范围是0-65535个脉冲。

17.ADD *+,8,AR4含义是:以当前AR中的内容为地址的数据存储单元内容左移8位后与ACC中内容相加,结果送与ACC,且AR中内容加一,并指定AR4为下一个当前AR。

18.在数的定标中,如果采用Q表示法,Q越大,数值范围越大,但精度越低。

19.LF240X中断源分为__软件______中断和__硬件______中断。

20. 在TMS320LF240X DSP中,优先级最高的中断是__复位______。

21.TMS320LF240X DSP共有__3____种基本的数据寻址方式,分别是立即、直接、间接。

22.按数据格式分类,DSP芯片可分为定点式芯片和浮点式芯片。

23.TMS320LF2407A DSP有3种低功耗模式。

24.DSP执行一条指令,需要通过取指、译码和执行等阶段。

信号与信息处理研究生实验4桶形移位器

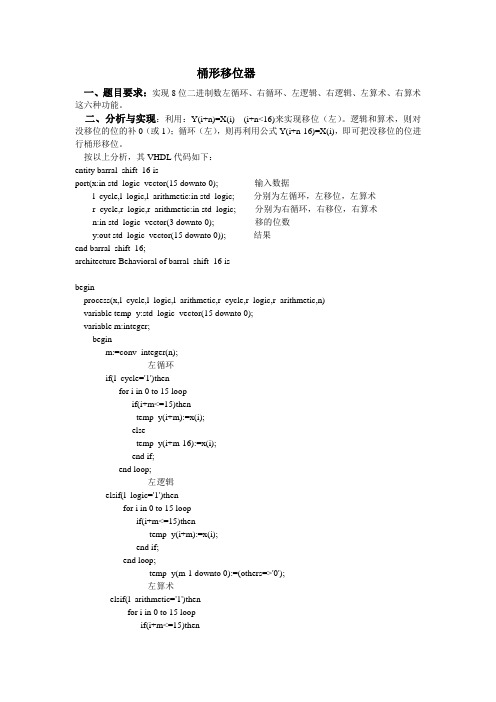

桶形移位器一、题目要求:实现8位二进制数左循环、右循环、左逻辑、右逻辑、左算术、右算术这六种功能。

二、分析与实现:利用:Y(i+n)=X(i) (i+n<16)来实现移位(左)。

逻辑和算术,则对没移位的位的补0(或1);循环(左),则再利用公式Y(i+n-16)=X(i),即可把没移位的位进行桶形移位。

按以上分析,其VHDL代码如下:entity barral_shift_16 isport(x:in std_logic_vector(15 downto 0); --输入数据l_cycle,l_logic,l_arithmetic:in std_logic; --分别为左循环,左移位,左算术r_cycle,r_logic,r_arithmetic:in std_logic; --分别为右循环,右移位,右算术n:in std_logic_vector(3 downto 0); --移的位数y:out std_logic_vector(15 downto 0)); --结果end barral_shift_16;architecture Behavioral of barral_shift_16 isbeginprocess(x,l_cycle,l_logic,l_arithmetic,r_cycle,r_logic,r_arithmetic,n)variable temp_y:std_logic_vector(15 downto 0);variable m:integer;beginm:=conv_integer(n);-------------------------左循环--------------------------------------if(l_cycle='1')thenfor i in 0 to 15 loopif(i+m<=15)thentemp_y(i+m):=x(i);elsetemp_y(i+m-16):=x(i);end if;end loop;-------------------------左逻辑--------------------------------------elsif(l_logic='1')thenfor i in 0 to 15 loopif(i+m<=15)thentemp_y(i+m):=x(i);end if;end loop;temp_y(m-1 downto 0):=(others=>'0');-------------------------左算术--------------------------------------elsif(l_arithmetic='1')thenfor i in 0 to 15 loopif(i+m<=15)thentemp_y(i+m):=x(i);end if;end loop;temp_y(m-1 downto 0):=(others=>x(0));-------------------------右循环--------------------------------------elsif(r_cycle='1')thenfor i in 15 downto 0 loopif(i-m>=0)thentemp_y(i-m):=x(i);elsetemp_y(16+i-m):=x(i);end if;end loop;-------------------------右逻辑--------------------------------------elsif(r_logic='1')thenfor i in 15 downto 0 loopif(i-m>=0)thentemp_y(i-m):=x(i);end if;end loop;temp_y(15 downto 16-m):=(others=>'0');-------------------------右算术--------------------------------------elsif(r_arithmetic='1')thenfor i in 15 downto 0 loopif(i-m>=0)thentemp_y(i-m):=x(i);end if;end loop;temp_y(15 downto 16-m):=(others=>x(15)); ---------------------------------------------------------------------end if;y<=temp_y;end process;end Behavioral;三、仿真结果与期望值一致,结果正确。

移位操作电路实验报告(3篇)

第1篇一、实验目的1. 理解移位操作电路的工作原理。

2. 掌握移位操作电路的设计与搭建方法。

3. 验证移位操作电路的功能和性能。

二、实验原理移位操作电路是数字电路中常用的基本单元,用于实现二进制数的移位操作。

根据移位方向的不同,移位操作可分为逻辑移位和算术移位。

1. 逻辑移位:将移位的数据视为无符号数据,移位过程中不考虑数据的符号位。

逻辑移位包括逻辑左移(SLL)和逻辑右移(SRL)。

2. 算术移位:将移位的数据视为带符号数据,移位过程中保持符号位不变。

算术移位包括算术右移(SRA)。

移位操作电路主要由移位寄存器和控制逻辑组成。

移位寄存器用于存储待移位的数据,控制逻辑根据移位指令控制移位寄存器的移位操作。

三、实验设备1. 移位寄存器:一片74LS1942. 逻辑门电路:若干3. 电源:+5V4. 导线:若干5. 实验平台:示波器、逻辑分析仪等四、实验内容1. 逻辑左移(SLL)实验(1)搭建电路:将74LS194连接成8位左移寄存器,并添加控制逻辑。

(2)输入数据:将初始数据输入移位寄存器。

(3)控制移位:通过控制逻辑,实现数据的逻辑左移操作。

(4)观察结果:使用示波器或逻辑分析仪观察移位寄存器的输出,验证逻辑左移功能。

2. 逻辑右移(SRL)实验(1)搭建电路:将74LS194连接成8位右移寄存器,并添加控制逻辑。

(2)输入数据:将初始数据输入移位寄存器。

(3)控制移位:通过控制逻辑,实现数据的逻辑右移操作。

(4)观察结果:使用示波器或逻辑分析仪观察移位寄存器的输出,验证逻辑右移功能。

3. 算术右移(SRA)实验(1)搭建电路:将74LS194连接成8位算术右移寄存器,并添加控制逻辑。

(2)输入数据:将初始数据输入移位寄存器。

(3)控制移位:通过控制逻辑,实现数据的算术右移操作。

(4)观察结果:使用示波器或逻辑分析仪观察移位寄存器的输出,验证算术右移功能。

五、实验结果与分析1. 逻辑左移实验结果:通过示波器或逻辑分析仪观察移位寄存器的输出,发现数据实现了逻辑左移,验证了逻辑左移功能。

数字电子技术实验4.7 移位寄存器及其应用的Multisim仿真实验

7 SL 2 SR

9 S0 10 S1

1 ~CLR 11 CLK

74LS194D

S1 J1

Key = 1

S0 J2

Key = 0

图4-66 环形计数器仿真电路图

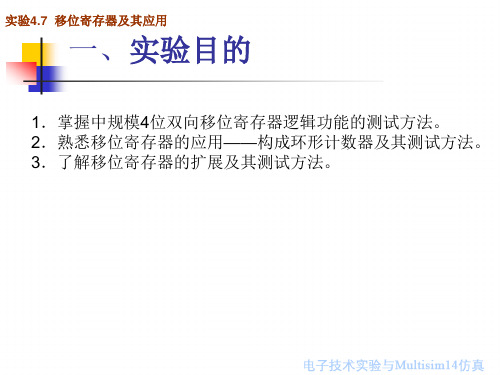

实验4.7 移位寄存器及其应用

五、实验室操作实验内容

1.测试74LS194的逻辑功能 2.环形计数器 3.移位寄存器的扩展

图4-67 扩展后的移位寄存器

实验4.7 移位寄存器及其应用

一、实验目的

1.掌握中规模4位双向移位寄存器逻辑功能的测试方法。 2.熟悉移位寄存器的应用——构成环形计数器及其测试方法。 3.了解移位寄存器的扩展及其测试方法。

实验4.7 移位寄存器及其应用

二、实验设备及材料

1.装有Multisim 14的计算机。 2.数字电路实验箱。 3.数字万用表。 4.74LS194×2。

实验4.7 移位寄存器及其应用

三、实验原理

功能 清除 送数 右移 左移

保持

表4-40 74LS194功能表

输

入

输出

S1 S0 CP SL

SR

D0 D1 D2 D3

Q0

Q1

Q2

Q3

0 ×× × × × ×××× 0

0

0

0

1 11 ↑×× ab cd

a

b

c

d

1

01

↑

×

DSR × × × × DSR

Q0

QA QB QC QD

XLA1

1

F

CQT

图4-63 字信号发生器控制面板图 图4-64 字信号发生器数据控制方式设置

图4-65 74LS194逻辑功能测试波形图

反馈移位型序列信号发生器的设计实验报告

反馈移位型序列信号发生器的设计实验报告引言移位型序列信号发生器是一种能够产生特定序列的电路或设备,其在通信、计算机科学、数字信号处理等领域中有着广泛的应用。

在本实验中,我们设计了一种基于移位寄存器的移位型序列信号发生器,并对其进行了性能测试和分析。

本报告将对该实验的设计、实现和测试结果进行详细说明。

实验设计1.移位寄存器基本原理移位寄存器是一种常用的数字电路元件,其可以实现对二进制数据的移位、存储和输出。

它由若干个触发器组成,每个触发器接收相邻位的信号,并向右或向左移位。

例如,在一个4位移位寄存器中,初始存储的数据为1010,当向右移位时,数据变为0101。

2.移位型序列发生器的基本原理移位型序列发生器是一种利用移位寄存器和异或门构成的电路,用于产生特定的数字序列。

该电路的工作原理如下:将初始数据存储到移位寄存器中,然后依次对寄存器中的每个元素进行移位操作,并将移位后的数据与某个固定的数进行异或运算,得到输出序列的每一位。

例如,一个长度为4的序列发生器,初始数据为1010,异或运算的固定数为0011,则输出序列为1101、1110、0111、1011、0101、1010、1001、0100。

3.实验设计本实验中,我们设计了一个4位移位型序列发生器。

其基本原理如下图所示:图1. 移位型序列发生器电路图该电路由4个D触发器、2个与门和1个异或门组成。

其中,D触发器用于存储移位后的数据,两个与门用于控制移位寄存器的移位方向,异或门用于计算输出序列的每一位。

初始数据为1010,异或运算的固定数为0011。

具体实现过程如下:(1)首先将初始数据1010存储到4个D触发器中。

(2)然后依次进行4次移位操作,每次移位后将移位后的数据输入到异或门中进行计算,并将计算结果存储到一个新的移位寄存器中。

(3)当新的移位寄存器中存储的数据与初始数据相同时,停止计算,输出序列结束。

实验实现根据上述设计原理,我们完成了移位型序列发生器的实现。

基于数据流的视频解码微控制器设计

基于数据流的视频解码微控制器设计阮建国;李陆军【摘要】针对数字视频解码芯片设计中多种视频协议的解析问题,提出一种专用微控制器设计方法.该方法采用面向视频解析的指令集,针对视频解析过程的特点对指令进行特别优化,采用配合该专用微控制器的视频解析模型,较好实现了MPEG1/2、AVS、H.264等视频协议的兼容,保证了解码效率且不会增加芯片面积和功耗.【期刊名称】《计算机工程》【年(卷),期】2010(036)012【总页数】3页(P232-233,241)【关键词】视频解码;解码控制单元;数据流;M叉树【作者】阮建国;李陆军【作者单位】华东理工大学信息科学与工程学院,上海,200237;华东理工大学信息科学与工程学院,上海,200237【正文语种】中文【中图分类】TP3991 概述在数字视频解码芯片的设计中,如何兼容多个视频协议(包括 MPEG1/2、AVS、H.264等)且不过分增加芯片面积和功耗,是芯片设计者必须面对的问题。

目前常用的单芯片兼容多视频解码标准的解决方案有 3种:(1)完全软件实现,即DSP.+MCU 架构[1]。

该方案灵活性强,开发周期短,但由于通用DSP和MCU IP核的成本通常较昂贵,因此不适合单芯片级的实现。

(2)完全由硬件实现[2]。

由于硬件实现不易修改,适应性不强,因此难以做到兼容多种解码协议。

(3)软件和硬件结合实现,即 MCU.+专用硬件[3]。

由于 MCU只负责控制而不负责解析,因此仍然难以实现对多种视频协议解码的支持。

本文提出一种新方法,即设计一个专用 MCU并将其作为视频解码器的一部分,从而利用视频流语法的依赖关系解决单芯片对多种视频协议的支持问题。

2 解码控制单元模型解码控制单元(Decoder Controller Unit, DCU)是一种专用MCU,用于实现视频流的语法解析及语法元素提取。

通过指令执行,DCU可以像普通MCU一样用软件控制流程来操作,以灵活地解析各种视频流语法并尽可能少地改动硬件结构。

《DSP处理器及应用》复习题

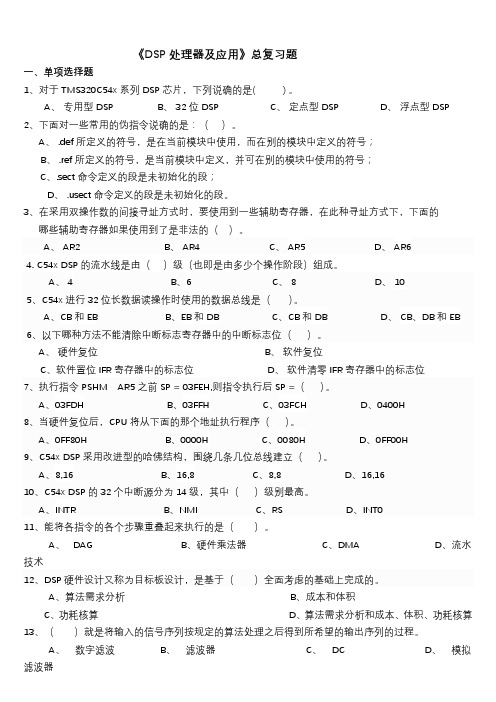

《DSP处理器及应用》总复习题一、单项选择题1、对于TMS320C54x系列DSP芯片,下列说确的是()。

A、专用型DSPB、32位DSPC、定点型DSPD、浮点型DSP2、下面对一些常用的伪指令说确的是:()。

A、.def所定义的符号,是在当前模块中使用,而在别的模块中定义的符号;B、.ref所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

3、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的哪些辅助寄存器如果使用到了是非法的()。

A、AR2B、AR4C、AR5D、AR64.C54x DSP的流水线是由()级(也即是由多少个操作阶段)组成。

A、4B、6C、8D、105、C54x进行32位长数据读操作时使用的数据总线是()。

A、CB和EBB、EB和DBC、CB和DBD、CB、DB和EB6、以下哪种方法不能清除中断标志寄存器中的中断标志位()。

A、硬件复位B、软件复位C、软件置位IFR寄存器中的标志位D、软件清零IFR寄存器中的标志位7、执行指令PSHM AR5之前SP = 03FEH,则指令执行后SP =()。

A、03FDHB、03FFHC、03FCHD、0400H8、当硬件复位后,CPU将从下面的那个地址执行程序()。

A、0FF80HB、0000HC、0080HD、0FF00H9、C54x DSP采用改进型的哈佛结构,围绕几条几位总线建立()。

A、8,16B、16,8C、8,8D、16,1610、C54x DSP的32个中断源分为14级,其中()级别最高。

A、INTRB、NMIC、RSD、INT011、能将各指令的各个步骤重叠起来执行的是()。

A、DAGB、硬件乘法器C、DMAD、流水技术12、DSP硬件设计又称为目标板设计,是基于()全面考虑的基础上完成的。

A、算法需求分析B、成本和体积C、功耗核算D、算法需求分析和成本、体积、功耗核算13、()就是将输入的信号序列按规定的算法处理之后得到所希望的输出序列的过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

桶形移位器

一、题目要求:实现8位二进制数左循环、右循环、左逻辑、右逻辑、左算术、右算术这六种功能。

二、分析与实现:利用:Y(i+n)=X(i) (i+n<16)来实现移位(左)。

逻辑和算术,则对没移位的位的补0(或1);循环(左),则再利用公式Y(i+n-16)=X(i),即可把没移位的位进行桶形移位。

按以上分析,其VHDL代码如下:

entity barral_shift_16 is

port(x:in std_logic_vector(15 downto 0); --输入数据

l_cycle,l_logic,l_arithmetic:in std_logic; --分别为左循环,左移位,左算术

r_cycle,r_logic,r_arithmetic:in std_logic; --分别为右循环,右移位,右算术

n:in std_logic_vector(3 downto 0); --移的位数

y:out std_logic_vector(15 downto 0)); --结果

end barral_shift_16;

architecture Behavioral of barral_shift_16 is

begin

process(x,l_cycle,l_logic,l_arithmetic,r_cycle,r_logic,r_arithmetic,n)

variable temp_y:std_logic_vector(15 downto 0);

variable m:integer;

begin

m:=conv_integer(n);

-------------------------左循环--------------------------------------

if(l_cycle='1')then

for i in 0 to 15 loop

if(i+m<=15)then

temp_y(i+m):=x(i);

else

temp_y(i+m-16):=x(i);

end if;

end loop;

-------------------------左逻辑--------------------------------------

elsif(l_logic='1')then

for i in 0 to 15 loop

if(i+m<=15)then

temp_y(i+m):=x(i);

end if;

end loop;

temp_y(m-1 downto 0):=(others=>'0');

-------------------------左算术--------------------------------------

elsif(l_arithmetic='1')then

for i in 0 to 15 loop

if(i+m<=15)then

temp_y(i+m):=x(i);

end if;

end loop;

temp_y(m-1 downto 0):=(others=>x(0));

-------------------------右循环--------------------------------------

elsif(r_cycle='1')then

for i in 15 downto 0 loop

if(i-m>=0)then

temp_y(i-m):=x(i);

else

temp_y(16+i-m):=x(i);

end if;

end loop;

-------------------------右逻辑--------------------------------------

elsif(r_logic='1')then

for i in 15 downto 0 loop

if(i-m>=0)then

temp_y(i-m):=x(i);

end if;

end loop;

temp_y(15 downto 16-m):=(others=>'0');

-------------------------右算术--------------------------------------

elsif(r_arithmetic='1')then

for i in 15 downto 0 loop

if(i-m>=0)then

temp_y(i-m):=x(i);

end if;

end loop;

temp_y(15 downto 16-m):=(others=>x(15)); ---------------------------------------------------------------------

end if;

y<=temp_y;

end process;

end Behavioral;

三、仿真结果

与期望值一致,结果正确。

左循环右循环

左逻辑右逻辑

左算术右算术。