CMOS System-on-a-Chip Voltage Scaling Beyond 50nm

modern system-on-chip design on arm 笔记

modern system-on-chip design on arm 笔记Modern system-on-chip (SoC) design on ARM involves the integration of multiple components onto a single chip, enabling high-performance computing in a compact and power-efficient package. In this note, we will explore some key aspects of SoC design on ARM.1. Architecture: ARM provides a range of processor architectures, such as ARM Cortex-A, Cortex-R, and Cortex-M, each catering to different application requirements. SoC designers need to select the appropriate architecture based on factors like performance, power consumption, and real-time processing capabilities.2. Integration of Components: SoC design involves integrating various components like the processor core, memory subsystem, peripherals, and interfaces onto a single chip. This integration enables efficient communication between different components, reducing latency and power consumption.3. Power Management: Power management is a critical aspect of SoC design, as modern devices demand high performance while maintaining long battery life. SoC designers use techniques like power gating, clock gating, and voltage-frequency scaling to optimize power consumption in different operating modes.4. Security: With the increasing connectivity of devices, SoC design needs to prioritize security. ARM provides TrustZone technology, enabling the isolation of secure and non-secure software and protecting sensitive data from unauthorized access. SoC designers need to incorporate security features and developrobust encryption and authentication mechanisms.5. Verification and Validation: SoC designers undertake rigorous verification and validation processes to ensure the correct functioning of the integrated components. This involves testing the system for diverse scenarios, corner cases, and performance benchmarks. Advanced verification techniques like simulation, formal verification, and emulation are utilized to detect and fix design flaws.6. Software Development: SoC designers work closely with software developers to optimize software architecture for the specific SoC design. This collaboration involves developing device drivers, firmware, and operating systems that leverage the hardware capabilities effectively.7. Packaging and Manufacturing: Once the SoC design is finalized, it needs to be packaged and manufactured. The packaging involves integrating the chip into a package with appropriate interconnects and thermal management. The manufacturing process includes wafer fabrication, die testing, and final assembly.In conclusion, modern SoC design on ARM involves selecting the right processor architecture, integrating components, optimizing power consumption, ensuring security, thorough verification and validation, software development, and packaging/manufacturing. All these aspects collectively contribute to the successful deployment of efficient and high-performance ARM-based SoCs.。

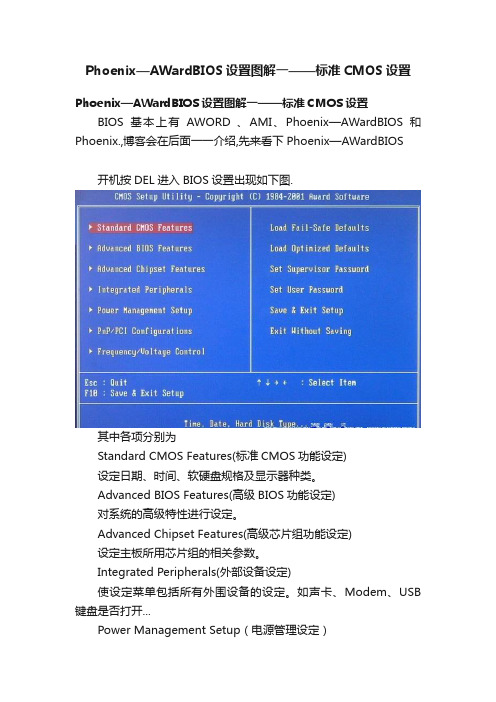

Phoenix—AWardBIOS设置图解一——标准CMOS设置

Phoenix—AWardBIOS设置图解一——标准CMOS设置Phoenix—AWardBIOS设置图解一——标准CMOS设置BIOS基本上有AWORD 、AMI、Phoenix—AWardBIOS和Phoenix.,博客会在后面一一介绍,先来看下Phoenix—AWardBIOS开机按DEL进入BIOS设置出现如下图.其中各项分别为Standard CMOS Features(标准CMOS功能设定)设定日期、时间、软硬盘规格及显示器种类。

Advanced BIOS Features(高级BIOS功能设定)对系统的高级特性进行设定。

Advanced Chipset Features(高级芯片组功能设定)设定主板所用芯片组的相关参数。

Integrated Peripherals(外部设备设定)使设定菜单包括所有外围设备的设定。

如声卡、Modem、USB 键盘是否打开...Power Management Setup(电源管理设定)设定CPU、硬盘、显示器等设备的节电功能运行方式。

PNP/PCI Configurations(即插即用/PCI参数设定)设定ISA的PnP即插即用介面及PCI介面的参数,此项仅在您系统支持PnP/PCI时才有效。

Frequency/Voltage Control(频率/电压控制)设定CPU的倍频,设定是否自动侦测CPU频率等。

Load Fail-Safe Defaults(载入最安全的缺省值)使用此菜单载入工厂默认值作为稳定的系统使用。

Load Optimized Defaults(载入高性能缺省值)使用此菜单载入最好的性能但有可能影响稳定的默认值。

Set Supervisor Password(设置超级用户密码)使用此菜单可以设置超级用户的密码。

Set User Password(设置用户密码)使用此菜单可以设置用户密码。

Save & Exit Setup(保存后退出)保存对CMOS的修改,然后退出Setup程序。

英语作文-探索集成电路设计的未来趋势与发展方向

英语作文-探索集成电路设计的未来趋势与发展方向Exploring the Future Trends and Development Directions of Integrated Circuit Design。

In recent years, the field of integrated circuit (IC) design has witnessed rapid advancements and breakthroughs. As the backbone of modern technology, ICs are essential components in various electronic devices, ranging from smartphones and computers to medical equipment and automotive systems. In this article, we will explore the future trends and development directions of IC design, focusing on three key aspects: miniaturization, power efficiency, and functional integration.First and foremost, miniaturization is a fundamental trend in IC design. Over the years, the size of ICs has continuously decreased, leading to the development of smaller and more powerful electronic devices. This trend is expected to continue in the future, with the demand for compact and portable devices on the rise. To achieve miniaturization, designers need to overcome various challenges, such as reducing power consumption, improving heat dissipation, and enhancing signal integrity. Advanced fabrication technologies, such as nanoscale lithography and 3D integration, will play a crucial role in enabling further miniaturization of ICs.Secondly, power efficiency is another important aspect of IC design. With the increasing demand for energy-saving devices and the growing concern for environmental sustainability, power efficiency has become a key consideration in IC design. Designers are constantly exploring new techniques to reduce power consumption without compromising performance. This includes the use of low-power design methodologies, such as voltage scaling, clock gating, and power gating, as well as the integration of power management circuits. Additionally, the development of energy harvesting technologies, such as solar cells and wireless charging, presents opportunities for further improving the power efficiency of ICs.Lastly, functional integration is a significant direction for the future of IC design. Traditionally, ICs were designed to perform specific functions, such as processing, memory, or communication. However, the increasing complexity of electronic systems demands higher levels of integration. Designers are now focusing on integrating multiple functions onto a single chip, leading to the development of system-on-chip (SoC) and system-in-package (SiP) solutions. This trend enables the creation of more versatile and compact devices, as well as the realization of emerging technologies like internet of things (IoT) and artificial intelligence (AI). To achieve functional integration, designers need to address challenges related to interconnectivity, power distribution, and thermal management.In conclusion, the future of IC design is characterized by miniaturization, power efficiency, and functional integration. These trends are driven by the demand for smaller, more energy-efficient, and multifunctional electronic devices. To stay at the forefront of IC design, designers need to embrace advanced fabrication technologies, explore innovative power-saving techniques, and focus on integrating multiple functions onto a single chip. By doing so, they can contribute to the development of cutting-edge technologies and shape the future of the electronics industry.。

单片机篮球计分器毕业论文中英文资料外文翻译文献

单片机篮球计分器外文翻译一英文原文:DescriptionThe AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash Programmable and Erasable Read Only Memory (PEROM) and 128 bytes RAM. The device is manufactured using Atmel’s high density nonvolatile memory technology and is compatible with the industry standardMCS-51™ instruction set and pinout. The chip combines a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C51 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications.Features:• Compatible with MCS-51™ Products• 4K Bytes of In-System Reprogrammable Flash Memory• Endurance: 1,000 Write/Erase Cycles• Fully Static Operation: 0 Hz to 24 MHz• Th ree-Level Program Memory Lock• 128 x 8-Bit Internal RAM• 32 Programmable I/O Lines• Two 16-Bit Timer/Counters• Six Interrupt Sources• Programmable Serial Channel• Low Power Idle and Power Down ModesThe AT89C51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset. Pin Description:VCC Supply voltage.GND Ground.Port 0Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When is are written to port 0 pins, the pins can be used as high impedance inputs.Port 0 may also be configured to be the multiplexed loworder address/data bus during accesses to external program and data memory. In this mode P0 has internal pullups.Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pullups are required during program verification.Port 1Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups.Port 3 also serves the functions of various special features of the AT89C51 as listed below:receives somecontrol signals forFlash programmingand verification.RSTReset input. Ahigh on this pin fortwo machine cycles while the oscillator is running resets the device.ALE/PROGAddress Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSENProgram Store Enable is the read strobe to external program memory.When the AT89C51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPPExternal Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset.EA should be strapped to VCC for internal program executions.This pin also receives the 12-volt programming enable voltage(VPP) during Flash programming, for parts that require 12-volt VPP.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively, of an invertingamplifier which can be configured for use as an on-chip oscillator, as shown in Figure1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through adivide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.Idle ModeIn idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to aport pin or to external memory.二中文翻译:AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4Kbytes的快速可擦写的只读程序存储器(PEROM)和128 bytes 的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51产品指令系统,片内置通用8位中央处理器(CPU)和flish 存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

常用集成电路名词缩写

PLCC Plastic Leaded Chip Carrier

PLE Physical Layout Estimator

PLI Programming Language Interface

PLL Phase Locked Loop

POP Process Oriented Programming

PPA Performance,Power,Area

APR Auto place and route

ARM Advanced RISC Machines

ASB ASCII ASIC

Advanced System Bus

American standard code for information interchange

Application Special Integrated Circuit

DVE Discovery Visualization Environment

DVFS Dynamic Voltage Frequency Scaling

DVR Design Rule Violation

DVT Design verification test

ECC Error Correcting Code

CTL Computation tree logic

CTS Clock Tree Synthesis

DAC Digital-to-Analog Converter

DC Design compiler

DCM Digital Clock Manager

DCT Discrete cosine transform

SEB Single Event Burnout

SEE Single Event Effect

半导体物理与器件物理

半导体物理、材料、工艺 半导体器件物理 集成电路工艺 集成电路设计和测试 微系统,系统

微电子学发展的特点

向高集成度、高性能、低功耗、高可靠性电路方向发展 与其它学科互相渗透,形成新的学科领域: 光电集成、MEMS、生物芯片

半导体概要

固体材料:绝缘体、半导体、导体 (其它:半金属,超导体)

MEM

Math

Bus

Controller

IO

Graphics

PCB集成 工艺无关

系统

亚微米级工艺 依赖工艺 基于标准单元互连 主流CAD:门阵列 标准单元

集成电路芯片

世纪之交的系统设计

SYSTEM-ON-A-CHIP

深亚微米、超深亚 微米级工艺 基于IP复用 主流CAD:软硬件协 同设计

1970

1980

1990

2000

2010

存储器容量 60%/年 每三年,翻两番

1965,Gordon Moore 预测 半导体芯片上的晶体管数目每两年翻两番

1.E+9 1.E+8 1.E+7 1.E+6 1.E +5 1.E+4 1.E+3

’70 ’74 ’78 ’82 ’86 ’90 ’94 ’98 ’2002

Pentium II: 7,500,000

微处理器的性能

100 G 10 G Giga 100 M 10 M Mega Kilo

1970 1980 1990 2000 2010

Peak Advertised Performance (PAP)

Moore’s Law

Real Applied Performance (RAP) 41% Growth

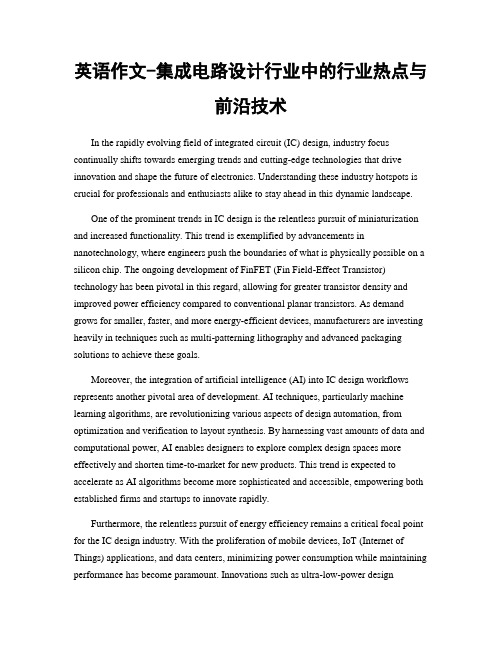

英语作文-集成电路设计行业中的行业热点与前沿技术

英语作文-集成电路设计行业中的行业热点与前沿技术In the rapidly evolving field of integrated circuit (IC) design, industry focus continually shifts towards emerging trends and cutting-edge technologies that drive innovation and shape the future of electronics. Understanding these industry hotspots is crucial for professionals and enthusiasts alike to stay ahead in this dynamic landscape.One of the prominent trends in IC design is the relentless pursuit of miniaturization and increased functionality. This trend is exemplified by advancements in nanotechnology, where engineers push the boundaries of what is physically possible on a silicon chip. The ongoing development of FinFET (Fin Field-Effect Transistor) technology has been pivotal in this regard, allowing for greater transistor density and improved power efficiency compared to conventional planar transistors. As demand grows for smaller, faster, and more energy-efficient devices, manufacturers are investing heavily in techniques such as multi-patterning lithography and advanced packaging solutions to achieve these goals.Moreover, the integration of artificial intelligence (AI) into IC design workflows represents another pivotal area of development. AI techniques, particularly machine learning algorithms, are revolutionizing various aspects of design automation, from optimization and verification to layout synthesis. By harnessing vast amounts of data and computational power, AI enables designers to explore complex design spaces more effectively and shorten time-to-market for new products. This trend is expected to accelerate as AI algorithms become more sophisticated and accessible, empowering both established firms and startups to innovate rapidly.Furthermore, the relentless pursuit of energy efficiency remains a critical focal point for the IC design industry. With the proliferation of mobile devices, IoT (Internet of Things) applications, and data centers, minimizing power consumption while maintaining performance has become paramount. Innovations such as ultra-low-power designtechniques, adaptive voltage scaling, and on-chip power management units are instrumental in meeting these challenges. Additionally, emerging technologies like silicon photonics offer promising avenues for reducing power consumption in high-speed interconnects, paving the way for future generations of energy-efficient computing systems.In parallel, the industry is witnessing significant advancements in specialized IC design for niche applications. Fields such as biomedical electronics, automotive electronics, and quantum computing demand tailored solutions that go beyond traditional CMOS (Complementary Metal-Oxide-Semiconductor) technologies. These specialized ICs often require stringent reliability, low noise, and high sensitivity, prompting innovations in materials, device architectures, and fabrication techniques. As these sectors expand, they drive cross-disciplinary collaborations and inspire novel approaches to IC design that cater to specific application requirements.Looking ahead, the convergence of these trends underscores a transformative era in IC design, characterized by unprecedented levels of integration, intelligence, and efficiency. As researchers and engineers continue to push boundaries, the industry's landscape will continue to evolve, fueled by innovations that redefine what is possible with semiconductor technology. Embracing these advancements and anticipating future developments will be essential for stakeholders seeking to navigate and capitalize on the opportunities presented by the dynamic field of integrated circuit design.。

英语作文-掌握集成电路设计中的关键技术与方法

英语作文-掌握集成电路设计中的关键技术与方法Integrated Circuit (IC) design plays a pivotal role in modern electronics, serving as the foundation for virtually all electronic devices we use today. Mastering the key techniques and methods in IC design is crucial for engineers and researchers in this field. This article explores the essential aspects of IC design, highlighting the methodologies and technologies that drive innovation and efficiency in this complex discipline.### Understanding IC Design Fundamentals。

At its core, IC design involves the creation of miniature electronic circuits that integrate thousands to billions of components onto a single semiconductor chip. This integration enables devices to perform complex functions while minimizing size and power consumption. The process begins with conceptualizing the circuit's functionality and architecture, followed by detailed design and verification stages.### Key Stages in IC Design。

半导体物理与器件英语

半导体物理与器件英语Semiconductor Physics and DevicesThe field of semiconductor physics and devices is a crucial aspect of modern technology, as it underpins the development of a wide range of electronic devices and systems that have transformed our daily lives. Semiconductors, which are materials with electrical properties that lie between those of conductors and insulators, have been the backbone of the digital revolution, enabling the creation of integrated circuits, transistors, and other essential components found in smartphones, computers, and a myriad of other electronic devices.At the heart of semiconductor physics is the study of the behavior of electrons and holes within these materials. Electrons, which are negatively charged particles, and holes, which are the absence of electrons and carry a positive charge, are the fundamental charge carriers in semiconductors. The interactions and movement of these charge carriers within the semiconductor lattice structure are governed by the principles of quantum mechanics and solid-state physics.One of the fundamental concepts in semiconductor physics is theenergy band structure. Semiconductors have a unique energy band structure, with a filled valence band and an empty conduction band separated by an energy gap. The size of this energy gap determines the semiconductor's electrical properties, with materials having a smaller energy gap being more conductive than those with a larger gap.The ability to manipulate the energy band structure and the behavior of charge carriers in semiconductors has led to the development of a wide range of electronic devices. The most prominent of these is the transistor, a fundamental building block of modern electronics. Transistors are used to amplify or switch electronic signals and power, and they are the essential components in integrated circuits, which are the heart of digital devices such as computers, smartphones, and various other electronic systems.Another important class of semiconductor devices are diodes, which are two-terminal devices that allow the flow of current in only one direction. Diodes are used in a variety of applications, including power supplies, rectifiers, and light-emitting diodes (LEDs). LEDs, in particular, have become ubiquitous in modern lighting and display technologies, offering improved energy efficiency, longer lifespan, and enhanced color quality compared to traditional incandescent and fluorescent light sources.Semiconductor devices are not limited to electronic applications; they also play a crucial role in optoelectronics, a field that deals with the interaction between light and electronic devices. Photodetectors, such as photodiodes and phototransistors, are semiconductor devices that convert light into electrical signals, enabling a wide range of applications, including imaging, optical communication, and solar energy conversion.The development of semiconductor physics and devices has been a continuous process, driven by the relentless pursuit of improved performance, efficiency, and functionality. Over the past several decades, we have witnessed remarkable advancements in semiconductor technology, with the miniaturization of devices, the introduction of new materials, and the development of innovative device architectures.One of the most significant trends in semiconductor technology has been the scaling of transistor dimensions, often referred to as Moore's Law. This observation, made by Intel co-founder Gordon Moore in 1965, predicted that the number of transistors on a microchip would double approximately every two years, leading to a dramatic increase in computing power and a corresponding decrease in device size and cost.This scaling has been achieved through a combination ofadvancements in fabrication techniques, material engineering, and device design. For example, the use of high-k dielectric materials and the implementation of FinFET transistor architectures have allowed for continued scaling of transistor dimensions while maintaining or improving device performance and power efficiency.Beyond the scaling of individual devices, the integration of multiple semiconductor components on a single integrated circuit has led to the development of increasingly complex and capable electronic systems. System-on-a-chip (SoC) designs, which incorporate various functional blocks such as processors, memory, and input/output interfaces on a single semiconductor die, have become ubiquitous in modern electronic devices, enabling greater functionality, reduced power consumption, and improved overall system performance.The future of semiconductor physics and devices holds immense promise, with researchers and engineers exploring new materials, device architectures, and application domains. The emergence of wide-bandgap semiconductors, such as silicon carbide (SiC) and gallium nitride (GaN), has opened up new possibilities in high-power, high-frequency, and high-temperature electronics, enabling advancements in areas like electric vehicles, renewable energy systems, and communication networks.Additionally, the integration of semiconductor devices with otheremerging technologies, such as quantum computing, neuromorphic computing, and flexible/wearable electronics, is paving the way for even more transformative applications. These developments have the potential to revolutionize fields ranging from healthcare and transportation to energy and communication, ultimately enhancing our quality of life and shaping the technological landscape of the future.In conclusion, the field of semiconductor physics and devices is a cornerstone of modern technology, underpinning the development of a vast array of electronic devices and systems that have become indispensable in our daily lives. The continuous advancements in this field, driven by the relentless pursuit of improved performance, efficiency, and functionality, have been instrumental in driving the digital revolution and shaping the technological landscape of the21st century. As we move forward, the future of semiconductor physics and devices promises even more remarkable innovations and transformative applications that will continue to shape our world.。

cmos设置中英文对照

按下“Del”键后,就可以看到CMOS Setup主菜单,不同厂家机子可能进入COMS的按键会不同有的是F1或F2Enter键:选择当前项目,Esc键:返回,F1功能键:显示目前设置项目的相关说明1、Standard CMOS Features(标准CMOS功能设置):主要是设置IDE硬盘的种类,还要设置日期、时间、软驱规格及显示卡的种类。

2、Advanced BIOS Features(高级BIOS功能设置)Anti-Virus Protection (是否打开病毒保护,对IDE硬盘的引导扇区进行保护):装系统时改为“Disabled”CPU Internal Cache (是否打开CPU内置高速缓存):为“Enabled”External Cache (是否打开外部高速缓存):为“Enabled”CPU L2 Cache ECC Checking(CPU二级高速缓存奇偶校验):为“Enabled”Processor Number Feature(处理器序列号):为“Enabled”Fast Boot(快速启动):设为“Enabled”Quick Post(快速开机自检,是否进行内存测试):为“Disabled”Quick Power On Self Test(快速开机自检):为“Enabled”limit cpuid maxval(处理器ID最大值) : 开启支持较旧的操作系统的处理器ID,建议为“Disabled”。

HDD Change Message(提示硬盘讯息):First Boot Device(第一个优先启动的开机设备)Second Boot Device(第二个启动的开机设备)Third Boot Device(第三个启动的开机设备)Boot Other Device(其他启动设备)Swap Floppy Drive(交换软驱代号):为“Disabled”Boot Up Floppy Seek(开机时测试软驱):为“Disabled”Boot Up NumLock Status(初始数字小键盘的锁定状态):为“On”Gate A20 Option(A20门选择):为“Normal”时,A20信号由键盘控制,缺省值为“Fast”Typematic Rate Setting(是否启用击键速率设置):为“Disabled”Security Option(检查密码方式):为“System”和“Setup”,要先设置密码。

映泰A770L3主板 BIOS说明书

3.1

跳线安装 ...........................................................................................12

3.2

安装细节 ...........................................................................................12

第五章: 帮助信息 ......................................................... 19

5.1

驱动程序安装注意事项 ...................................................................19

1.2 附件

HDD 数据线 X 1(可选) Serial ATA 数据线 X 2 ATX 机箱后置 I/O 面板 X 1 用户手册 X 1 驱动光盘 X 1 Serial ATA 电源线 X 1(可选) FDD 数据线 X 1 (可选) USB 2.0 数据线 X1 (可选)

x1

支持 PCI-E Gen2 x16 扩展卡

插槽

PCI Express Gen2 x1 插槽

x1

支持 PCI-E Gen2 x1 扩展卡

PCI 插槽

x3

支持 PCI 扩展卡

板载接口

软驱接口 打印机接口 IDE接口

x1

每个接口支持2个软驱

x1

每个接口支持1个打印机端口

x1

每个接口支持2个IDE设备

SATA 接口

x4

每个接口支持1个SATA设备

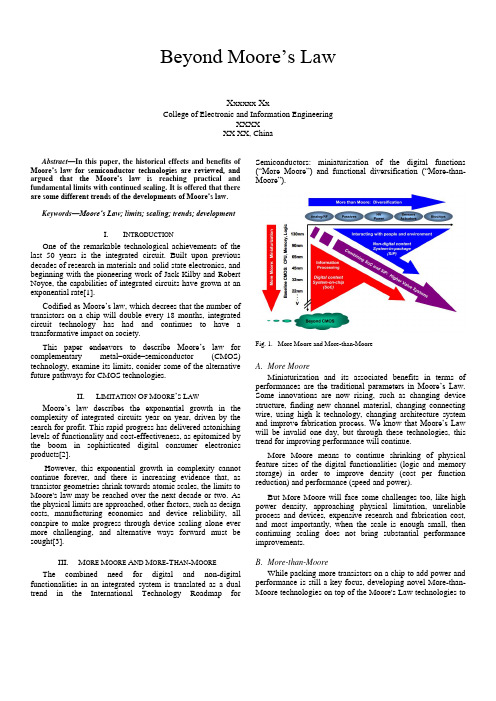

Beyond_Moore's_Law

Beyond Moore’s LawXxxxxx XxCollege of Electronic and Information EngineeringXXXXXX XX, ChinaAbstract—In this paper, the historical effects and benefits of Moore’s law for semiconductor technologies are reviewed, and argue d that the Moore’s law is reaching practical and fundamental limits with continued scaling. It is offered that there are some different trends of the developments of Moore’s law.Keywords—Moore’s Law; limits; scaling; trends; developmentI.I NTRODUCTIONOne of the remarkable technological achievements of the last 50 years is the integrated circuit. Built upon previous decades of research in materials and solid state electronics, and beginning with the pioneering work of Jack Kilby and Robert Noyce, the capabilities of integrated circuits have grown at an exponential rate[1].Codified as Moore’s law, which decrees that the number of transistors on a chip will double every 18 months, integrated circuit technology has had and continues to have a transformative impact on society.This paper endeavors to describe Moore’s law for complementary metal–oxide–semiconductor (CMOS) technology, examine its limits, conider some of the alternative future pathways for CMOS technologies.II.L IMITATION O F M OORE’S L AWMoore’s law describes the exponentia l growth in the complexity of integrated circuits year on year, driven by the search for profit. This rapid progress has delivered astonishing levels of functionality and cost-effectiveness, as epitomized by the boom in sophisticated digital consumer electronics products[2].However, this exponential growth in complexity cannot continue forever, and there is increasing evidence that, as transistor geometries shrink towards atomic scales, the limits to Moore's law may be reached over the next decade or two. As the physical limits are approached, other factors, such as design costs, manufacturing economics and device reliability, all conspire to make progress through device scaling alone ever more challenging, and alternative ways forward must be sought[3].III.M ORE M OORE A ND M ORE-T HAN-M OORE The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the International Technology Roadmap for Semiconductors: miniaturization of the digital functions (“More Moore”) and functional diversification (“More-than-Moore”).Fig. 1.More Moore and More-than-MooreA.More MooreMiniaturization and its associated benefits in terms of performances are the traditional parameters in Moore’s Law. Some innovations are now rising, such as changing device structure, finding new channel material, changing connecting wire, using high k technology, changing architecture system and improve fabrication process. We know that Moore’s Law will be invalid one day, but through these technologies, this trend for improving performance will continue.More Moore means to continue shrinking of physical feature sizes of the digital functionalities (logic and memory storage) in order to improve density (cost per function reduction) and performance (speed and power).But More Moore will face some challenges too, like high power density, approaching physical limitation, unreliable process and devices, expensive research and fabrication cost, and most importantly, when the scale is enough small, then continuing scaling does not bring substantial performance improvements.B.More-than-MooreWhile packing more transistors on a chip to add power and performance is still a key focus, developing novel More-than-Moore technologies on top of the Moore's Law technologies toprovide further values to semiconductor chips has also becomea more important issue.More-than-Moore means that Incorporation into devices offunctionalities that do not necessarily scale according to “M oore’s L aw”, but provide addition al value in different ways.More-than-Moore approach allows for the non-digitalfunctionalities to migrate from the system board-level into thepackage (sip) or onto the chip (soc).The second trend is characterized by functionaldiversification of semiconductor-based devices. These non-digital functionalities do contribute to the miniaturization ofelectronic systems, although they do not necessarily scale at the same rate as the one that describes the development of digital functionality. Consequently, in view of added functionality, this trend may be designated “More-than-Moore” (MtM).But we will face some problems by using the technologies of More-than-Moore. Such as integration of More Moore with More-than-Moore and Creation of intelligent compact systems.More-than-Moore technologies cover a wide range of fields. For example, MEMS applications include sensors, actuators and ink jet printers. RF CMOS applications include Bluetooth, GPS and Wi-Fi. CMOS image sensors are found in most digital cameras. High voltage drivers are used to power LED lights. These applications add value to computing and memory devices that are made from the traditional Moore's Law technology.Fig. 2.2007 ITRS “Moore’s Law and More” Definition Graphic Proposal Fig.2 is a definition of “Moore’s Law and More”. The red part is More Moore and the blue part is More-than-Moore. The red part contains the computing and data storage logic, while the blue part contains RF, HH Power, Passives, Sensors, Actuators, Bio-chips, Fluidics and other functionalities.parisonComparing More Moore and More-than-Moore from Fig.3 and Fig.4, we can draw some conclusions:•More Moore has smallest footprint but limited functionality.•More-than-Moore has full functionality but complex supple chain.They all have advantages and disadvantages. We can use them according to specific application. Fig. 3.Following Moore’s Law is one approach:Monolithic CMOS logic System-on-ChipFig. 4.Adding More-than-Moore is another: System-on-Chip and System-in-PackageIn modern society, the concept of Internet of Things is verypopular. In the past, people may pay attention to computingand storage more, so the IC industry develops rapidly following Moore’s Law. But now, people pay more attention tointernet of things, biomedical and so on. That is to say, peopleneed more demands of the IC besides the computing andstorage functionality.Fig. 5.An ideal application of More-than-MooreFig.5 is an example of More-than-Moore, of course, it is anideal application. But it shows some benefits of this trend.IV.B EYOND C MOSA.What is Beyond CMOSWhat we have talked about before is all based on Si-based CMOS technology. But we should realize that Si-based CMOS technology cannot do everything, especially when the transistors continue shrinking of physical feature sizes towards atomic scale.Fig. 6.More Moore, More-than-Moore and Beyond CMOSWhat More Moore do is to continue to go forward along the road of “Moore’s Law”. And More-than-Moore do is to d evelop and extend “Moore’s Law”. When the scaling bellows about 10nm, traditional Si-based CMOS technology may be invalid. So what Beyond CMOS want to do is to invent new devices or technologies when Si-based CMOS comes across its limitation.Fig. 7.Some new devices and technologyThe main idea of Beyond CMOS is to invent one or several new type switches which can replace the Si-based CMOS to process information. So these ideal devices need to have higher function density, higher performance, less power consumption, acceptable manufacturing cost, stable enough and suitable for large-scale manufacturing and so on.B.Several new devices1)Tunneling FET(TFET)TFET mainly according to the principle of tunneling of quantum mechanics, directly goes through channel from the source to drain rather than by diffusion. Fig. 8.Tunneling FET(TFET)2)Quantum Cellular Automata (QCA)Representing the binary information by changing the structure of the Cellular.Transmitting information based on neighbor interaction.Fig. 9.Quantum Cellular Automata (QCA)Fig. 10.Quantum Cellular Automata (QCA)3)Atomic Switch(QCA)Atomic switch based on the formation and the annihilation of the metal atoms bridge between the two electrons, forming a gate-control switch mode.Fig. 11.Atomic Switch4)SpinFETSpinFET use the spinning direction of electron to carry information.Fig. 12.SpinFETFig. 13.SpinFETThey all have advantages or dis advantages. Maybe they are not the best devices, but they represent the potential development trend of the devices in the future[4].V.S UMMARYMicroelectronics therefore seeks to develop in new ways, not only to continue to deliver better performance in traditional markets, but also to grow into new markets based on devising new, non-electronic, functions on integrated circuits.Microelectronics relies on complementary metal oxide semiconductor (CMOS) technology, the backbone of the electronics industry. Beyond Moore's law, it is foreseen that microelectronics will be a platform to support optical, chemical and biotechnology to deliver a step change beyond electronics-only integration.R EFERENCES[1]Cavin R K, Lugli III P, Zhirnov V V. Science and engineering beyondMoore's law[J]. Proceedings of the IEEE, 2012, 100(Special Centennial Issue): 1720-1749.[2]Cumming D R S, Furber S B, Paul D J. Beyond Moore's law[J].Philosophical transactions. Series A, Mathematical, physical, and engineering sciences, 2014, 372(2012).[3]Saraswat K C. How far can we push Si CMOS and what are thealternatives for future ULSI[C]//Device Research Conference (DRC), 2014 72nd Annual. IEEE, 2014: 3-4.[4]Kazior T E. Beyond CMOS: heterogeneous integration of III–V devices,RF MEMS and other dissimilar materials/devices with Si CMOS to create intelligent microsystems[J]. Philosophical Transactions of the Royal Society of London A: Mathematical, Physical and Engineering Sciences, 2014, 372(2012): 20130105.。

Full On-Chip CMOS Low Dropout Voltage Regulator

Zouak Mouhcine

Electrical Engineering Department Faculty of sciences and technology Fez, Morocco doyen@fst-usmba.ac.ma

Abstract— In This paper, we presents a full on-chip and area efficient low-dropout voltage regulator (LDO) which, exploiting the technique nested miller compensation with active capacitor(NMCAC) to eliminate the external capacitor without compromising the stability of the system in the full output current range. The external capacitor is removed allowing for greater power system integration for system on-chip applications. The proposed LDO is that provides a fast transient response, a low quiescent current 51 µA with a dropout voltage of 192 mV and output variation 69 mV when a full load step 0-50 mA is applied. It designed in 0.18 µm CMOS process.

英语作文-如何进行集成电路设计中的电源管理与优化

英语作文-如何进行集成电路设计中的电源管理与优化Power management and optimization in integrated circuit (IC) design is crucial for achieving efficient and reliable performance. It encompasses a variety of techniques and considerations aimed at ensuring that the power supply to the IC is managed effectively, thereby optimizing its overall operation. This article delves into the key strategies and methodologies employed in the field of power management within IC design.Firstly, it's essential to understand the significance of power management in ICs. Integrated circuits are ubiquitous in modern electronics, ranging from microprocessors in computers to sensors in IoT devices. These ICs require a stable and efficient power supply to function correctly. Effective power management not only prolongs battery life in portable devices but also reduces heat dissipation and improves overall system reliability.One of the primary objectives in power management is minimizing power consumption without compromising performance. This involves careful design considerations from the early stages of IC development. Techniques such as voltage scaling, where the operating voltage of the IC is adjusted based on the workload, play a crucial role. By dynamically adjusting the voltage levels, power consumption can be reduced during periods of low activity, thereby conserving energy.Furthermore, optimizing power distribution within the IC is essential. Power delivery networks (PDNs) are designed to ensure that the supply voltage remains stable across the IC, despite varying load conditions. Techniques like power gating and isolation help in selectively powering down specific parts of the IC when not in use, thereby reducing static power dissipation.Another critical aspect of power management is the efficient use of on-chip regulators and converters. These components are responsible for converting the external power supply to the required voltages and currents suitable for the IC's operation.Advanced techniques such as switch-mode power supplies (SMPS) and low-dropout regulators (LDOs) are employed to minimize power loss and improve efficiency.Moreover, the design of efficient clocking circuits is essential for power optimization. Clock gating techniques ensure that clock signals are disabled in parts of the IC that are idle, reducing unnecessary switching activities and hence power consumption. Additionally, employing advanced clock distribution networks helps in minimizing clock skew and reducing power dissipation due to clock signal routing.Thermal management is another critical consideration in power optimization. Excessive heat generation can degrade the performance and reliability of ICs. Techniques such as thermal-aware floorplanning and layout optimization help in distributing heat evenly and dissipating it effectively through heat sinks or other cooling mechanisms.In addition to hardware-level optimizations, software plays a vital role in power management. Power-aware algorithms and scheduling policies can significantly impact the overall energy efficiency of the system. Techniques like dynamic voltage and frequency scaling (DVFS) at the software level enable real-time adjustments to power consumption based on workload demands.Furthermore, comprehensive simulation and analysis tools are employed throughout the design process to predict and optimize power consumption. Tools such as SPICE (Simulation Program with Integrated Circuit Emphasis) enable designers to simulate the electrical behavior of the IC and validate power management strategies before fabrication.In conclusion, effective power management and optimization are indispensable aspects of modern IC design. By implementing techniques such as voltage scaling, power gating, efficient regulator design, clock gating, thermal management, and power-aware algorithms, designers can achieve significant improvements in energy efficiency and overall performance. As technology advances and demands for energy-efficient electronics grow, continuous innovation in power management techniques will remain critical for the development of next-generation integrated circuits.。

英语作文-揭秘集成电路设计中的功耗分析与优化方法

英语作文-揭秘集成电路设计中的功耗分析与优化方法Power analysis and optimization in integrated circuit (IC) design is a critical aspect that influences both the performance and efficiency of electronic devices. As technology advances, demands for lower power consumption in ICs have become increasingly stringent, driven by factors such as battery life in mobile devices, heat dissipation in high-performance computing, and environmental concerns. In this article, we will delve into various methods and strategies employed in the analysis and optimization of power consumption in IC design.Firstly, it's essential to understand the sources of power dissipation in ICs. The major contributors typically include dynamic power dissipation (P_dynamic), which arises from charging and discharging internal node capacitances during switching activities, and static power dissipation (P_static), caused by leakage currents in transistors even when they are not switching.To effectively analyze and optimize power consumption, designers employ several key methodologies:1. Power Estimation and Modeling:Before diving into optimization, accurate estimation of power consumption is crucial. This involves using tools and techniques to model power at various stages of the design process—from early architectural exploration to detailed circuit implementation. Power estimation tools simulate the behavior of the IC under different conditions (e.g., varying workloads or input signals) to predict power consumption accurately.2. Architectural Optimization:At the architectural level, design choices significantly impact power consumption. Techniques such as voltage and frequency scaling (DVFS), where the operating voltageand clock frequency are adjusted dynamically based on workload, are commonly used to achieve optimal power-performance trade-offs. Furthermore, employing low-power design architectures such as pipelining, parallelism, and data gating helps in reducing power consumption without compromising performance.3. Circuit-Level Optimization:Circuit-level optimizations focus on reducing both dynamic and static power dissipation. Techniques like clock gating, where parts of the circuit are selectively shut down when not in use, effectively reduce dynamic power consumption. Additionally, optimizing transistor sizing, using low-leakage transistors, and implementing efficient power gating techniques help in minimizing static power dissipation.4. Advanced Power Management Techniques:As ICs become more complex, advanced power management techniques are crucial. This includes sophisticated power gating strategies like multi-threshold CMOS (MTCMOS), where different parts of the chip can operate at different voltages or shut down independently. Furthermore, the integration of power islands allows certain blocks of the IC to operate autonomously, enabling further power savings.5. Verification and Validation:Throughout the design process, verification of power-related optimizations is essential to ensure they meet design goals. Techniques such as power-aware simulation and formal verification help in validating power reduction strategies early in the design cycle, thereby minimizing costly redesigns later.6. Post-Silicon Power Analysis:Post-silicon power analysis involves measuring actual power consumption on fabricated chips. This step validates earlier estimations and optimizations, providing feedback for future design iterations and improvements.In conclusion, the analysis and optimization of power consumption in IC design involve a comprehensive approach spanning from early architectural decisions to post-silicon validation. By employing advanced modeling, architectural optimizations, circuit-level techniques, and rigorous verification, designers can effectively meet stringent power constraints while maintaining optimal performance. This holistic approach not only enhances the efficiency and longevity of electronic devices but also contributes to sustainable and eco-friendly design practices in the semiconductor industry.。

A 5 GHz 0.95 dB NF Highly Linear Cascode LNA

A5GHz0.95dB NF Highly Linear Cascode Floating-Body LNA in180nmSOI CMOS TechnologyAnuj Madan,Member,IEEE,Michael J.McPartlin,Member,IEEE,Christophe Masse,William Vaillancourt,andJohn D.Cressler,Fellow,IEEEAbstract—A5GHz CMOS LNA featuring a record0.95dB noise-figure is ing an inductively-degenerated cascode topology combined withfloating-body transistors and high-Q passives on an SOI substrate,record noisefigure and superior lin-earity performance at5GHz are obtained.The low-noise amplifier (LNA)achieves up to11dB of gain while consuming12mW dc power,and is capable of supporting802.11a WLAN applications. The impact of SOI body-contact on the LNA RF performance is described and linked to improved intermodulation performance. Index Terms—Intermodulation distortion,linearity,low-noise amplifier(LNA),radio-frequency integrated circuits(RFICs), system-on-chip(SoC)CMOS,WLAN.I.I NTRODUCTIONH IGH data rate wireless local area networks(LAN)havefueled the rapid growth of portable electronics.To keep the overall solution cost of portable devices low,the wireless transceiver should be highly integrated with the baseband as a system-on-chip(SoC)solution,preferably using a low-com-plexity CMOS process[1].Due to the scaling-induced reduction in supply voltage,it has become increasingly difficult to inte-grate the RF front-end on the same chip with the digital base-band circuits,while also obtaining the required RF performance. As a result,“front-end modules”are typically used,which incor-porate performance-critical blocks such as the RF switch and the low-noise amplifier(LNA)on the receive side,and the power amplifier(PA)on the transmit side[2].In a typical radio re-ceiver front-end,the LNA is one of the key components since it dominates the radio sensitivity.The LNA design involves trade-offs between noise-figure(NF),gain,power dissipation,input matching,and harmonic content in the output signal.Adding in progressively lower power dissipation constraints inherent to battery-powered portable applications,a primary challenge in LNA design is achieving simultaneous noise and input matchingManuscript received May09,2011;revised September27,2011;accepted February02,2012.A.Madan and C.Masse are with Skyworks Solutions,Inc.,Woburn,MA 01801USA(e-mail:anuj.madan@).M.J.McPartlin and W.Vaillancourt are with Skyworks Solutions,Inc.,An-dover,MA01810USA.J.D.Cressler is with the School of Electrical and Computer Engineering, Georgia Institute of Technology,Atlanta,GA30332-0250USA.Color versions of one or more of thefigures in this letter are available online at .Digital Object Identifier10.1109/LMWC.2012.2187882at any given amount of power dissipation.Moreover,the ampli-fier’s compression point requirement also imposes a limitation on the LNA transistor size,making the simultaneous noise and input match even more difficult to achieve in practice.An integrated5GHz LNA implemented infloating body SOI CMOS technology is described in this letter.The activesilicon layer is isolated from the substrate by buried-oxide and is surrounded by shallow-trench isolation on all sides.The buried oxide layer combined with the high-substrate resistivity decrease substrate noise injection by providing isolation from the substrate.Due to the low-loss dielectric substrate,SOI inductors have higher self-resonant frequency and quality factor than those fabricated on bulk silicon.In this work,the 0.18SOI CMOS technology,originally intended for RF switch applications[3],allows one to achieve sub-1.0dB NF for the5GHz LNA.This work reports state-of-the-art noise performance,linearity and improved LNAfigures-of-merit for silicon-based5GHz LNAs targeting WLAN applications.II.D ESIGN OF THE CMOS LNAThe schematic diagram of the proposed LNA is shown in Fig.1.The LNA employs a cascode topology to realize the re-quired gain and provide isolation between the receive port and the antenna.The inductive matching elements are a combination of bondwires and on-chip inductors,and the capacitive elements are implemented as on-chip MIM capacitors.The isolated SOI substrate enables high-Q inductors to minimize the loss through matching network.The inductively-degenerated LNA can si-multaneously achieve minimum NF,input impedance matching, and maximum transconductance gain.The input impedance of the inductively degenerated LNA can be expressed as(1) where is the device transconductance and is the intrinsic gate-to-source capacitance of transistor M1.To match the input impedance to50,the imaginary part of the impedance can be eliminated by resonating and at an operating frequency of5GHz.The real part of the input impedance is shown as(2)1531-1309/$31.00©2012IEEEFig.1.Circuit schematic of the inductively-degenerated cascodeLNA.Fig.2.Die photograph of the fabricated LNA.The inductors used are 0.4nH for Ls,3.7nH for Lg,and 2.2nH for load inductor;the simulated quality factors,based on electro-magnetic simulations at 5GHz are 7.8,22.7,and 20.2,respec-tively.The value ofresistanceis chosen to ensure uncondi-tionally stable operation of the LNA up to 15GHz.TransistorsM1and M2are sized128wide with a minimum gate length of0.18.III.E XPERIMENTAL R ESULTSTo validate the design and probe the impact of various tech-nology options,the LNA has been fabricated in a0.18SOI CMOS process,with both floating-body and body-contacted FETs.The die photograph of the proposed LNA is shown in Fig.2.The active die area of the fully integrated LNAis(excluding the pads).On-chip MIM capacitors serve todecouple supply.All measurements were performed on a FR-4board after mounting the die directly on the board.The measured S-parameters of the floating-body LNA are plotted in Fig.3.Due to the combination of the on-chip matching network and the bond-wire inductance,the input return loss is 33dB at 5GHz,while the output return loss is 13dB at 5GHz.A small-signal gain of 11dB at 5GHz is obtained with a supply voltage of 1.5V and total current of8mA.Due to additional input capacitanceassociated with the body-contacted FET,a slightly different inductor valueat the input gives an input return loss of 22dB,as shown in Fig.3.Fig.3.S-parameters of floating-body and body-contacted LNA with integrated input and output matched to 50 .Fig.4.De-embedded NF of the LNA.The gain of the body-contacted LNA biased at the same cur-rent is reduced to 9.3dB,primarily because of lower transcon-ductanceof the body-contacted device as compared to the floating body device.A 0.95dB NF with an error ofis measured across five samples at room-temperature for the floating-body LNA at 5GHz,as shown in Fig.4.When the body terminal of the FETs is tied to its source terminal in the body-contacted LNA,the increased gate resistance due to the polysilicon abutting the body-contact degrades the NF to 1.9dB at 5GHz.Power handling capability of the LNA is critical for WLAN applications in order to avoid LNA compression and preserve the modulated signal received at the front-end.The input 1dBcompression pointfor the LNAs was measured to be ,as shown in Fig.5(a).A two-tone test with equalpower levels at 5.000GHz and 5.001GHz was performed to measure the input third-order intercept point (IIP3),as shown in Fig.5(b).The floating-body LNA has an IIP3of 5dBm while the body-contacted LNA has an IIP3of 6.5dBm.Minimum-achievable noise-figurefor a body-con-tacted device is 1dB higher than the floating-body device,asMADAN et al.:5GHZ 0.95DB NF HIGHLY LINEAR CASCODE FLOATING-BODY LNA3Fig.5.(a)Measured inputP compression point,and (b)comparison of measured harmonics and IIP3of theLNAs.Fig.6.SimulatedNF and extracted R comparison of the LNA input de-vice.TABLE IP ERFORMANCE C OMPARISON B ETWEEN R ECENTLY P UBLISHED LNASillustrated in Fig.6.This is primarily attributed to the higher gate-electrode resistance for body-contacted device,which is in-dependent of frequency [8].To evaluate the performance of the LNAs,different figure-of-merit (FOM)are often used.is the ratio of the gain (in dB)to the dc power consumption (in mW),which is more com-monly used for comparing low-power LNAs.Furthermore,it can be expanded to include the NF,IIP3,and operating fre-quency (fc)as follows [9].A larger FOM is better in all casesA comparison between the present LNAs and other recently published LNAs is presented in Table I [4]–[9].It should be noted that all of the LNAs shown are fully integrated without off-chip components.By achieving a 0.95dB NF while con-suming 12mW,this LNA exhibits the lowest NF and highest.Furthermore,the proposed LNA also meets the stringent wireless LAN standards demanding high linearity and power-handling capability for the 802.11a/n standard.IV .C ONCLUSIONWe have presented a fully-integrated 5GHz LNA for 802.11a/n WLAN applications.This state-of-the-art LNA features a NF below 1.0dB and has 11dB power gain,while consuming 12mW of power and maintaining an input return loss of 33dB.The measured input 1dB compression point at5GHz is,while IIP3is 5dBm.The body-contacted FET LNA performance is compared with the floating-body LNA.Due to the additional polysilicon gate resistance,the body-contacted FET based LNA is seen to have higher NF.R EFERENCES[1]M.Zargari et al.,“A dual-band CMOS MIMO radio SoC for IEEE802.11n wireless LAN,”IEEE J.Solid State Circuits ,vol.43,no.12,pp.2882–2895,Dec.2008.[2]C.-W.Huang et al.,“A 525mm highly integrated dual-band WLANfront-end module simplifies 802.11a/b/g and 802.11n radio designs,”in Proc.IEEE Radio Freq.Integr.Circuits Symp.,2007,pp.665–668.[3]A.Botula et al.,“A thin-film SOI 180nm CMOS RF switch tech-nology,”in Proc.IEEE Topical Meeting Silicon Monolith.Integr.Cir-cuits RF Syst.,Jan.2009,pp.1–4.[4]J.Borremans,S.Thijs,P.Wambacq,Y.Rolain,D.Linten,and M.Kuijk,“A fully integrated 7.3kV HBM ESD-protected transformer-based 4.5–6GHz CMOS LNA,”IEEE J.Solid State Circuits ,vol.44,no.2,pp.344–353,Feb.2009.[5]F.Gianesello,D.Gloria,C.Raynaud,and S.Boret,“5GHz 1.4dB NFCMOS LNA integrated in 130nm high resistivity SOI technology,”in Proc.Int.Symp.Integr.Circuits ,Sep.2007,pp.96–99.[6]C.-P.Chang,J.-H.Chen,and Y.-H.Wang,“A fully integrated 5GHzlow-voltage LNA using forward body bias technology,”IEEE Microw.Wireless Compon.Lett.,vol.19,no.3,pp.176–178,Mar.2009.[7]K.Han,J.Gil,S.-S.Song,J.Han,H.Shin,C.-K.Kim,and K.Lee,“Complete high-frequency thermal noise modeling of short-channel MOSFETs and design of 5.2GHz low noise amplifier,”IEEE J.Solid State Circuits ,vol.40,no.3,pp.726–735,Mar.2005.[8]M.Kang,I.M.Kang,Y.H.Jung,and H.Shin,“Separate extraction ofgate resistance components in RF MOSFETs,”IEEE Trans.Electron Devices ,vol.54,no.6,pp.1459–1463,Jun.2007.[9]D.Linten et al.,“A 5GHz fully integrated ESD-protected low-noiseamplifier in 90-nm RF CMOS,”IEEE J.Solid State Circuits ,vol.40,no.7,pp.1434–1442,Jul.2005.。

CMOS芯片原理和产品介绍

• Radiation hardness

• Color

CMOS 芯片的特性功能

Features Region of Interest: Makes it possible to address a certain area of the sensor and read this part out with a higher speed. Typically full row addressing, column addressing if required. Binning: Gives higher DR and speed with a reduced resolution. Typically 2x2 binning: +50% DR and 2.5 x more speed

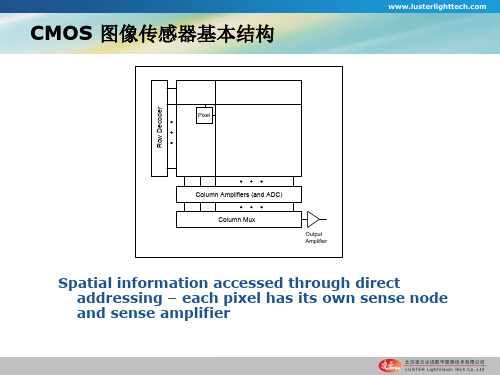

CMOS 图像传感器基本结构

Row Decoder

Pixel

Column Amplifiers (and ADC)

Column Mux

Output Amplifier

Spatial information accessed through direct addressing – each pixel has its own sense node and sense amplifier

CMOS 芯片的特性功能

Features Color: Application of on-chip color filters allows color imaging. Typically RGGB Bayer pattern.

V-CCD PD PD+amp MOS switch

Row selection

amp

微电子技术论文

50多年来微电子技术的发展历史,实际上就是不断创新的过程,这里指的创新包括原始创新、技术创新和应用创新等。晶体管的发明并不是一个孤立的精心设计的实验,而是一系列固体物理、半导体物理、材料科学等取得重大突破后的必然结果。1947年发明点接触型晶体管、1948年发明结型场效应晶体管以及以后的硅平面工艺、集成电路、CMOS技术、半导体随机存储器、CPU、非挥发存储器等微电子领域的重大发明也都是一系列创新成果的体现。同时,每一项重大发明又都开拓出一个新的领域,带来了新的巨大市场,对我们的生产、生活方式产生了重大的影响。也正是由于微电子技术领域的不断创新,才能使微电子能够以每三年集成度翻两番、特征尺寸缩小倍的速度持续发展几十年。自1968年开始,与硅技术有关的学术论文数量已经超过了与钢铁有关的学术论文,所以有人认为,1968年以后人类进入了继石器、青铜器、铁器时代之后硅石时代(silicon age)〖1〗。因此可以说社会发展的本质是创新,没有创新,社会就只能被囚禁在“超稳态”陷阱之中。虽然创新作为经济发展的改革动力往往会给社会带来“创造性的破坏”,但经过这种破坏后,又将开始一个新的处于更高层次的创新循环,社会就是以这样螺旋形上升的方式向前发展。

作者简介 王阳元,1935年生,微电子学家。浙江宁波人。1958年北京大学物理系毕业。北京大学微电子学研究所教授。中国科学院院士。

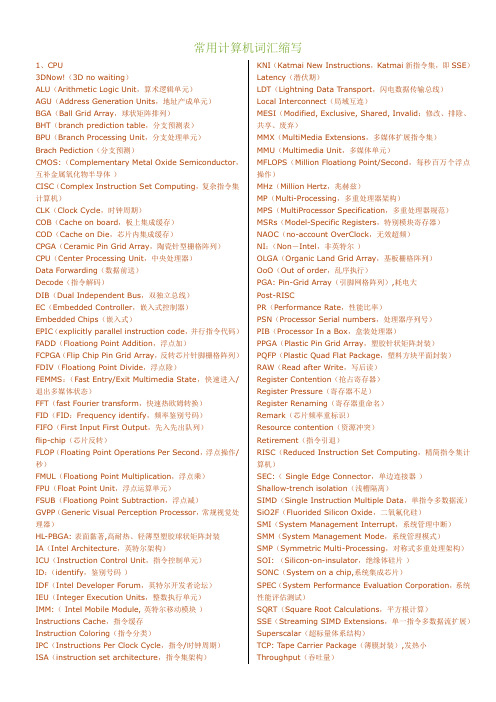

常用计算机词汇英文缩写

常用计算机词汇缩写1、CPU3DNow!(3D no waiting)ALU(Arithmetic Logic Unit,算术逻辑单元)AGU(Address Generation Units,地址产成单元)BGA(Ball Grid Array,球状矩阵排列)BHT(branch prediction table,分支预测表)BPU(Branch Processing Unit,分支处理单元)Brach Pediction(分支预测)CMOS: (Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)CISC(Complex Instruction Set Computing,复杂指令集计算机)CLK(Clock Cycle,时钟周期)COB(Cache on board,板上集成缓存)COD(Cache on Die,芯片内集成缓存)CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)CPU(Center Processing Unit,中央处理器)Data Forwarding(数据前送)Decode(指令解码)DIB(Dual Independent Bus,双独立总线)EC(Embedded Controller,嵌入式控制器)Embedded Chips(嵌入式)EPIC(explicitly parallel instruction code,并行指令代码)FADD(Floationg Point Addition,浮点加)FCPGA(Flip Chip Pin Grid Array,反转芯片针脚栅格阵列)FDIV(Floationg Point Divide,浮点除)FEMMS:(Fast Entry/Exit Multimedia State,快速进入/退出多媒体状态)FFT(fast Fourier transform,快速热欧姆转换)FID(FID:Frequency identify,频率鉴别号码)FIFO(First Input First Output,先入先出队列)flip-chip(芯片反转)FLOP(Floating Point Operations Per Second,浮点操作/秒)FMUL(Floationg Point Multiplication,浮点乘)FPU(Float Point Unit,浮点运算单元)FSUB(Floationg Point Subtraction,浮点减)GVPP(Generic Visual Perception Processor,常规视觉处理器)HL-PBGA: 表面黏著,高耐热、轻薄型塑胶球状矩阵封装IA(Intel Architecture,英特尔架构)ICU(Instruction Control Unit,指令控制单元)ID:(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛)IEU(Integer Execution Units,整数执行单元)IMM:( Intel Mobile Module, 英特尔移动模块)Instructions Cache,指令缓存Instruction Coloring(指令分类)IPC(Instructions Per Clock Cycle,指令/时钟周期)ISA(instruction set architecture,指令集架构)KNI(Katmai New Instructions,Katmai新指令集,即SSE)Latency(潜伏期)LDT(Lightning Data Transport,闪电数据传输总线)Local Interconnect(局域互连)MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元)MFLOPS(Million Floationg Point/Second,每秒百万个浮点操作)MHz(Million Hertz,兆赫兹)MP(Multi-Processing,多重处理器架构)MPS(MultiProcessor Specification,多重处理器规范)MSRs(Model-Specific Registers,特别模块寄存器)NAOC(no-account OverClock,无效超频)NI:(Non-Intel,非英特尔)OLGA(Organic Land Grid Array,基板栅格阵列)OoO(Out of order,乱序执行)PGA: Pin-Grid Array(引脚网格阵列),耗电大Post-RISCPR(Performance Rate,性能比率)PSN(Processor Serial numbers,处理器序列号)PIB(Processor In a Box,盒装处理器)PPGA(Plastic Pin Grid Array,塑胶针状矩阵封装)PQFP(Plastic Quad Flat Package,塑料方块平面封装)RAW(Read after Write,写后读)Register Contention(抢占寄存器)Register Pressure(寄存器不足)Register Renaming(寄存器重命名)Remark(芯片频率重标识)Resource contention(资源冲突)Retirem ent(指令引退)RISC(Reduced Instruction Set Computing,精简指令集计算机)SEC:( Single Edge Connector,单边连接器)Shallow-trench isolation(浅槽隔离)SIMD(Single Instruction Multiple Data,单指令多数据流)SiO2F(Fluorided Silicon Oxide,二氧氟化硅)SMI(System Management Interrupt,系统管理中断)SMM(System Management Mode,系统管理模式)SMP(Symmetric Multi-Processing,对称式多重处理架构)SOI: (Silicon-on-insulator,绝缘体硅片)SONC(System on a chip,系统集成芯片)SPEC(System Performance Evaluation Corporation,系统性能评估测试)SQRT(Square Root Calculations,平方根计算)SSE(Streaming SIMD Extensions,单一指令多数据流扩展)Superscalar(超标量体系结构)TCP: Tape Carrier Package(薄膜封装),发热小Throughput(吞吐量)TLB(Translate Look side Buffers,翻译旁视缓冲器)USWC(Uncacheabled Speculative Write Combination,无缓冲随机联合写操作)VALU(Vector Arithmetic Logic Unit,向量算术逻辑单元)VLIW(Very Long Instruction Word,超长指令字)VPU(Vector Permutate Unit,向量排列单元)VPU(vector processing units,向量处理单元,即处理MMX、SSE等SIMD指令的地方)2、主板ADIMM(advanced Dual In-line Memory Modules,高级双重内嵌式内存模块)AMR(Audio/Modem Riser;音效/调制解调器主机板附加直立插卡)AHA(Accelerated Hub Architecture,加速中心架构)ASK IR(Amplitude Shift Keyed Infra-Red,长波形可移动输入红外线)ATX: AT Extend(扩展型AT)BIOS(Basic Input/Output System,基本输入/输出系统)CSE(Configuration Space Enable,可分配空间)DB:(Device Bay,设备插架)DMI(Desktop Management Interface,桌面管理接口)EB(Expansion Bus,扩展总线)EISA(Enhanced Industry Standard Architecture,增强形工业标准架构)EMI(Electromagnetic Interference,电磁干扰)ESCD(Extended System Configuration Data,可扩展系统配置数据)FBC(Fram e Buffer Cache,帧缓冲缓存)FireWire(火线,即IEEE1394标准)FSB: (Front Side Bus,前置总线,即外部总线)FWH( Firmware Hub,固件中心)GMCH(Graphics & Memory Controller Hub,图形和内存控制中心)GPIs(General Purpose Inputs,普通操作输入)ICH(Input/Output Controller Hub,输入/输出控制中心)IR(infrared ray,红外线)IrDA(infrared ray,红外线通信接口可进行局域网存取和文件共享)ISA:(Industry Standard Architecture,工业标准架构)ISA(instruction set architecture,工业设置架构)MDC(Mobile Daughter Card,移动式子卡)MRH-R(Memory Repeater Hub,内存数据处理中心)MRH-S(SDRAM Repeater Hub,SDRAM数据处理中心)MTH(Memory Transfer Hub,内存转换中心)NGIO(Next Generation Input/Output,新一代输入/输出标准)P64H(64-bit PCI Controller Hub,64位PCI控制中心)PCB(printed circuit board,印刷电路板)PCBA(Printed Circuit Board Assembly,印刷电路板装配)PCI:(Peripheral Component Interconnect,互连外围设备)PCI SIG (Peripheral Component Interconnect Special Interest G roup,互连外围设备专业组)POST(Power On Self Test,加电自测试)RNG(Random number Generator,随机数字发生器)RTC: (Real Time Clock 实时时钟)KBC(KeyBroad Control,键盘控制器)SAP(Sideband Address Port,边带寻址端口)SBA(Side Band Addressing,边带寻址)SMA: (Share Memory Architecture,共享内存结构)STD(Suspend T o Disk,磁盘唤醒)STR(Suspend T o RAM,内存唤醒)SVR: (Switching Voltage Regulator 交换式电压调节)USB(Universal Serial Bus,通用串行总线)USDM(Unified System Diagnostic Manager,统一系统监测管理器)VID(Voltage Identification Definition,电压识别认证)VRM (Voltage Regulator Module,电压调整模块)ZIF: (Zero Insertion Force, 零插力)主板技术GigabyteACOPS:(Automatic CPU OverHeat Prevention SystemCPU 过热预防系统)SIV: (System Information Viewer系统信息观察)磐英ESDJ(Easy Setting Dual Jumper,简化CPU双重跳线法)浩鑫UPT(USB、PANEL、LINK、TV-OUT四重接口)芯片组ACPI(Advanced Configuration and Power Interface,先进设置和电源管理)AGP(Accelerated Graphics Port,图形加速接口)I/O(Input/Output,输入/输出)MIOC: (Memory and I/O Bridge Controller,内存和I/O桥控制器)NBC: (North Bridge Chip北桥芯片)PIIX: (PCI ISA/IDE Accelerator加速器)PSE36: (Page Size Extension 36-bit,36位页面尺寸扩展模式)PXB:(PCI Expander Bridge,PCI增强桥)RCG: (RAS/CAS Generator,RAS/CAS发生器)SBC: (South Bridge Chip南桥芯片)SMB: (System Management Bus全系统管理总线)SPD(Serial Presence Detect,内存内部序号检测装置)SSB: (Super South Bridge,超级南桥芯片)TDP:(Triton Data Path数据路径)TSC: (Triton System Controller系统控制器)QPA: (Quad Port Acceleration四接口加速)3、显示设备ASIC: (Application Specific Integrated Circuit特殊应用积体电路)ASC(Auto-Sizing and Centering,自动调效屏幕尺寸和中心位置)ASC(Anti Static Coatings,防静电涂层)AGAS(Anti Glare Anti Static Coatings,防强光、防静电涂层)BLA: (Bearn Landing Area电子束落区)BMC(Black Matrix Screen,超黑矩阵屏幕)CRC: (Cyclical Redundancy Check循环冗余检查)CRT(Cathode Ray Tube,阴极射线管)DDC:(Display Data Channel,显示数据通道)DEC(Direct Etching Coatings,表面蚀刻涂层)DFL(Dynamic Focus Lens,动态聚焦)DFS(Digital Flex Scan,数字伸缩扫描)DIC: (Digital Image Control数字图像控制)Digital Multiscan II(数字式智能多频追踪)DLP(digital Light Processing,数字光处理)DOSD:(Digital On Screen Display同屏数字化显示)DPMS(Display Power Management Signalling,显示能源管理信号)Dot Pitch(点距)DQL(Dynamic Quadrapole Lens,动态四极镜)DSP(Digital Signal Processing,数字信号处理)EFEAL(Extended Field Elliptical Aperture Lens,可扩展扫描椭圆孔镜头)FRC:(Frame Rate Control帧比率控制)HVD(High Voltage Differential,高分差动)LCD(liquid crystal display,液晶显示屏)LCOS: (Liquid Crystal On Silicon硅上液晶)LED(light emitting diode,光学二级管)L-SAGIC(Low Power-Small Aperture G1 wiht Impregnated Ca thode,低电压光圈阴极管)LVD(Low Voltage Differential,低分差动)LVDS:(Low Voltage Differential Signal低电压差动信号)MALS(Multi Astigmatism Lens System,多重散光聚焦系统)MDA(Monochrome Adapter,单色设备)MS: (Magnetic Sensors磁场感应器)Porous Tungsten(活性钨)RSDS: (Reduced Swing Differential Signal小幅度摆动差动信号)SC(Screen Coatings,屏幕涂层)Single Ended(单终结)Shadow Mask(阴罩式)TDT(Timeing Detection Table,数据测定表)TICRG: (Tungsten Impregnated Cathode Ray Gun钨传输阴级射线枪)TFT(thin film transistor,薄膜晶体管)UCC(Ultra Clear Coatings,超清晰涂层)VAGP:( Variable Aperature Grille Pitch可变间距光栅)VBI:( Vertical Blanking Interval垂直空白间隙)VDT(Video Display T erminals,视频显示终端)VRR: (Vertical Refresh Rate垂直扫描频率)4、视频3D:(Three Dimensional,三维)3DS(3D SubSystem,三维子系统)AE(Atmospheric Effects,雾化效果)AFR(Alternate Frame Rendering,交替渲染技术)Anisotropic Filtering(各向异性过滤)APPE(Advanced Packet Parsing Engine,增强形帧解析引擎)AV(Analog Video,模拟视频)Back Buffer,后置缓冲Backface culling(隐面消除)Battle for Eyeballs(眼球大战,各3D图形芯片公司为了争夺用户而作的竞争)Bilinear Filtering(双线性过滤)CEM(cube environment mapping,立方环境映射)CG(Computer Graphics,计算机生成图像)Clipping(剪贴纹理)Clock Synthesizer,时钟合成器compressed textures(压缩纹理)Concurrent Command Engine,协作命令引擎Center Processing Unit Utilization,中央处理器占用率DAC(Digital to Analog Converter,数模传换器)Decal(印花法,用于生成一些半透明效果,如:鲜血飞溅的场面)DFP(Digital Flat Panel,数字式平面显示器)DFS:( Dynamic Flat Shading动态平面描影,可用作加速Dithering抖动)Directional Light,方向性光源DME:( Direct Memory Execute直接内存执行)DOF(Depth of Field,多重境深)dot texture blending(点型纹理混和)Double Buffering(双缓冲区)DIR(Direct Rendering Infrastructure,基层直接渲染)DVI(Digital Video Interface,数字视频接口)DxR:( DynamicXTended Resolution动态可扩展分辨率)DXTC(Direct X Texture Compress,DirectX纹理压缩,以S3TC为基础)Dynamic Z-buffering(动态Z轴缓冲区),显示物体远近,可用作远景E-DDC(Enhanced Display Data Channel,增强形视频数据通道协议,定义了显示输出与主系统之间的通讯通道,能提高显示输出的画面质量)Edge Anti-aliasing,边缘抗锯齿失真E-EDID(Enhanced Extended Identification Data,增强形扩充身份辨识数据,定义了电脑通讯视频主系统的数据格式)Execute Buffers,执行缓冲区environment mapped bump mapping(环境凹凸映射)Extended Burst Transactions,增强式突发处理Front Buffer,前置缓冲Flat(平面描影)Frames rate is King(帧数为王)FSAA(Full Scene Anti-aliasing,全景抗锯齿)Fog(雾化效果)flip double buffered(反转双缓存)fog table quality(雾化表画质)GART(Graphic Address Remappng Table,图形地址重绘表)Gouraud Shading,高洛德描影,也称为内插法均匀涂色GPU(Graphics Processing Unit,图形处理器)GTF(Generalized Timing Formula,一般程序时间,定义了产生画面所需要的时间,包括了诸如画面刷新率等)HAL(Hardware Abstraction Layer,硬件抽像化层)hardware motion compensation(硬件运动补偿)HDTV(high definition television,高清晰度电视)HEL: Hardware Emulation Layer(硬件模拟层)high triangle count(复杂三角形计数)ICD(Installable Client Driver,可安装客户端驱动程序)IDCT(Inverse Discrete Cosine Transform,非连续反余弦变换,GeForce的DVD硬件强化技术)Immediate Mode,直接模式IPPR: (Image Processing and Pattern Recognition图像处理和模式识别)large textures(大型纹理)LF(Linear Filtering,线性过滤,即双线性过滤)lighting(光源)lightmap(光线映射)Local Peripheral Bus(局域边缘总线)mipmapping(MIP映射)Modulate(调制混合)Motion Compensation,动态补偿motion blur(模糊移动)MPPS:(Million Pixels Per Second,百万个像素/秒)Multi-Resolution Mesh,多重分辨率组合Multi Threaded Bus Master,多重主控Multitexture(多重纹理)nerest Mipmap(邻近MIP映射,又叫点采样技术)Overdraw(透支,全景渲染造成的浪费)partial texture downloads(并行纹理传输)Parallel Processing Perspective Engine(平行透视处理器)PC(Perspective Correction,透视纠正)PGC(Parallel Graphics Configuration,并行图像设置)pixel(Picture element,图像元素,又称P像素,屏幕上的像素点)point light(一般点光源)point sampling(点采样技术,又叫邻近MIP映射)Precise Pixel Interpolation,精确像素插值Procedural textures(可编程纹理)RAMDAC(Random Access Memory Digital to Analog Converte r,随机存储器数/模转换器)Reflection mapping(反射贴图)ender(着色或渲染)S端子(Seperate)S3(Sight、Sound、Speed,视频、音频、速度)S3TC(S3 Texture Compress,S3纹理压缩,仅支持S3显卡)S3TL(S3 Transformation & Lighting,S3多边形转换和光源处理)Screen Buffer(屏幕缓冲)SDTV(Standard Definition T elevision,标准清晰度电视)SEM(spherical environment mapping,球形环境映射)Shading,描影Single Pass Multi-Texturing,单通道多纹理SLI(Scanline Interleave,扫描线间插,3Dfx的双Voodoo 2配合技术)Smart Filter(智能过滤)soft shadows(柔和阴影)soft reflections(柔和反射)spot light(小型点光源)SRA(Symmetric Rendering Architecture,对称渲染架构)Stencil Buffers(模板缓冲)Stream Processor(流线处理)SuperScaler Rendering,超标量渲染TBFB(Tile Based Frame Buffer,碎片纹理帧缓存)texel(T像素,纹理上的像素点)Texture Fidelity(纹理真实性)texture swapping(纹理交换)T&L(Transform and Lighting,多边形转换与光源处理)T-Buffer(T缓冲,3dfx Voodoo4的特效,包括全景反锯齿Full-scene Anti-Aliasing、动态模糊Motion Blur、焦点模糊Depth of Field Blur、柔和阴影Soft Shadows、柔和反射Soft Reflections)TCA(Twin Cache Architecture,双缓存结构)Transparency(透明状效果)Transformation(三角形转换)Trilinear Filtering(三线性过滤)Texture Modes,材质模式TMIPM: (Trilinear MIP Mapping三次线性MIP材质贴图)UMA(Unified Memory Architecture,统一内存架构)Visualize Geom etry Engine,可视化几何引擎Vertex Lighting(顶点光源)Vertical Interpolation(垂直调变)VIP(Video Interface Port,视频接口)ViRGE: (Video and Rendering Graphics Engine视频描写图形引擎)Voxel(Volume pixels,立体像素,Novalogic的技术)VQTC(Vector-Quantization T exture Compression,向量纹理压缩)VSIS(Video Signal Standard,视频信号标准)v-sync(同步刷新)Z Buffer(Z缓存)5、音频3DPA(3D Positional Audio,3D定位音频)AC(Audio Codec,音频多媒体数字信号编解码器)Auxiliary Input(辅助输入接口)CS(Channel Separation,声道分离)DS3D(DirectSound 3D Streams)DSD(Direct Stream Digital,直接数字信号流)DSL(Down Loadable Sample,可下载的取样音色)DLS-2(Downloadable Sounds Level 2,第二代可下载音色)EAX(Environmental Audio Extensions,环境音效扩展技术)Extended Stereo(扩展式立体声)FM(Frequency Modulation,频率调制)FIR(finite impulse response,有限推进响应)FR(Frequence Response,频率响应)FSE(Frequency Shifter Effect,频率转换效果)HRTF(Head Related Transfer Function,头部关联传输功能)IID(Interaural Intensity Difference,两侧声音强度差别)IIR(infinite impulse response,无限推进响应)Interactive Around-Sound(交互式环绕声)Interactive 3D Audio(交互式3D音效)ITD(Interaural Time Difference,两侧声音时间延迟差别)MIDI:( Musical Instrument Digital Interface乐器数字接口)NDA:( non-DWORD-aligned ,非DWORD排列)Raw PCM:( Raw Pulse Code Modulated元脉码调制)RMA:( RealMedia Architecture实媒体架构)RTSP: (Real Time Streaming Protocol实时流协议)SACD(Super Audio CD,超级音乐CD)SNR(Signal to Noise Ratio,信噪比)S/PDIF(Sony/Phillips Digital Interface,索尼/飞利普数字接口)SRS: (Sound Retrieval System声音修复系统)Surround Sound(环绕立体声)Super Intelligent Sound ASIC(超级智能音频集成电路)THD+N(Total Harmonic Distortion plus Noise,总谐波失真加噪音)QEM(Qsound Environmental Modeling,Qsound环境建模扬声器组)WG(Wave Guide,波导合成)WT(Wave T able,波表合成)6、RAM & ROMABP: (Address Bit Permuting,地址位序列改变)ATC(Access Time from Clock,时钟存取时间)BSRAM(Burst pipelined synchronous static RAM,突发式管道同步静态存储器)CAS(Column Address Strobe,列地址控制器)CCT(Clock Cycle Time,时钟周期)DB: (Deep Buffer深度缓冲)DDR SDRAM(Double Date Rate,双数据率SDRAM)DIL(dual-in-line)DIMM(Dual In-line Memory Modules,双重内嵌式内存模块)DRAM(Dynamic Random Access Memory,动态随机存储器)DRDRAM(Direct RAMbus DRAM,直接RAMbus内存)ECC(Error Checking and Correction,错误检查修正)EEPROM(Electrically Erasable Programmable ROM,电擦写可编程只读存储器)FM: (Flash Memory快闪存储器)FMD ROM (Fluorescent Material Read Only Memory,荧光质只读存储器)PIROM:(Processor Information ROM,处理器信息ROM)PLEDM: Phase-state Low Electron(hole)-number Drive MemoryQBM(Quad Band Memory,四倍边带内存)RAC(Rambus Asic Cell,Rambus集成电路单元)RAS(Row Address Strobe,行地址控制器)RDRAM(Rambus Direct RAM,直接型RambusRAM)RIMM(RAMBUS In-line Memory Modules,RAMBUS内嵌式内存模块)SDR SDRAM(Single Date Rate,单数据率SDRAM)SGRAM(synchronous graphics RAM,同步图形随机储存器)SO-DIMM(Small Outline Dual In-line Memory Modules,小型双重内嵌式内存模块)SPD(Serial Presence Detect,串行存在检查)SRAM(Static Random Access Memory,静态随机存储器)SSTL-2(Stub Series T erminated Logic-2)TSOPs(thin small outline packages,超小型封装)USWV(Uncacheable, Speculative, Write-Combining非缓冲随机混合写入)VCMA(Virtual Channel Memory architecture,虚拟通道内存结构)7、磁盘AAT(Average access time,平均存取时间)ABS(Auto Balance System,自动平衡系统)ASMO(Advanced Storage Magneto-Optical,增强形光学存储器)AST(Average Seek time,平均寻道时间)ATA(AT Attachment,AT扩展型)ATOMM(Advanced super Thin-layer and high-Output Metal Me dia,增强形超薄高速金属媒体)bps(bit per second,位/秒)CAM(Common Access Model,公共存取模型)CSS(Common Command Set,通用指令集)DMA(Direct Memory Access,直接内存存取)DVD(Digital Video Disk,数字视频光盘)EIDE(enhanced Integrated Drive Electronics,增强形电子集成驱动器)FAT(File Allocation T ables,文件分配表)FDBM(Fluid dynamic bearing motors,液态轴承马达)FDC(Floppy Disk Controller,软盘驱动器控制装置)FDD(Floppy Disk Driver,软盘驱动器)GMR(giant magnetoresistive,巨型磁阻)HDA(head disk assembly,磁头集合)HiFD(high-capacity floppy disk,高容量软盘)IDE(Integrated Drive Electronics,电子集成驱动器)LBA(Logical Block Addressing,逻辑块寻址)MBR(Master Boot Record,主引导记录)MTBF(Mean Time Before Failure,平均故障时间)PIO(Programmed Input Output,可编程输入输出模式)PRML(Partial Response Maximum Likelihood,最大可能部分反应,用于提高磁盘读写传输率)RPM(Rotation Per Minute,转/分)RSD:(Removable Storage Device移动式存储设备)SCSI(Small Computer System Interface,小型计算机系统接口)SCMA:(SCSI Configured Auto Magically,SCSI自动配置)S.M.A.R.T.(Self-Monitoring, Analysis and Reporting T echnology ,自动监测、分析和报告技术)SPS(Shock Protection System,抗震保护系统)STA(SCSI Trade Association,SCSI同业公会)Ultra DMA(Ultra Direct Memory Access,超高速直接内存存取)LVD(Low Voltage Differential)Seagate硬盘技术DiscWizard(磁盘控制软件)DST(Drive Self Test,磁盘自检程序)SeaShield(防静电防撞击外壳)8、光驱ATAPI(AT Attachment Packet Interface)BCF(Boot Catalog File,启动目录文件)BIF(Boot Image File,启动映像文件)CDR(CD Recordable,可记录光盘)CD-ROM/XA(CD-ROM eXtended Architecture,唯读光盘增强形架构)CDRW(CD-Rewritable,可重复刻录光盘)CLV(Constant Linear Velocity,恒定线速度)DAE(digital Audio Extraction,数据音频抓取)DDSS(Double Dynamic Suspension System,双悬浮动态减震系统)DDSS II(Double Dynamic Suspension System II,第二代双层动力悬吊系统)PCAV(Part Constant Angular Velocity,部分恒定角速度)VCD(Video CD,视频CD)9、打印机AAS(Automatic Area Seagment?)dpi(dot per inch,每英寸的打印像素)ECP(Extended Capabilities Port,延长能力端口)EPP(Enhanced Parallel Port,增强形平行接口)IPP(Internet Printing Protocol,因特网打印协议)ppm(paper per minute,页/分)SPP(Standard Parallel Port,标准并行口)TET(Text Enhanced Technology,文本增强技术)USBDCDPD(Universal Serial Bus Device Class Definition for Prin ting Devices,打印设备的通用串行总线级标准)VD(Variable Dot,变点式列印)10、扫描仪TWAIN(Toolkit Without An Interesting Name)协议11、计算机公司Ali: Acer Lab(宏棋实验室)ASF: Applied Science FictionAMD: Advanced Micro Device(超微半导体)AMI: American Megatrends IncorporatedEAR(Extreme Audio Reality)HP: Hewlett-Packard,美国惠普公司IBM: International Business Machine,国际商业机器IDG(International Data Group,国际数据集团)IMS: International Meta SystemMLE:Microsoft Learning and Entertainment,微软教学与娱乐公司MS(Microsoft,微软)NAI: Network Associates Incorporation,前身为McAfee。

C8051F060_07中文资料

• Programmable hysteresis/response time - Voltage Reference - Precision VDD Monitor/Brown-Out Detector On-Chip JTAG Debug & Boundary Scan - On-chip debug circuitry facilitates full-speed, nonintrusive in-circuit/in-system debugging Provides breakpoints, single-stepping, watchpoints, stack monitor; inspect/modify memory and registers Superior performance to emulation systems using ICE-chips, target pods, and sockets IEEE1149.1 compliant boundary scan Complete development kit

Clock Sources - Internal calibrated precision oscillator: 24.5 MHz - External oscillator: Crystal, RC, C, or clock Supply Voltage .......................... 2.7 to 3.6 V - Multiple power saving sleep and shutdown modes 100-Pin and 64-Pin TQFP Packages Available Temperature Range: -40 to +85 °C

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。