KK74ACT132D中文资料

SN74HC132DBR中文资料

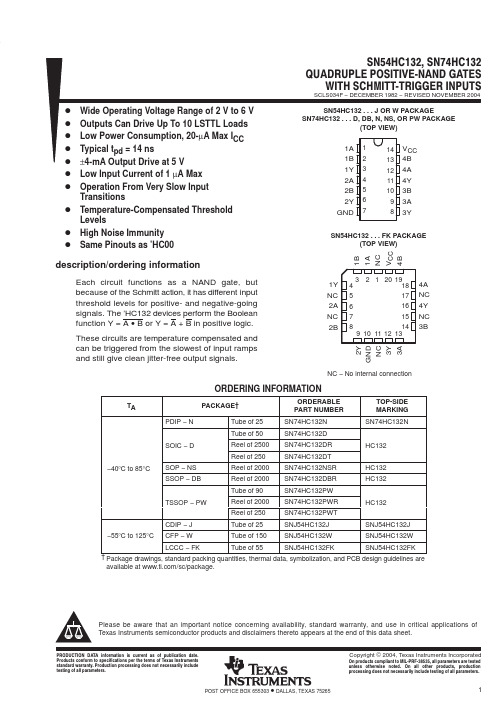

PACKAGING INFORMATIONOrderableDevice Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)5962-89845022A ACTIVE LCCC FK 201TBD POST-PLATE N /A for Pkg Type 5962-8984502CA ACTIVE CDIP J 141TBD A42SNPB N /A for Pkg Type 5962-8984502DA ACTIVE CFP W 141TBD A42N /A for Pkg Type 5962-8984502VCA ACTIVE CDIP J 141TBD A42SNPB N /A for Pkg Type 5962-8984502VDA ACTIVE CFP W 141TBD A42N /A for Pkg Type SN54HC132J ACTIVE CDIP J 141TBD A42SNPB N /A for Pkg Type SN74HC132D ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DBLE OBSOLETE SSOP DB 14TBDCall TI Call TISN74HC132DBR ACTIVE SSOP DB 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DBRE4ACTIVE SSOP DB 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DE4ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DG4ACTIVE SOIC D 1450Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DR ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DRE4ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DRG4ACTIVE SOIC D 142500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DT ACTIVE SOIC D 14250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132DTE4ACTIVE SOIC D 14250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132N ACTIVE PDIP N 1425Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type SN74HC132NE4ACTIVE PDIP N 1425Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type SN74HC132NSR ACTIVE SO NS 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132NSRE4ACTIVE SO NS 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132PW ACTIVE TSSOP PW 1490Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132PWE4ACTIVE TSSOP PW 1490Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132PWLE OBSOLETE TSSOP PW 14TBDCall TI Call TISN74HC132PWR ACTIVE TSSOP PW 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132PWRE4ACTIVE TSSOP PW 142000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132PWT ACTIVE TSSOP PW 14250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC132PWTE4ACTIVETSSOPPW14250Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM18-Jul-2006Orderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)SNJ54HC132FK ACTIVE LCCC FK 201TBD POST-PLATE N /A for Pkg Type SNJ54HC132J ACTIVE CDIP J 141TBD A42SNPB N /A for Pkg Type SNJ54HC132W ACTIVE CFP W 141TBD A42N /A for Pkg Type SNV54HC132J ACTIVE CDIP J 14TBD Call TI Call TI SNV54HC132WACTIVECFPW14TBDCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI'sknowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.18-Jul-2006IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityLow Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2006, Texas Instruments Incorporated。

74ACT74中文资料

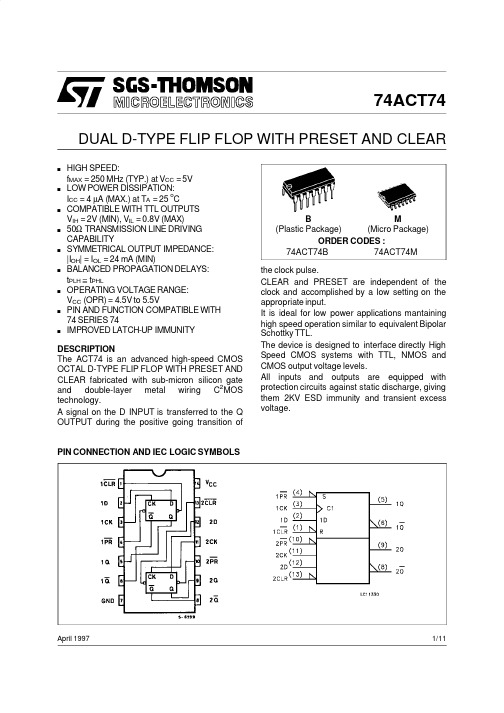

74ACT74DUAL D-TYPE FLIP FLOP WITH PRESET AND CLEARApril 1997sHIGH SPEED:f MAX =250MHz (TYP.)at V CC =5V sLOW POWER DISSIPATION:I CC =4µA (MAX.)at T A =25o CsCOMPATIBLE WITH TTL OUTPUTS V IH =2V (MIN),V IL =0.8V (MAX)s50ΩTRANSMISSION LINE DRIVING CAPABILITYsSYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =24mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅t PHLsOPERATING VOLTAGE RANGE:V CC (OPR)=4.5V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES 74sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe ACT74is an advanced high-speed CMOS OCTAL D-TYPE FLIP FLOP WITH PRESET AND CLEAR fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.A signal on the D INPUT is transferred to the Q OUTPUT during the positive going transition of the clock pulse.CLEAR and PRESET are independent of the clock and accomplished by a low setting on the appropriate input.It is ideal for low power applications mantaining high speed operation similar to equivalent Bipolar Schottky TTL.The device is designed to interface directly High Speed CMOS systems with TTL,NMOS and CMOS output voltage levels.All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODES :74ACT74B 74ACT74M M(Micro Package)B (Plastic Package)1/11INPUT AND OUTPUT EQUIVALENT CIRCUIT LOGIC DIAGRAMS PIN DESCRIPTIONPIN No SYMBOL NAME AND FUNCTION 1,131CLR,2CLRAsyncronous Reset-Direct Input2,121D,2D Data Inputs3,111CK,2CK Clock Input(LOW-to-HIGH,Edge-Triggered)4,101PR,2PR Asyncronous Set-DirectInput5,91Q,2Q True Flip-Flop Outputs6,81Q,2Q Complement Flip-FlopOutputs7GND Ground(0V)14V CC Positive Supply VoltageTRUTH TABLEINPUTS OUTPUTS FUNCTION CLR PR D CK Q QL H X X L H CLEARH L X X H L PRESETL L X X H HH H L L HH H H H LH H X Q n Q n NO CHANGE X:Don’t CareThis logic diagram has not be used to estimate propagation delays74ACT742/1174ACT74ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7V V I DC Input Voltage-0.5to V CC+0.5V V O DC Output Voltage-0.5to V CC+0.5VI IK DC Input Diode Current±20mAI OK DC Output Diode Current±20mAI O DC Output Current±50mAI CC or I GND DC V CC or Ground Current±200mAT stg Storage Temperature-65to+150o CT L Lead Temperature(10sec)300o C Absolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these condition is not implied.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage 4.5to5.5V V I Input Voltage0to V CC V V O Output Voltage0to V CC V T op Operating Temperature:-40to+85o C dt/dv Input Rise and Fall Time V CC=4.5to5.5V(note1)8ns/V 1)V IN from0.8V to2.0V3/11DC SPECIFICATIONSSymbol Parameter Test Conditions Value UnitV CC (V)T A=25o C-40to85o C Min.Typ.Max.Min.Max.V IH High Level Input Voltage 4.5V O=0.1V orV CC-0.1V 2.0 1.5 2.0V5.5 2.0 1.5 2.0V IL Low Level Input Voltage 4.5V O=0.1V orV CC-0.1V 1.50.80.8V5.5 1.50.80.8V OH High Level OutputVoltage 4.5V I(*)=V IH orV ILI O=-50µA 4.4 4.49 4.4V 5.5I O=-50µA 5.4 5.49 5.44.5I O=-24mA 3.86 3.765.5I O=-24mA 4.86 4.76V OL Low Level OutputVoltage 4.5V I(*)=V IH orV ILI O=50µA0.0010.10.1V 5.5I O=50mA0.0010.10.14.5I O=24mA0.360.445.5I O=24mA0.360.44I I Input Leakage Current 5.5V I=V CC or GND±0.1±1µA I CCT Max I CC/Input 5.5V I=V CC-2.1V0.6 1.5mA I CC Quiescent SupplyCurrent5.5V I=V CC or GND440µAI OLD Dynamic Output Current(note1,2)5.5V OLD=1.65V max75mAI OHD V OHD=3.85V min-75mA1)Maximum test duration2ms,one output loaded at time2)Incident wave switch ing is guaranteed on transmission lines with impe dances as low as50Ω.(*)All outputs loaded.74ACT744/11CAPACITIVE CHARACTERISTICSSymbolParameterTest ConditionsValueUnitV CC (V)T A =25o C-40to 85o C Min.Typ.Max.Min.Max.C IN Input Capacitance 5.04pF C PDPower Dissipation Capacitance (note 1)5.043pF 1)C PD isdefined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load.(Refer to Test Circuit).Ave rage operating current can be obtained by the following equation.I CC (opr)=C PD •V CC •f IN +I CC /n (per circuit)AC ELECTRICAL CHARACTERISTICS (C L =50pF,R L =500Ω,Input t r =t f =3ns)SymbolParameterTest ConditionValueUnitV CC (V)T A =25oC -40to 85o C Min.Typ.Max.Min.Max.t PLH t PHL Propagation Delay Time CK to Q5.0(*)5.010.011.0ns t PLH t PHL Propagation Delay Time PR or CLR to Q or Q 5.0(*)5.010.011.0ns t w CK Pulse Width,HIGH or LOW5.0(*) 1.5 5.06.0ns t s Setup Time Q to CK HIGH or LOW 5.0(*)0.5 3.0 3.5ns t h Hold Time Q to CK HIGH or LOW 5.0(*)-0.5 1.0 1.0ns t rem Removal Time PR or CLR to CK 5.0(*)-0.71.01.0ns f MAXMaximim Clock Frequency5.0(*)10025085MHz(*)Voltage range is 5V ±0.5V74ACT745/1174ACT74TEST CIRCUITC L=50pF or equivalent(includes jig and probe capacitance)R L=R1=500Ωor equiva lentR T=Z OUT of pulse generator(typically50Ω)WAVEFORM1:PROPAGATION DELAYS,SETUP AND HOLD TIMES(f=1MHz;50%duty cycle) 6/1174ACT74 WAVEFORM2:PROPAGATION DELAYS(f=1MHz;50%duty cycle)7/1174ACT74WAVEFORM3:RECOVERY TIMES(f=1MHz;50%duty cycle) WAVEFORM3:PULSE WIDTH8/11DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B 1.391.650.0550.065b 0.50.020b10.250.010D 200.787E 8.50.335e 2.540.100e315.240.600F 7.10.280I 5.10.201L 3.30.130Z1.272.540.0500.100P001APlastic DIP14MECHANICAL DATA74ACT749/11DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.068a10.10.20.0030.007a2 1.650.064b 0.350.460.0130.018b10.190.250.0070.010C 0.50.019c145(typ.)D 8.558.750.3360.344E 5.86.20.2280.244e 1.270.050e37.620.300F 3.8 4.00.1490.157G 4.6 5.30.1810.208L 0.5 1.270.0190.050M 0.680.026S8(max.)P013GSO14MECHANICAL DATA74ACT7410/11元器件交易网74ACT74 Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsabilit y for theconsequences of use of such information nor for any infringemen t of patents or other rights of third parties which may results from its use.Nolicense is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectr onics.Specifications mention edin this publication are subject to change without notice.This publication supersede s and replaces all information previously supplied.SGS-THOMSON Microelectr onics products are not auth orized for use as critical compon ents in life support devices or systems without expre sswritten approval of SGS-THOMSON Microelectonics.©1997SGS-THOMSON Microelectronics-Printed in Italy-All Rights Reserve dSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A.11/11。

KK74LV139D中文资料

2.0

1.85

-

1.8

-

1.8

-

2.7

2.55

-

2.5

-

2.5

-

3.0

2.85

-

2.8

-

2.8

-

3.6

3.45

-

3.4

-

3.4

-

4.5

4.35

-

4.3

-

4.3

-

5.5

5.35

-

5.3

-

5.3

-

VIH or VIL

3.0

-IO=6.0 mA

4.5

-IO=12.0 mA

2.48

- 2.40 - 2.20 -

VIH High-level input voltage

1.2

0.9

-

0.9

-

0.9

-

В

2.0

1.4

-

1.4

-

1.4

-

2.7 to 3.6 2.0

-

2.0

-

2.0

-

4.5 to 5.5 0.7 Vcc - 0.7 Vcc - 0.7 Vcc -

VIL Low -level input voltage

B

3.70

3.60

3.50

VOL Low-level

VIH or VIL

1.2

output voltage I0=100µA

2.0

3.0

-

0.15 -

0.2

-

0.2 B

-

0.15 -

0.2

-

0.2

-

0.15 -

MC74ACT132DG,MC74AC132DG,MC74ACT132DG,MC74ACT132DR2G,MC74AC132DR2G, 规格书,Datasheet 资料

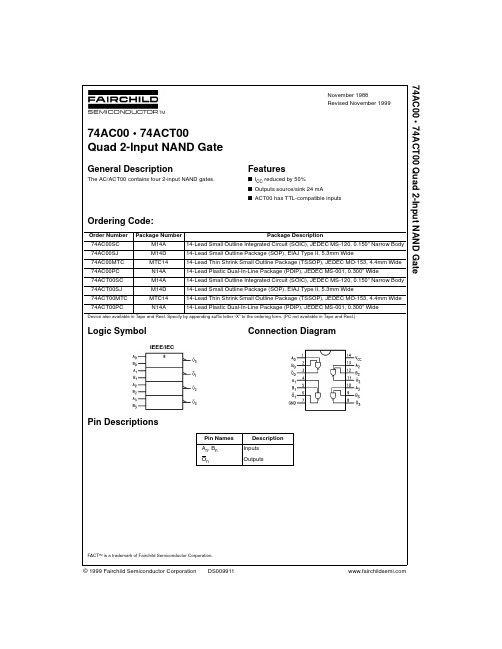

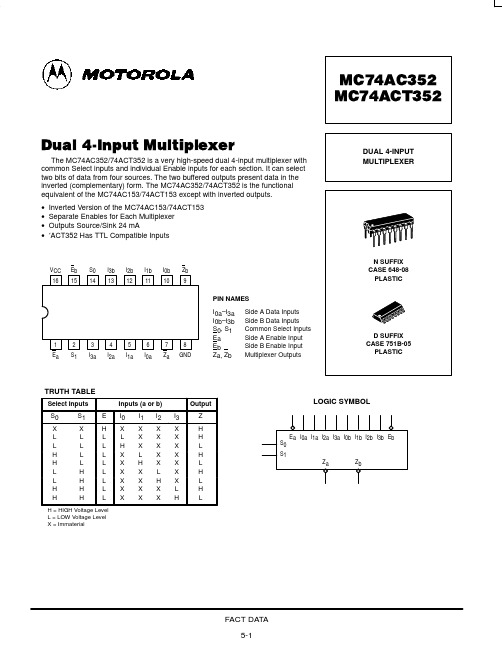

MC74AC132, MC74ACT132 Quad 2−Input NAND Schmitt TriggerThe MC74AC/74ACT132 contains four 2−input NAND gates which are capable of transforming slowly changing input signals into sharply defined, jitter−free output signals. In addition, they have greater noise margin than conventional NAND gates.Each circuit contains a 2−input Schmitt trigger. The Schmitt trigger uses positive feedback to effectively speed−up slow input transitions, and provide different input threshold voltages for positive and negative-going transitions. This hysteresis between the positive−going and negative−going input threshold is determined by resistor ratios and is essentially insensitive to temperature and supply voltage variations.Features•Schmitt Trigger Inputs•Outputs Source/Sink 24 mA•′ACT132 Has TTL Compatible Inputs•Pb−Free Packages are AvailableGNDVFigure 1. Pinout; 14−Lead Packages Conductors(Top View)FUNCTION TABLEInputs OutputA B YL L HL H HH L HH H LH = HIGH Voltage Level L = LOW Voltage LevelSee detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.ORDERING INFORMATIONRECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Max UnitV CC Supply Voltage′AC 2.0 5.0 6.0V ′ACT 4.5 5.0 5.5V in, V out DC Input Voltage, Output Voltage (Ref. to GND)0−V CC Vt r, t f Input Rise and Fall Time (Note 1)′AC Devices except Schmitt Inputs V CC @ 3.0 V−150−V CC @ 4.5 V−40−ns/V V CC @ 5.5 V−25−t r, t f Input Rise and Fall Time (Note 2)′ACT Devices except Schmitt Inputs V CC @ 4.5 V−10−ns/V V CC @ 5.5 V−8.0−T J Junction Temperature (PDIP)−−140°C T A Operating Ambient Temperature Range−402585°C I OH Output Current − High−−−24mAI OL Output Current − Low−−24mA1.V in from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.2.V in from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)74AC74ACUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV OH Minimum High LevelOutput Voltage 3.0 2.99 2.9 2.9I OUT = −50 m A4.5 4.49 4.4 4.4V5.5 5.49 5.4 5.4V*V IN = V IL or V IH3.0− 2.56 2.46−12 mA4.5− 3.86 3.76I OH−24 mA5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 3.00.0020.10.1I OUT = 50 m A4.50.0010.10.1V5.50.0010.10.1V*V IN = V IL or V IH3.0−0.360.4412 mA4.5−0.360.44I OL24 mA5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0m A V I = V CC, GNDI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V MinI CC Maximum QuiescentSupply Current 5.5−4.040m A V IN = V CC or GND*All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V CC.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74AC74ACUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay 3.3 2.0−13.0 1.514.0ns3−5 5.0 2.0−9.0 1.510.0t PHL Propagation Delay 3.3 2.0−13.5 1.515.0ns3−5 5.0 2.0−9.0 1.510.0*Voltage Range 3.3 V is 3.3 V ±0.3 V. Voltage Range 5.0 V is 5.0 V ±0.5 V.DC CHARACTERISTICSSymbol Parameter V CC(V)74ACT74ACTUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV OH Minimum High LevelOutput Voltage 4.5 4.49 4.4 4.4VI OUT = −50 m A5.5 5.49 5.4 5.4*V IN = V IL or V IH4.5− 3.86 3.76VI OH−24 mA 5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 4.50.0010.10.1VI OUT = 50 m A5.50.0010.10.1*V IN = V IL or V IH4.5−0.360.44VI OL24 mA 5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0m A V I = V CC, GND D I CCT Additional Max. I CC/Input 5.50.6− 1.5mA V I = V CC−2.1 VI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V Min I CC Maximum QuiescentSupply Current 5.5− 4.040m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74ACT74ACTUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay 5.0 3.0−11.5 2.513.0ns3−6 t PHL Propagation Delay 5.0 3.0−11.0 2.512.5ns3−5 *Voltage Range 5.0 V is 5.0 V ±0.5 V.INPUT CHARACTERISTICS (unless otherwise specified)Symbol Parameter V CC(V) 74AC 74ACT Unit Test ConditionsMaximum Positive Threshold 3.0 2.2V t+ 4.5 3.2 2.0V T A = Worst Case5.5 3.9Minimum Negative Threshold 3.00.5V t− 4.50.90.8V T A = Worst Case5.5 1.13.0 1.2V h(max)Maximum Hysteresis 4.5 1.4 1.2V T A = Worst Case5.5 1.63.00.3V h(min)Minimum Hysteresis 4.50.40.4V T A = Worst Case5.50.5CAPACITANCESymbol Parameter ValueTyp Unit Test ConditionsC IN Input Capacitance 4.5pF V CC = 5.0 V C PD Power Dissipation Capacitance30pF V CC = 5.0 VMARKING DIAGRAMSA = Assembly Location WL, L = Wafer Lot YY, Y = YearWW, W = Work Week G=Pb −Free PackagePDIP −14SOIC −14MC74AC132N AWLYYWWG MC74ACT132N AWLYYWWG 74AC132ALYWG SOEIAJ −1474ACT132ALYWG111411141414ORDERING INFORMATIONDevicePackage Shipping †MC74AC132N PDIP −1425 Units/RailMC74AC132NG PDIP −14(Pb −Free)MC74ACT132N PDIP −14MC74ACT132NG PDIP −14(Pb −Free)MC74AC132D SOIC −1455 Units/Rail MC74AC132DG SOIC −14(Pb −Free)MC74AC132DR2SOIC −142500/Tape & Reel MC74AC132DR2G SOIC −14(Pb −Free)MC74ACT132D SOIC −1455 Units/Rail MC74ACT132DG SOIC −14(Pb −Free)MC74ACT132DR2SOIC −142500/Tape & Reel MC74ACT132DR2G SOIC −14(Pb −Free)MC74AC132MEL SOEIAJ −142000/Tape & ReelMC74AC132MELG SOEIAJ −14(Pb −Free)MC74ACT132MEL SOEIAJ −14MC74ACT132MELGSOEIAJ −14(Pb −Free)PDIP−14 CASE 646−06 ISSUE PSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOEIAJ −14CASE 965−01ISSUE ANOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74ACT00MTC中文资料

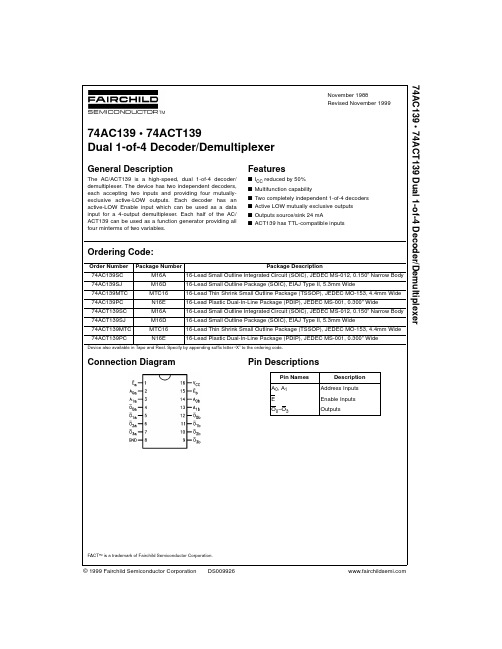

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering form. (PC not available in Tape and Reel.)

SN74ACT32中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

MC74ACT352D中文资料

KK74ACT574中文资料

TECHNICAL DATAKK 74ACT574Octal 3-StateNoninverting D Flip-FlopHigh-Performance Silicon-Gate CMOSThe KK HC/HCT574. The KK 74ACT574 may be used as a level converter for interfacing TTL or NMOS outputs to High Speed CMOS inputs.Data meeting the setup time is clocked to the outputs with the rising edge of the Clock. The Output Enable input does not affect the states of the flip-flops, but when Output Enable is high, all device outputs are forced to the high-impedance state; thus, data may be stored even whenthe outputs are not enabled.• TTL/NMOS Compatible Input Levels• Outputs Directly Interface to CMOS, NMOS, and TTL• Operating Voltage Range: 4.5 to 5.5 V• Low Input Current: 1.0 µA; 0.1 µA @ 25°C• Outputs Source/Sink 24 mAFUNCTION TABLEX = don’t careZ = high impedancePIN ASSIGNMENTLOGIC DIAGRAMPIN 20=V CCPIN 10 = GNDMAXIMUM RATINGS*Symbol Parameter ValueUnit V CC DC Supply Voltage (Referenced to GND) -0.5 to +7.0 VV IN DC Input Voltage (Referenced to GND) -0.5 to V CC +0.5 VV OUT DC Output Voltage (Referenced to GND) -0.5 to V CC +0.5 VI IN DC Input Current, per Pin ±20 mAI OUT DC Output Sink/Source Current, per Pin ±50 mAI CC DC Supply Current, V CC and GND Pins ±50 mAP D Power Dissipation in Still Air, Plastic DIP+ SOIC Package+ 750500mWTstg Storage Temperature -65 to +150 °CT L Lead Temperature, 1 mm from Case for 10 Seconds(Plastic DIP or SOIC Package)260 °C*Maximum Ratings are those values beyond which damage to the device may occur.Functional operation should be restricted to the Recommended Operating Conditions.+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°CSOIC Package: : - 7 mW/°C from 65° to 125°CRECOMMENDED OPERATING CONDITIONSSymbol Parameter MinMaxUnit V CC DC Supply Voltage (Referenced to GND) 4.5 5.5 VV IN, V OUT DC Input Voltage, Output Voltage (Referenced to GND) 0 V CC VT J Junction Temperature (PDIP) 140 °CT A Operating Temperature, All Package Types -40 +85 °CI OH Output Current - High -24 mAI OL Output Current - Low 24 mAt r, t f Input Rise and Fall Time *(except Schmitt Inputs) V CC =4.5 VV CC =5.5 V108.0ns/V* VINfrom 0.8 V to 2.0 VThis device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, V IN and V OUT should be constrained to the range GND≤(V IN or V OUT)≤V CC.Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC). Unused outputs must be left open.DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)V CC Guaranteed Limits Symbol Parameter TestConditions V25 °C -40°C to85°CUnitV IH Minimum High-Level Input Voltage V OUT=0.1 V or V CC-0.1 V 4.55.52.02.02.02.0VV IL Maximum Low -Level Input Voltage V OUT=0.1 V or V CC-0.1 V 4.55.50.80.80.80.8VV OH Minimum High-Level Output Voltage I OUT≤ -50 µA 4.55.54.45.44.45.4V*VIN=V IH or V ILI OH=-24 mAI OH=-24 mA4.55.53.864.863.764.76V OL Maximum Low-Level Output Voltage I OUT≤ 50 µA 4.55.50.10.10.10.1V*VIN=V IH or V ILI OL=24 mAI OL=24 mA4.55.50.360.360.440.44I IN Maximum InputLeakage CurrentV IN=V CC or GND 5.5±0.1 ±1.0 µA∆I CCT Additional Max.I CC/InputV IN=V CC - 2.1 V 5.5 1.5 mAI OZ Maximum Three-State LeakageCurrent V IN (OE)= V IH or V ILV IN =V CC or GNDV OUT =V CC or GND5.5±0.5 ±5.0 µAI OLD+Minimum DynamicOutput CurrentV OLD=1.65 V Max 5.575 mAI OHD+Minimum DynamicOutput CurrentV OHD=3.85 V Min 5.5-75 mAI CC Maximum QuiescentSupply Current(per Package)V IN=V CC or GND 5.58.0 80 µA* All outputs loaded; thresholds on input associated with output under test.+Maximum test duration 2.0 ms, one output loaded at a time.AC ELECTRICAL CHARACTERISTICS (V CC=5.0 V ± 10%, C L=50pF, Input t r=t f=3.0 ns)GuaranteedLimits Symbol Parameter 25 °C -40°C to 85°C UnitMin Max MinMaxf max Maximum Clock Frequency (50% Duty Cycle)(Figure 1)100 85 MHz t PLH Propagation Delay, Clock to Q (Figure 1) 2.5 11 2.0 12 nst PHL Propagation Delay, Clock to Q (Figure 1) 2.0 10 1.5 11 nst PZH Propagation Delay, Output Enable to Q (Figure 2) 2.0 9.5 1.5 10 nst PZL Propagation Delay, Output Enable to Q (Figure 2) 2.0 9.0 1.5 10 nst PHZ Propagation Delay, Output Enable to Q (Figure 2) 2.0 10.5 1.5 11.5 nst PLZ Propagation Delay, Output Enable to Q (Figure 2) 2.0 8.5 1.5 9.0 nsC IN Maximum Input Capacitance 4.5 4.5 pFTypical @25°C,V CC=5.0 VC PD Power Dissipation Capacitance 40 pFTIMING REQUIREMENTS (V CC=5.0 V ± 10%, C L=50pF, Input t r=t f=3.0 ns)GuaranteedLimit Symbol Parameter 25°C -40°C to 85°C Unitt SU Minimum Setup Time, Data to Clock (Figure 3) 2.5 2.5nst h Minimum Hold Time, Clock to Data (Figure 3) 1.0 1.0nst w Minimum Pulse Width, Clock (Figure 1) 3.0 4.0 nsFigure 1. Switching Waveforms Figure 2. Switching WaveformsFigure 3. Switching WaveformsEXPANDED LOGIC DIAGRAM。

KK74HC132AD中文资料

TECHNICAL DATAKK 74HC132AQuad 2-Input NAND Gatewith Schmitt-Trigger InputsHigh-Performance Silicon-Gate CMOSThe KK 74HC132A is identical in pinout to the LS/ALS132. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LS/ALSTTL outputs.The KK 74HC132A can be used to enhance noise immunity or to square up slowly changing waveforms.• Outputs Directly Interface to CMOS, NMOS, and TTL • Operating Voltage Range: 2.0 to 6.0 V • Low Input Current: 1.0 µA• High Noise Immunity Characteristic of CMOS DevicesLOGIC DIAGRAMPIN 14 =V CC PIN 7 = GNDPIN ASSIGNMENTFUNCTION TABLEInputs Output A B Y L L H L H H H L H H H LMAXIMUM RATINGS*Symbol Parameter ValueUnit V CC DC Supply Voltage (Referenced to GND) -0.5 to +7.0 VV IN DC Input Voltage (Referenced to GND) -1.5 to V CC +1.5 VV OUT DC Output Voltage (Referenced to GND) -0.5 to V CC +0.5 VI IN DC Input Current, per Pin ±20 mAI OUT DC Output Current, per Pin ±25 mAI CC DC Supply Current, V CC and GND Pins ±50 mAP D Power Dissipation in Still Air, Plastic DIP+ SOIC Package+ 750500mWTstg Storage Temperature -65 to +150 °CT L Lead Temperature, 1 mm from Case for 10 Seconds(Plastic DIP or SOIC Package)260 °C*Maximum Ratings are those values beyond which damage to the device may occur.Functional operation should be restricted to the Recommended Operating Conditions.+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°CSOIC Package: : - 7 mW/°C from 65° to 125°CRECOMMENDED OPERATING CONDITIONSSymbol Parameter MinMaxUnit V CC DC Supply Voltage (Referenced to GND) 2.0 6.0 VV IN, V OUT DC Input Voltage, Output Voltage (Referenced to GND) 0 V CC VT A Operating Temperature, All Package Types -55 +125 °Ct r, t f Input Rise and Fall Time (Figure 1) - nolimit*ns*When VIN≈ 0.5V CC, I CC> > quiescent current.This device contains protection circuitry to guard against damage due to high static voltages or electric fields.However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to thishigh-impedance circuit. For proper operation, V IN and V OUT should be constrained to the range GND≤(V IN orV OUT)≤V CC.Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC). Unusedoutputs must be left open.DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)V CC Guaranteed LimitSymbol Parameter TestConditions V25 °Cto-55°C ≤85°C≤125°CUnitV T+max Maximum Positive-Going InputThreshold Voltage V OUT=0.1 V⎢I OUT⎢≤ 20 µA2.04.56.01.53.154.21.53.154.21.53.154.2VV T+min MinimumPositive-Going InputThreshold Voltage V OUT=0.1 V⎢I OUT⎢≤ 20 µA2.04.56.01.02.33.00.952.252.950.952.252.95VV T-max MaximumNegative-Going InputThreshold Voltage V OUT=V CC-0.1 V⎢I OUT⎢≤ 20 µA2.04.56.00.92.02.60.952.052.650.952.052.65VV T-min MinimumNegative-Going InputThreshold Voltage V OUT=V CC-0.1 V⎢I OUT⎢≤ 20 µA2.04.56.00.30.91.20.30.91.20.30.91.2VV H max Note Maximum HysteresisVoltageV OUT=0.1 V or V CC-0.1 V⎢I OUT⎢≤ 20 µA2.04.56.01.22.253.01.22.253.01.22.253.0VV H min Note Minimum HysteresisVoltageV OUT=0.1 V or V CC-0.1 V⎢I OUT⎢≤ 20 µA2.04.56.00.20.40.50.20.40.50.20.40.5VV OH Minimum High-Level Output Voltage V IN≤V T-min or V T+max⎢I out⎢≤ 20 µA2.04.56.01.94.45.91.94.45.91.94.45.9VV IN≤V T-min or V T+max⎢I OUT⎢≤ 4.0 mA⎢I OUT⎢≤ 5.2 mA4.56.03.985.483.845.343.75.2V OL Maximum Low-Level Output Voltage V IN≥V T+max⎢I OUT⎢≤ 20 µA2.04.56.00.10.10.10.10.10.10.10.10.1VV IN≥ V T+max⎢I OUT⎢≤ 4.0 mA⎢I OUT⎢≤ 5.2 mA4.56.00.260.260.330.330.40.4I IN Maximum InputLeakage CurrentV IN=V CC or GND 6.0±0.1±1.0 ±1.0 µAI CC Maximum QuiescentSupply Current(per Package) V IN=V CC or GNDI OUT=0µA6.0 1.0 10 40 µANote. V H min>(V T+min)-(V T-max); V H max=(V T+max)+(V T-min).AC ELECTRICAL CHARACTERISTICS (C L=50pF,Input t r=t f=6.0 ns)V CC Guaranteed LimitSymbol Parameter V25 °Cto-55°C≤85°C ≤125°C Unitt PLH, t PHL Maximum Propagation Delay, Input A or B to Output Y (Figures 1 and 2) 2.04.56.0125252115531261903832nst TLH, t THL Maximum Output Transition Time, Any Output (Figures 1 and 2) 2.04.56.07515139519161102219nsC IN Maximum Input Capacitance - 10 10 10 pFPower Dissipation Capacitance (Per Gate) Typical @25°C,V CC=5.0 VC PD Used to determine the no-load dynamic powerconsumption: P D=C PD V CC2f+I CC V CC24 pFFigure 1. Switching Waveforms。

74ACT323PCX中文资料

June 1988Revised October 199874ACT323 8-Bit Universal Shift/Storage Register with Synchronous Reset and Common I/O Pins © 1999 Fairchild Semiconductor Corporation DS009787.prf 74ACT3238-Bit Universal Shift/Storage Register withSynchronous Reset and Common I/O PinsGeneral DescriptionThe ACT323 is an 8-bit universal shift/storage register with3-STATE outputs. Parallel load inputs and flip-flop outputsare multiplexed to minimize pin count. Separate serialinputs and outputs are provided for Q0 and Q7 to alloweasy cascading. Four operation modes are possible: hold(store), shift left, shift right and parallel load.Featuress I CC and I OZ reduced by 50%s Common parallel I/O for reduced pin counts Additional serial inputs and outputs for expansions Four operating modes: shift left, shift right, load andstores3-STATE outputs for bus-oriented applicationss Outputs source/sink 24 mAs TTL-compatible inputsOrdering Code:Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic Symbols Connection DiagramPin Assignmentfor DIPPin DescriptionsFACT™ is a trademark of Fairchild Semiconductor Corporation.Order Number Package Number Package Description74ACT323PC N20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePin Name DescriptionCP Clock Pulse InputDS0Serial Data Input for Right ShiftDS7Serial Data Input for Left ShiftS0, S1Mode Select InputsSR Synchronous Reset InputOE1, OE23-STATE Output Enable InputsI/O0–I/O7Multiplexed Parallel Data Inputs or3-ST ATE Parallel Data OutputsQ0, Q7Serial Outputs 274A C T 323Functional DescriptionThe ACT323 contains eight edge-triggered D-type flip-flops and the interstage logic necessary to perform synchronous reset, shift left, shift right, parallel load and hold operations.The type of operation is determined by S 0 and S 1 as shown in the Mode Select Table. All flip-flop outputs are brought out through 3-STATE buffers to separate I/O pins that also serve as data inputs in the parallel load mode. Q 0 and Q 7are also brought out on other pins for expansion in serial shifting of longer words.A LOW signal on SR overrides the Select inputs and allows the flip-flops to be reset by the next rising edge of CP . Allother state changes are also initiated by the LOW-to-HIGH CP transition. Inputs can change when the clock is in either state provided only that the recommended setup and hold times, relative to the rising edge of CP , are observed.A HIGH signal on either OE 1 or OE 2 disables the 3-ST ATE buffers and puts the I/O pins in the high impedance state.In this condition the shift, load, hold and reset operations can still occur. The 3-STA TE buffers are also disabled by HIGH signals on both S 0 and S 1 in preparation for a paral-lel load operation.Mode Select TableH = HIGH Voltage Level L = LOW Voltage Level X = Immaterial= LOW-to-HIGH Clock T ransitionInputsResponseSR S 1S 0CP L X X Synchronous Reset; Q 0–Q 7 = LOW H H HParallel Load; I/O n →Q nH LHShift Right; DS 0→Q 0, Q 0→Q 1, etc.H H L Shift Left; DS 7→Q 7, Q 7→Q 6, etc. HLLXHold 74ACT323Logic DiagramPlease note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays. 474A C T 323Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, with-out exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT ™ circuits outside databook specifications.DC Electrical CharacteristicsNote 2: All outputs loaded; thresholds on input associated with output under test.Note 3: Maximum test duration 2.0 ms, one output loaded at a time.Supply Voltage (V CC )−0.5V to +7.0VDC Input Diode Current (I IK )V I = −0.5V −20 mA V I = V CC + 0.5V +20 mADC Input Voltage (V I )−0.5V to V CC + 0.5VDC Output Diode Current (I OK ) V O = −0.5V −20 mA V O = V CC + 0.5V +20 mADC Output Voltage (V O )−0.5V to V CC + 0.5VDC Output Source or Sink Current (I O ) ±50 mA DC V CC or Ground Current Per Output Pin (I CC or I GND )±50 mAStorage Temperature (T STG )−65°C to +150°CJunction Temperature (T J )PDIP140°CSupply Voltage (V CC ) 4.5V to 5.5V Input Voltage (V I )0V to V CC Output Voltage (V O )0V to V CCOperating Temperature (T A )−40°C to +85°CMinimum Input Edge Rate (∆V/∆t)V IN from 0.8V to 2.0V V CC @ 4.5V , 5.5V125 mV/nsSymbol ParameterV CC T A = +25°C T A = −40°C to +85°C Units Conditions (V)Typ Guaranteed LimitsV IH Minimum High Level 4.5 1.5 2.0 2.0V V OUT = 0.1V Input Voltage 5.5 1.5 2.0 2.0or V CC − 0.1V V IL Maximum Low Level 4.5 1.50.80.8V V OUT = 0.1V Input Voltage 5.5 1.50.80.8or V CC − 0.1V V OHMinimum High Level 4.5 4.49 4.4 4.4VI OUT = −50 µA Output Voltage5.5 5.495.4 5.4V IN = V IL or V IH4.5 3.86 3.76V I OH = −24 mA5.54.864.76I OH = −24 mA (Note 2)V OLMaximum Low Level 4.50.0010.10.1VI OUT = 50 µA Output Voltage5.50.0010.10.1V IN = V IL or V IH4.50.360.44V I OL = −24 mA5.50.360.44I OL = −24 mA (Note 2)I IN Maximum Input 5.5±0.1±1.0µA V I = V CC , GND Leakage Current I OZT Maximum I/O 5.5±0.3±3.0µA V I/O = V CC or GND Leakage Current V IN = V IH , V IL I CCT Maximum I CC /Input 5.5 0.61.5mA V I = V CC −2.1V I OLD Minimum Dynamic 5.575mA V OLD = 1.65V Max I OHD Output Current (Note 3) 5.5 −75mA V OHD = 3.85V Min I CCMaximum Quiescent 5.54.040.0µAV IN = V CC or GNDSupply Current74ACT323AC Electrical CharacteristicsNote 4: Voltage Range 5.0 is 5.0V ±0.5VAC Operating RequirementsNote 5: Voltage Range 5.0 is 5.0V ±0.5VCapacitanceV CCT A = 25°C T A = −40°C to +85°CSymbol Parameter(V)C L = 50 pFC L = 50 pF Units(Note 4)Min Typ MaxMin Maxf max Maximum Input Frequency 5.0120125 110MHz t PLH Propagation Delay 5.05.09.012.5 4.014.0ns CP to Q 0 or Q 7t PHL Propagation Delay 5.05.09.013.54.515.0nsCP to Q 0 or Q 7t PLH Propagation Delay 5.05.08.512.54.514.5nsCP to I/O nt PHL Propagation Delay 5.06.010.014.55.016.0nsCP to I/O nt PZH Output Enable Time 5.0 3.57.511.0 3.012.5ns t PZL Output Enable Time 5.0 3.57.511.5 3.013.0ns t PHZ Output Disable Time 5.0 4.08.512.5 3.013.5ns t PLZOutput Disable Time5.03.08.011.52.512.5nsT A = 25°CT A = −40°C to +85°CSymbolParameterV CC C L = 50 pF C L = 50 pF Units(V)V CC = +5.0V V CC = +5.0V(Note 5)Typ Guaranteed Minimum t SSetup Time, HIGH or LOW 5.02.05.05.0ns S 0 or S 1 to CPt HHold Time, HIGH or LOW 5.00 1.5 1.5 nsS 0 or S 1 to CPt SSetup Time, HIGH or LOW 5.0 1.0 4.0 4.5 nsI/O n , DS 0, DS 7 to CPt HHold Time, HIGH or LOW 5.00 1.0 1.0 nsI/O n , DS 0, DS 7 to CPt SSetup Time, HIGH or LOW 5.0 1.0 2.5 2.5 nsSR to CPt HHold Time, HIGH or LOW 5.00 1.0 1.0 nsSR to CPt WCP Pulse Width 5.0 2.0 4.0 4.5 nsHIGH or LOWSymbol ParameterTyp Units ConditionsC IN Input Capacitance4.5 pF V CC = OPEN C PDPower Dissipation Capacitance170pFV CC = 5.0VF a irch ild d o e s n o t a ssu m e a n y re spo n sib ility fo r u se o f a n y circu itry de scrib e d , n o circu it pa ten t lice nse s a re im p lie d a nd F a irch ild re se rv e s the rig h t a t a n y tim e w ith ou t n o tice to cha n g e sa id circu itry an d sp e cifica tio n s.74A C T 323 8-B i t U n i v e r s a l S h i f t /S t o r a g e R e g i s t e r w i t h S y n c h r o n o u s R e s e t a n d C o m m o n I /O P i n sLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePackage Number N20A。

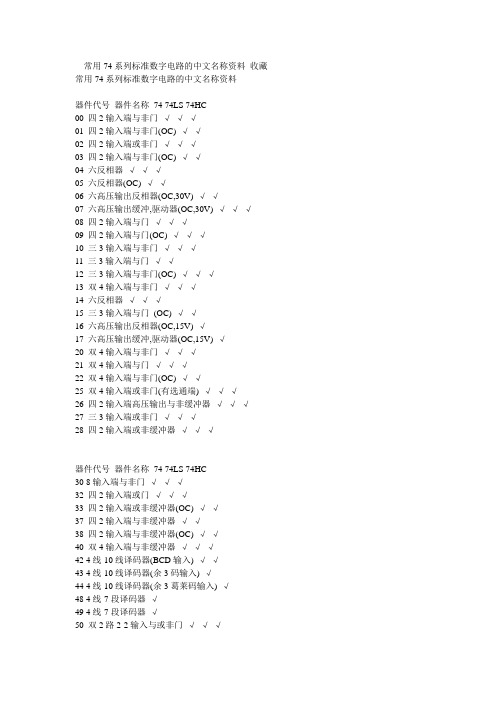

常用74系列标准数字电路的中文名称资料

常用74系列标准数字电路的中文名称资料收藏常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门(OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√器件代号器件名称74 74LS 74HC30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√器件代号器件名称74 74LS 74HC74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√74F74是高速的TTL芯片和74HC一样就是速度高109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√d触发器芯片有:74HC74 74LS90 双D触发器74LS7474LS364八D触发器(三态)7474、74 H74、74F74、74ALS74、74L74、74LS74A、74S74、74HC73、74C74双D型正沿触发器(带预置和清除端)74174、74LS174、74F174、74ALS174、74S174、74HC174、74C174六D型触发器(带清除端)74175、74LS175、74F175、74ALS175、74S175、74HC175、74C175 四D型触发器(带清除端)74273、74LS273、74S273、74F273、74ALS273、74HC273 八D型触发器(带清除端)74LS364八D触发器(三态)74LS377、74F377、74S3777八D 触发器74LS378、74F378、74S378、74HC378六D 触发器74LS379、74F379、74S379、74HC379八D 触发器。

74ACT32PC中文资料

元器件交易网

74AC32 • 74ACT32

Absolute Maximum Ratings(Note 1)

Supply Voltage (VCC) DC Input Diode Current (IIK) VI = −0.5V VI = VCC + 0.5V DC Input Voltage (VI) DC Output Diode Current (IOK) VO = −0.5V VO = VCC + 0.5V DC Output Voltage (VO) DC Output Source or Sink Current (IO) DC VCC or Ground Current per Output Pin (ICC or IGND) Storage Temperature (TSTG) Junction Temperature (TJ) PDIP 140°C ±50 mA −65°C to +150°C ±50 mA −20 mA +20 mA −0.5V to VCC + 0.5V −20 mA +20 mA −0.5V to VCC + 0.5V −0.5V to +7.0V

74ACT139MTC中文资料

IEEE/IEC

FIGURE 1. Gate Functions (Each Half)

Truth Table

Inputs E H L L L L A0 X L H L H A1 X L L H H O0 H L H H H Outputs O1 H H L H H O2 H H H L H O3 H H H H L

2.0V to 6.0V 4.5V to 5.5V 0V to VCC 0V to VCC −40°C to +85°C

125 mV/ns

DC Electrical Characteristics for AC

Symbol VIH Parameter Minimum HIGH Level Input Voltage VIL Maximum LOW Level Input Voltage VOH Minimum HIGH Level Output Voltage VCC (V) 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 VOL Maximum LOW Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 IIN (Note 4) IOLD IOHD ICC (Note 4) Maximum Input Leakage Current Minimum Dynamic Output Current (Note 3) Maximum Quiescent Supply Current 5.5 5.5 5.5 5.5 4.0 0.002 0.001 0.001 TA = +25°C Typ 1.5 2.25 2.75 1.5 2.25 2.75 2.99 4.49 5.49 2.1 3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 2.56 3.86 4.86 0.1 0.1 0.1 0.36 0.36 0.36 ± 0.1 TA = −40°C to +85°C Guaranteed Limits 2.1 3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 VIN = VIL or VIH 2.46 3.76 4.76 0.1 0.1 0.1 VIN = VIL or VIH 0.44 0.44 0.44 ± 1.0 75 −75 40.0 µA mA mA µA V IOL = 12 mA IOL = 24 mA IOL = 24 mA (Note 2) VI = VCC, GND VOLD = 1.65V Max VOHD = 3.85V Min VIN = VCC or GND V IOUT = 50 µA V IOH = −12 mA IOH = −24 mA IOH = −24 mA (Note 2) V IOUT = −50 µA V VOUT = 0.1V or VCC − 0.1V V Units Conditions VOUT = 0.1V or VCC − 0.1V

74系列中文资料(超级全)

│14 13 12 11 10 9 8│

)

│ Y = A+B

│ 1 2 3 4 5 6 7│

└┬─┬─┬─┬─┬─┬─┬┘

1A 1B 1Y 2A 2B 2Y GND

Vcc 4Y 4B 4A 3Y 3B 3A

┌┴─┴─┴─┴─┴─┴─┴┐ 2 输入四或非门 74LS02

│14 13 12 11 10 9 8│

常见数字逻辑器件中文注解

74LS12 TTL 开路输出 3 输入端三与非门

74 系列:

74LS121 TTL 单稳态多谐振荡器

74LS00 TTL 2 输入端四与非门

74LS122 TTL 可再触发单稳态多谐振荡器

74LS01 TTL 集电极开路 2 输入端四与非门

74LS123 TTL 双可再触发单稳态多谐振荡器

└┬─┬─┬─┬─┬─┬─┬─┬┘

-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND

8*2 输入比较器 B8 A8 B7 A7 B6 A6 B5 A5

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2 输入比较器 74LS688

│20 19 18 17 16 15 14 13 12 11│

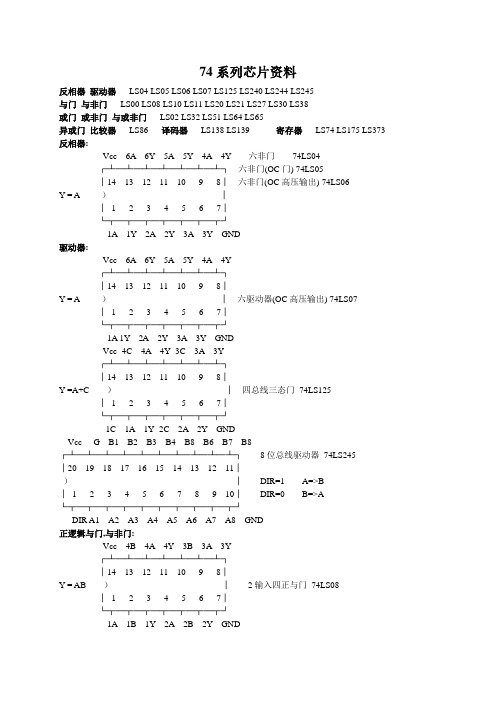

寄存器 LS74 LS175 LS373

反相器:

Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04

┌┴─┴─┴─┴─┴─┴─┴┐ 六非门(OC 门) 74LS05

_ │14 13 12 11 10 9 8│ 六非门(OC 高压输出) 74LS06

Y=A )

│

│ 1 2 3 4 5 6 7│

3-8 译码器 74LS138

Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _

电子行业74系列芯片中文资料超级全

电子行业74系列芯片中文资料超级全CD4506双二组2输入可扩展或非门CD4508双4位锁存D型触发器CD4510可预置BCD码加/减计数器CD4511BCD锁存,7段译码,驱动器CD4512八路数据选择器CD4513BCD锁存,7段译码,驱动器(消隐)CD45144位锁存,4线-16线译码器CD45154位锁存,4线-16线译码器CD4516可预置4位二进制加/减计数器CD4517双64位静态移位寄存器CD4518双BCD同步加计数器CD4519四位与或选择器CD4520双4位二进制同步加计数器CD452124级分频器CD4522可预置BCD同步1/N计数器CD4526可预置4位二进制同步1/N计数器CD4527BCD比例乘法器CD4528双单稳态触发器CD4529双四路/单八路模拟开关CD4530双5输入端优势逻辑门CD453112位奇偶校验器CD45328位优先编码器CD4536可编程定时器CD4538精密双单稳CD4539双四路数据选择器CD4541可编程序振荡/计时器CD4543BCD七段锁存译码,驱动器CD4544BCD七段锁存译码,驱动器CD4547BCD七段译码/大电流驱动器CD4549函数近似寄存器CD4551四2通道模拟开关CD4553三位BCD计数器CD4555双二进制四选一译码器/分离器CD4556双二进制四选一译码器/分离器CD4558BCD八段译码器CD4560"N"BCD加法器CD4561"9"求补器CD4573四可编程运算放大器CD4574四可编程电压比较器CD4575双可编程运放/比较器CD4583双施密特触发器CD4584六施密特触发器CD45854位数值比较器CD45998位可寻址锁存器。

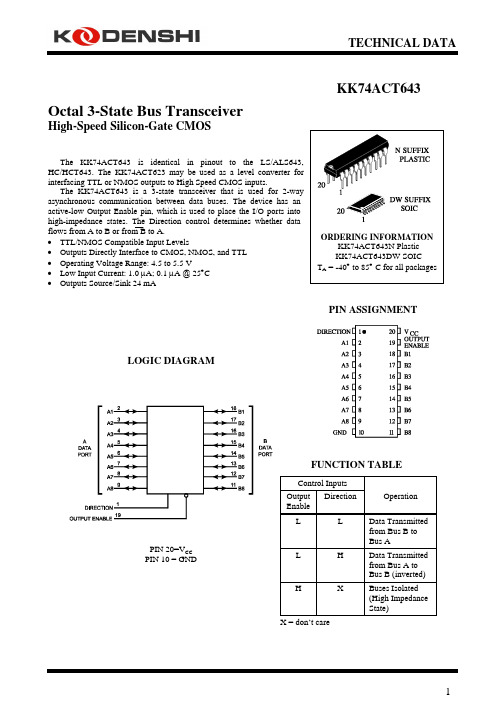

KK74ACT643N中文资料

TECHNICAL DATAKK 74ACT643Octal 3-State Bus TransceiverHigh-Speed Silicon-Gate CMOSThe KK HC/HCT643. The KK 74ACT623 may be used as a level converter for interfacing TTL or NMOS outputs to High Speed CMOS inputs.The KK asynchronous communication between data buses. The device has an active-low Output Enable pin, which is used to place the I/O ports into high-impedance states. The Direction control determines whether dataflows from A to B or from B to A.• TTL/NMOS Compatible Input Levels• Outputs Directly Interface to CMOS, NMOS, and TTL• Operating Voltage Range: 4.5 to 5.5 V• Low Input Current: 1.0 µA; 0.1 µA @ 25°C • Outputs Source/Sink 24 mAPIN ASSIGNMENTLOGIC DIAGRAMPIN 20=V CC PIN 10 = GNDFUNCTION TABLEControl InputsOutput EnableDirection OperationL L Data Transmittedfrom Bus B to Bus A L H Data Transmittedfrom Bus A to Bus B (inverted) H X Buses Isolated(High Impedance State) X = don’t careMAXIMUM RATINGS*Symbol Parameter ValueUnit V CC DC Supply Voltage (Referenced to GND) -0.5 to +7.0 VV IN DC Input Voltage (Referenced to GND) -0.5 to V CC +0.5 VV OUT DC Output Voltage (Referenced to GND) -0.5 to V CC +0.5 VI IN DC Input Current, per Pin ±20 mAI OUT DC Output Sink/Source Current, per Pin ±50 mAI CC DC Supply Current, V CC and GND Pins ±50 mAP D Power Dissipation in Still Air, Plastic DIP+ SOIC Package+ 750500mWTstg Storage Temperature -65 to +150 °CT L Lead Temperature, 1 mm from Case for 10 Seconds(Plastic DIP or SOIC Package)260 °C*Maximum Ratings are those values beyond which damage to the device may occur.Functional operation should be restricted to the Recommended Operating Conditions.+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°CSOIC Package: : - 7 mW/°C from 65° to 125°CRECOMMENDED OPERATING CONDITIONSSymbol Parameter MinMaxUnit V CC DC Supply Voltage (Referenced to GND) 4.5 5.5 VV IN, V OUT DC Input Voltage, Output Voltage (Referenced to GND) 0 V CC VT J Junction Temperature (PDIP) 140 °CT A Operating Temperature, All Package Types -40 +85 °CI OH Output Current - High -24 mAI OL Output Current - Low 24 mAt r, t f Input Rise and Fall Time *(except Schmitt Inputs) V CC =4.5 VV CC =5.5 V108.0ns/V* VINfrom 0.8 V to 2.0 VThis device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, V IN and V OUT should be constrained to the range GND≤(V IN or V OUT)≤V CC.Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC). Unused outputs must be left open.DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)V CC Guaranteed Limits Symbol Parameter TestConditions V25 °C -40°C to85°CUnitV IH Minimum High-Level Input Voltage V OUT= 0.1 V or V CC-0.1 V 4.55.52.02.02.02.0VV IL Maximum Low -Level Input Voltage V OUT= 0.1 V or V CC-0.1 V 4.55.50.80.80.80.8VV OH Minimum High-Level Output Voltage I OUT≤ -50 µA 4.55.54.45.44.45.4V*VIN=V IH or V ILI OH=-24 mAI OH=-24 mA4.55.53.864.863.764.76V OL Maximum Low-Level Output Voltage I OUT≤ 50 µA 4.55.50.10.10.10.1V*VIN= V IH or V ILI OL=24 mAI OL=24 mA4.55.50.360.360.440.44I IN Maximum InputLeakage CurrentV IN=V CC or GND 5.5±0.1 ±1.0 µA∆I CCT Additional Max.I CC/InputV IN=V CC - 2.1 V 5.5 1.5 mAI OZ Maximum Three-State LeakageCurrent V IN (OE)= V IH or V ILV IN =V CC or GNDV OUT =V CC or GND5.5±0.6 ±6.0 µAI OLD+Minimum DynamicOutput CurrentV OLD=1.65 V Max 5.575 mAI OHD+Minimum DynamicOutput CurrentV OHD=3.85 V Min 5.5-75 mAI CC Maximum QuiescentSupply Current(per Package)V IN=V CC or GND 5.58.0 80 µA* All outputs loaded; thresholds on input associated with output under test.+Maximum test duration 2.0 ms, one output loaded at a time.AC ELECTRICAL CHARACTERISTICS (V CC=5.0 V ± 10%, C L=50pF,Input t r=t f=3.0 ns)GuaranteedLimits Symbol Parameter 25 °C -40°C to 85°C UnitMin Max MinMax t PLH Propagation Delay, A to B or B to A(Figure 1)1.5 8.0 1.0 9.0 nst PHL Propagation Delay, A to B or B to A(Figure 1)1.5 8.0 1.0 9.0 nst PZH Propagation Delay, Direction or Output Enable toA orB (Figure 2)1.5 10.5 1.0 11.5 nst PZL Propagation Delay, Direction or Output Enable toA orB (Figure 2)1.5 10.5 1.0 11.5 nst PHZ Propagation Delay, Direction or Output Enable toA orB (Figure 2)1.5 10.5 1.0 11.5 nst PLZ Propagation Delay, Direction or Output Enable toA orB (Figure 2)1.5 10.5 1.0 11.5 nsC IN Maximum Input Capacitance 4.5 4.5 pFC OUT Maximum Tree-State I/O Capacitance(Output in High-Impedance State015 15pF Typical @25°C,V CC=5.0 VC PD Power Dissipation Capacitance 45 pFFigure 1. Switching Waveforms Figure 2. Switching WaveformsEXPANDED LOGIC DIAGRAM。

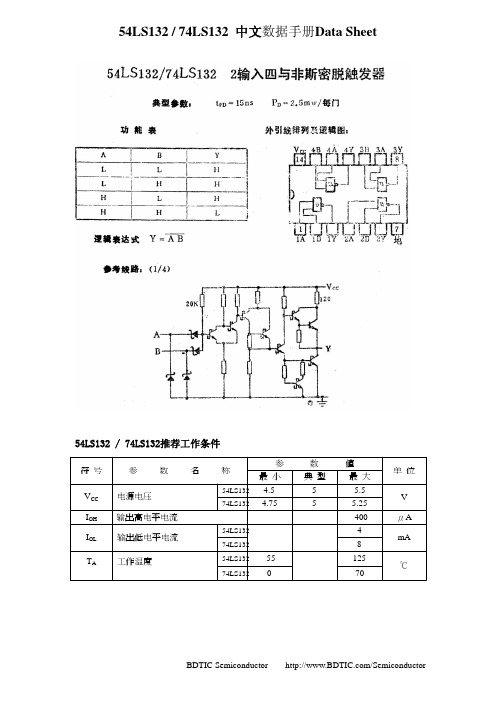

54LS132 74LS132 中文数据手册Data Sheet

54LS132 / 74LS132 中文数据手册Data Sheet54LS132 / 74LS132推荐工作条件 参 数 值 最 小 典 型 最 大 符 号 参 数 名 称单 位 54LS132 4.55 5.5 74LS132 4.75 5 5.25 V CC 电源电压VI OH输出高电平电流 -400 μA 54LS132 4 I OL 输出低电平电流 T A 工作温度 mA ℃74LS1328 54LS132 -55 125 74LS132070BDTIC Semiconductor /Semiconductor54LS132 / 74LS132 参数 参 数 值 最小典型最大 符 号 参 数 名 称 单位测 试 条件+ T 正跃变阈值电压 1.4 1.6 1.9V V CC =5V_ T 负跃变阈值电压 0.50.81V V CC =5VV T+-V T- 滞后电压 0.40.8V V CC =5V V CD 输入钳位电压 -1.5V V =最小 I =-18mA CC I 54LS132 2.5 3.4 V V CC =最小 I OH =最大V I =V T V OH输出高电平 74LS132 2.7 3.4-最小 54,74 0.25 0.4 I OL =4mA V CC =最小 V V OL 输出低电平74LS132 0.350.5I OL =8mA V I =V T +最大 +T 正跃变输入电流 -0.14mA V CC =5V V I =V T +_ T 负跃变输入电流 -0.18mA V CC =5V V I =V TI I 输入电流(最大输入电压时) 0.1mA V CC =最大 V I =7VI IH输入高电平电流 20μA V CC =最大 V I =2.7VI IL输入低电平电流 -0.4mA V CC =最大 V IL =2.7V I OS短路输出电流 -15-100mA V CC =最大 I CCH高电平输出电源电流 5.911mA I CCL 低电平输出电源电流 8.214mAt PLH 传输延迟(低到高) 1522ns t PHL传输延迟(高到低) 15 22 ns C L =15pF R L =2k ΩBDTIC Semiconductor /SemiconductorBDTIC Semiconductor /Semiconductor。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TECHNICAL DATAKK 74ACT132Quad 2-Input NAND Gatewith Schmitt-Trigger InputsHigh-Performance Silicon-Gate CMOSThe KK HC/HCT132. The KK 74ACT132 may be used as a level converter for interfacing TTL or NMOS outputs to High Speed CMOS inputs.The KK 74ACT132 can be used to enhance noise immunity or to squareup slowly changing waveforms.• TTL/NMOS Compatible Input Levels• Outputs Directly Interface to CMOS, NMOS, and TTL• Operating Voltage Range: 4.5 to 5.5 V• Low Input Current: 1.0 µA; 0.1 µA @ 25°C• Outputs Source/Sink 24 mALOGIC DIAGRAMPIN 14 =V CC PIN 7 = GNDPIN ASSIGNMENTFUNCTION TABLEInputs Output A B Y L L H L H H H L H H H LMAXIMUM RATINGS*Symbol Parameter ValueUnit V CC DC Supply Voltage (Referenced to GND) -0.5 to +7.0 VV IN DC Input Voltage (Referenced to GND) -0.5 to V CC +0.5 VV OUT DC Output Voltage (Referenced to GND) -0.5 to V CC +0.5 VI IN DC Input Current, per Pin ±20 mAI OUT DC Output Sink/Source Current, per Pin ±50 mAI CC DC Supply Current, V CC and GND Pins ±50 mAP D Power Dissipation in Still Air, Plastic DIP+ SOIC Package+ 750500mWTstg Storage Temperature -65 to +150 °CT L Lead Temperature, 1 mm from Case for 10 Seconds(Plastic DIP or SOIC Package)260 °C*Maximum Ratings are those values beyond which damage to the device may occur.Functional operation should be restricted to the Recommended Operating Conditions.+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°CSOIC Package: : - 7 mW/°C from 65° to 125°CRECOMMENDED OPERATING CONDITIONSSymbol Parameter MinMaxUnit V CC DC Supply Voltage (Referenced to GND) 4.5 5.5 VV IN, V OUT DC Input Voltage, Output Voltage (Referenced to GND) 0 V CC VT J Junction Temperature (PDIP) 140 °CT A Operating Temperature, All Package Types -40 +85 °CI OH Output Current - High -24 mAI OL Output Current - Low 24 mAt r, t f Input Rise and Fall Time *(except Schmitt Inputs) V CC =4.5 VV CC =5.5 V108.0ns/V* VINfrom 0.8 V to 2.0 VThis device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, V IN and V OUT should be constrained to the range GND≤(V IN or V OUT)≤V CC.Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC). Unused outputs must be left open.DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)V CC Guaranteed Limits Symbol Parameter TestConditions V25 °C -40°C to85°CUnitV OH Minimum High-LevelOutput Voltage I OUT≤ -50 µA 4.55.54.45.44.45.4V*VIN≤ V T - min or V T +maxI OH=-12 mAI OH=-24 mAI OH=-24 mA4.55.53.864.863.764.76V OL Maximum Low-LevelOutput Voltage I OUT≤ 50 µA 4.55.50.10.10.10.1V*VIN≥ V T +maxI OL=12 mAI OL=24 mAI OL=24 mA4.55.50.360.360.440.44V T +max MaximumPositive-Going Input ThresholdVoltage V OUT =0.1 VT A = Worst Case4.55.52.02.0VV T - min Minimum Negative-Going Input ThresholdVoltage V OUT = V CC - 0.1 VT A = Worst Case4.55.50.80.8VV H max MaximumHysteresisVoltage V OUT =0.1 V or V CC - 0.1 VT A = Worst Case4.55.51.21.2VV H min MinimumHysteresisVoltage V OUT =0.1 V or V CC - 0.1 VT A = Worst Case4.55.50.40.4VI IN Maximum InputLeakage CurrentV IN=V CC or GND 5.5±0.1 ±1.0 µA∆I CC Addition QuiescentSupply CurrentV IN=V CC -2.1 V 5.5 1.5 mAI OLD+Minimum DynamicOutput CurrentV OLD=1.65 V Max 5.575 mAI OHD+Minimum DynamicOutput CurrentV OHD=3.85 V Min 5.5-75 mAI CC Maximum QuiescentSupply Current(per Package)V IN=V CC or GND 5.5 4.0 40 µA* All outputs loaded; thresholds on input associated with output under test.+Maximum test duration 2.0 ms, one output loaded at a time.Note: V H=(V T+)-(V T-)AC ELECTRICAL CHARACTERISTICS (V CC=5.0 V ± 10%, C L=50pF,Input t r=t f=3.0 ns)LimitsGuaranteed Symbol Parameter 25 °C -40°C to 85°C UnitMin Max MinMax3.0 11.5 2.5 13.0 nst PLH Propagation Delay, Input A or B to Output Y(Figure 1)t PHL Propagation Delay, Input A or B to Output Y3.0 11.0 2.5 12.5 ns(Figure 1)C IN Maximum Input Capacitance 4.5 4.5 pFTypical @25°C,V CC=5.0 VC PD Power Dissipation Capacitance 30 pFFigure 1. Switching Waveforms。