L813PW中文资料

CWP130中文资料

1IXYS reserves the right to change limits, test conditions and dimensions ContentsPage Symbols and Definitions 2Nomenclature2General Information 3A ssembly Instructions4FRED, Rectifier Diode and Thyristor Chips in Planar Design5IGBT ChipsV CESI CG-Series, Low V CE(sat) B2 Types 600 ...1200 V7 ... 20 A 6G-Series, Fast C2 Types600 V 7 ... 20 A 6S-Series, SCSOA Capability, Fast Types 600 V10 ... 20 A 6E-Series, Improved NPT³ technology1200 ... 1700 V20 ... 150 A7MOSFET ChipsV DSSR DS(on)HiPerFET TM Power MOSFET70 ...1200 V 0.005 ... 4.5 Ω8-10PolarHT TM MOSFET, very Low R DS(on)55 ... 300 V 0.015 ... 0.135 Ω11P-Channel Power MOSFET-100 ...-600 V 0.06 ... 1.2 Ω12N-Channel Depletion Mode MOSFET 500 ...1000 V30 ... 110 Ω12Layouts13-17Bipolar ChipsV RRM / V DRMI F(AV)M / I T(AV)M Rectifier Diodes 1200 ... 1800 V 12 ... 416 A 18-19FREDs600 ... 1200 V 8 ... 244 A 20-21Low Leakage FREDs 200 ... 1200 V 9 ... 148 A 22-23SONIC-FRD TM Diodes 600 ... 1800 V 12 ... 150 A 24-25GaAs Schottky Diodes 100 ... 600 V 3.5 ... 25 A 26-27Schottky Diodes8 ... 200 V 28 ... 145 A 28-31Phase Control Thyristors 800 ... 2200 V 15 ... 540 A 32-33Fast Rectifier Diodes1600 ... 1800 V10 ... 26 A34Direct Copper Bonded (DCB), Direct Alu Bonded (DAB) Ceramic SubstratesWhat is DCB/DAB?35DCB Specification362© 2004 IXYS All rights reservedSymbols and DefinitionsC ies Input capacitance of IGBT C iss Input capacitance of MOSFET-di/dt Rate of decrease of forward current I C DC collector current I D Drain currentI FForward current of diodeI F(AV)M Maximum average forward current at specified T h I FSM Peak one cycle surge forward current I GT Gate trigger current I R Reverse currentI RM Maximum peak recovery current I TForward current of thyristorI T(AV)M Maximum average on-state current of a thyristor at specified T hI TSM Maximum surge current of a thyristor R DS(on)Static drain-source on-state resistance R thjc Thermal resistance junction to case r TSlope resistance of a thyristor or diode (for power loss calculations) T case Case temperature T h Heatsink temperaturet fiCurrent fall time with inductive load T j , T (vj)Junction temperatureT jm , T (vj)m Maximum junction temperature t rrReverse recovery time of a diode V CE(sat)Collector-emitter saturation voltage V CES Maximum collector-emitter voltage V DRM Maximum repetitive forward blocking voltage of thyristorV DSS Drain-source break-down voltage V F Forward voltage of diode V R Reverse voltageV RRM Maximum peak reverse voltage of thyristor or diodeV T On-state voltage of thyristorV T0Threshold voltage of thyristors or diodes (for power loss calculation only)Chip and DCB Ceramic Substrates Data book Edition 2004Published by IXYS Semiconductor GmbH Marketing CommunicationsEdisonstraße 15, D-68623 Lampertheim© IXYS Semiconductor GmbH All Rights reserved As far as patents or other rights of third parties are concerned, liability is only assumed for chips and DCB parts per se, not for applications, processes and circuits implemented with components or assemblies. Terms of delivery and the right to change design or specifications are reserved.NomenclatureIGBT and MOSFET DiscreteIXSD 40N60A (Example)IX IXYSDie technology E NPT 3 IGBTF HiPerFETTM Power MOSFETG Fast IGBTS IGBT with SCSOA capability T Standard Power MOSFET D Unassembled chip (die)40Current rating, 40 = 40 A N N-channel type PP-channel type60Voltage class, 60 = 600 Vxx MOSFETA Prime RDS(on) for standard MOSFET Q Low gate charge dieQ2Low gate charge die, 2nd generation P PolarHTTM Power MOSFET L Linear Mode MOSFET IGBT--No letter, low VCE(sat)A Or A2, std speed type B Or B2, high speed typeCOr C2, very high speed type W-CWP 55-12/18(Thyristor Example)WPackage typeC Chip functionC = Silicon phase control thyristor W Unassembled chip PProcess designatorP = Planar passivated chip cathode on top55Current rating value of one chip in A 12/18Voltage class, 12/18 = 1200 up to 1800 VDiode and Thyristor ChipsC-DWEP 69-12(Diode Example)C Package typeD Chip functionD = Silicon rectifier diode W Unassembled chipEPProcess designatorEP = Epitaxial rectifier diodeN = Rectifier diode, cathode on top P = Rectifier diode, anode on topFN = Fast Rectifier diode, cathode on top FP = Fast Rectifier diode, anode on top69Current rating value of one chip in A -12Voltage class, 12 = 1200 V 001947 TS2/765/17557Registration No.:0019473IXYS reserves the right to change limits, test conditions and dimensions General Informations for ChipsWhen mounting Power Semiconductor chips to a header, ceramic substrate or hybrid thick film circuit, the solder system and the chip attach process are very important to the reliability and performance of the final product. This brochure provides several guidelines that describe recommended chip attachment pro-cedures. These methods have been used successfully for many years at IXYS.Available forms of chip packingsIXYS offers various options.Please order from one of the following possibilities:Packaging Options Delivery formC-...*Chips in tray (Waffle Pack);Electrically testedT-...*Chips in wafer, unsawed;Bipolar = 5" (125 mm ∅) wafer;Electrically tested, rejects are inked W-...*Chips in wafer on foil, sawed;Bipolar = 5" (125 mm ∅) wafer;Electrically tested, rejects are inked...* must be amended by the exact chip type designation.Packing, Storage and HandlingChips should be transported in their original containers. All chip transfer to other containers or for assembly should be done only with rubber-tipped vacuum pencils. Contact with human skin (or with a tool that has been touched by hand) leaves an oily residue that may adversely impact subsequent chip attach or reliability.At temperatures below 104°F (40°C), there is no limitation on storage time for chips in sealed original packages. Chips removed from original packages should be assembled immediately. The wetting ability of the contact metallization with solder can be preserved by storage in a clean and dry nitrogen atmosphere.The IGBT and MOSFET Chips are electrostatic discharge (ESD) sensitive. Normal ESD precautions for handling must be observed.Prior to chip attach, all testing and handling of the chips must be done at ESD safe work stations according to DIN IEC 47(CO) 701.Ionized air blowers are recommended for added ESD protection.Contamination of the chips degrades the assembly results.Finger prints, dust or oily deposits on the surface of the chips have to be absolutely avoided.Rough mechanical treatment can cause damage to the chip.Electrical TestsThe electrical properties listed in the data sheet presume correctly assembled chips. Testing ofnon-assembled chips requires the following precautions:-High currents have to be supplied homogeneously to the whole metallized contact area.-Kelvin probes must be used to test voltages at high currents-Applying the full specified blocking or reverse voltage may cause arcing across the glass passivated junction termination, because the electrical field on top of the passivation glass causes ionization of the surrounding air. This phenomenon can be avoided by usinginert fluids or by increasing the pressure of the gas surrounding the chip to values above 30 psig (2 bars).General Rules for AssemblyThe linear thermal expansion coefficient of silicon is very small compared to usual contact metals. If a large area metallized silicon chip is directly soldered to a metal like copper, enormous shear stress is caused by temperature changes (e.g. when cooling down from the solder temperature or by heating during working conditions) which can disrupt the solder mountdown.If it is found that larger chips are cracking during mountdown or in the application, then the use of a low thermal expansion coefficient buffer layer, e.g. tungsten, molybdenum or Trimetal ®, for strain relief should be considered. An alternative solution is to soft-solder these larger chips to DCB ceramic substrates because of their matching thermal expansion coefficients.4© 2004 IXYS All rights reservedMOS/IGBT ChipsRecommended Solder SystemIXYS recommends a soft solder chip attach using a solder composition of 92.5 % Pb, 5 % Sn and 2.5 % Ag. The maximum chip attach temperature is 460°C for MOSFET and 360°C for HiPerFET TM and IGBT.Wire BondingIt is recommended to use wire of diameter not greater than 0.38 mm (0.015") for bonding to the source emitter and gate pads. Multiple wires should be used in place of thicker wire to handle high drain or emitter currents. See tables for number of recommended wire bonds. At smaller gate pads 0.15 mm is recommended.Thermal Response TestingTo assure good chip attach processing, thermal response testing per MIL STD 750, Method 3161 or equivalent should be performed.Bipolar ChipsAssemblingIXYS bipolar semiconductor chips have a soft-solderable, multi-layer metallization (Ti/Ni/Ag) on the bottom side and, on top, either the same metallization scheme or an alumunium layer sufficiently thick for ultrasonic bonding. Note that the last layer of metal for soldering is pure silver.Regardless of their type all chips possess the same glass passivated junction termination system on top of the chip. For that reason they can be easily chip bonded or they can all be simply soldered to a flat contacting electrode in accordance to the General Rules on Page 3. All kinds of the usual soft solders with melting points below 660°F (350°C) can be used thanks to their pure silver top metal.Solders with high melting points are preferable due to their better power cycling capability, i.e. they are more resistant to thermal fatigue.Soldering temperature should not exceed 750°F (400°C). The maximum temperature should not be applied for more than five minutes.As already mentioned above the electrical properties quoted in the data sheets can only be obtained with properly assembled chips.This is only possible when all contact materials to be soldered together are well wetted and the solder is practically free of voids.A simple means to achieve good solder connections is to use a belt furnace running with a process gas containing at least 10 %Hydrogen in Nitrogen.Other approved methods are also allowed, provided that the above mentioned temperature-time-limits are not exceeded and temperature shocks above 930°F/min (500 K/min) are avoided.We do not recommend the use of fluxes for soldering!Ultrasonic Wire BondingChips provided with a thick aluminium layer are designed for ultrasonic wire bonding. Wire diameters up to 500 µm can be used dependent on chip types. Setting wires in parallel and application of stitch bonding lead to surge current ratings comparable to soldered chips.CoatingAlthough the chips are glass passivated, they must be protected against arcing and environmental influences. The coating material that is in contact with the chip surface must have the following properties:- elasticity (to prevent mechanical stress)- high purity, no contamination with alkali metals - good adhesion to metals and glass passivation.Assembly Instructions5IXYS reserves the right to change limits, test conditions and dimensionsFRED, Rectifier Diode and Thyristor Chips in Planar DesignFast Recovery Epitaxial Diodes (FRED)Power switches (IGBT, MOSFET, BJT, GTO) for applications in electronics are only as good as their associated free-wheeling diodes. At increasing switching frequencies, the proper functioning and efficiency of the power switch, aside from conduction losses,is determined by the turn-off behavior of the diode (characterized by Q rr , I RM and t rr - Fig. 1.Rectifier Diode and Thyristor ChipsThe figures 3 a-c show cross sectional views of the diode and thyristor chips in the passivation area. All thyristor and diode chips (DWN, DWFN,CWP) are fabricated using separation diffusion processes so that all junctions terminate on the topside of the chip. Now the entire bottom surfaces of all chips are available for soldering onto a DCB or other ceramic substrate without a molybdenum strain buffer. The elimination of the strain buffer and its solder joint reduces thermal resistance and increases blocking voltage stability. The junction termination areas are passivated with glass, whose thermal expansion coefficient matches that of silicon. All silicon chips increasingly use planar technology with guard rings and channel stoppers to reduce electric fields on the chip surface.The contact areas of the chips have vapor deposited metal layers which contribute substantially to their high power cycle capability. All chips are processed on silicon wafers of 5" diameter and diced after a wafer sample test which auto-matically marks chips not meeting the electrical specification.The chip geometry is square or rectangular.Fig. 3a-cCross sections of Chips in the passivation area a) Diode chip, type DWN, DWFN b) Diode chip, type DWP, DWFP c) Thyristor chip, type CWPThe reverse current character-istic following the peak reverse current I RM is another very im-portant property. The slope of the decaying reverse current di rr /dt results from design para- meters (technology and dif-fusion of the FRED chip Fig. 2. In a circuit this current slope, in conjunction with parasitic induc-tances (e.g. connecting leads, causes over-voltage spikes and high frequency interference vol-tages.The higher the di rr /dt ("hard recovery" or "snap-off" behavior) the higher is the resulting additional stress for both the diode and the paralleled switch. A slow decay of the reverse current ("soft recovery" behavior), is the most desirable characteristic, and this is designed into all FRED. The wide range of available blocking voltages makes it possible to apply these FRED as output rectifiers in switch-mode power supplies (SMPS) as well as protective and free-wheeling diodes for power switches in inverters and welding power supplies.MetalizationFig. 1:Current and voltage during turn-on andturn-offswitching of fast diodesFig. 2:Cross section of glassivated planar epitaxial diode chip with seperation diffusion (type DWEP)Epitaxie Sch ich t n -Sub stra t n+KathodeAnodeGuard ringSubstrate n+Epitaxy layer n-CathodeAnode Glasspassivation p n n +GlasspassivationGuard ring Metalization Fig. 3b)MetalizationChannel-stopperGlasspassivationGuard ring EmitterFig. 3c)Fig. 3a)18© 2004 IXYS All rights reservedRectifier DiodesTypeV RRMVDWN 5800 -DWP 51200DWN 21200 -DWN 91800DWN 17 DWP 17DWN 21DWP 21DWN 35DWP 35DWN 50DWP 50DWN 75DWP 75DWN 110DWP 110DWN 340DWN 1081600 -1Mounted on DCB19© 2004 IXYS All rights reservedDWNDWPRectifier DiodesTypeDWN 5DWP 5DWN 2•DWN 9•DWN 17 •DWP 17•DWN 21•DWP 21•DWN 35•DWP 35•DWN 50•DWP 50DWN 75•DWP 75•DWN 110•DWP 110•DWN 340•DWN 108•s o l d e r a b l e20© 2004 IXYS All rights reserved FRED - F ast R ecovery E pitaxial DiodesTypeV RRMVDWEP 27-02200DWEP 37-02DWEP 77-02DWEP 8-06600DWEP 12-06DWEP 15-06DWEP 23-06DWEP 25-06DWEP 35-06DWEP 55-06DWEP 75-06DWEP 3-101000DWEP 10-10DWEP 18-10DWEP 20-10DWEP 30-10DWEP 50-101 Mounted on DCB21© 2004 IXYS All rights reserved FRED - F ast R ecovery E pitaxial DiodesTypeDWEP 27-02•DWEP 37-02•DWEP 77-02••DWEP 8-06•DWEP 12-06••DWEP 15-06••DWEP 23-06••DWEP 25-06••DWEP 35-06••DWEP 55-06•DWEP 75-06••DWEP 3-10•DWEP 10-10•DWEP 18-10•DWEP 20-10•DWEP 30-10••DWEP 50-10•s o l d e r a b l eb o n d a b l e22© 2004 IXYS All rights reservedLow Leakage Fast Recovery Epitaxial DiodesTypeV RRM VDWLP 4-02200DWLP 15-02DWLP 15-02B DWLP 25-02DWLP 4-03300DWLP 8-03DWLP 15-03DWLP 15-03A DWLP 23-03DWLP 23-03A DWLP 55-03DWLP 75-03DWLP 8-04400DWLP 15-04DWLP 23-04DWLP 55-04DWLP 75-04DWLP 150-04DWLP 4-066001Mounted on DCB23© 2004 IXYS All rights reservedLow Leakage Fast Recovery Epitaxial DiodesTypeDWLP 4-02•DWLP 15-02•DWLP 15-02B •DWLP 25-02•DWLP 4-03•DWLP 8-03•DWLP 15-03•DWLP 15-03A •DWLP 23-03•DWLP 23-03A •DWLP 55-03••DWLP 75-03•DWLP 8-04•DWLP 15-04•DWLP 23-04•DWLP 55-04••DWLP 75-04••DWLP 150-04••DWLP 4-06•s o l d e r a b l eb o n d a b l e24© 2004 IXYS All rights reserved SONIC-FRD TMDiodesTypeV DWHP 8-06 F in design DWHP 15-06 F 600DWHP 23-06 FDWHP 56-06 F DWHP 69-06 F DWHP 150-06 F in design DWHFP 15-12 F 1200DWHFP 23-12 F DWHFP 56-12 F DWHFP 56-12 S DWHFP 69-12 F DWHFP 69-12 S DWHFP 150-12 S DLFP 55-17 S 1700DLFP 68-17 S DLFP 150-17 S DLFP 200-17 S 1Mounted on DCB25© 2004 IXYS All rights reserved SONIC-FRD TMDiodesTypeDWHP 8-06 F DWHP 15-06 F DWHP 23-06 F DWHP 56-06 F DWHP 69-06 F DWHP 150-06 F DWHFP 15-12 F DWHFP 23-12 FDWHFP 56-12 F DWHFP 56-12 SDWHFP 69-12 F DWHFP 69-12 S DWHFP 150-12 S DLFP 55-17 S DLFP 68-17 S DLFP 150-17 S DLFP 200-17 S s o l d e r a b l e26© 2004 IXYS All rights reservedGaAs Schottky DiodesTypeV RRMVDWGS04-01A 100DWGS10-01C DWGS04-018A 180DWGS04-018CDWGS10-018ADWGS10-018C DWGS20-018A DWGS20-018C DWGS04-025A 250DWGS04-025C DWGS10-025A DWGS10-025C DWGS20-025A DWGS20-025C DWGS04-03A 300DWGS04-03C DWGS10-03A27© 2004 IXYS All rights reservedGaAs Schottky DiodesD W GS04-01A D W GS10-01CD W GS04-018A D W GS04-018C D W GS10-018A D W GS10-018C D W GS20-018A D W GS20-018C D W GS04-025A D W GS04-025C D W GS10-025A D W GS10-025C D W GS20-025A D W GS20-025C D W GS04-03A D W GS04-03C D W GS10-03A s o l d e r a b l e28© 2004 IXYS All rights reservedSchottky DiodesTypeV RRMVDWS 39-08D DWS 9-15B 15DWS 19-15B DWS 29-15B DWS 7-30B 30DWS 17-30B DWS 27-30B DWS 37-30B DWS 217-30B DWS 3-45B 45DWS 4-45A DWS 13-45B DWS 14-45A DWS 23-45B DWS 24-45A DWS 33-45B 1Mounted on DCB29© 2004 IXYS All rights reservedSchottky DiodesTypeDWS 39-08D •DWS 9-15B •DWS 19-15B •DWS 29-15B •DWS 7-30B •DWS 17-30B •DWS 27-30B•DWS 37-30B •DWS 217-30B •DWS 3-45B •DWS 4-45A •DWS 13-45B •DWS 14-45A •DWS 23-45B ••DWS 24-45A •DWS 33-45B ••s o l d e r a b l eb o n d a b l e30© 2004 IXYS All rights reservedSchottky DiodesTypeV RRMVDWS 5-60A 60DWS 15-60BDWS 25-60BDWS 35-60B DWS 25-80B 80DWS 36-80A DWS 2-100A 100DWS 12-100A DWS 22-100A DWS 32-100A DWS 1-150A 150DWS 11-150A DWS 21-150A DWS 31-150A DWS 1-180A 1801 Mounted on DCB31© 2004 IXYS All rights reservedSchottky DiodesTypeDWS 5-60A •DWS 15-60B •DWS 25-60B •DWS 35-60B •DWS 25-80B •DWS 36-80A •DWS 2-100A •DWS 12-100A •DWS 22-100A •DWS 32-100A ••DWS 1-150A •DWS 11-150A •DWS 21-150A •DWS 31-150A •DWS 1-180A •s o l d e r a b l eb o n d a b l e32© 2004 IXYS All rights reservedPhase Control ThyristorsTypeV DRM V RRMVCWP 7-CG 800 -CWP 81200CWP 8-CG CWP 35CWP 16-CG 1200 -CWP 21-CG 1600 -CWP 22-CG CWP 24CWP 25-CG CWP 411200 -CWP 501800CWP 55CWP 71CWP 130CWP 180CWP 341CWP 3471Mounted on DCB33© 2004 IXYS All rights reservedPhase Control Thyristors...-CG typesTypeCWP 7-CG ••CWP 8••CWP 8-CG•CWP 35••CWP 16-CG ••CWP 21-CG ••CWP 22-CG ••CWP 24••CWP 25-CG ••CWP 41••CWP 50••CWP 55••CWP 71••CWP 130••CWP 180••CWP 341•CWP 347•s o l d e r a b l eb o n d a b l e34© 2004 IXYS All rights reservedDWFN DWFPFast Rectifier DiodesTypeV RRMVDWFN 2-16/181600 -DWFN 9-16/181800DWFN 17-16/18DWFP 17-16/18DWFN 21-16/18DWFN 35-16/181 Mounted on DCBTypeo l d e r a b l e。

SC813资料

POWER MANAGEMENT Adapter/USB Tri-Mode Single-cell Li-ion ChargerFeaturesSingle input charger with three charging modes Constant voltage — 4.2V, 1% regulationFast-charge current regulation — 15% at 70mA, 9% at 700mACharging by current regulation, voltage regulation, and thermal limitingInput voltage protection — 30VCurrent-limited adapter support capability — reduces power dissipation in charger ICUSB high and low power modes limit charge current to prevent USB Vbus overloadInstantaneous CC-to-CV transition for faster charging Programmable battery-dependent currents (adapter mode fast- and pre-charge, termination)Programmable source-limited currents (USB-high mode fast-charge, and USB-low mode fast- and pre-charge)Independent programming of termination current with dual-mode operation Three termination options — fl oat-charge, automatic re-charge, or forced re-charge to keep the battery topped-off after termination without fl oat-charging Soft-start reduces adapter or USB load transients High operating voltage range of SC811 permits use of unregulated adaptersComplies with CCSA YD/T 1591-2006Space saving 2x2x0.6 (mm) MLPD package WEEE and RoHS compliantApplicationsMobile phones MP3 playersGPS handheld receiversDescriptionThe SC811 and SC813 are highly versatile single input triple mode (adapter/USB high current, USB low current) linear single-cell Li-ion battery chargers, each in an 8 lead 2x2 MLPD ultra-thin package. The input will survive sus-tained input voltage up to 30V to protect against hot plug overshoot and faulty charging adapters. The SC811 has 9.6V rising, 8.2V falling OVP thresholds for general purpose charging with low cost adaptors. The SC813 has 6V rising, 5.6V falling OVP thresholds for customers utilizing charg-ing adapters with specifi cations that are similar to a USB Vbus supply. The SC811 and SC813 differ only in OVP threshold.Charging begins automatically when an input source is applied to the charging input. Thermal limiting protects against excessive power dissipation. The charger can be programmed to turn off when charging is complete or to continue operating as an LDO regulator while fl oat-charg-ing the battery.Three charging modes are provided: adapter mode, USB low power mode, and USB high power mode. Battery-capacity-dependent and charging source-dependent current programming are independently programmed. Adapter and USB high power modes can charge up to 1A, with the charging adapter operating either in voltage regulation or in current limit to obtain the lowest possible power dissipation. A single current programming pin is used to program pre-charge, termination, and adapter-mode fast-charge currents in fixed proportions. In the USB modes, a second programming pin is used to program low power pre-charge current and low and high power fast-charge currents. This confi guration allows indepen-dent programming of termination current. The two USB modes dynamically limit the charging load if necessary to prevent overloading the USB Vbus supply.V ADAPTERSC811 / SC813Typical Application CircuitPin Confi gurationMarking InformationOrdering InformationDevicePackageSC811ULTRT (1)(2)MLPD-UT-8 2×2SC813ULTRT (1)(2)MLPD-UT-8 2×2SC811EVB Evaluation Board SC813EVBEvaluation BoardNotes:(1) Available in tape and reel only. A reel contains 3,000 devices.(2) Lead-free package only. Device is WEEE and RoHS compliant.Exceeding the above specifi cations may result in permanent damage to the device or device malfunction. Operation outside of the parameters specifi ed in the Electrical Characteristics section is not recommended.NOTES:(1) Tested according to JEDEC standard JESD22-A114-B.(2) This is the input voltage at which the charger is guaranteed to begin operation. Maximum operating voltage is the maximum Vsupply asdefined in EIA/JEDEC Standard No. 78, paragraph 2.11.(3) Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.Absolute Maximum RatingsVIN (V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3 to +30.0BAT, IPRGM, IPUSB (V) . . . . . . . . . . . . . . . . . . . . . . . . .-0.3 to +6.5STATB, ENB, MODE (V) . . . . . . . . . . . . . . . . . . .-0.3 to V BAT + 0.3VIN Input Current (A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.5Total Power Dissipation (W) . . . . . . . . . . . . . . . . . . . . . . . . . . . 2BAT, IPRGM, IPUSB Short to GND Duration . . . . Continuous ESD Protection Level (1) (kV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Recommended Operating ConditionsOperating Ambient Temperature (°C) . . . . . . . . . -40 to +85SC811:VIN Adapter Mode Operating Voltage (2) (V) . . . 4.60 to 8.20VIN USB Modes Operating Voltage (2) (V) . . . . . . 4.35 to 8.20SC813:VIN Adapter Mode Operating Voltage (2) (V) . . . 4.60 to 5.60VIN USB Modes Operating Voltage (2) (V) . . . . . . 4.35 to 5.60Thermal InformationThermal Resistance, Junction to Ambient (3) (°C/W) . . . . . 68Junction Temperature Range (°C) . . . . . . . . . . . . . . . . . . +150Storage Temperature Range (°C) . . . . . . . . . . . . -65 to +150Peak IR Reflow Temperature (°C) . . . . . . . . . . . . . . . . . . . +260Test Conditions: V VIN = 4.75V to 5.25V; V BAT = 3.7V; Typ values at 25°C; Min and Max at -40°C < T A < 85°C, unless specifi ed.ParameterSymbolConditions MinTypMaxUnitsVIN Adapter Mode Rising Threshold VT ADUVLO-R 4.304.45 4.60V VIN Adapter Mode Falling Threshold (1)VT ADUVLO-F V VIN > V BAT 2.702.853.00V VIN USB Modes Rising Threshold VT USBUVLO-R V VIN > V BAT4.204.35V VIN USB Modes Falling Threshold VT USBUVLO-F V VIN > V BAT3.654.00V VIN USB Modes HysteresisVT USBUVLO-H VT USBUVLOR - VT USBUVLOF 100mVVIN OVP Rising ThresholdVT OVP-RAll modes, SC8119.09.6VAll modes, SC813 5.856.0VIN OVP Falling ThresholdVT OVP-FAll modes, SC8118.28.8VAll modes, SC8135.6 5.75VIN OVP HysteresisVT OVP-HVT OVP-R - VT OVP-F , all modes, SC81150200mVVT OVP-R - VT OVP-F , all modes, SC81350100Electrical CharacteristicsParameterSymbolConditionsMin TypMaxUnitsVIN Charging Disabled Quiescent CurrentIq VIN_DIS V ENB = V BAT23mA VIN Charging Enabled Quiescent CurrentIq VIN_EN V ENB = 0V,excluding I BAT , I IPRGM , and I IPUSB 23mA CV Regulation Voltage V CV I BAT = 50mA, -40°C ≤ T J ≤ 125°C4.16 4.204.24V CV Voltage Load Regulation V CV_LOAD Relative to V CV @ 50mA, 1mA ≤ I BAT ≤ 1A, -40°C ≤ T J ≤ 125°C-2010mV Re-charge Threshold VT ReQ V CV - V BAT60100140mV Pre-charge Threshold (rising)VT PreQ 2.852.90 2.95V Battery Leakage Currentl BAT_V0V BAT = V CV , V VIN = 0V 0.11μA l BAT_DIS V BAT = V CV , V VIN = 5V, V ENB = 2V0.11μA l BAT_MONV BAT = V CV , V VIN = 5V; ENB not connected0.11μA IPRGM Programming Resistor R IPRGM 2.0529.4kΩFast-Charge Current, Adapter Mode I FQ_AD R IPRGM = 2.94kΩ, VT PreQ < V BAT < V CV 643694745mA Pre-Charge Current, Adapter Mode and USB High Power Mode I PreQ_AD R IPRGM = 2.94kΩ, 1.8V < V BAT < VT PreQ105139173mA Termination Current, Any Mode I TERM R IPRGM = 2.94kΩ, V BAT = V CV596980mA IPUSB Programming Resistor R IPUSB 2.0529.4kΩFast-Charge Current, USB High Power ModeI FQ_USB R IPUSB = 4.42kΩ, 1.8V < V BAT < VT PreQ 427462497mA Pre-Charge Current and Fast-Charge Current, USB Low Power Mode I PreQ_USB R IPUSB = 4.42kΩ, 1.8V < V BAT < V CV 6992116mA Dropout VoltageV DO I BAT = 700mA, 0°C ≤ T J ≤ 125°C 0.400.60V IPRGM Fast-charge Regulated Voltage V IPRGM_FQ V VIN = 5.0V, VT PreQ < V BAT < V CV2.04V IPRGM Pre-charge Regulated Voltage V IPRGM_PQ 1.8V < V BAT < VT PreQ 0.408V IPRGM Termination Threshold Voltage VT IPRGM_TERM V BAT = V CV(either input selected)0.204V IPUSB Fast-charge Regulated Voltage V IPUSB_FQ V VIN = 0V, VT PreQ < V BAT < V CV2.04V IPUSB Pre-charge or USB Low Power Mode Regulated VoltageV IPUSB_PQ V VIN = 0V, V BAT < VT PreQ0.408VVIN USB Modes Under-Voltage Load Regulation Limiting VoltageV UVLR5mA ≤ VIN supply current limit ≤500mA, V MODE = 2V, R IPUSB = 3.65kΩ (559mA)4.45 4.58 4.70VElectrical Characteristics (continued)Electrical Characteristics (continued)ParameterSymbolConditions Min TypMax UnitsThermal Limiting Threshold Temperature T TL 130°C Thermal Limiting Ratei T 50mA/ °C ENB or MODE Input High Voltage ThresholdV IH 1.6VENB or MODE Input Mid Voltage Range V IM 0.71.3V ENB or MODE Input Low Voltage ThresholdV IL 0.3V ENB Input High-range Threshold Input CurrentI ENB_IH_TH ENB current required to pull ENB from floating midrange into high range 2350μAENB Input High-range Sustain Input CurrentI ENB_IH_SUS Current required to hold ENB in high range, Min V IH ≤ V ENB ≤ V BAT ,Min V IH ≤ V BAT ≤ 4.2V0.31μA MODE Input High-range Input Current I MODE_IH V MODE = Min V IH2375μA ENB or MODE Input Mid-range Load LimitI IM Input will float to mid range when thisload limit is observed.-55μA ENB or MODE Input Low-range Input CurrentI IL 0V ≤ (V ENB or V MODE ) ≤ Max V IL -2512μA MODE Input Monitor State Input CurrentI MODE_MON V MODE = V BAT = 4.2V,V ENB = 1V and Charging Terminated1μA ENB or MODE Input Leakage I ILEAK V VIN = 0V or V VIN = 5V, V ENB and V MODE = V BAT = 4.2V1μA STATB Output Low Voltage V STAT_LO I STAT_SINK = 2mA 0.5V STATB Output High CurrentI STAT_HIV STAT = 5V1μANotes:(1) Sustained operation to VT ADUVLO-F ≤ V VIN is guaranteed only if a current limited charging source applied to VIN is pulled below VT ADUVLO-R by thecharging load; forced VIN voltage below VT ADUVLO-R may in some cases result in regulation errors or other unexpected behavior.Typical CharacteristicsCV Line RegulationCV Load RegulationCV Temperature RegulationCC AD or USB High FQ Line RegulationCC AD or USB High FQ V BAT RegulationCC AD or USB High FQ Temperature RegulationTypical CharacteristicsCC USB Low Power FQ Line RegulationCC USB Low Power FQ VRegulationCC USB Low Power FQ Temperature RegulationCC PQ Line RegulationCC PQ Temperature RegulationTypical CharacteristicsI FQ_AD vs. R IPRGM , or I FQ_USB High Power vs. R IPUSBIor I vs. R , or I Low Power vs. R Charging Cycle Battery Voltage and CurrentPre-Charging Battery Voltage and CurrentCC-to-CV Battery Voltage and CurrentRe-Charge Cycle Battery Voltage and CurrentTypical CharacteristicsMode Reselection — USB Low to USB HighMode Reselection — USB High to USB LowMode Reselection — AD to USB HighMode Reselection — USB High to ADMode Reselection — AD to USB LowMode Reselection — USB Low to AD100μs/divI BAT (100mA/div))V MODE =0V—V MODE (2V/div)I BAT =0mA—V VIN =5V, V BAT=3.7V100μs/div I BAT (100mA/div)V MODE =0V—V MODE (2V/div)I BAT =0mA—V VIN =5V, V BAT=3.7V100μs/divI BAT (100mA/div)V MODE (2V/div)V VIN =5V, V BAT=3.7V100μs/divI BAT (100mA/div)V MODE (2V/div)V VIN =5V, V BAT=3.7V100μs/divI BAT (100mA/div)V MODE =0V—V MODE (2V/div)I BAT =0mA—V VIN =5V, V BAT=3.7V100μs/divI BAT (100mA/div)V MODE =0V—V MODE (2V/div)I BAT =0mA—V VIN =5V, V BAT =3.7VV MODE =0V—I BAT =0mA—V MODE =0V—I BAT =0mA—Pin DescriptionsPin #Pin Name Pin Function1VIN Supply pin — connect to charging adapter (wall adapter or USB). This pin is protected against damage due to high voltage up to 30V.2MODE Charging mode selection (tri-level logical) input — Logical high selects USB high power mode, fl oating selects USB low power mode, ground selects adapter mode.3STATB Status output pin — This open-drain pin is asserted (pulled low) when a valid charging supply is connected to the VIN pin, and a charging cycle begins. It is released when the termination current is reached, indicating that charging is complete. STATB is not asserted for re-charge cycles.4GND Ground5IPUSB Fast-charge and pre-charge current programming pin for a USB mode charging source — USB high power mode (100%) and low power mode (20%) fast-charge current are programmed by connecting a resistor from this pin to ground. USB low power mode pre-charge current is equal to the low power mode fast-charge current (20% of USB high power mode fast-charge current).6 IPRGM Adapter mode fast-charge, adapter and USB high power modes pre-charge, and all modes termination current programming pin — Connect a resistor from this pin to ground. Pre-charge current is 20% of IPRGM-programmed adapter mode fast-charge current when in adapter mode or USB high power mode. The charging termination current threshold (for adapter or either USB mode selection) is 10% of the IPRGM programmed fast-charge current.7BAT Charger output — connect to battery positive terminal.8ENB Combined device enable/disable — Logic high disables the device. Tie to GND to enable charging with indefi nite fl oat-charging. Float this pin to enable charging without fl oat-charge upon termination. Note that this pin must be grounded if the SC811/3 is to be operated without a battery connected to BAT.T Thermal Pad Pad is for heatsinking purposes —not connected internally. Connect exposed pad to ground plane using multiple vias.Block DiagramCharger OperationThe SC811/3 is a single input tri-mode stand-alone Li-ion battery charger. (The SC811 diff ers from the SC813 only in the input voltage Over Voltage Protection threshold.) It provides selections of adapter mode and USB high and low power mode charging. The device is independently programmed for battery capacity dependent currents (adapter fast-charge current and termination current) using the IPRGM pin. Charging currents from the USB Vbus supply, which has a maximum load specifi cation, are programmed using the IPUSB pin when either of the USB modes is selected.When an input supply is fi rst detected, a charge cycle is initiated and the STATB open-drain output goes low. If the battery voltage is less than the pre-charge threshold voltage, the pre-charge current is supplied. Pre-charge current is 20% of the IPRGM (adapter or USB high power modes) or IPUSB (USB low power mode) programmed fast-charge current.When the battery voltage exceeds the pre-charge thresh-old, typically within seconds for a standard battery with a starting cell voltage greater than 2V, the fast-charge Constant Current (CC) mode begins. The charge current soft-starts in three steps (20%, 60%, and 100% of pro-grammed fast-charge current) to reduce adapter load transients. CC current is programmed by the IPRGM resis-tance to ground when adapter mode is selected and by the IPUSB resistance to ground when either USB mode is selected. In USB low power mode, the CC current is held at 20% of the IPUSB programmed fast-charge current.The charger begins Constant Voltage (CV) regulation when the battery voltage rises to the fully-charged single-cell Li-ion regulation voltage (V CV ), nominally 4.2V. In CV regulation, the output voltage is regulated, and as the battery charges, the charge current gradually decreases. The STATB output goes high when I BAT drops below the termination threshold current, which is 10% of the IPRGM pin programmed fast-charge current regardless of the mode selected. This is known as charge termination.Optional Float-charging or MonitoringDepending on the state of the ENB input, upon termina-tion the SC811/3 either operates indefi nitely as a voltage regulator (known as float-charging) or it turns off itsoutput. If the output is turned off upon termination, the device enters the monitor state. In this state, the output remains off until the BAT pin voltage decreases by the re-charge threshold (VT ReQ ). A re-charge cycle then begins automatically and the process repeats. A forced re-charge cycle can also be periodically commanded by the processor to keep the battery topped-off without fl oat-charging. See the Monitor State section for details. Re-charge cycles are not indicated by the STATB pin.Charging Input Pin Mode DependenciesThe UVLO rising and falling thresholds are adjusted with the charging mode selected. In adapter mode, if the charging current loads the adapter beyond its current limit, the input voltage will be pulled down to just above the battery voltage. The adapter mode UVLO falling threshold is set close to the battery voltage pre-charge threshold to permit low-dissipation charging from a current limited adapter.The USB modes provide a higher UVLO falling threshold applicable to the USB specifi cation. The USB modes also provide Under-Voltage Load Regulation (UVLR), in which the charging current is reduced if needed to prevent overloading of the USB Vbus supply. UVLR can serve as a low-cost alternative to directly programming the USB low power charge current. This can be beneficial for charging small batteries, for which the USB high power fast-charge current must be programmed to less than 500mA. The fi xed 20% USB low power mode fast-charge current would be less than 100mA and, therefore, is unsuitable for minimum charge-time applications. UVLR can also be used where there is no signal available to indicate whether USB low or high power mode should be selected.All modes use the same input Over-Voltage Protection (OVP) threshold as defi ned in the Electrical Characteristics section for the device being used.Constant Current Mode Fast-charge Current ProgrammingConstant Current (CC) regulation is active when the battery voltage is above VT PreQ and less than V CV . When adapter mode is selected, the programmed CC regula-tion fast-charge (FQ) current is inversely proportional toApplications InformationApplications Information (continued)the resistance between IPRGM and GND according to the equation59,,35*07\SB ,35*0$'B )4When either of the USB modes is selected, the pro-grammed CC regulation fast-charge current is inversely proportional to the resistance between IPUSB and GND according to the equation59,,386%7\S B ,386%86%B )4The fast-charge current can be programmed for a minimum of 70mA and a maximum of 995mA for either adapter or USB high power mode. This range for both modes permits the use of USB high power mode for general purpose adapter charging, allowing fully inde-pendent programming of termination current. (See the application sections, Independent Programming of Termination Current, and USB-only Charging of Very Large Batteries.)Current regulation accuracy is dominated by gain error at high current settings, and off set error at low current set-tings. The range of expected fast-charge output current versus programming resistance R IPRGM or R IPUSB (for adapter or USB high power mode, respectively) is shown in Figures1a and 1b. Each figure shows the nominal fast-charge current versus nominal R IPRGM or R IPUSB resistance as the center plot, and two theoretical limit plots indicating maximum and minimum current versus nominal pro-gramming resistance. These plots are derived from models of the expected worst-case contribution of error sources depending on programmed current. The current range includes the uncertainty due to 1% tolerance resis-tors. The dots on each plot indicate the currents obtained with standard value 1% tolerance resistors. Figures 1a and 1b show low and high resistance ranges, respectively. The USB low power mode fast-charge current accuracy is exactly like that of pre-charge in high power mode. USB low power mode current regulation accuracy is addressed in the next section.Pre-charge and USB Low Power Mode Fast-charge Current RegulationPre-charging is automatically selected when the battery voltage is below the pre-charge threshold voltage (VT PreQ ), typically 2.8V. Pre-charge current conditions the battery for fast charging. The pre-charge current value is fi xed at 20% nominally of the fast-charge current. It is pro-grammed by the resistance between IPRGM and GND for adapter mode and USB high power mode, and by the resistance between IPUSB and GND for USB low power mode. Note that USB low power mode pre-charge current is equal to USB low power mode fast-charge current.Figure 1a — Fast-charge Current Tolerance versus Programming Resistance, Low Resistance RangeFigure 1b — Fast-charge Current Tolerance versus Programming Resistance, High Resistance RangePre-charge current regulation accuracy is dominated by offset error. The range of expected pre-charge output current versus programming resistance R IPRGM or R IPUSB is shown in Figures 2a and 2b. Each figure shows the nominal pre-charge current versus nominal R IPRGM or R IPUSB resistance as the center plot and two theoretical limit plots indicating maximum and minimum current versus nominal programming resistance. These plots are derived from models of the expected worst-case contribution of error sources depending on programmed current. The current range includes the uncertainty due to 1% toler-ance resistors. The dots on each plot indicate the currents obtained with standard value 1% tolerance resistors. Figures 2a and 2b show low and high resistance ranges, respectively.TerminationWhen the battery voltage reaches V CV , the SC811/3 transi-tions from constant current regulation to constant voltageregulation. While V BAT is regulated to V CV , the current into the battery decreases as the battery becomes fully charged. When the output current drops below the termi-nation threshold current, charging terminates. Upon termination, the STATB pin open drain output turns off and the charger either enters monitor state or float-charges the battery, depending on the logical state of the ENB input pin.Applications Information (continued)The termination threshold current is fi xed at 10% of the adapter mode fast-charge current, as programmed by the resistance between IPRGM and GND, for all charging modes. If only the USB modes will be used, the termina-tion threshold current can be programmed independently of the fast-charge current. (See the application sections, Independent Programming of Termination Current, and USB-only Charging of Very Large Batteries.)Charger output current is the sum of the battery charge current and the system load current. Battery charge current changes gradually, and establishes a slowly diminishing lower bound on the output current while charging in CV mode. The load current into a typical digital system is highly transient in nature. Charge cycle termination is detected when the sum of the battery charging current and the greatest load current occurring within the immediate 300μs to 550μs past interval is less than the programmed termination current. This timing behavior permits charge cycle termination to occur during a brief low-load-current interval, and does not require that the longer interval average load current be small.Termination threshold current accuracy is dominated by off set error. The range of expected termination current versus programming resistance R IPRGM (for any charging mode) is shown in Figures 3a and 3b. Each fi gure showsFigure 2a — Pre-charge Current and USB Low Power Mode Fast-charge Current Tolerance vs. ProgrammingResistance, Low Resistance RangeFigure 2b — Pre-charge Current and USB Low Power Mode Fast-charge Current Tolerance vs. ProgrammingResistance, High Resistance Rangethe nominal termination current versus nominal R IPRGM resistance as the center plot and two theoretical limit plots indicating maximum and minimum current vs. nominal programming resistance. These plots are derived from models of the expected worst-case contribution of error sources depending on programmed current. The current range includes the uncertainty due to a 1% tolerance resistor. The dots on each plot indicate the currents obtained with standard value 1% tolerance resistors. Figures 3a and 3b show low and high resistance ranges, respectively.Tri-level Logical Input PinsThe MODE and ENB pins are tri-level logical inputs. They are designed to interface to a processor GPIO port that is powered from a peripheral supply voltage as low as 1.8V or as high as a fully charged battery. While a connected GPIO port is confi gured as an output, the processor writes 0 to select ENB or MODE low-range, and 1 to select high-range. The GPIO port is confi gured as an input to select mid-range.These pins can also be permanently grounded to select low-range or left unconnected to select mid-range for fi xed mode operation. The MODE pin can also be perma-nently connected to a logical high voltage source, such as BAT or a regulated peripheral supply voltage.The equivalent circuit looking into these pins is a variable resistance, minimum 15kΩ, to an approximately 1V source.The input will fl oat to mid range whenever the external driver sinks or sources less than 5μA, a common worst-case characteristic of a high impedance GPIO, or a weak pull-up or pull-down GPIO, confi gured as an input. The driving GPIO must be able to sink or source at least 75μA to ensure a low or high state, respectively, although the drive current is typically far less. (See the Electrical Characteristics table.)Mode InputThe MODE pin is a tri-level logical input. When driven high (V MODE > Min V IH ), the SC811/3 will operate in USB High Power mode. If the MODE input voltage is within its speci-fi ed mid range (Min V IM < V ENB < Max V IM ), either by fl oating (by reconfi guring its GPIO as an input) or by being exter-nally forced, the SC811/3 will operate in USB Low Power mode. When driven low (V MODE < Max V IL ), the SC811/3 will operate in adapter mode.When there is no charging source present, when the charger is disabled, or when operating in the monitor state (described in a later section), the MODE pin enters a high impedance state, suspending the tri-level functional-ity. Upon re-charge or re-enabling the charger, the MODE pin tri-level interface is reactivated.Typically a processor GPIO port direction defaults to input upon processor reset, or is high impedance when un-powered. This is the ideal initial condition for driving the MODE pin, since this will select USB Low Power mode,Programming Resistance, Low Resistance RangeProgramming Resistance, High Resistance RangeApplications Information (continued)which is the safest default mode with the lowest fast-charge current.Enable InputThe ENB pin is a tri-level logical input that allows selection of the following behaviors:charging enabled with fl oat-charging after ter-mination (ENB = low range)charging enabled with fl oat-charging disabled and battery monitoring at termination (ENB = mid range)charging disabled (ENB = high range).If the ENB input voltage is permitted to fl oat to mid-range, the charger is enabled but it will turn off its output follow-ing charge termination and will enter the monitor state. This state is explained in the next section. Mid-range can be selected either by floating the input (sourcing or sinking less than 5μA) or by being externally forced such that V ENB falls within the midrange limits specifi ed in the Electrical Characteristics table.When driven low (V ENB < Max V IL ), the charger is enabled and will continue to float-charge the battery following termination. If the charger is already in monitor state fol-lowing a previous termination, it will exit the monitor state and begin fl oat-charging.When ENB is driven high (V ENB > Min V IH ), the charger is disabled and the ENB input pin enters a high impedance state, suspending tri-level functionality. The specified high level input current I IH is required only until a high level is recognized by the SC811/3 internal logic. The tri-level float circuitry is then disabled and the ENB input becomes high impedance. Once forced high, the ENB pin will not fl oat to mid range. To restore tri-level operation, the ENB pin must fi rst be pulled down to mid or low range (at least to V ENB < Max V IM ), then, if desired, released (by reconfi guring the GPIO as an input) to select mid-range. If the ENB GPIO has a weak pull-down when confi gured as an input, then it is unnecessary to drive ENB low to restore tri-level operation; simply confi gure the GPIO as an input. When the ENB selection changes from high-range to mid- or low-range, a new charge cycle begins and STATB goes low.•••Note that if a GPIO with a weak pull-up input confi gura-tion is used, its pull-up current will fl ow from the GPIO into the ENB pin while it is fl oating to mid-range. Since the GPIO is driving a 1V equivalent voltage source through a resistance (looking into ENB), this current is small — pos-sibly less than 1μA. Nevertheless, this current is drawn from the GPIO peripheral power supply and, therefore, from the battery after termination. (See the next section, Monitor State.) For this reason, it is preferable that the GPIO chosen to operate the ENB pin should provide a true high impedance (CMOS) configuration or a weak pull-down when confi gured as an input. When pulled below the fl oat voltage, the ENB pin output current is sourced from VIN, not from the battery.Monitor StateIf the ENB pin is fl oating, the charger output and STATB pin will turn off and the device will enter the monitor state when a charge cycle is complete. If the battery voltage falls below the re-charge threshold (V CV - V ReQ ) while in the monitor state, the charger will automatically initiate a re-charge cycle. The battery leakage current during monitor state is no more than 1μA over temperature and typically less than 0.1μA at room temperature.While in the monitor state, the ENB tri-level input pin remains fully active, and although in midrange, is sensitive to both high and low levels. The SC811/3 can be forced from the monitor state (no fl oat-charging) directly to fl oat-charging operation by driving ENB low. This operation will turn on the charger output, but will not assert the STATB output. If the ENB pin is again allowed to float to mid-range, the charger will remain on only until the output current becomes less than the termination current, and charging terminates. The SC811/3 turns off its charging output and returns to the monitor state within a millisec-ond. This forced re-charge behavior is useful for periodically testing the battery state-of-charge and topping-off the battery, without float-charging and without requiring the battery to discharge to the auto-matic re-charge voltage. ENB should be held low for at least 1ms to ensure a successful forced re-charge.Forced re-charge can be requested at any time during the charge cycle, or even with no charging source present, with no detrimental effect on charger operation. This allows the host processor to schedule a forced re-charge。

PWPC板维修手册完整版

AOC PWPC板简介PWPC类产品:(A/D+D/D) power+Inverter powerA/D POWR:由于一般市用电网提供的是220V/50Hz或110V/60Hz的交流电压,而LCD显示器电路是工作在直流低压的条件下,所以需要在显示器上专门配有电源电路。

其作用就是将市电的交流电压转换成为12V的直流电压输出,从而向显示器主板供电。

即为:AdapterD/D POWER:由于显示器内部的主板上需要8V/5V/3.3V/2.5V或1.8V可选电压以满足主板不同的IC供电,鉴于此,在PWPC板上用DC-DC电压转换器以获得。

INVERTER POWER :因液晶屏本身没有发光功能,这就需要在液晶屏后加一个照明系统,现在发光部件的主流为被称作冷阴极管的萤光管。

其发光原理与室内照明用的热阴管类似,但不需象热阴管那样先预热灯丝,它在较低温状态就能点亮,因此叫冷阴极管。

但要驱动这种冷阴极管需要能输出1000~1500V交流电压的特殊电源。

这就要从12V直流电压转换得到,即为:Inverter。

早期,冠捷电子采用Adapter和Inverter分开的方式实现对显示器的供电。

Adapter采用的PWM IC为UC3842或UC3843、Inverter采用的PWM IC为TL1451。

后来,出于Cost down的考虑,采用Adapter和Inverter一体化的方案,即:PWPC板。

目前,Adapter部分采用的PWM IC为SG6841、Inverter部分采用的PWM IC为TL1451或BA9741。

此回路原理会在第二章中得到详细介绍。

PWPC板维修方式: PWPC板可以在不具备有PANEL及主板的情况下,被单独、方便地维修。

维修方法及维修案例将在第三章中得到详细介绍。

认识PWPC板PCB 板料号接主板连接PIN输入电源接口正面图与PANEL 灯管连接电源用开关变压器INVERTER 用升压变压器机种名PWPC 序列号背面图注:根据供给PANEL 的灯管及尺寸不一致,其机构及所用的料件相应改变。

泓格模拟量输入卡ISO813快速上手手册

1

2

3

4

5

6

SW1 : 基准地址

Base Adders 200-20F 210-21F 220-22F() 230-23F : 300-30F : 3F0-3FF

A9 1 OFF OFF OFF OFF : OFF : OFF A8 2 ON ON ON ON : OFF : OFF A7 3 ON ON ON ON : ON : OFF A6 4 ON ON ON ON : ON : OFF A5 5 ON ON OFF OFF : ON : OFF A4 6 ON OFF ON OFF : ON :

免责声明

凡使用本系列产品除产品质量所造成的损害,泓格科技股份有限公司不承担任何法律责任。泓格科 技股份有限公司有义务提供本系列产品可靠而详尽资料,但保留修订权利,且不承担使用者非法利用资 料对第三方所造成侵害构成的法律责任。

安全导则

在系统最终调试之前,您应该对控制设备进行完整的控制功能测试和必要的安全性能测试。 您在安装、调试、试运行控制设备的过程中,应保证系统涉及或可能涉及设备的安全运行。 由于不可预见的设备错误或操作错误随时可能发生,您在操作中应提高警觉,避免造成此类危及人 身安全或设备损害的事件。

泓格科技(ICP DAS)主网页

专业技术支持 代理商及订购信息 增强设备功能的相关信息 常见问题 应用案例

联络方式 Service@ Copyright ©2008 by ICP DAS Co., Ltd. All right are reserved

1. 检查 Switch1 (此设定值 须与 I/O 地址设定相符)及 Jumper1 and Jumper2 (此

CMWL系列贴片塑封电感器说明书

电感专业制造商 CMWL系列贴片塑封电感器

●EXTERNAL DIMENSIONS UNIT:mm(外形尺寸)

● PART NUMBERING SYSTEM(品名系统)

CMWL1210F 330K T

12345

1、SERIES NAME 品名 C代C.RD.,M指贴片系列,WL为塑封电感系列

2、DIMENSIONS 尺寸 外围*高度 F和D指产品材料代号

3、INDUCTANCE 电感值 前两位为有效数字,第三位表示零的个数

4、TOLERANCE CODE 公差 J:±5%,K:±10%,L:±15%,M:±20%,P:±25%,N:±30%

5、PACKING CODE 包装方式 T:Tape&Reel(卷装) B:In Bulk

● FEATURES(特性)

Various high power inductors are superior to be high saturation for surface mounting.

具有高功率、高饱和电流,低阻抗、小型化之特点

● APPLICATIONS(用途)

录影机、OA仪器、数码相机、液晶电视、笔记本电脑、小型通信机器、DC/DC变压器之电源供应等

************************************************************************************ Design As Customers Requested Specifications可根据客户需求设计

电感专业制造商 CMWL系列贴片塑封电感器。

pw113电路原理图

HVDGSAESLEL 2 00 2 01

2 02

IRIN GSCL

2 03

GSDA(

2 04

DDCD

2 05

SCL ) 2 06

SDA

2 07

KEY7

KEY6

64

X T_O U T TR ST TC K TMS TD I PTOD RO TA 7 PO R TA 6 PO R TA 5 PO R TA 4 PO R TA 3 PO R TA 2 PO R TA 1 PO R TA 0 PO R TB 7 PO R TB 6 PO R TB 5 PO R TB 4 PO R TB 3 PO R TB 2 PO R TB 1 PO R TB 0 PO R TC 7 PO R TC 6 PO R TC 5 PO R TC 4 PO R TC 3 PO R TC 2 PO R TC 1 PO R TC 0 RXD TX D

2

3

V SS3 V SS3 310 V SS3 53 VSS3 73 VSS3 1 0857 V SS3 1 24 V SS3 1 41 V SS3 1 72 V SS3

1 66 V SSP 1 68 V SSP

+1. 8 V A

ETEXSTTR ST

1 42

RST# PWXI

2 8 R ESET 1 39

+1. 8 V B

C 101 0 .1

C 103 0 .1

C 105 0 .1

+3. 3 V A

+3. 3 V A

DBO7 DBO6 DBO5 DBO4 DBO3 DBO2 DBO1 DBO0

1 11 1 12 1 13 1 14 1 15 1 16 1 17 1 18

银河PW说明书

一般组成..............................................… … … (29) 信息显示.................................................… .(29) 测量系统… ...............................................… .(35) 电压测量..................................................… (36) 电流测量................................................… ..(37) 功率和频率测量............................................… (37) 电池测量................................................… ..(37) 选择和设置................................................… (37)

_____________________________________________________________________________________

梅兰日兰电子(中国)有限公司版权所有 第2页

E-51028230XT/BD

Galaxy PW用户手册 目录

启动

系统的启动................................................… (24) 一个模块的启动............................................… (25)

停机

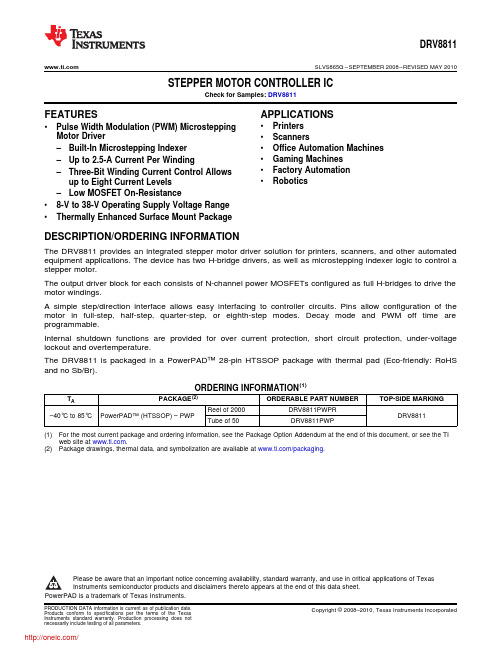

DRV8811PWPR;DRV8811PWP;DRV8811EVM;中文规格书,Datasheet资料

DRV8811 SLVS865G–SEPTEMBER2008–REVISED MAY2010STEPPER MOTOR CONTROLLER ICCheck for Samples:DRV8811FEATURES APPLICATIONS•Printers•Pulse Width Modulation(PWM)MicrosteppingMotor Driver•Scanners•Office Automation Machines –Built-In Microstepping Indexer•Gaming Machines–Up to2.5-A Current Per Winding•Factory Automation–Three-Bit Winding Current Control Allows•Roboticsup to Eight Current Levels–Low MOSFET On-Resistance•8-V to38-V Operating Supply Voltage Range•Thermally Enhanced Surface Mount PackageDESCRIPTION/ORDERING INFORMATIONThe DRV8811provides an integrated stepper motor driver solution for printers,scanners,and other automated equipment applications.The device has two H-bridge drivers,as well as microstepping indexer logic to control a stepper motor.The output driver block for each consists of N-channel power MOSFETs configured as full H-bridges to drive the motor windings.A simple step/direction interface allows easy interfacing to controller circuits.Pins allow configuration of the motor in full-step,half-step,quarter-step,or eighth-step modes.Decay mode and PWM off time are programmable.Internal shutdown functions are provided for over current protection,short circuit protection,under-voltage lockout and overtemperature.The DRV8811is packaged in a PowerPAD™28-pin HTSSOP package with thermal pad(Eco-friendly:RoHS and no Sb/Br).ORDERING INFORMATION(1)T A PACKAGE(2)ORDERABLE PART NUMBER TOP-SIDE MARKINGReel of2000DRV8811PWPR–40°C to85°C PowerPAD™(HTSSOP)–PWP DRV8811Tube of50DRV8811PWP(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .(2)Package drawings,thermal data,and symbolization are available at /packaging.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PowerPAD is a trademark of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©2008–2010,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.DRV8811SLVS865G–SEPTEMBER2008–REVISED FUNCTIONAL BLOCK DIAGRAM2Submit Documentation Feedback Copyright©2008–2010,Texas Instruments IncorporatedProduct Folder Link(s):DRV8811DRV8811 SLVS865G–SEPTEMBER2008–REVISED MAY2010TERMINAL FUNCTIONSNAME NO.I/O(1)DESCRIPTION EXTERNAL COMPONENTS OR CONNECTIONSPOWER AND GROUNDGND7,21-Device groundVMA28-Bridge A power supply Connect to motor supply(8V to38V).Both pins must be connectedto same supply.VMB15-Bridge B power supply Connect to motor supply(8V to38V).Both pins must be connectedto same supply.VCC10-Logic supply voltage Connect to3-V to5-V logic supply.Bypass to GND with a0.1-m Fceramic capacitorCP123IO Charge pump flying capacitor Connect a0.22-m F capacitor between CP1and CP2CP224IO Charge pump flying capacitor Connect a0.22-m F capacitor between CP1and CP2VCP22IO High-side gate drive voltage Connect a0.22-m F ceramic capacitor to V MVGD20IO Low-side gate drive voltage Bypass to GND with a0.22-m F ceramic capacitorCONTROLENABLEn26I Enable input Logic high to disable device outputs,logic low to enable outputs SLEEPn27I Sleep mode input Logic high to enable device,logic low to enter low-power sleep mode DECAY5I Decay mode select Voltage applied sets decay mode-see motor driver description fordetails.Bypass to GND with a0.1-m F ceramic capacitorSTEP19I Step input Rising edge causes the indexer to move one stepDIR3I Direction input Level sets the direction of steppingUSM013I Microstep mode0USM0and USM1set the step mode-full step,half step,quarterstep,or eight microsteps/stepUSM112I Microstep mode1USM0and USM1set the step mode-full step,half step,quarterstep,or eight microsteps/stepRESETn17I Reset input Active-low reset input initializes the indexer logic and disables theH-bridge outputsSRn16I Sync.Rect.enable input When active low,synchronous rectification is enabledVREF8I Current set reference input Reference voltage for winding current setRCA6I Bridge A blanking and off time adjust Connect a parallel resistor and capacitor to GND-see motor driverdescription for detailsRCB9I Bridge B blanking and off time adjust Connect a parallel resistor and capacitor to GND-see motor driverdescription for detailsISENA1-Bridge A ground/Isense Connect to current sense resistor for bridge AISENB14-Bridge B ground/Isense Connect to current sense resistor for bridge BOUTPUTSAOUT14O Bridge A output1Connect to bipolar stepper motor winding AAOUT225O Bridge A output2Positive current is AOUT1→AOUT2BOUT111O Bridge B output1Connect to bipolar stepper motor winding BBOUT218O Bridge B output2Positive current is BOUT1→BOUT2HOMEn2O Home position Logic low when at home state of step table,logic high at other states (1)Directions:I=input,O=output,OZ=3-state output,OD=open-drain output,IO=input/outputCopyright©2008–2010,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):DRV8811ISENAHOMEDIRAOUT1DECAYRCAGNDVREFRCBVCCBOUT1USM1USM0ISENBVMASLEEPnENABLEnAOUT2CP2CP1VCPGNDVGDSTEPBOUT2RESETnSRnVMBDRV8811SLVS865G–SEPTEMBER2008–REVISED ABSOLUTE MAXIMUM RATINGS(1)(2)(3)over operating free-air temperature range(unless otherwise noted)MIN MAX UNIT V MX Power supply voltage range–0.340VV CC Power supply voltage range–0.37V Digital pin voltage range–0.5V CC VV REF Input voltage range–0.3V V CC V ISENSEx pin voltage range–0.30.5VI O(peak)Peak motor drive output current,t<1m s6AI O Continuous motor drive output current±2.5AP D Continuous total power dissipation See Dissipation Ratings Table T J Operating virtual junction temperature range–40150°CT A Operating ambient temperature range–4085°CT stg Storage temperature range–60150°C (1)Stresses beyond those listed under"absolute maximum ratings"may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under"recommended operating conditions"is not implied.Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.(2)All voltage values are with respect to network ground terminal.(3)Power dissipation and thermal limits must be observed.DISSIPATION RATINGSDERATINGBOARD PACKAGE R q JA FACTOR T A<25°C T A=70°C T A=85°CABOVE T A=25°CLow-K(1)PWP67.5°C/W14.8mW/°C 1.85W 1.18W0.96W Low-K(2)PWP39.5°C/W25.3mW/°C 3.16W 2.02W 1.64W High-K(3)PWP33.5°C/W29.8mW/°C 3.73W 2.38W 1.94W High-K(4)PWP28°C/W35.7mW/°C 4.46W 2.85W 2.32W(1)The JEDEC Low-K board used to derive this data was a76mm x114mm,2-layer,1.6mm thick PCB with no backside copper.(2)The JEDEC Low-K board used to derive this data was a76mm x114mm,2-layer,1.6mm thick PCB with25cm22-oz copper onbackside.(3)The JEDEC High-K board used to derive this data was a76mm x114mm,4-layer,1.6mm thick PCB with no backside copper andsolid1oz.internal ground plane.(4)The JEDEC High-K board used to derive this data was a76mm x114mm,4-layer,1.6mm thick PCB with25cm21-oz copper onbackside and solid1oz.internal ground plane.4Submit Documentation Feedback Copyright©2008–2010,Texas Instruments IncorporatedProduct Folder Link(s):DRV8811DRV8811 SLVS865G–SEPTEMBER2008–REVISED MAY2010RECOMMENDED OPERATING CONDITIONSover operating free-air temperature range(unless otherwise noted)MIN NOM MAX UNITV M Motor power supply voltage range(1)838VV CC Logic power supply voltage range3 5.5VV REF VREF input voltage V CC V(1)All V M pins must be connected to the same supply voltage.Copyright©2008–2010,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):DRV8811DRV8811SLVS865G–SEPTEMBER2008–REVISED ELECTRICAL CHARACTERISTICSover operating free-air temperature range(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Power SuppliesI VM V M operating supply current V M=35V,f PWM<50KHz 4.58mAI VCC V CC operating supply current f PWM<50KHz0.44mAI VMQ V M sleep mode supply current V M=35V1220m AI VCCQ V CC sleep mode supply current520m AV M undervoltage lockout voltage V M rising 6.78V UVLO V V CC undervoltage lockout voltage V CC rising 2.71 2.95VREF Input/Current Control AccuracyI REF VREF input current VREF=3.3V–33m AVREF=2.0V,70%to100%current–55%ΔI CHOP Chopping current accuracyVREF=2.0V,20%to56%current–1010% Logic-Level InputsV IL Input low voltage0.3×V CC VV IH Input high voltage0.7×V CC VI IL Input low current VIN=0.3×V CC–2020m AI IH Input high current VIN=0.3×V CC–2020m A HOMEn OutputV OL Output low voltage I O=200m A0.3×VCC VV OH Output high voltage I O=–200m A0.7×VCC V Decay Input0.21×V IL Input low threshold voltage For fast decay mode VVCCV IH Input high threshold voltage For slow decay mode0.6×VCC VH-Bridge FETSV M=24V,I O=2.5A,T J=25°C0.50R ds(on)HS FET on resistanceΩV M=24V,I O=2.5A,T J=85°C0.600.75V M=24V,I O=2.5A,T J=25°C0.50R ds(on)LS FET on resistanceΩV M=24V,I O=2.5A,T J=85°C0.600.75I OFF–2020m A Motor Drivert OFF Off time Rx=56kΩ,Cx=680pF303846m st BLANK Current sense blanking time Rx=56kΩ,Cx=680pF7009501200nst DT Dead time(1)SRn=010*******ns Protection CircuitsI OCP Overcurrent protection trip level 2.5 4.5 6.5At TSD Thermal shutdown temperature(1)Die temperature150160180°C (1)Not tested in production-guaranteed by design.6Submit Documentation Feedback Copyright©2008–2010,Texas Instruments IncorporatedProduct Folder Link(s):DRV8811STEP DIR,USMx SLEEPnDRV8811 SLVS865G–SEPTEMBER2008–REVISED MAY2010TIMING REQUIREMENTSover operating free-air temperature range(unless otherwise noted)PARAMETER MIN MAX UNIT f STEP Step frequency500kHz t WH(STEP)Pulse duration,STEP high1m st WL(STEP)Pulse duration,STEP low1m st SU(STEP)Setup time,command to STEP rising200nst H(STEP)Hold time,command to STEP rising200nst WAKE Wakeup time,SLEEPn inactive to STEP1msCopyright©2008–2010,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):DRV8811DRV8811SLVS865G–SEPTEMBER2008–REVISED FUNCTIONAL DESCRIPTIONPWM H-Bridge DriversDRV8811contains two H-bridge motor drivers with current-control PWM circuitry,and a microstepping indexer.A block diagram of the motor control circuitry is shown below.Figure1.Block Diagram8Submit Documentation Feedback Copyright©2008–2010,Texas Instruments IncorporatedProduct Folder Link(s):DRV88118REFX CHOP ISENSEV I R =·OFF t R C=·1400BLANK t C=·DRV8811SLVS865G –SEPTEMBER 2008–REVISED MAY 2010Current RegulationThe PWM chopping current is set by a comparator,which compares the voltage across a current sense resistor,multiplied by a factor of 8,with a reference voltage.The reference voltage is input from the VREF pin.The full-scale (100%)chopping current is calculated as follows:(1)Example:If a 0.22-Ωsense resistor is used and the VREFx pin is 3.3V,the full-scale (100%)chopping current is 3.3V/(8*0.22Ω)=1.875A.The reference voltage is also scaled by an internal DAC that allows torque control for fractional stepping of a bipolar stepper motor,as described in the "Microstepping Indexer"section below.When a winding is activated,the current through it rises until it reaches the chopping current threshold described above,then the current is switched off for a fixed off time.The off time is determined by the values of a resistor and capacitor connected to the RCA (for bridge A)and RCB (for bridge B)pins.The off time is approximated by:(2)To avoid falsely tripping on transient currents when the winding is first activated,a blanking period is used immediately after turning on the FETs,during which the state of the current sense comparator is ignored.The blanking time is determined by the value of the capacitor connected to the RCx pin and is approximated by:(3)Decay ModeDuring PWM current chopping,the H-bridge is enabled to drive through the motor winding until the PWM current chopping threshold is reached.This is shown in Figure 2,Item 1.The current flow direction shown indicates positive current flow in the step table below.Once the chopping current threshold is reached,the H-bridge can operate in two different states,fast decay or slow decay.In fast decay mode,once the PWM chopping current level has been reached,the H-bridge reverses state to allow winding current to flow in a reverse direction.If synchronous rectification is enabled (SRn pin logic low),the opposite FETs are turned on;as the winding current approaches zero,the bridge is disabled to prevent any reverse current flow.If SRn is high,current is recirculated through the body diodes,or through external Schottky diodes.Fast-decay mode is shown in Figure 2,Item 2.In slow-decay mode,winding current is re-circulated by enabling both of the low-side FETs in the bridge.This is shown in Figure 2,Item 3.Copyright ©2008–2010,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):DRV8811Drive current Slow decay (brake)Fast decay (reverse)0.6CC FDDECAYV t R C In V æö·=··ç÷èøDRV8811SLVS865G –SEPTEMBER 2008–REVISED MAY 2010Figure 2.Decay ModeThe DRV8811also supports a mixed decay mode.Mixed decay mode begins as fast decay,but after a period of time switches to slow decay mode for the remainder of the fixed off time.Fast and mixed decay modes are only active if the current through the winding is decreasing;if the current is increasing,then slow decay is always used.Which decay mode is used is selected by the voltage on the DECAY pin.If the voltage is greater than 0.6x V CC ,slow decay mode is always used.If DECAY is less than 0.21x V CC ,the device operates in fast decay mode when the current through the winding is decreasing.If the voltage is between these levels,mixed decay mode is enabled.In mixed decay mode,the voltage on the DECAY pin sets the point in the cycle that the change to slow decay mode occurs.This time can be approximated by:(4)Operation of the blanking,fixed off time,and mixed decay mode is illustrated in Figure 3.10Submit Documentation FeedbackCopyright ©2008–2010,Texas Instruments IncorporatedProduct Folder Link(s):DRV8811分销商库存信息:TIDRV8811PWPR DRV8811PWP DRV8811EVM。

SHAIXING GUANGDA BUSINESS SHD SEMICONDUCTOR CO.,LT

概述SDC11557是一款单项全波风扇驱动电路,具有三种速度控制模式。

T 输出为放大的霍尔信号,适用于游戏机、CPU 制冷风扇等需要低噪音的风扇。

芯片内置锁机保护功能和温度保护功能。

在正常运转时,芯片静态电流小于5mA.SDC11557适用于MSOP-8封装。

应用⏹低噪音单相直流风扇特点⏹ 静音驱动⏹ 内置锁机保护和自动重启功能 ⏹ 具有低功耗待机模式(PWM=0) ⏹ 集成FG ⏹ 集成温度保护功能 ⏹ 低占空比启动管脚描述1OUT22VCC 3IN+4IN-5FG6PWM 7OUT18GND图1 管脚排布管脚编号管脚名称管脚功能 1 OUT2 输出2脚 2 VCC 电源 3 IN+ 霍尔输入正端 4 IN- 霍尔输入负端 5 FG 转速频率输出 6 PWM PWM 输入 7 OUT1 输出1脚 8 GND接地端表1 管脚描述功能框图图2 功能框图订购信息封装温度范围标识号 打印Pb-free Halogen-free Pb-free Halogen-free 包装形式SDC11557MTR-E1SDC11557MTR-G11557 1557 编带MSOP-8-40~85℃SDC11557M-E1 SDC11557M-G1 15571557 管装绝对最大额定值(注意:应用不要超过最大额定值,以防止损坏。

长时间工作在最大额定值的情况下可能影响器件的可靠性。

)参 数符 号条件数 值单 位V CC 最大允许电压 V CC - -0.3 to 8V最大输出电流 I OUT - 1 A 输出脚最大允许电压 V OUT - -0.3 to 8 V FG 最大允许电压 V FG - -0.3 to 8VFG 最大输出电流 I FG - 10 mA 储藏温度 T STG - -65 to 150 ℃ 焊接温度,10S T SDR - 260 ℃ 最大结温Tj--40 to 150℃表2 最大额定值推荐工作条件参 数符 号条件数 值单 位V CC 工作电压范围 V CC 2.0 to 6.0 V 霍尔输入共模电压范围 V Hall 0.4 to Vcc-1.1 V 环境温度Ta-40 to 105℃表3 推荐工作条件电气参数(无特别指明情况下:Ta=25℃,VCC=12V )参数符号条件下 限典 型 上 限 单 位I CC1 运转、锁机保护- 4 5 mA 工作电流 I CC2待机(PWM=0)- 0.1 0.2µA锁机检测时间 T ON 0.350.5 0.65 S 锁机保护时间 T OFF 3.5 5 6.5 S 输出管饱和压降V O I OUT = 250mA, 上下管总压降- 0.3 0.44 V FG 饱和压降 V FG I FG = 5mA - 0.2 0.4 V FG 漏电流 I FGL VFG = 5V -<0.11µA 增益 G IOV OUT /(V IN+-V IN-)44 45 46dBPWM 高电平 V PWMH 0.5xV CC - V CC +0.5 VPWM 低电平 V PWML0 - 0.2xV CC VPWM 输入频率范围F PWM 0.02 - 50 kHZ 快速启动激活时间 T QS - 66.5 90 ms 霍尔输入失调电压 V HOFS - - ±6 mV 霍尔输入迟滞 V HYS ±5±10 ±15 mV 温度保护点OTS- 165 -℃温度保护迟滞/ - 30 - ℃表4 电特性真值表输入输出IN- IN+ PWMIN-IN+ PWM工作模式IN-L H L HHH L H H LH L HLLL H LL H L H H L L H LH-H L-H L L H - - L--L-表5 真值表功耗曲线图3 功耗曲线图(MSOP-8)典型应用图图4 典型应用图功能描述锁机保护和自动重启功能芯片提供锁机保护和自动重启功能,在风扇发生锁止情况时避免线圈过热烧毁。

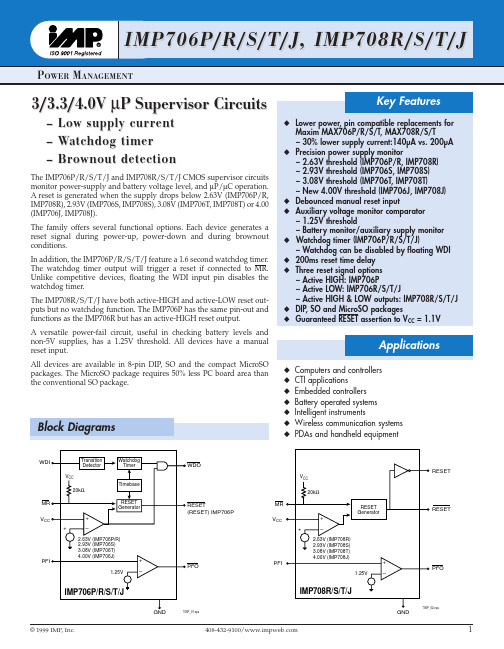

IMP813L中文资料

Key Features

x Lower power, pin compatible replacements for Maxim MAX706P/R/S/T, MAX708R/S/T – 30% lower supply current:140µA vs. 200µA

x Precision power supply monitor – 2.63V threshold (IMP706P/R, IMP708R) – 2.93V threshold (IMP706S, IMP708S) – 3.08V threshold (IMP706T, IMP708T) – New 4.00V threshold (IMP706J, IMP708J)

5 GND

706P_03.eps

Ordering Information

Part Number

IMP706PCPA IMP706PCSA IMP706PCUA IMP706PEPA IMP706PESA IMP706RCPA IMP706RCSA IMP706RCUA IMP706REPA IMP706RESA IMP706SCPA IMP706SCSA IMP706SCUA IMP706SEPA IMP706SESA IMP706TCPA IMP706TCSA IMP706TCUA IMP706TEPA IMP706TESA IMP706JCPA IMP706JCSA IMP706JCUA IMP706JEPA IMP706JESA IMP708RCPA IMP708RCSA IMP708RCUA IMP708REPA IMP708RESA IMP708SCPA IMP708SCSA IMP708SCUA IMP708SEPA IMP708SESA IMP708TCPA IMP708TCSA IMP708TCUA IMP708TEPA IMP708TESA IMP708JCPA IMP708JCSA IMP708JCUA IMP708JEPA IMP708JESA

电源控制器 PW-8说明书

淳中视讯电源控制器 PW-8 使用说明书目录绪言................................................................................................2页一:本机特点................................................................................2页二:通讯协议................................................................................3页协议定义.................................................................................3页协议解析.................................................................................3页三:电源控制器平面图................................................................5页四:电源控制器连接方法............................................................6页五:注意事项及常见故障检修....................................................7页附录一:售后服务与技术支持....................................................7页感谢您购买和使用本公司的PW-8电源控制器产品。

在使用本机前,请细阅这本用户手册,以便能正确使用。

并且请妥善保存这本手册,万一有不了解或故障时,这本手册会带给您很大的帮助。

HLW8012用户手册

模拟输入(所有通道)

共模信号

模拟输入

满量程时对电压通道的串扰 (50, 60Hz) 输入电容

等效输入阻抗

电流通道 电压通道

等效输入噪声

电流通道 电压通道

电源供给

电流消耗

IA+ID

功耗

(VDD = 5 V)

掉电检测低压阈值

掉电检测高压阈值

符号 PActive IRMS VRMS

IC EII NI

PC PMLO PMHI

版本 REV 1.0 REV 1.1 REV 1.2 REV 1.3

REV 1.3

1/9

HLW8012 1 芯片功能说明

HLW8012 为单相多功能计量芯片,其提供高频脉冲 CF 用于电能计量和高频 CF1 用于指示电流 有效值或者电压有效值。本芯片采用 SOP8 封装。

2.2 模拟特性

符号 VDD TA

最小值 4.5 -40

典型值 5.0 -

最大值 5.5 +85

单位 V ℃

VDD = 5 V ± 10%;GND = 0 V

参数

精度

有功功率

全增益范围

输入范围 0.1%~100%

电流有效值

全增益范围

输入范围 0.2%~100%

电压有效值

全增益范围

输入范围 0.2%~100%

最小值 典型值 最大值 单位

-

±0.2

-

%

-

±0.5

-

%

-

±0.5

-

%

-1

-

1

V

-

-100

-

dB

-

6.4

-

pF

SY87813LHG TR;SY87813LHG;中文规格书,Datasheet资料